Изобретение относится к ядерной электронике и может быть применено для определения координат линейных треков и прослеживания треков частиц при обработке данных эксперимен та в ядерной физике.

Цель изобретения - расширение области применения и увеличение производительности устройства путем обработки координат нескольких тре- ков на каждой строке разложения исследуемой картины.

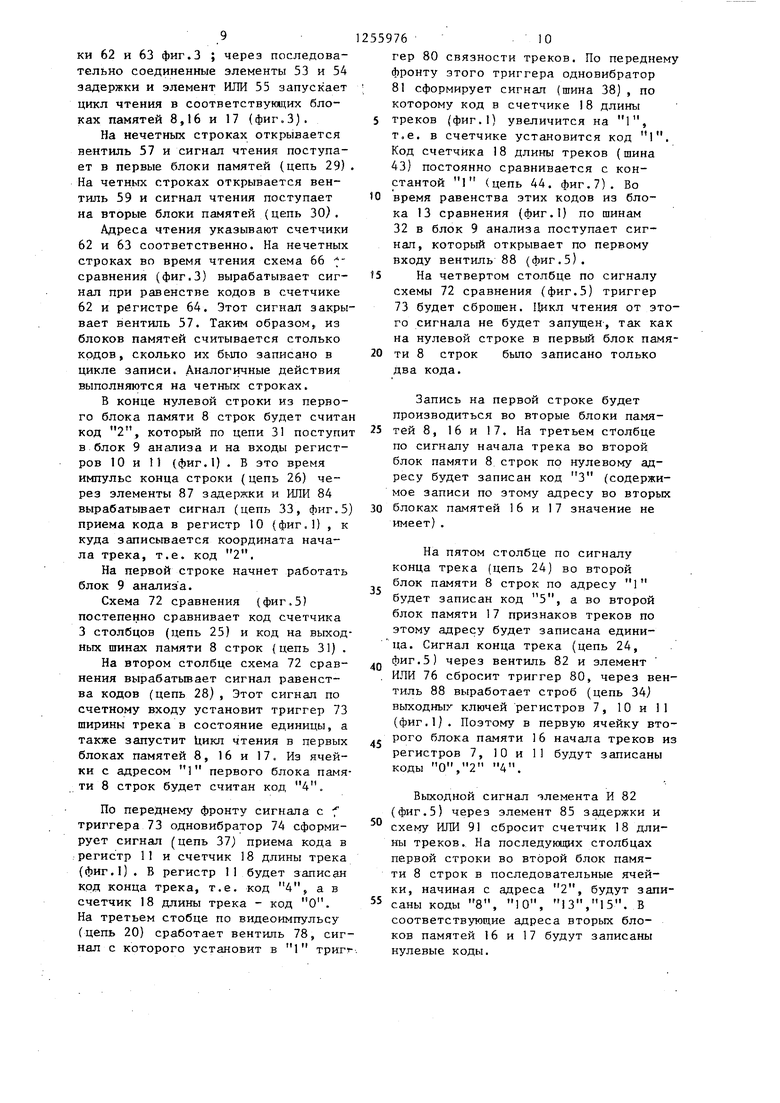

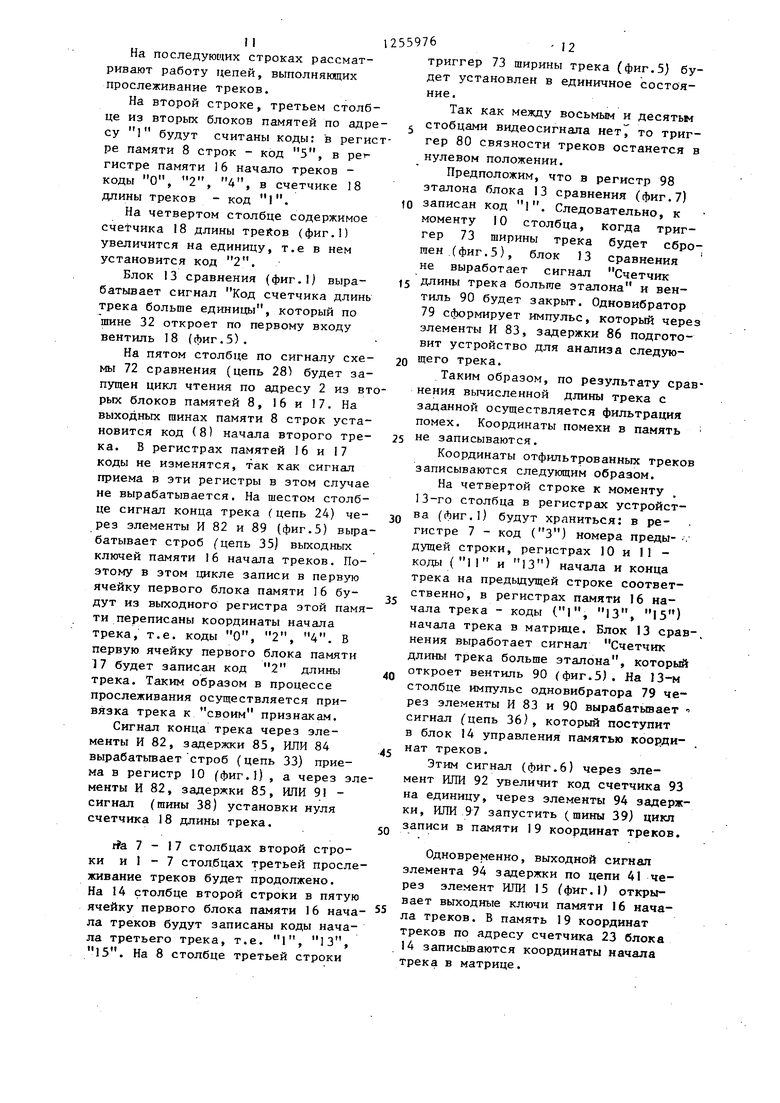

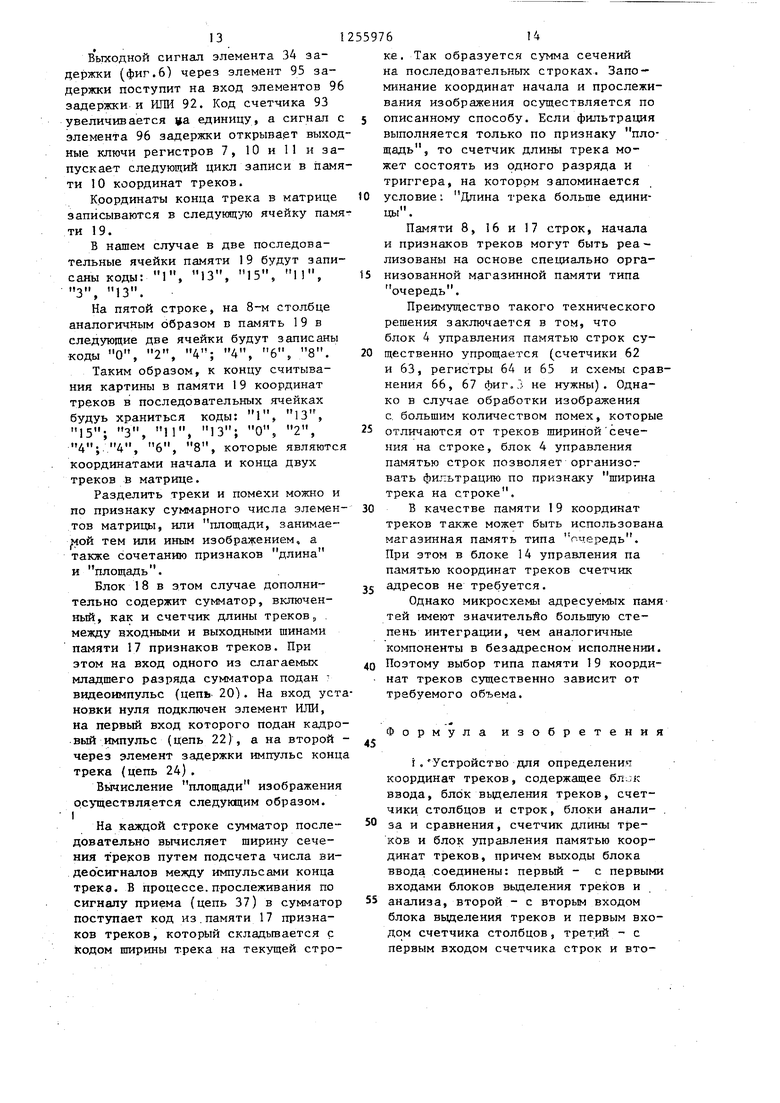

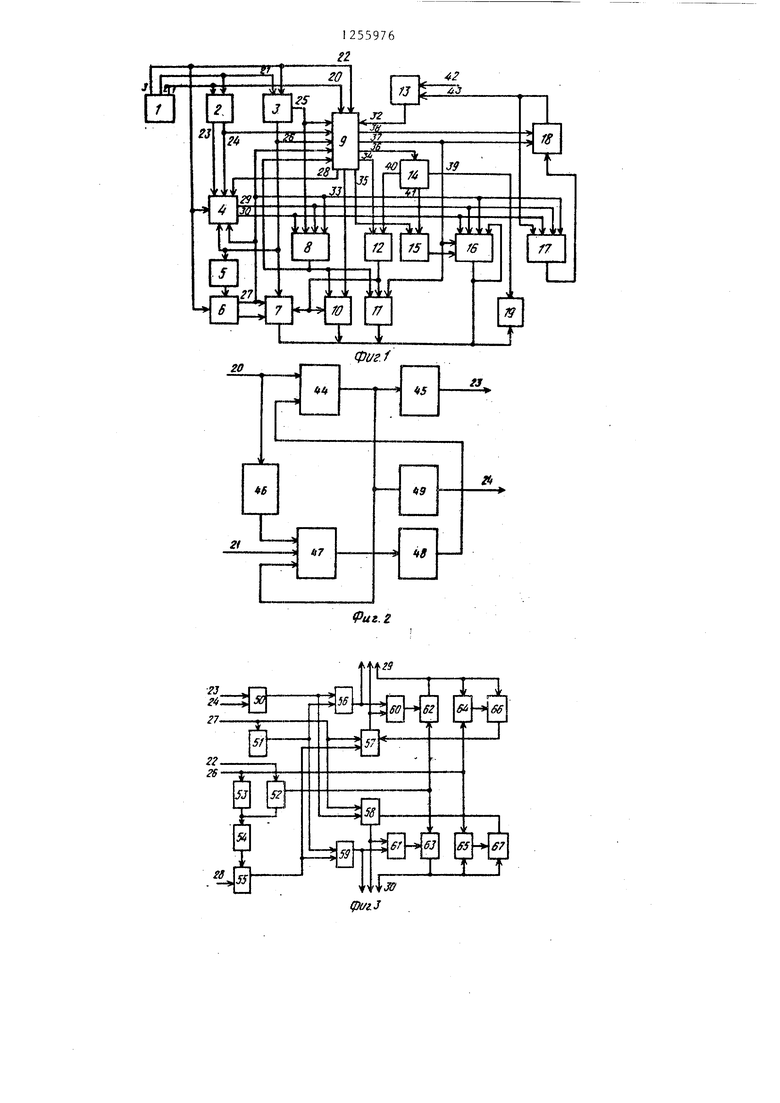

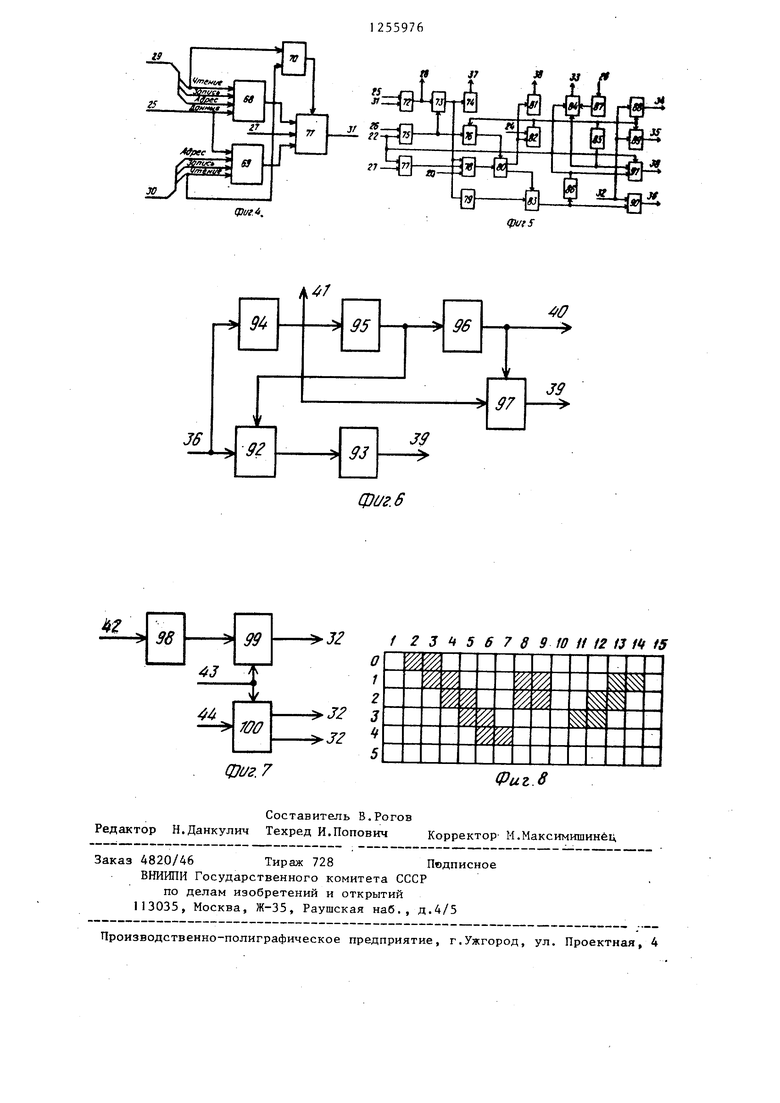

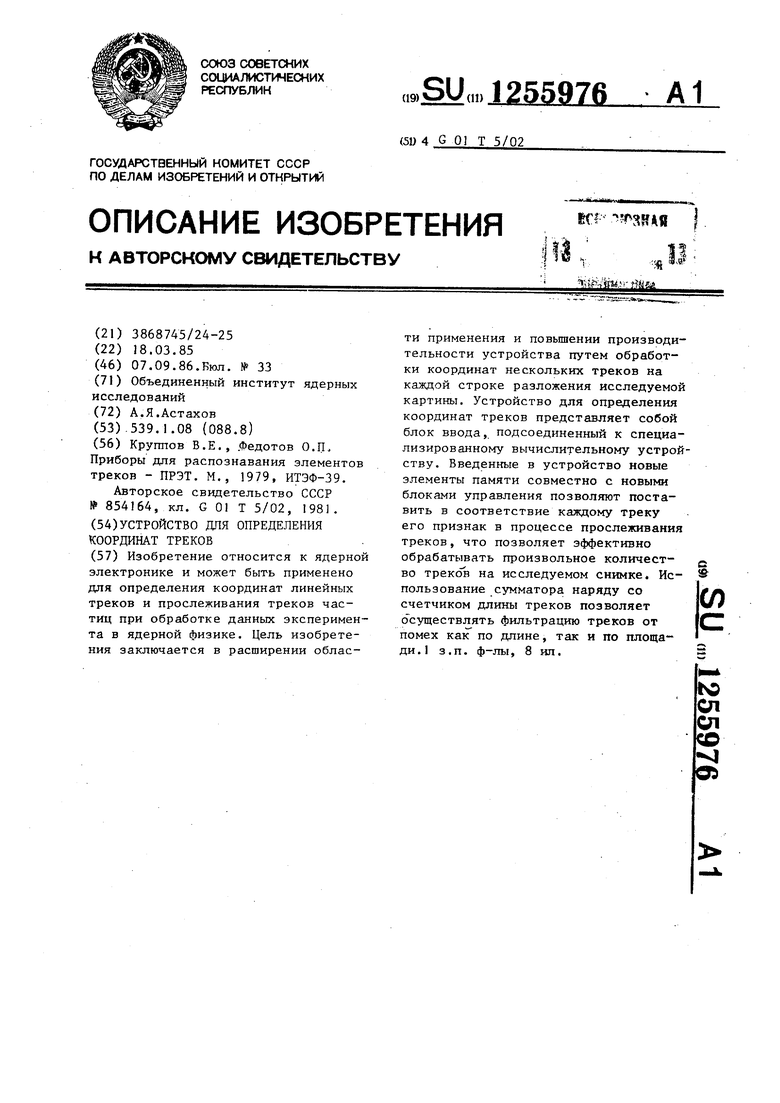

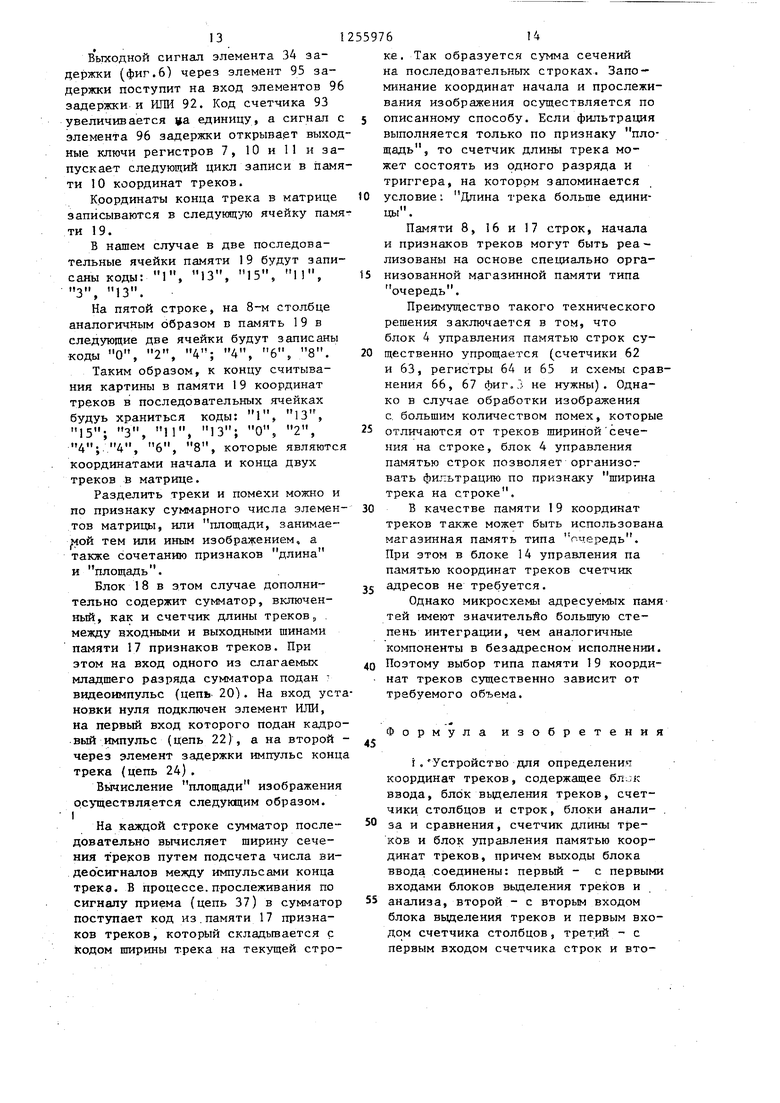

На фиг.1 приведена блок-схема устройства для определения координат треков; на фиг.2 - структурная схема блока вьщеления треков; на фиг.З - структурная схема блока управления памяти строк; на фиг,4 - структурная схема памяти строк; на фиг.5 - структурная схема блока анализа; на фиг.6 - структурная схема блока управления памятью координат треков; на фиг. 7 - струк- турная схема блока сравнения; .. на фиг.8 - типичная картина, обра- батываемая устройством.

Устройство для определения координат треков содержит блок 1 ввода, блок 2 выделения треков, счетчик 3 столбцов, блок 4 управ- ления памятью строк, элемент 5 задержки, счетчик 6 строк, первый 10 и второй 1I и третий 7 регистры с выходными ключами, память 8 строк, блок 9 анализа, элементы ИЛИ 12 и 1 блок 13 сравнения, блок 14 управления памятью координат треков, блок 16 начала треков, память 17 признаков треков, счетчик 18 длины треков

память 19 координат треков.

Первый выход блока 1 ввода (цепь 20) соединен с первыми входами блока 2 вьщеления треков и блока 9 анализа, второй {цепь 21) - с вторым входом блока 2 выделения треков и первым входом счетчика 3 столбцов, третий (цепь 22) - с первыми входами блока 4 управления памятью строк и счетчика 6 строк, вторым входом счетчика 3 столбцов и четвертым вхо- дом блока 9 анализа. Выходы блока 2 вьщеления треков соединены: первый

(цепь 23) - с вторым входом блока 4 управления памятью строк, второй

(цепь 24) - с третьим входом блока 4 и третьим входом блока 9 анализа. Первый выход счетчика 3 столбцов (цепь 25) подключен к второму входу

5 0 5

0 ,

0

0

5

блока 9 анализа и третьему входу памяти 8 строк, второй выход счетчика 3 (цепь 26) соединен с четвертым входом блока 4 управления памятью- строк, первым входом регистра 7, шестым входом блока 9 анализа и через элемент 5 задержки - с вторым входом счетчика 6 строк, выходы которого подключены к вторым входам регистра 7, причем первый разряд счетчи- . ка 6 строк (цепь 27) соединен с шестым входом блока 4 управления памятью строк, седьмым входом блока 9 анализа и четвертыми входами памятей В, 16 и 17 строк, начала и признаков треков, первые и вторые входы которых подключены соответственно к первым (цепь 29) и вторым (цепь ЗО) выходным шинам блока 4 управления памятью строк. Выходы памяти 8 строк (цепь 3) подключены к первым входам регистров 10 и 11 и пятым входам блока 9 анализа, на восьмые входы которого подключены выходы ( цепь 32). блока 13 сравнения. Выходы блока 9 анализа соединены: первый - с пятым входом блока 4 управления памятью строк (цепь 28), второй - с вторым входом регистра 10 (цепь 33) , третий и четвертый - с первыми входами элементов ИЛИ 12 и 15 соответствен- но (цепи 34 и 35), пятьй - с выходом блока 14 управления памятью координат треков (цепь 36), шестой - с первым входом счетчика 18 длины треков, вторым входом регистра 11 и пятым входом памяти 16 начала треков (цепь 37) , седьмой - с вторым входом счетчика 18 длины треков (цепь 38). Выходы блока 14 управления памятью координат треков соединены: первый - с первым входом па памяти 19 координат треков (цепь 39) на вторые входы которой подключены выходы памяти 16 начала треков и четвертые входы этой же памяти, а также соответствующие выходы регистров 7, 10 и 11 , второй - .с вторым входом элемента ИЛИ 12 (цепь 40), выход которого соединен с третьими входами регистров 7, 10 и 11, третий - с вторым входом элемента ИЛИ 15 (цепь 41), выход которого соединен с шестым входом памяти 16 начала треков.

Между третьими входами и выход- -, ными шинами памяти 17 признаков треков включен счетчик 18 длины

треков, выход которого.подключен также к первом входу блока 13 сранения (цепь 43), на второй вход которого поступает код эталона (цепь 42),

Блок 1 ввода осуществляет разло ние исследуемой картины на ячейки по строкам и столбцам, преобразование освещенности каждой ячейки в электрический сигнал и выдачу видесигналов от каждой ячейки.

Реализовать блок 1 ввода можно на основе телевизионной камеры на приборах с зарядовой связью.

На первый выход блока 1 поступают видеоимпульсы (цепь 20), на второй и третий - синхронизирующие и кадровые импульсы соответственно (цепи 21 и 22).

Блок 2 выделения треков вырабатывает сигналы начала и конца каждого трека на строке и содержит (фиг.2 триггер 44, одновибраторы 45, 48 и 49, инвертор 46, схему И 47 и элемент 48 задержки.

Первый вход блокэ 2 (цепь 20) поключен к установочному входу триггера 44 и входу инвертора 46, выход которого соединен с первым входом схемы И 47, второй вход которой подключен к второму входу блока 2 (цепь 21) . Выход схемы И 47 через элемент 48 задержки соединен с входом установки нуля триггера 44, выход которого подключен к входам одновибраторов 45 и 49 и третьему входу.схемы И 47. Выходы одновибраторов 45 и 49 образуют первый и второй выходы блока 2 выделения треков (цепи 23 и 24).

Счетчик 3 столбцов осуществляет пересчет синхроимпульсов по модулю числа элементов в строке.

Блок 4 управления памятью строк вырабатывает сигналы Запись, Чтение и адреса для каждого блока памяти 8, 16, 17 строк, начала и . признаков треков, соответственно и содержит (фиг.З) элементы ИЛИ 50, 52 и 55, инвертор 51, элементы 53 и 54 задержки, элементы И 56 - 59, элемент ИЛИ, последовательно соединенный с элементами 60 и 61 задержки, счетчики 62 и 63, регистры 64 и 65, а также 66 и 67 сравнения.

Первый вход блока 53 (цепь 22) подключен к первому входу элемента

559764

ИЛИ 52, выход которого соединен с входами установки нуля счетчиков 62 и 63. Второй и третий входы блока 53 (цепи 23, 24) подключены к вхо- 5 дам элементов И 56 и 58.

Четверты вход (цепь 26) подключен к входам приема кода в регистры 64 и 65 и через элемент 53 задержки - к второму входу элемента ИЛИ 52 10 и входу элемента 54 задержки. Пятый вход (цепь 28) подключен к входу элемента ИЛИ 55, второй вход которого соединен с выходом элемента 54 задержки, а выход соединен с входа- 15 ми элементов И 57 и 59. Шестой вход (цепь 27) подключен к вторым входам элементов И 57 и 58 и через инвертор 51 - к вторым входам элементов И 56 и 59.

20 Вьсходы элементов И 56 и 59 через элемент ИЛИ, последовательно соединенный с элементом 60 задержки, соединены со счетным входом счетчика 62, выход которого соединен с информа- 25 ционным входом регистра 64 и первым входом схемы 66 сравнения, на второй вход которогой подключен выход регистра 64, а выход схемы 66 сравнения соединен с третьим входом схе- O мы И 57. Выходы схем И 56 и 57 и счетчика 62 соединены с первыми выходами блока 4 шины 29). Выходы элементов И 58 и 59 через элемент ИЛИ, последовательно соединенный с , элементом 61 задержки соединены со счетным входом счетчика 63, выход которого соединен с информационным входом регистра 65 и первым входом схемы 67 сравнения, на второй вход 0 которой подключен выход регистра 65. а выход схемы 67 сравнения соединен с третьим входом элемента И 58. Выходы элементов И 58 и 59 и счетчика 63 образуют второй выход бло- 5 ка 4 (шины 30) .

Счетчик 6 строк вырабатывает номер строки разложения последующего изображения.

Регистры 7,10 и 11 служат для Q временного хранения координат треков в следуюгцем формате: номер строки, начало и конец трека на строке. Регистры имеют три.входа: информацио- ный вход строба приема кода и строк 5 выходных ключей.

Выходные ключи регистров имеют три состояния: логический уровень высокий , низки 1 и Вьжлючено.

Память 8 строк служит для временного хранения информации и треках текущей строки в формате: начало и конец п&рвого трека, начало и конец второго и т.д.

Состав памяти 8 строк (фиг.4) состоит из первого блока 68 памяти, второго блока 69 памяти, элемента ИЛИ 70, ь|ультиплексора с регистром

.71.

Первые и вторые входы памяти 8 строк, которые образуют сигналы Чтение, Запись и адреса для блоков 68 и 69 памяти подключены соответственно к шинам 29 и 30. Информа ционные входы блоков 68 и 69 памяти подключены к входной шине 25.

Управляющий вход мультиплексора подключен к шине 27. Сигналы Чтение блоков 68 и 69 памяти через элемент ИЛИ 70 подключены к входу строба приема кода в регистр. Информационные выходы блоков 68 и 69 памяти подключены к входам мультиплексор

Память 16 начала треков служит для временного хранения координат начала треков в формате: номер строки, координаты начала и конца трека на строке. Память 16 начала треков имеет структуру, подобную памяти 8 строк. Отличия заключаются в том, что регистр имеет выходные ключи.

Память 16 начала треков по сравнению с памятью 8 строк имеет два дополнительнб1х входа: вход строба .приема кода в регистр и строк выходных ключей.

Память 17 признаков треков служит для хранения в процессе прослеживания треков признаков, по которым выполняется фильтрация треков от помех. Структура памяти 17 признаков треков подобна структуре памяти 8 строк. Выходом памяти 17 служат выходы мультиплексора.

Блок 9 анализа проверяет связность треков на последовательных строках разложения исследуемой картины. По этому условию вырабатываются сигналы для вычисления длины треков, запоминания координат начала и координат отфильтрованных треков. Блок 9 С фиг.5) включает в себя схему 72 сравнения, триггеры 73, 77 и 80, одновибраторы 74, 79 и 81, элементы ИЛИ 75,. 76, 84 и 91, элементы И 78, 82, 83, 88 - 90, элементы 85 - 87 задержки.

Первьй вход элемента И 78 является первым входом блока 9 (цепь 20), Второй и пятый входы блока (цепи 25 и 31) подключены к входам схемы 72 сравнения, выход которой является первым выходом блока 9 (цепь 28) и подключен к входу установки единицы триггера 73.

Первый вход элемента И 82 служит третьими входом блока 9 (цепь 24). Четвертый вход блока 9 (цепь 22) соединен с первыми входами элементов ИЛИ 75 и 91 и входом установки нуля триггеров 77, единичный вход которого является седьмым входом блока 9. Шестой вход блока (цепь 26) соединен с вторым входом элемента ИЛИ 75 и через элемент 87 задержки - первым входом элемента ИЛИ 84. Шины восьмого входа (цепь 32) соединены соответственно с первыми входами элементов И 88 - 90.

Выход элемента ИЛИ 75 соединен с первым входом элемента ИЛИ 76 и входом установки нуля триггера 73, выход которого соединен с входами одновибраторов 74, 79 и вторым входом элемента И 78, на третий вход которого подключен выход триггера 77. Выход элемента ИЛИ 76 соединен с входом установки нуля триггера 80, единичный вход которого соединен с выходом элемента И 78 а единичный выход - с входом одновибратора 81 и вторым входом элемента И 82, выход которого соединен с вторым входом элемента ИЛИ 76, вторыми входами элементов И 88 и 89 и .через элемент 85 задержки - с вторыми входами элементов ИЛИ 84 и 91. Нулевой выход триггера 80 соединен с первым-входом элемента И 83, на второй вход которого подключен выход одновибратора 79, а выход элемента И 83 соединен с вторым входом элемента И 90 и через элемент 86 задержки - с третьими входами элементов ИЛИ 84 и 91. Выходами блока 9 анализа являются: вторым - выход элемента ИЛИ 84 (цепь 33) , третьим и четвертым - выходы элементов И 88 и 89 (цепи 34, 35J , пятым - выход элемента И 90, шестым.- вькод одновибратора 74, седьмыми - выходы одно- вибратора 81 и элемента ИЛИ 9.

Блок 14 управления памятью координат треков вырабатывает сигнал Запись, коды адресов для памяти 19 координат треков и выходные стро

бы для регистров 7,10, .11 и памяти начала треков. Блок 14 (фиг.6) содержит элементы ИЛИ 92 и 97, счет - чик 93, элементы 94 - 96 задержки.

Первый вход элемента ИЛИ 92 и вход элемента 94 задержки подключены к входной цепи 36. Элементы 94-9 задержки включены последовательно, причем выходы элементов 94 и 96 задержки соединены с входами элемента ИЛИ 97. Выход элемента 95 задержки соединен с вторым входом элемента ИЛИ 92, выход которого подключен к суммирующему входу счетчика 93.

Выходами блока 14 являются: первым - выходы счетчика 93 и элемента ИШ 97 (шины 39), вторым - выход элемента 96 задержки (цепь 40), третьим - выход элемента 94 задержки (цепь 41).

Блок 13 сравнения вьграбатьгаает сигналы, по которым осуществляется управление процессом прослеживания треков и состоит из (фиг.7) регистра 98 эталона, схем 99 и 100 сравнения.

Первые входы схем 99 и 100 сравнения являются первыми входами блока 13. На второй вход схемы 99 сравнения подключен выход регистра 98 эталона, выходные шины которого являются вторым входом блока 13(цепь 42j. На второй вход схемы 100 сравнения поступает код единицы (цепь 44. Выход Счетчик длины трека болше эталонаМсхемы 99 сравнения, а также вькоды Счетчик длины трека равен единице и больше единицы схемы 100 сравнения образуют выходн шины блока 13 (цепь 32).

Счетчик 18 длины треков вычисляет признак длина трека или фона на последовательных строках.

Координаты отфильтрованных тре- ков записьтаются в память I9 координат треков. Информация о треках хранится в следующем формате: номер строки, начало и конец трека на строке.

Устройство работает следующим образом.

При анализе картины (фиг.8), кадровый импульс блока 1 ввода (цепь 2

сбрасьгеает: счетчики столбцов 3 и строк 6 (фиг.1), через элемент ШШ 52 - счетчики 62 и 63 (фиг.З), триггер 77, через элемент ИЛИ 75 25

40

559768

триггер 73, через элемент ИЛИ 76 - триггер 80, через элемент ИЛИ 91 (шины 38, Фиг.5) - счетчик I8 длины треков (фиг.1) .

J При появлении видеоимпульса триггер 44 блока 2 вьщеления треков устанавливается в единицу (фиг.2).

Одновибратор 45 формирует сигнал начала трека (цепь 23). Если трек 10 занимает несколько ячеек на текущей строке, то триггер 44 все это время- удерживается в единичном состоянии. По окончании трека срабатывает вентиль 47 и через элемент 48 задержки 15 устанавливает триггер 44 в нулевое положение. Одновибратор 49 формирует импульс конца трека (цепь 24).

В случае картины, на фиг.8 на нулевой строке (по коду с.четчика 20 строк импульс начала трека будет сформирован на втором столбце, ,а импульс конца трека - на четвертом.

Сигналы начала и конца трека запускают циклы записи в блоках памятей 8, 16 и 17. На четных строках открывается вентиль 56 и сигнал записи поступает в первые блоки памятей (цепь 29, фиг.З). Адрес записи указывает счетчик 62. После каждого импульса начала и конца трека код в счетчике 62 увеличивается на единицу.

На нечетных строках открывается вентиль 58 и сигнал записи поступает на вторые блоки памятей (цепь 30) . Адрес записи в этом случае указывает счетчик 63. На нулевой строке в первый блок памяти 8 строк по адресам О и 1 будут записаны коды 2 и 4. В первые блоки памятей 16 и 17 по этим адресам будут записаны О,

В конце нулевой строки счетчик 3 столбцов вырабатывает сигнал конца строки (цепь 26), который разрешает прием кода из счетчика 6 строк в : регистр 7 (фиг.1) , а также кода из счетчиков 62 и 63 в регистры 64.и 6| соответственно (фиг.З), сбрасывает через элемент ИЛИ 75 триггер 73, через элемент ИЛИ 76 триггер 80 (фиг.5).

30

35

45

50

Импульс конца строки через элемент 5 задержки поступает на счетчик 6 строк, на котором устанавлива.-- ется код следуицей строки, в конце нулевой строки на счетчике 6 установится код 1, через элементы 53 задержки и ИЛИ 52 сбрасывает счетчи-.

ки 62 и 63 фиг.З ; через последовательно соединенные элементы 53 и 54 задержки и элемент ИЛИ 55 запускает цикл чтения в соответствующих блоках памятей 8,16 и 17 (фиг.З).

На нечетных строках открывается вентиль 57 и сигнал чтения поступает в первые блоки памятей (цепь 29) . На четных строках открывается вентиль 59 и сигнал чтения поступает на вторые блоки памятей (цепь 30).

Адреса чтения указывают счетчики 62 и 63 соответственно. На нечетных строках во время чтения схема 66 сравнения (фиг.З) вырабатывает сигнал при равенстве кодов в счетчике 62 и регистре 64. Этот сигнал закрывает вентиль 57. Таким образом, из блоков памятей считывается столько кодов, сколько их было записано в цикле записи. Аналогичные действия выполняются на четных строках.

В конце нулевой строки из первого блока памяти 8 строк будет считан код 2, который по цепи 31 поступит в блок 9 анализа и на входы регистров 10 и П (фиг.1) . Б это время импульс конца строки (цепь 26) через элементы 87 задержки и ИЛИ 84 вырабатывает сигнал (цепь 33, фиг.5) приема кода в регистр 10 (фиг.1} , к куда записьтается координата начала трека, т.е. код 2.

На первой строке начнет работать блок 9 анализа.

Схема 72 сравнения (фиг.5) постепенно сравнивает код счетчика 3 столбцов (цепь 25) и код на выходных шинах памяти 8 строк (цепь 31) .

На втором столбце схема 72 сравнения вырабатьшает сигнал равенства кодов (цепь 28), Этот сигнал по счетному входу установит триггер 73 ширины трека в состояние единицы, а также запустит Цикл чтения в первых блоках памятей 8, 16 и 17. Из ячейки с адресом 1 первого блока памяти 8 строк будет считан код 4.

По переднему фронту сигнала с f триггера 73 одновибратор 74 сформирует сигнал (цепь 37) приема кода в регистр 11 и счетчик 18 длины трека (фиг.1). Б регистр 11 будет записан код конца трека, т.е. код 4, а в счетчик 18 длины трека - код О. На третьем стобце по видеоимпульсу (цепь 20) сработает вентиль 78, сигнал с которого установит в 1 тригг

55976 10

гер 80 связности треков. По переднему фронту этого триггера одновибратор

81 сформирует сигнал (шина 38), по

которому код в счетчике 18 длины 5 треков (фиг.1) увеличится на 1, т.е. в счетчике установится код 1. Код счетчика 18 длины треков (шина 43) постоянно сравнивается с константой 1 (цепь 44. фиг.7). Во О время равенства этих кодов из блока 13 сравнения (фиг.1) по шинам 32 в блок 9 анализа поступает сигнал, который открывает по первому входу вентиль 88 (фиг.5). 15 На четвертом столбце по сигналу схемы 72 сравнения (фиг.5) триггер 73 будет сброшен. Цикл чтения от этого сигнала не будет запущен, так как на нулевой строке в первьй блок памя- 20 ти 8 строк было записано только два кода.

Запись на первой строке будет производиться во вторые блоки памя25 тей 8, 16 и 17. На третьем столбце по сигналу начала трека во второй блок памяти 8 строк по нулевому адресу будет записан код 3 (содержимое записи по зтому адресу во вторых

30 блоках памятей 16 и 17 значение не имеет).

На пятом столбце по сигналу конца трека (цепь 24) во второй блок памяти 8 строк по адресу 1 будет записан код 5, а во второй блок памяти 17 признаков треков по этому адресу будет записана едини- ца. Сигнал конца трека (цепь 24, фиг.5) через вентиль 82 и элемент . ИЛИ 76 сбросит триггер 80, через вентиль 88 выработает строб (цепь 34J выходных ключей регистров 7, 10 и 11 (фиг.1). Лоэтому в первую ячейку вто- ., рого блока памяти 16 начала треков из регистров 7, 10 и 11 будут записаны коды О,2 4.

40

Выходной сигнал элемента И 82 (фиг.5) через элемент 85 задержки и

схему ИЛИ 91 сбросит счетчик 18 длины треков. На последующих столбцах первой строки во второй блок памяти 8 строк в последовательные ячейки, начиная с адреса 2, будут записаны коды 8, 10, 13,15. В соответствуюш,ие адреса вторых блоков памятей 16 и 17 будут записаны нулевые коды.

11

Ha последующих строках рассматривают работу цепей, выполняющих прослеживание треков.

На второй строке, третьем столбце из вторых блоков памятей по адресу 1 будут считаны коды: в регисре памяти 8 строк - код 5, в pei- гистре памяти 16 начало треков - коды О, 2, А, в счетчике 18 длины треков - код 1.

На четвертом столбце содержимое счетчика 18 длины треЛов (фиг.П увеличится на единицу, т.е в нем установится код 2.

Блок 13 сравнения (фиг.1) вырабатывает сигнал Код счетчика длинь трека больше единицы, который по шине 32 откроет по первому входу вентиль 18 (Лиг.5).

На пятом столбце по сигналу схемы 72 сравнения (цепь 28) будет запущен цикл чтения по адресу 2 из втрых блоков памятей 8, 16 и 17. На выходных гаинах памяти 8 строк установится код (8) начала второго трека. В регистрах памятей 16 и 17 коды не изменятся, так как сигнал приема в эти регистры в этом случае не вырабатывается. На шестом столбце сигнал конца трека (цепь 24) через элементы И 82 и 89 (фиг.5) вырабатывает строб ( цепь 35) выходных ключей памяти 16 начала треков. Поэтому в этом цикле записи в первую ячейку первого блока памяти I6 будут из выходного регистра этой памяти переписаны координаты начала трека, т.е. коды О, 2, 4. В первую ячейку первого блока памяти 17 будет записан код 2 длины трека. Таким образом в процессе

прослеживания осуществляется при.

вязка трека к своим признакам. Сигнал конца трека через элементы И 82, задержки 85, ИЛИ 84 вырабатьшает строб (цепь 33) приема в регистр 10 (фиг.1), а через элменты И 82, задержки 85, ИЛИ 91 - сигнал (гаины 38) установки нуля счетчика 18 длины трека.

rfa 7 - 17 столбцах второй строки и 1 - 7 столбцах третьей прослеживание треков будет продолжено. На 14 столбце второй строки в пятую ячейку первого блока памяти 16 начала треков будут записаны коды начала третьего трека, т.е. Г , 13, 15. На 8 столбце третьей строки

10

20

255976- 12

триггер 73 ширины трека (фиг.5) будет установлен в единичное состояние.

Так как между восьмым и десятым J стобцами видеосигнала нет то триггер 80 связности треков останется в нулевом положении.

Предположим, что в регистр 98 эталона блока 13 сравнения (фиг.7) записан код 1. Следовательно, к моменту 10 столбца, когда триггер 73 ширины трека будет сбро- гаен.(фиг.5), блок 13 сравнения не выработает сигнал Счетчик 5 длины трека больше эталона и вентиль 90 будет закрыт. Одновибратор 79 сформирует импульс, который через элементы И 83, задержки 86 подготовит устройство для анализа следующего трека.

Таким образом, по результату сравнения вычисленной длины трека с заданной осуществляется фильтрация помех. Координаты помехи в память не записываются.

Координаты отфильтрованных треков записываются следующим образом.

На четвертой строке к моменту 13-го столбца в регистрах устройства (фиг.1) будут храниться: в регистре 7 - код (3) номера преды- . дущей строки, регистрах 10 и 11 - коды (II и 13) начала и конца трека на предьщущей строке соответственно, в регистрах памяти 16 начала трека - коды (1, 13, 15) начала трека в матрице. Блок 13 срав-. нения выработает сигнал Счетчик длины трека больше эталона, который откроет вентиль 90 (фиг.5). На 13-м столбце импульс одновибратора 79 через элементы И 83 и 90 вырабатьгаает сигнал (цепь 36), который поступит в блок 14 управления памятью координат треков.

Этим сигнал (фиг.6) через элемент ИЛИ 92 увеличит код счетчика 93 на единицу, через элементы 94 задержки, ИЛИ 97 запустить (шины 39) цикл записи в памяти 19 координат треков.

25

30

35

40

45

50

Одновременно, выходной сигнал элемента 94 задержки по цепи 41 через элемент ИЛИ 15 (фиг.1) открывает выходные ключи памяти 16 начала треков. В память 19 координат треков по адресу счетчика 23 блока 14 записываются координаты начала трека в матрице.

Выходной сигнал элемента 34 задержки (фиг.6) через элемент 95 задержки поступит на вход элементов 96 задержки и ИЛИ 92. Код счетчика 93 увеличивается va единицу, а сигнал с элемента 96 задержки открывает выходные ключи регистров 7, 10 и 11 и запускает следующий цикл записи в памяти 10 координат треков.

Координаты конца трека в матрице записываются в следующую ячейку памяти 19.

В нашем случае в две последовательные ячейки памяти 19 будут записаны коды: 1, 13, 15, 11, 3, 13.

На пятой строке, на 8-м столбце аналогичным образом в память 19 в следующие две ячейки будут записаны коды О, 2, 4, 6, 8.

Таким образом, к концу считывания картины в памяти 19 координат треков в последовательных ячейках будуь храниться коды: 1, 13, 3, 11, О, 2, 4, 6, 8, которые являются координатами начала и конца двух треков в матрице.

Разделить треки и помехи можно и по признаку суммарного числа элементов матрицы, или площади, занимаемой тем или иным изображением, а также сочетанию признаков длина и площадь.

Блок 18 в этом случае дополнительно содержит сумматор, включенный, как и счетчик длины треков, . между входными и выходными шинами памяти 17 признаков треков. При этом на вход одного из слагаемых младшего разряда сумматора подан - видеоимпульс (цепь 20). На вход установки нуля подключен элемент ИЛИ, на первьй вход которого подан кадровый импульс (цепь 22), а на второй - через элемент задержки импульс конца трека (цепь 24).

Вычисление площади изображения осуществляется следующим образом. I

На каждой строке сумматор последовательно вычисляет ширину сечения T pejcoB путем подсчета числа видеосигналов между импульсами конца трека. В процессе.прослеживания по сигналу приема (цепь 37) в сумматор поступает код из.памяти 17 признаков треков, который складьгоается с кодом ширины трека на текущей строке. Так образуется сумма сечений на последовательных строках. Запоминание координат начала и прослеживания изображения осуществляется по

описанному способу. Если фильтрация выполняется только по признаку площадь, то счетчик длины трека может состоять из одного разряда и триггера, на котором запоминается

условие: Длина трека больше едини- цы.

Памяти 8, 16 и 17 строк, начала и признаков треков могут быть реализованы на основе специально организованной магазинной памяти типа очередь.

Преимущество такого технического решения заключается в том, что блок 4 управления памятью строк существенно упрощается (счетчики 62

и 63, регистры 64 и 65 и схемы сравнения 66, 67 не нужны). Однако в случае обработки изображения с большим количеством помех, которые

отличаются от треков щириной сечения на строке, блок 4 управления памятью строк позволяет организог вать фильтрацию по признаку ширина трека на строке.

В качестве памяти 19 координат треков также может быть использована магазинная память типа очередь. При этом в блоке 14 управления па памятью координат треков счетчик

адресов не требуется.

Однако микросхемы адресуемых памятей имеют значительйо большую степень интеграции, чем аналогичные компоненты в безадресном исполнении.

Поэтому выбор типа памяти 19 координат треков существенно зависит от требуемого объема.

45

Формула изобретения

г. Устройство для определения координат треков, содержащее блч;к ввода, блок вьщеления треков, счетчики столбцов и строк, блоки анали- .

за и сравнения, счетчик длины тре- кОв и блок управления памятью координат треков, причем выходы блока ввода соединены: первый - с первыми входами блоков выделения треков и

анализа, второй - с вторым входом блока выделения треков и первым входом счетчика столбцов, третий - с первым входом счетчика строк и вто15

рым входом счетчика столбцов, первый выход которого соединен с вторым входом блока анализа, а выход счетчика длины треков соединен с первым входом блока сравнения, второй вход которого является входом кода эталона, шины первого выхода блока управления памятью координат треков соединены с соответствующими первыми входа

ми памяти координат треков, о т л и- ч ающееся тем, что, с целью расширения области пр именения и увеличения производительности путем обработки координат нескольких треков на каждой строке исследуемой картины, в него введены памяти строк, начала треков и признаков треков, каждая из которых состоит из двух блоков памяти, выходы которых подключены к мультиплексору, причем в память строк включен регистр, соединенный входами с мультиплексором памяти строк, а в память начала треков включен регистр с выходными ключами, соединенный входами с мультиплексором памяти начала треков, блок управления памятью строк, три регистра с выходными клю чами, два элемента ИЛИ и элемент задержки, причем третий выход блока ввода соединен с первым входом блока управления памятью строк, к первьм и вторым выходным шинам которого параллельно подключены соответственно первые и вторые входные щины памятей

строк, начала треков и признаков тре-35 венно, выход первого элемента ИЛИ ков, первый выход блока вьщеления

соединен с третьими : входами регис ров , а выход второго элемента ИЛИ с шестым входом памяти начала треков, выходные шины которой соедине

треков соединен с вторым входом блока управления памятью строк, третий вход которого соединен с вторым выходом блока выделения треков и третьим входом блока анализа, четвертый вход которого соединен с третьим выходом блока ввода, третий вход памяти строк соединен с первым выходом счетчика столбцов, а выходные шины этой памяти подключены к первым входам первого и второго регистров и пятым входам блока анализа, шестой вход которого соединен с вторым вы0

Ю 1555976,6

ходом счетчика столбцов, первым входом третьего регистра, четвертым входом блока управления памятью строк и через элемент задержки с вто- 5 рым входом счетчика строк, выход которого соединен с вторым входом третьего регистра, причем первый разряд счетчика строк соединен также с четвертыми входами памятей строк, начала треков и признаков треков, шестым входом блока управления памятью строк и седьмым входом блока анализа, на восьмые входы которого подключены выходы блока сравнения, а выходы блока анализа подклю чены: первый - к пятому входу блока управления памятью строк, второй - к второму входу первого регистра, третий и четвертый - соответственно к первым входам первого и второго элементов ИЛИ, пятый - к входу блока управления памятью координат треков, шестой - к первому входу счетчика длины треков, пятому входу памяти начала треков и второму входу второго регистра,.седьмые - к вторым входам счетчика длины треков, выход которого соединен с третьим входом памяти признаков треков, а третий вход - с выходом этой памяти , второй и третий выходы блока управления памятью координат треков соединены с вторыми входами первого и второго элементов ИЛИ соответст5

0

венно, выход первого элемента ИЛИ

соединен с третьими : входами регистров , а выход второго элемента ИЛИ - с шестым входом памяти начала треков, выходные шины которой соединены

с третьими входными шинами этой же памяти и вторыми входными шинами памяти координат треков, а также ответствуюгчими выходными шинами . регистров.

2. Устройство по п.1, о т л и - чающееся тем, что блоки памятей строк, начала треков и признаков треков вьтолнены на основе магазинной памяти типа Очередь.

х

Z7

7T

J lffKf

jfjemxt

v SsSSSuL

JC

(риг..

(5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распознавания треков частиц | 1982 |

|

SU1059586A2 |

| Устройство для распознавания трековчАСТиц | 1979 |

|

SU845165A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2017 |

|

RU2727555C2 |

| УСТРОЙСТВО ПЛАНИРОВАНИЯ ТОПОЛОГИИ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМ | 2012 |

|

RU2530275C2 |

| Устройство для отображения информации | 1983 |

|

SU1124374A1 |

| Устройство для считывания графической информации | 1988 |

|

SU1536413A1 |

| Устройство для ввода цифровой информации | 1990 |

|

SU1698884A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Микропрограммное устройство управления | 1985 |

|

SU1354192A1 |

Изобретение относится к ядерной электронике и может быть применено для определения координат линейных треков и прослеживания треков частиц при обработке данных эксперимента в ядерной физике. Цель изобретения заключается в расширении облас-L- -.-- - . а . ти применения и повьппении производительности устройства путем обработки координат нескольких треков на каждой строке разложения исследуемой картины. Устройство для определения координат треков представляет собой блок ввода,, подсоединенный к специализированному вычислительному устройству. Введенные в устройство новые элементы памяти совместно с новыми блоками управления позволяют поставить в соответствие каждому треку его признак в процессе прослеживания треков, что позволяет эффективно обрабатывать произвольное количество трексзв на исследуемом снимке. Использование сумматора наряду со счетчиком длины треков позволяет Осуществлять фильтрацию треков от помех как по длине, так и по площади . 1 3.п. ф-лы, 8 ип. (Л С -ч f т сл со Од

Заказ 4820/46 Тираж 728Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

фиг. 6

| Круппов В.Е., .Федотов О.П | |||

| Приборы для распознавания элементов треков - ПРЭТ | |||

| М., 1979, ИТЭФ-39 | |||

| Устройство для определения координат треков | 1980 |

|

SU854164A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-09-07—Публикация

1985-03-18—Подача