Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах микропроцессорных систем.

Целью изобретения является упрощение устройства и расширение функциональных возможностей за счет независимости работы от типа системного контроллера.

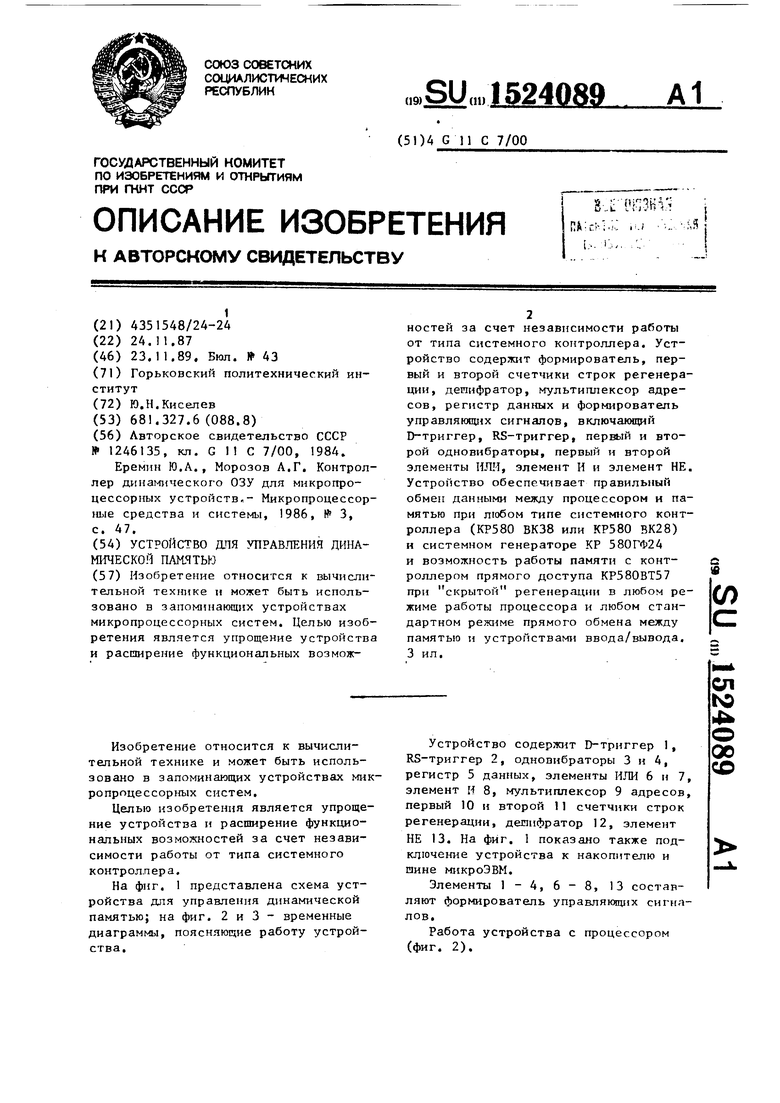

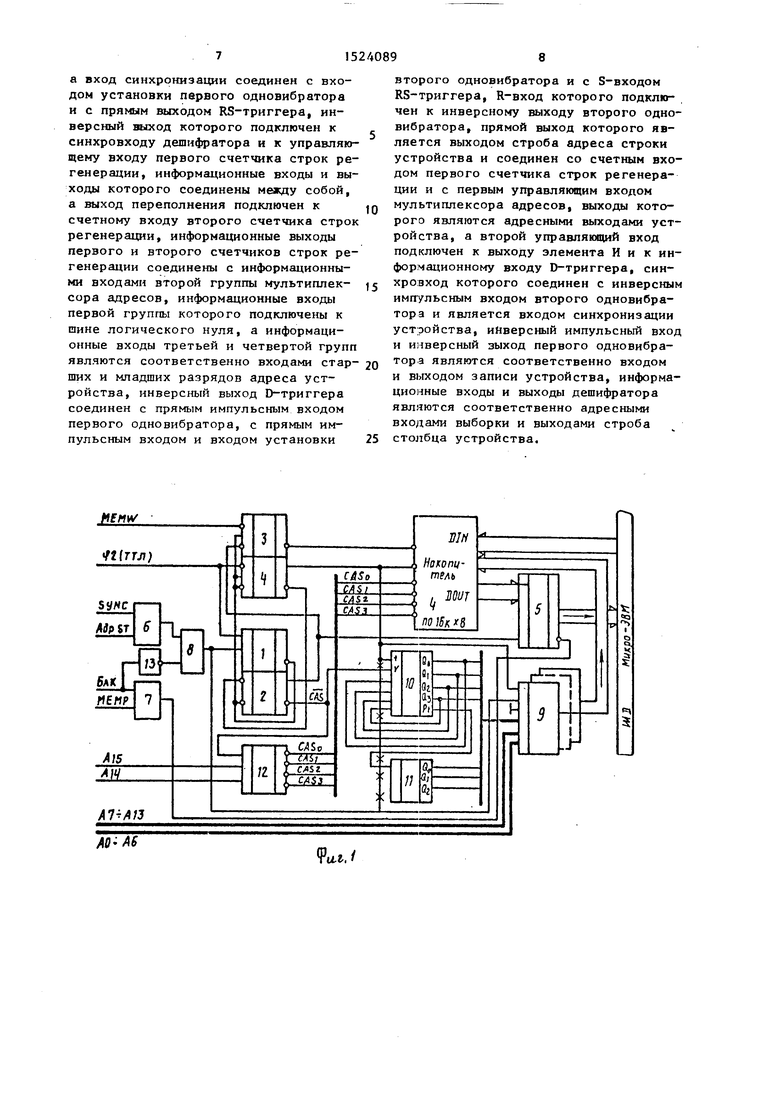

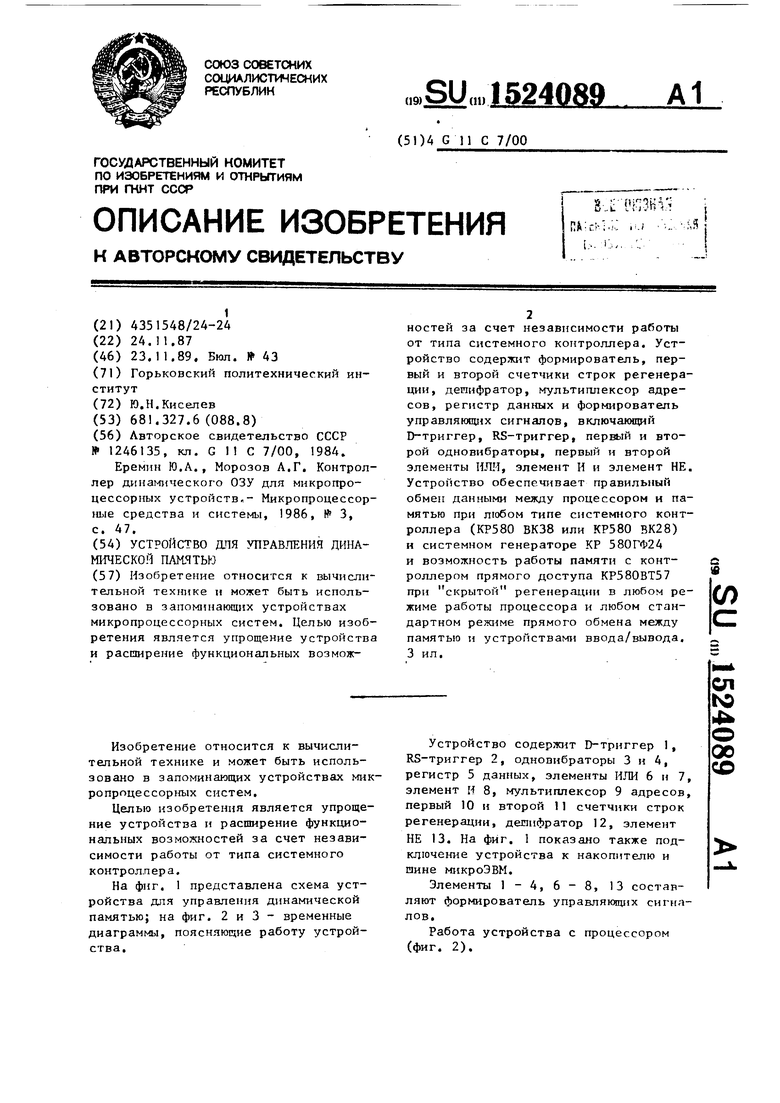

На фиг. 1 представлена схема устройства для управления динамической памятью; на фиг. 2 и 3 - временные диаграммы, поясняющие работу устройства.

Устройство содержит D-триггер 1, RS-триггер 2, одновибраторы 3 и 4, регистр 5 данных, элементы ИЛИ 6 и 7, элемент И 8, мультиплексор 9 адресов, первый 10 и второй 11 счетчики строк регенерации, дешифратор 12, элемент НЕ 13. На фиг. 1 показано также подключение устройства к накопителю и шине микроэвм.

Элементы 1 - 4, 6-8, 13 составляют формирователь управлякяцих сигналов.

Работа устройства с процессором (фиг. 2).

СП

ю

4

О 00

со

В отсутствие сигнала SYNC процес-, сора по отрицательному фронту сигнала ч периодически (в каждом такте) запускается одновибратор 4, формируя паузу между сигналами RAS накопителя. Дпительпость паузы между сигиапами RAS устапавливается в соответствии с техническими параметрами БИС ЗУ так, чтобы между началом очередного сигнала RAS и положительным фронтом ближайшего сигнала (( имелся временной интервал, который требуется по ТУ между сигналами RAS и CAS.

Триггеры 1 и 2, одновибратор 3 на-. писи кода по сигналу CAS.

20

В начале любого обращения к памяти накопитель находится в режиме выдачу данных в регистр 5 по сигналу CAS. Наличие регистра 5 позволяет ограничиться одним циклом обращения к накопителю по чтению, даже если режим чтения в процессоре продолжается бесконечно долго. Выдача данных из регистра 5 на шину данных микроЭВМ разходятся в исходном,состоянии, мультиплексор 9 передает на адресные входы накопителя код адреса со счетчиков 10 и 11 строк регенерации. Режим ре- геперацни последовательных строк на- копитешя продолжается до появления сигнала SYNC (начало цикла) процессора.

Сигнал SYNC, поступая на мультиплексор 9 в первом такте цикла, обес-25 решается только сигналом IffiMR при от- печивает в паузе между сигналами RAS подключение к адресным входам накопителя адресов АО-А6, образующих адрес строки ячейки памяти, к которой обращается процессор. Кроме того, сигнал SYNC формируется триггером 1 во втором такте процессорного цикла по положительному фронту Lf, вызывая блокировку запуска одновибратора 4 во втором такте. Это приводит к увели30

чению длительности сигнала RAS на время обращения к накопителю со сто- рО1Ш процессора.

Начало сигнала RAS при наличии сигнала SYNC обеспечивает передачу гультиплексором 9 кода адреса столбца А7-А13 ячейки памяти. Срабатывание триггера 1 вызывает переключение триггера 2, который фop иpyeт сигнал CAS - сигнал фиксации адреса столбца в накопителе. Поскольку сигнал SYNC првцессора заканчивается во втором такте процессорного цикла, триггер 1 вернется в исходное состоя}ше по по40

45

сутствии сигнала БЛК (блокировки обращения в памяти).

Сигнал записи в накопитель формируется одновибратором 3 при наличии сигнала MEMl J. Запуск одновибратора 3 разрешается в течение длительного сиг1-:ала CAS в момент возврата триггера 1 в исходное состояние. Длительность сигнала № определяется длительностью положительной полуволны сигнала i-fj (не менее 200 не, что соответ- ст.вует ТУ на БИС динамической памяти серии К565) при условии, что хронирующая цепь одновибратора 3 рассчитана на формирование несколько большей длительности. Окончание сигнала Л совпадает с концом сигнала CAS.

Таким образом при выдаче данных из процессора в память в накопителе вна- чалЕ - выполняется чтение по требуемому .су, а затем запись данных процессора по тому же адресу (использован режим БИС ЗУ Считывание - модификация - запись).

Поскольку моменты начала формироложительному фронту Lf в такте, кото-

рый следует за вторым тактом (типовой 50 дания сигналов MEMR и МЕМС для нор- третий такт, либо такт ожидания примальной работы управления и выполнения правильного обмена данными между процессором и памятью не важны, схема успешно работает при различных стандартных системных контроллерах, При необходимости организаций банотсутствии сигнала READY на входе процессора), и снимает блокировку запуска одновибратора 4 и сигнал установки триггера 2 в состояние 1. Таким образом, в следующем такте Л1о отрицательному фронту сигнала if запускается одновибратор 4 и триг55

ков памяти сигнал CAS, формируемый триггером 2, должен переключаться на

гер 2 Боэврадается в исходное состояние, т.е. заканчивается формирование сигналов RAS и CAS. Следующий сигнал RAS вызывает уже цикл регенерации накопителя.

Поскольку счетчик регенерации ин- крементируется по концу сигнала RAS, а в цикле обращения к накопителю строка, код которой был сформирован в счетчике к началу обращения, не была регенерирована, увеличение содержимого счетчиков 10 и 11 блокируется переводом счетчика 10 в режим переза

В начале любого обращения к памяти накопитель находится в режиме выдачу данных в регистр 5 по сигналу CAS. Наличие регистра 5 позволяет ограничиться одним циклом обращения к накопителю по чтению, даже если режим чтения в процессоре продолжается бесконечно долго. Выдача данных из регистра 5 на шину данных микроЭВМ разрешается только сигналом IffiMR при от-

решается только сигналом IffiMR при от-

сутствии сигнала БЛК (блокировки обращения в памяти).

Сигнал записи в накопитель формируется одновибратором 3 при наличии сигнала MEMl J. Запуск одновибратора 3 разрешается в течение длительного сиг1-:ала CAS в момент возврата триггера 1 в исходное состояние. Длительность сигнала № определяется длительностью положительной полуволны сигнала i-fj (не менее 200 не, что соответ- ст.вует ТУ на БИС динамической памяти серии К565) при условии, что хронирующая цепь одновибратора 3 рассчитана на формирование несколько большей длительности. Окончание сигнала Л совпадает с концом сигнала CAS.

Таким образом при выдаче данных из процессора в память в накопителе вна- чалЕ - выполняется чтение по требуемому .су, а затем запись данных процессора по тому же адресу (использован режим БИС ЗУ Считывание - модификация - запись).

Поскольку моменты начала формиро

дания сигналов MEMR и МЕМС для нор- мальной работы управления и выков памяти сигнал CAS, формируемый триггером 2, должен переключаться на

1-

5152

тот или иной банк (страницу) накопителя кодом старших разрядов адресной шины Роль этого переключателя в схеме (фиг. 2) выполняет дешифратор 12, Блокировка обращения к памяти достигается запретом формирования сигнала на выходе элемента 8 и запретом чтения состояния регистра 5. Сигнал блокировки обращения к памяти должен быть подан не позднее чем за 100 не до начала сигнала RAS в цикле обращения к памяти.

Предлагаемая схема управления обеспечивает скрытую регенерацию последовательных строк накопителя динамического типа с темпом одна строка за один цикл процессора.

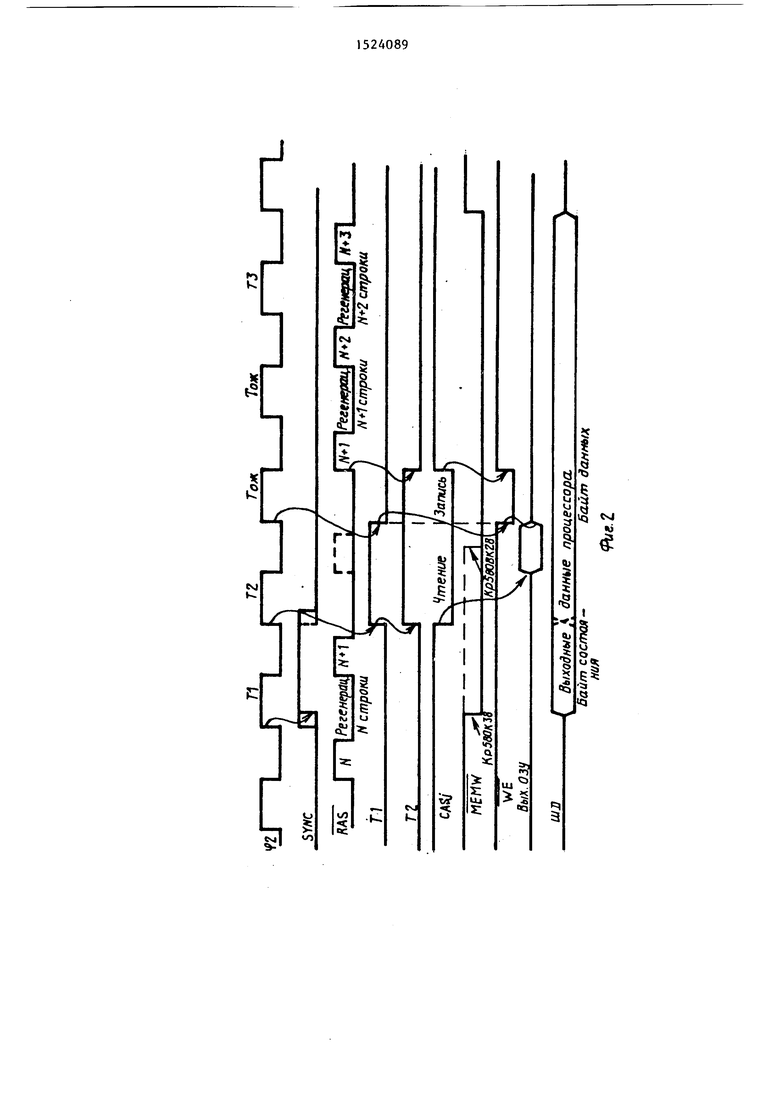

Работа устройства управления в режиме прямого доступа к памяти под уп равлением стандартного контроллера ПД типа КР580ВТ57 (фиг..3).

Переход процессора в режим захвата шин происходит в конце такта ТЗ процессорного цикла, когда обмен данными между процессором и памят ыо или регистром внешнего устройства завершен. Передача управления шинами микроэвм контроллеру прямого доступа КР580ВТ57 вызывает в Нем формирование циклов ПД, подобных циклу считывания управления памятью и регистрации ввода - вывода. В предлагаемом устройстве управления идентификация цикла прямого доступа вызывается сигналом ЛБЕ.ST. - стробом запоминания старшего байта адреса ячейки памяти, к которой обращается контроллер ПД, Обращение к ОЗУ происходит также как при взаимодействии с процессором при условии программирования БИС ПД на режим удлиненной записи в память. Невыполнение этого условия (обычная запись) может привести к пропуску сигнала MEMTv за счет его значетельного запаздывания по отношению к моменту анализа этого сигнала в узле управления (по ТУ БИС КР 580ВТ57 задержка сигнала относительно начала такта S3 может составлять 250 не).

. В циклах ПД по чтению ОЗУ режим удлиненной записи в контроллере ПД может не использоваться. На фиг. 3 показано взаимодействие устройства управления и контроллера прямого доступа в регкимах чтения памяти и записи в память. Также как при работе с процессором в режиме ПД выполняется

5

10

15

20

25

скрытая регенерация памяти и в тактах ожидания.

Таким образом, в предлагаемом устройстве управления идентификация обращения к памяти со стороны процессора сигналом SYNC позволяет использовать это устройство при любом типе системного контроллера КР580ВК38 или КР580ВК28; тактовой последовательностью является системный сигнал, вырабатываемый стандартным систеьшым генератором КР580ГФ24.

Применение запоминающего регистра на выходе накопителя позволяет осуществить правильньй обмен данными между памятью и процессором в автоматическом режиме и режиме ожидания,а также между памятью ивнешним устройством в режиме прямого доступа под управлением стандартного контроллера ПД типа КР580ВК57,

Использование режима Чтение-модификация-запись в накопителе динамического типа упрощает схему управления .

Формула изобретения

0

5

5

0

5

0

Устройство для управления ческой памятью, содержащее формирователь управляющих сигналов, мультипликатор адресов, дешифратор, первый счетчик строк регенерации, отличающееся тем, что, с целью упрощения устройства и расширения функциональных возможностей за счет обеспечения независимости работы от типа системного контроллера, в устройство введен регистр данных, второй счетчик строк регенерации, а формирователь управляющих сигналов содержит D-триггер, P.S-триггер, первый и второй одновибраторы, первый и второй элементы ИЛИ, элемент И и элемент ПЕ, причем входы первого элемента ИЛИ являются входами синхронизации и строба адреса устройства, а выход соединен с первым входом элемента И, второй вход которого подключен к выходу элемента ПЕ, вход которого является входом блокировки устройства и соединен с первым входом второго элемента ИЛИ, второй вход которого является входом чтения устройства, а выход подключен к входу выборки регистра данных, информационные входы и выходы которого являются соответственно информационными входами и выходами устройства.

а вход синхронизации соединен с входом установки первого одновибратора и с прямым выходом RS-триггера, инверсный выход которого подключен к синхровходу дешифратора и к управляющему входу первого счетчика строк регенерации, информационные входы и выходы которого соединены между собой, а выход переполнения подключен к счетному входу второго счетчика строк регенерации, информационные выходы первого и второго счетчиков строк регенерации соединены с информгщионны- ми входами второй группы мультиплексора адресов, информационные входы первой группы которого подключены к шине логического нуля, а информационные входы третьей и четвертой групп являются соответственно входами стар- ших и младших разрядов адреса устройства, инверсный выход D-триггера соединен с прямым импульсным входом первого одновибратора, с прямым импульсным входом и входом установки

второго одновибратора и с S-входом RS-триггера, R-вход которого подключен к инверсному выходу второго одно- вибратора, прямой выход которого является выходом строба адреса строки устройства и соединен со счетным входом первого счетчика строк регенерации и с первым управляющим входом мультиплексора адресов, выходы которого являются адресными выходами устройства, а второй управляющий вход подключен к выходу элемента И и к информационному входу D-триггера, син- хровход которого соединен с инверсным имп /льсным входом второго Одновибратора и является входом синхронизации устройства, инверсный импульсный вход и инверсный выход первого одновибратора Являются соответственно входом и выходом записи устройства, информационные входы и выходы дешифратора являются соответственно адресными входами выборки и выходами строба столбца устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления динамической памятью | 1990 |

|

SU1735858A1 |

| Динамическое оперативное запоминающее устройство | 1987 |

|

SU1499401A1 |

| Устройство для управления регенерацией в полупроводниковой динамической памяти | 1991 |

|

SU1807521A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1569905A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| Контроллер динамического оперативного запоминающего устройства | 1987 |

|

SU1442995A1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство формирования сигналов управления динамической памятью | 1989 |

|

SU1741141A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах микропроцессорных систем. Целью изобретения является упрощение устройства и расширение функциональных возможностей за счет независимости работы от типа системного контроллера. Устройство содержит формирователь, первый и второй счетчики строк регенерации, дешифратор, мультиплексор адресов, регистр данных и формирователь управляющих сигналов, включающий D-триггер, RS-триггер, первый и второй одновибраторы, первый и второй элементы ИЛИ, элемент И и элемент НЕ. Устройство обеспечивает правильный обмен данными между процессором и памятью при любом типе системного контроллера /КР580 ВК38 или КР580 ВК28/ и системном генераторе КР 580ГФ24 и возможность работы памяти с контроллером прямого доступа КР580ВТ57 при "скрытой" регенерации в любом режиме работы процессора и любом стандартном режиме прямого обмена между памятью и устройствами ввода/вывода. 3 ил.

МЕШ

АО-AS

«Pat./

I

LJ

| Устройство для регенерации информации в блоках памяти микропроцессорной системы | 1984 |

|

SU1246135A1 |

| Еремин Ю.А., Морозов А.Г | |||

| Контроллер динамического ОЗУ для микропроцессорных устройств.- Микропроцессорные средства и системы, 1986, № 3, с | |||

| Способ очищения сернокислого глинозема от железа | 1920 |

|

SU47A1 |

Авторы

Даты

1989-11-23—Публикация

1987-11-24—Подача