11

Изобретение относится к вычислительной технике и может быть использовано при построении устройств управления систолических, матричных9 конвейерных и других мультипроцессорных систем, использующих параллельную обработку информации.

Цель изобретения - расширение об - ласти применения устройства за счет реализации программируемой динамической адаптации маршрутов передачи данных.

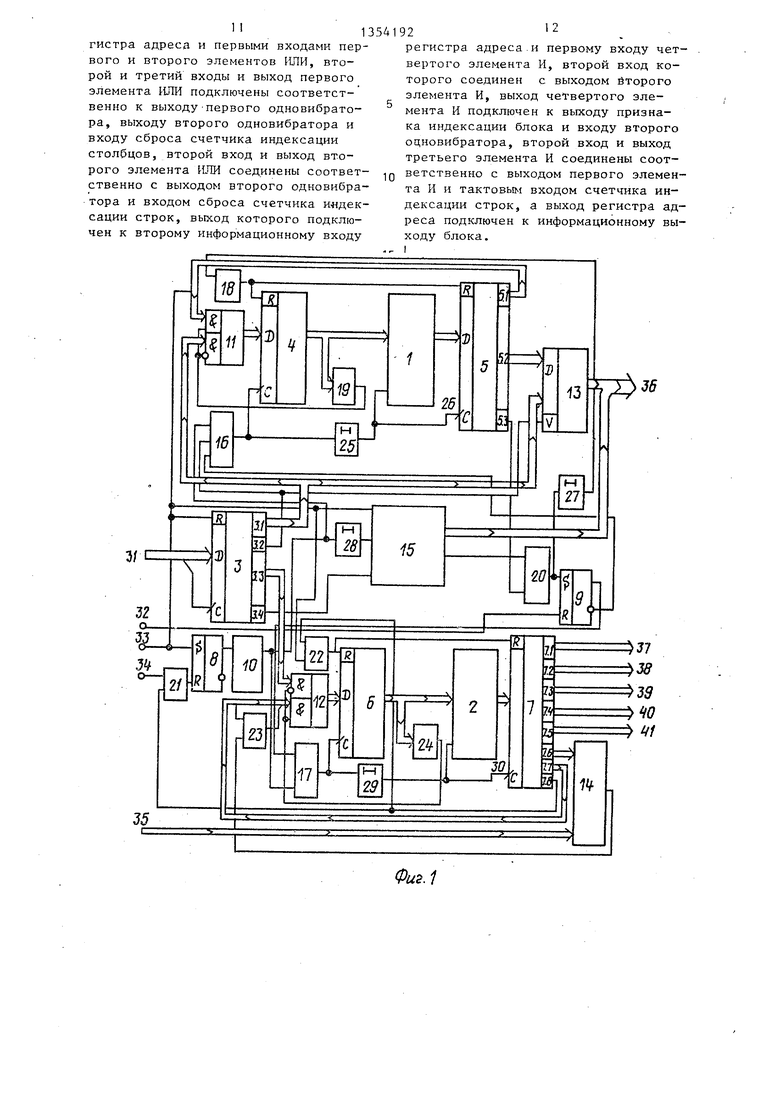

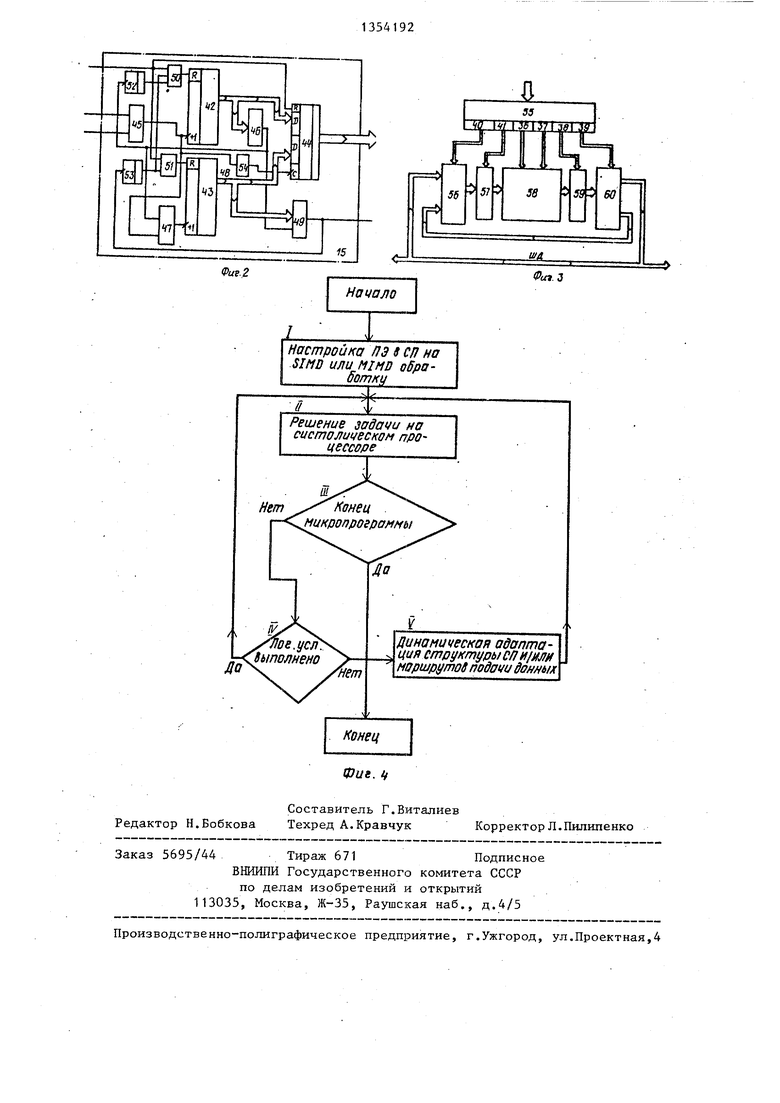

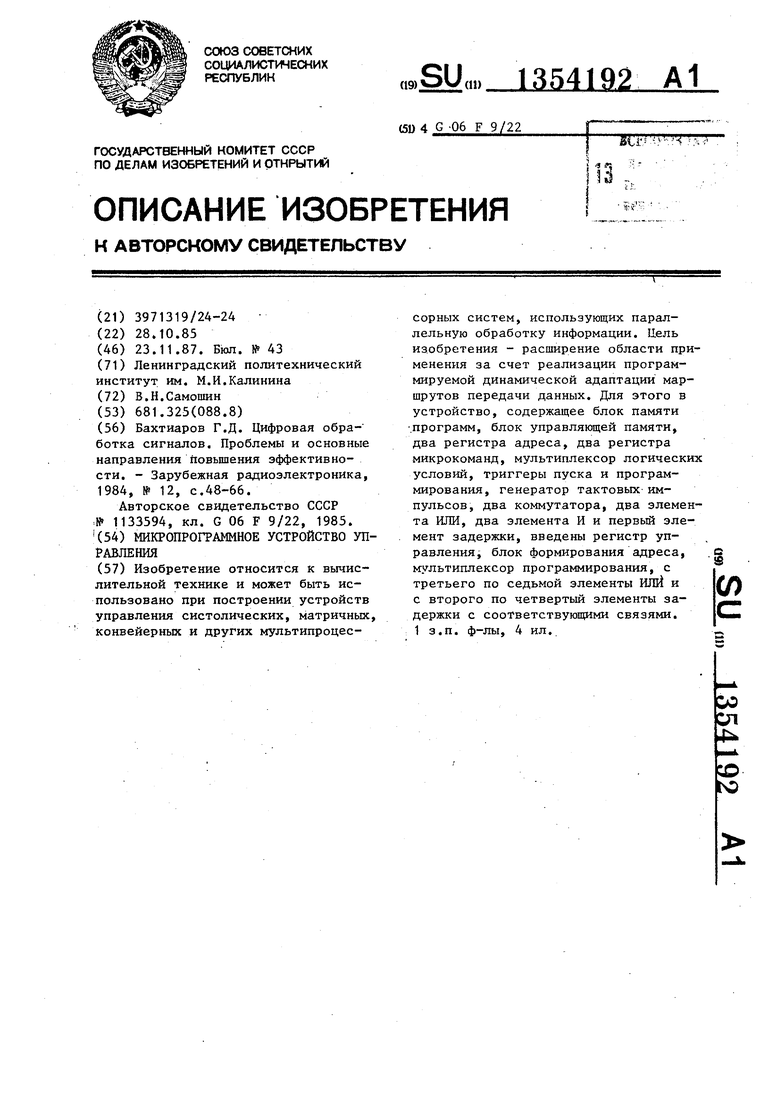

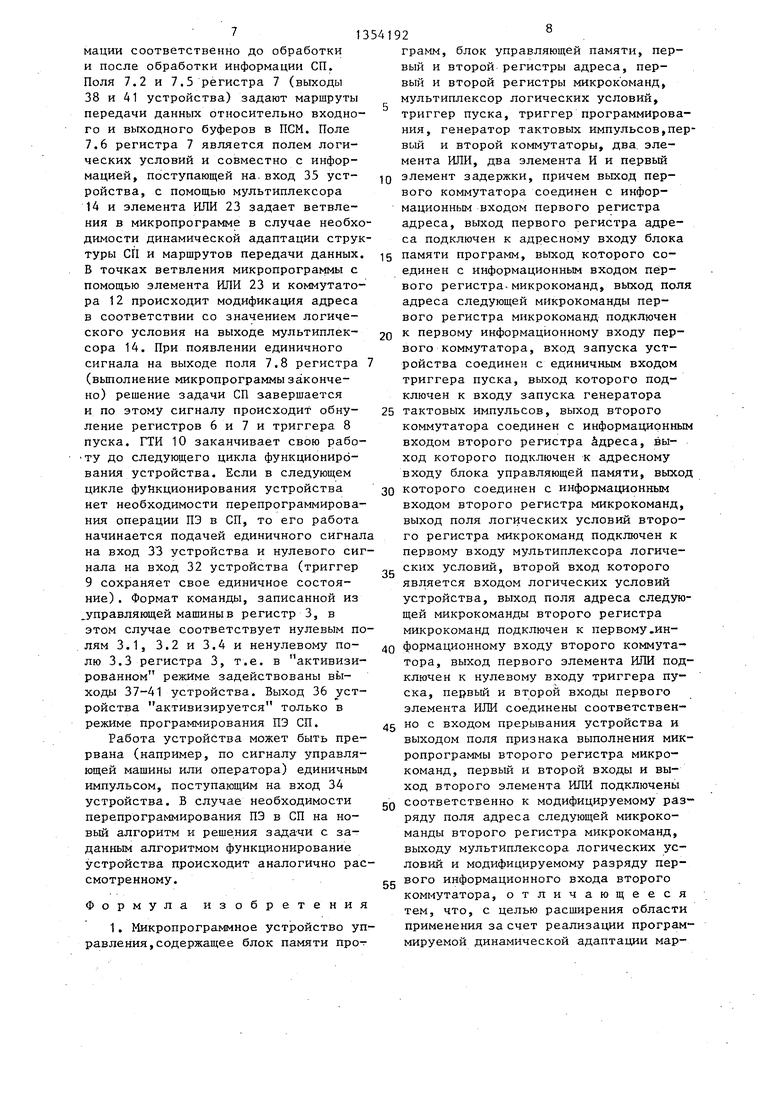

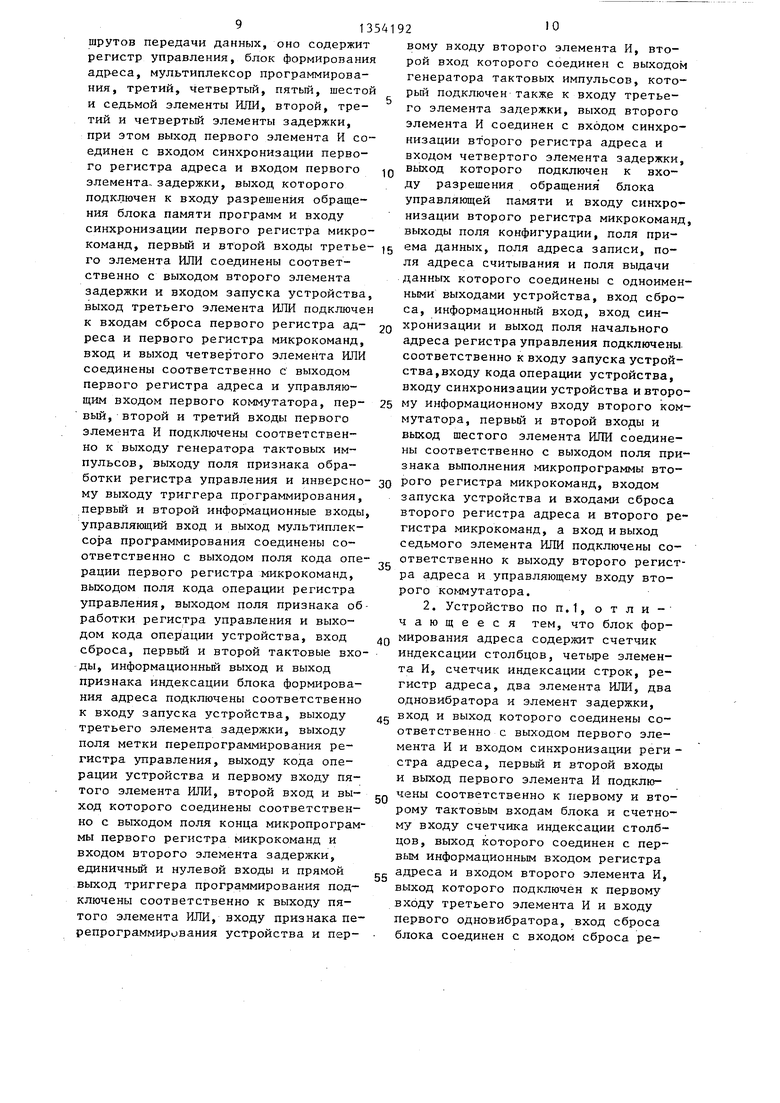

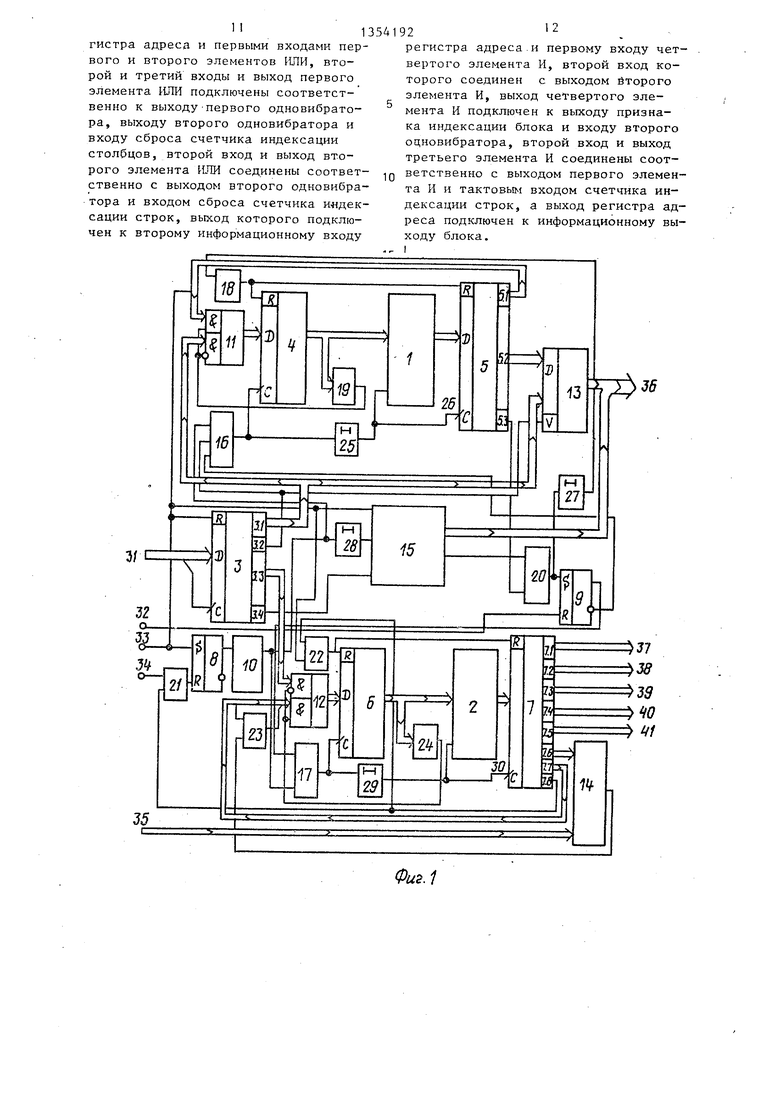

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функцио нальная схема блока формирования адреса; на фиг.З - устройство в составе систолического процессора; на фиг.4 - блок-схема алгоритме функционирования устройства.

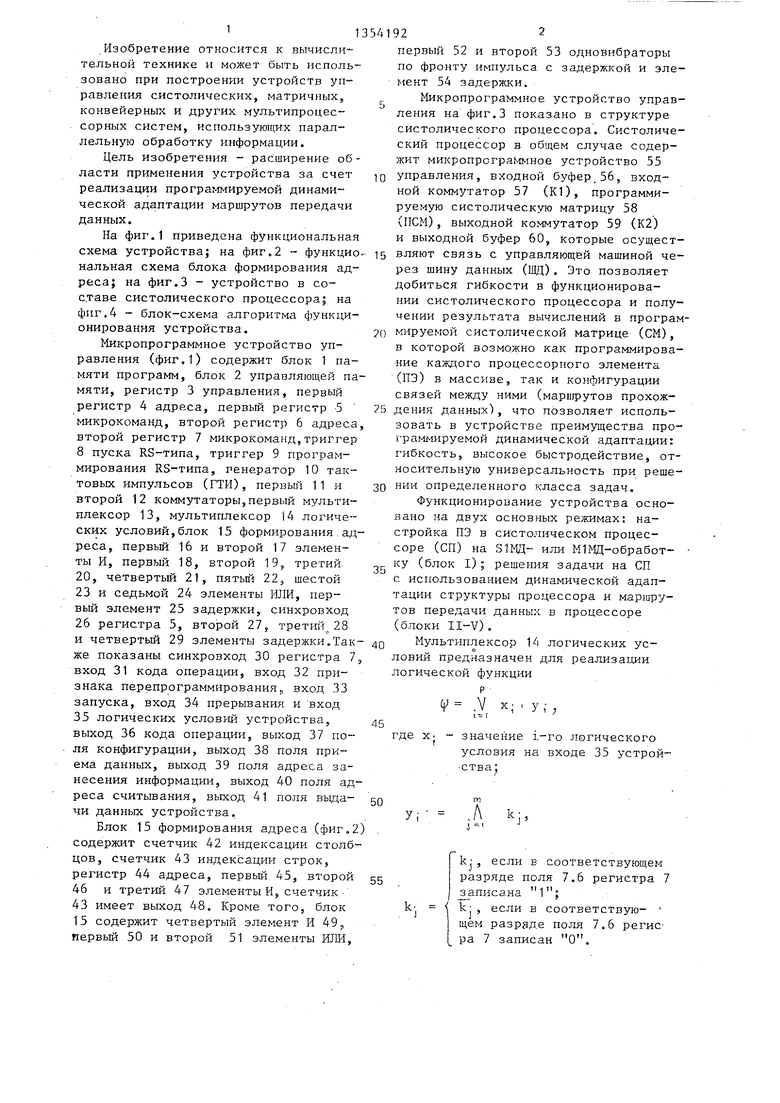

Микропрограммное устройство управления (фиг.1) содержит блок 1 памяти программ, блок 2 управляющей памяти, регистр 3 управления, первый регистр 4 адреса, первый регистр 5 микрокоманд, второй регистр 6 адреса второй регистр 7 микрокоманд,триггер 8 пуска RS-типа, триггер 9 программирования RS-типа, генератор 10 тактовых импульсов (ГТИ), первый 11 и второй 12 комь утаторы,первый мультиплексор 13, мультиплексор 14 логических условий,блок 15 формирования.адреса, первый 16 и второй 17 элементы И, первый 18, второй 19, третий 20, четвертый 21, пятьм 22, шестой 23 и седьмой 24 элементы ИЛИ, пер- вьш элемент 25 задержки, синхровход 26 регистра 5, второй 27, третий 28 и четв.ертый 29 элементы задержки.Так же показаны синхровход 30 регистра 7 вход 31 кода операции, вход 32 признака перепрограммирования,, вход 33 запуска, вход 34 прерывания и вход 35 логических условий устройства, вьпсод 36 кода операции, выход 37 поля конфигурации, выход 38 поля приема данных, выход 39 поля адреса занесения информации, выход 40 поля адреса считывания, выход 41 поля выда- чи данных устройства.

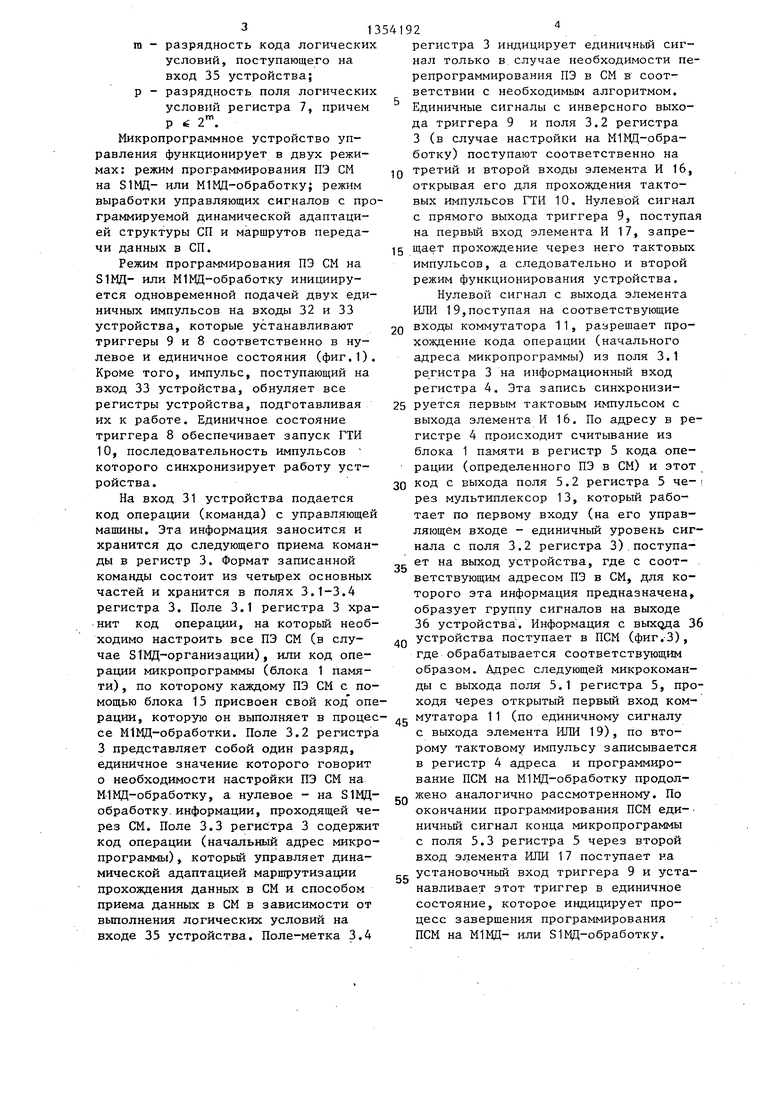

Блок 15 формирования адреса (фиг.2 содержит счетчик 42 индексации столбцов, счетчик 43 индексации строк, регистр 44 адреса, первый 45, второй 46 и третий 47 элементы И, счетчик 43 имеет выход 48. Кроме того, блок 15 содержит четвертый элемент И 49,, первый 50 и второй 51 элементы ИЛИ,

922

первый 52 и второй 53 одновибраторы по фронту импульса с задёрлской и элемент 54 задержки.

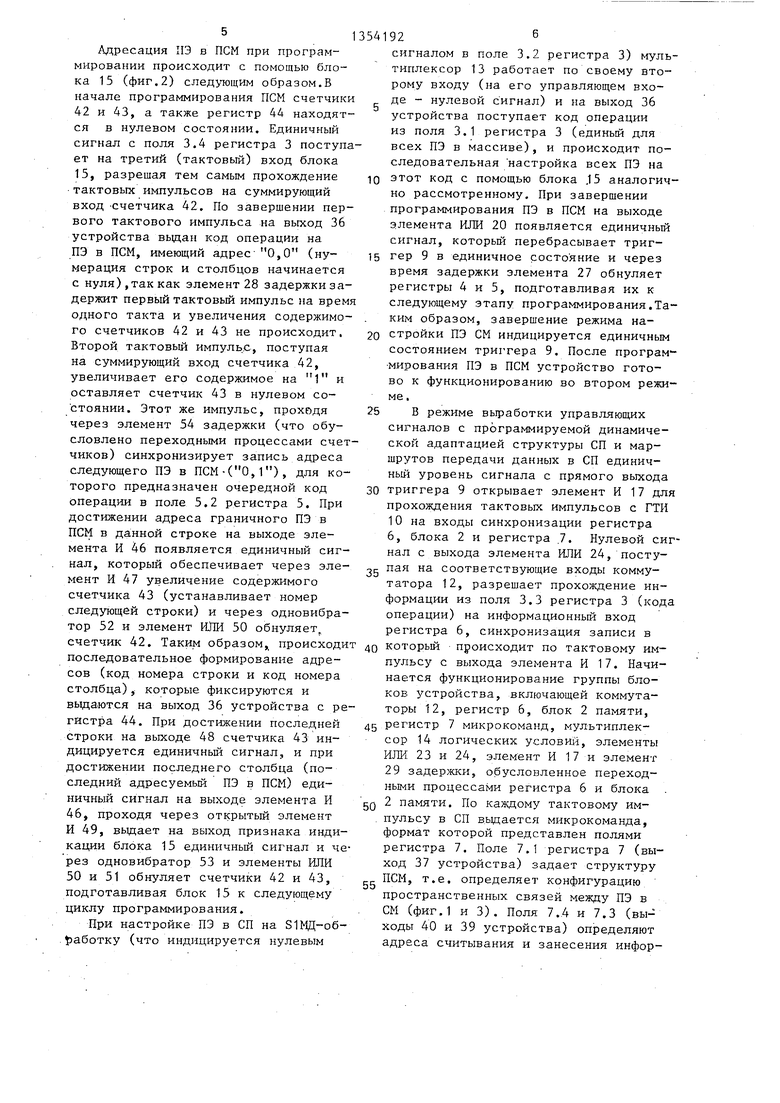

Микропрограммное устройство управления на фиг.З показано в структуре систолического процессора. Систолический процессор в общем случае содержит микропрограЬ{мное устройство 55 управления, входной буфер.56, входной коммутатор 57 (К1), программируемую систолическую матрицу 58 (ПСМ), выходной коммутатор 59 (К2) и выходной буфер 60, которые осуществляют связь с управляющей машиной через шину данных (ШД). Это позволяет добиться гибкости в функционировании систолического процессора и получении результата вычислений в программируемой систолической матрице (СМ), в которой возможно как программирование каждого процессорного элемента (ПЭ) в массиве, так и конфигурации связей между ними (марифутов прохождения данных), что позволяет использовать в устройстве преимущества программируемой динамической адаптации: гибкость, высокое быстродействие, относительную универсальность при решении определенного класса задач.

Функционирование устройства основано на двух основных режимах: настройка ПЭ в систолическом процессоре (СП) на 51МД- или М1МД-обработ- ку (блок I); решения задачи на СП с использованием динамической адаптации структуры процессора и марш-ру- тов передачи данных в процессоре (блоки II-V),

Мультиплексор 14 логических условий предназначен для реализации логической функции р

V ,V Х; , у,где х- - значение i-ro логического

условия на входе 35 устрой- ства ,

У;

.Л

kj, если в соответствующем разряде поля 7.6 регистра 7 аписана

I k:, если в соответствую- j щем разряде поля 7.6 регис ра 7 записан О.

га - разрядность кода логических условий, поступающего на вход 35 устройства;

р - разрядность поля логических условий регистра 7, причем

/1 Ш

Р 2 .

Микропрограммное устройство управления функционирует в двух режимах: режим программирования ПЭ СМ на 51МД- или М1МД-обработку; режим выработки управляющих сигналов с программируемой динамической адаптацией структуры СП и маршрутов передачи данных в СП.

Режим программирования ПЭ СМ на 51МД- или М1ВД-обработку инициируется одновременной подачей двух единичных импульсов на входы 32 и 33 устройства, которые устанавливают триггеры 9 и 8 соответственно в нулевое и единичное состояния (фиг.1). Кроме того, импульс, поступающий на вход 33 устройства, обнуляет все регистры устройства, подготавливая их к работе. Единичное состояние триггера 8 обеспечивает запуск ГТИ 10, последовательность импульсов которого синхронизирует работу устройства.

На вход 31 устройства подается код операции (команда) с управляющей машины. Эта информация заносится и хранится до следующего приема команды в регистр 3. Формат записанной команды состоит из четырех основных частей и хранится в полях 3.1-3.4 регистра 3. Поле 3.1 регистра 3 хранит код операции, на который необходимо настроить все ПЭ СМ (в случае 51МД-организации), или код операции микропрограммы (блока 1 памяти) , по которому каждому ПЭ СМ с помощью блока 15 присвоен свой код операции, которую он выполняет в процес- g мутатора 11 (по единичному сигналу

се М1МД-обработки. Поле 3.2 регистра 3 представляет собой один разряд, единичное значение которого говорит о необходимости настройки ПЭ СМ на М1МД-обработку, а нулевое - на 81МД- обработку. информации, проходящей через СМ. Поле 3.3 регистра 3 содержит код операции (начальный адрес микропрограммы) , который управляет динамической адаптацией маршрутизации прохождения данных в СМ и способом приема данных в СМ в зависимости от вьтолнения логических условий на входе 35 устройства. Поле-метка 3.4

50

с выхода элемента ИЛИ 19), по второму тактовому импульсу записываетс в регистр 4 адреса и программирование ПСМ на М1МД-обработку продолжено аналогично рассмотренному. По окончании программирования ПСМ единичньш сигнал конца микропрограммы с поля 5.3 регистра 5 через второй вход элемента ИЛИ 17 поступает на установочный вход триггера 9 и уста навливает этот триггер в единичное состояние, которое индицирует процесс завершения программирования ПСМ на М1МД- или 51МД-обработку.

5

0

регистра 3 индицирует единичный сигнал только в случае необходимости перепрограммирования ПЭ в СМ в соответствии с необходимьм алгоритмом. Единичные сигналы с инверсного выхода триггера 9 и поля 3.2 регистра 3 (в случае настройки на М1МД-обра- ботку) поступают соответственно на третий и второй входы элемента И 16, открывая его для прохождения тактовых импульсов ГТИ 10. Нулевой сигнал с прямого выхода триггера 9, поступая на первый вход элемента И 17, запрещает прохождение через него тактовых импульсов, а следовательно и второй режим функционирования устройства.

Нулевой сигнал с выхода элемента ИЛИ 19,поступая на соответствующие входы коммутатора 11, разрешает прохождение кода операции (начального адреса микропрограммы) из поля 3.1 ре.гистра 3 на информационный вход регистра 4. Эта запись синхронизируется первым тактовьгм импульсом с выхода элемента И 16. По адресу в регистре 4 происходит считывание из блока 1 памяти в регистр 5 кода операции (определенного ПЭ в СМ) и этот код с выхода поля 5.2 регистра 5 че- рез мультиплексор 13, который работает по первому входу (на его управляющем входе - единичный уровень сигнала с поля 3.2 регистра 3).поступает на выход устройства, где с соответствующим адресом ПЭ в СМ, для которого эта информация предназначена, образует группу сигналов на выходе 36 устройства. Информация с выхода 36 устройства поступает в ПСМ (фиг,-3), где обрабатывается соответствующим образом. Адрес следующей микрокоманды с выхода поля 5.1 регистра 5, проходя через открытый первый вход ком5

0

0

g мутатора 11 (по единичному сигналу

0

с выхода элемента ИЛИ 19), по второму тактовому импульсу записывается в регистр 4 адреса и программирование ПСМ на М1МД-обработку продолжено аналогично рассмотренному. По окончании программирования ПСМ еди ничньш сигнал конца микропрограммы с поля 5.3 регистра 5 через второй вход элемента ИЛИ 17 поступает на установочный вход триггера 9 и устанавливает этот триггер в единичное состояние, которое индицирует процесс завершения программирования ПСМ на М1МД- или 51МД-обработку.

5

Адресация ИЭ в ПСМ при программировании происходит с помощью блока 15 (фиг.2) следующим образом.В начале программирования ПСМ счетчики 42 и 43, а также регистр 44 находятся в нулевом состоянии. Единичный сигнал с поля 3.4 регистра 3 поступает на третий (тактовый) вход блока 15, разрешая тем самым прохождение тактовых импульсов на суммирующий вход -счетчика 42. По завершении первого тактового импульса на вьгход 36 устройства выдан код операции на ПЭ в ПСМ, имеющий адрес 0,0 (ну- мерация строк и столбцов начинается с нуля),так как элемент 28 задержки задержит первый тактовый импульс на врем одного такта и увеличения содержимо- го счетчиков 42 и 43 не происходит, Второй тактовый импульс, поступая на суммирующий вход счетчика 42, увеличивает его содержимое на 1 и оставляет счетчик 43 в нулевом состоянии. Этот же импульс, проходя через элемент 54 задержки (что обусловлено переходными процессами счетчиков) синхронизирует запись адреса следующего ПЭ в ПСМ-(0,1), для которого предназначен очередной код операции в поле 5.2 регистра 5. При достижении адреса граничного ПЭ в ПСМ в данной строке на выходе элемента И 46 появляется единичный сигнал, который обеспечивает через эле- мент И 47 увеличение содержимого счетчика 43 (устанавливает номер следующей строки) и через одновибра- тор 52 и элемент ШЖ 50 обнуляет счетчик 42. Таким образом,, происходи последовательное формирование адресов (код номера строки и код номера столбца), которые фиксируются и вьщаются на выход 36 устройства с регистра 44. При достижении последней строки на выходе 48 счетчика 43 индицируется единичньш сигнал, и при достижении последнего столбца (последний адресуемьм ПЭ в ПСМ) единичный сигнал на выходе элемента И 46, проходя через открытый элемент И 49, вьздает на выход признака индикации блока 15 единичный сигнал и через одновибратор 53 и элементы ИЛИ 50 и 51 обнуляет счетчики 42 и 43, подготавливая блок 15 к следующему циклу программирования.

При настройке ПЭ в СП на 81МД-об- . заботку (что индицируется нулевым

926

сигналом в поле 3.2 регистра 3) мультиплексор 13 работает по своему второму входу (на его управляющем входе - нулевой с игнал) и на выход 36 устройства поступает код операции из поля 3.1 регистра 3 (единьй для всех ПЭ в массиве), и происходит последовательная настройка всех ПЭ на этот код с помощью блока .15 аналогично рассмотренному. При завершении программирования ПЭ в ПСМ на выходе элемента ИЛИ 20 появляется единичный сигнал, которьш перебрасывает триггер 9 в единичное состояние и через время задержки элемента 27 обнуляет регистры 4 и 5, подготавливая их к следующему этапу программирования.Таким образом, завершение режима настройки ПЭ СМ индицируется единичным состоянием триггера 9. После програм мирования ПЭ в ПСМ устройство готово к функционированию во втором режиме.

В режиме выработки управляющих сигналов с программируемой динамической адаптацией структуры СП и маршрутов передачи данных в СП единичный уровень сигнала с прямого выхода триггера 9 открывает элемент И 17 дл прохождения тактовых импульсов с ГТИ 10 на входы синхронизации регистра 6, блока 2 и регистра .7. Нулевой синал с выхода элемента ИЛИ 24, поступая на соответствующие входы коммутатора 12, разрешает прохождение информации из поля 3.3 регистра 3 (код операции) на информационный вход регистра 6, синхронизация записи в которьй происходит по тактовому импульсу с выхода элемента И 17. Начинается функционирование группы блоков устройства, включающей коммутаторы 12, регистр 6, блок 2 памяти, регистр 7 микрокоманд, мультиплексор 14 логических условий, элементы ШЖ 23 и 24, элемент И 17 и элемент 29 задержки, обусловленное переходными процессами регистра 6 и блока 2 памяти. По каждому тактовому импульсу в СП в.ыдается микрокоманда, формат которой представлен полями регистра 7. Поле 7.1 регистра 7 (выход 37 устройства) задает структуру ПСМ, т.е. определяет конфигурацию пространственных связей между ПЭ в СМ (фиг.1 и 3). Поля 7.-4 и 7.3 (выходы 40 и 39 устройства) определяют адреса считывания и занесения информации соответственно до обработки и после обработки информации СП. Поля 7.2 и 7.5 регистра 7 (выходы 38 и 41 устройства) задают маршруты передачи данных относительно входного и выходного буферов в ПСМ. Поле 7.6 регистра 7 является полем логических условий и совместно с информацией, поступающей на. вход 35 устройства, с помощью мультиплексора 14 и элемента ИЛИ 23 задает ветвления в микропрограмме в случае необходимости динамической адаптации структуры СП и маршрутов передачи данных.

8точках ветвления микропрограммы с помощью элемента ИЛИ 23 и коммутатора 12 происходит модификация адреса в соответствии со значением логического условия на выходе мультиплексора 14. При появлении единичного сигнала на выходе поля 7.8 регистра (вьшолнение микропрограммы закончено) решение задачи СП завершается

и по этому сигналу происходит обнуление регистров 6 и 7 и триггера 8 пуска. ГТИ 10 заканчивает свою рабо- ту до следующего цикла функционирования устройства. Если в следующем цикле функционирования устройства нет необходимости перепрограммирования операции ИЗ в СП, то его работа начинается подачей единичного сигнал на вход 33 устройства и нулевого сигнала на вход 32 устройства (триггер

9сохраняет свое единичное состояние) . Формат команды, записанной из

.управляющей машины в регистр 3, в этом случае соответствует нулевым полям 3.1, 3.2 и 3.4 и ненулевому полю 3.3 регистра 3, т.е. в активизированном режиме задействованы выходы 37-41 устройства. Выход 36 устройства активизируется только в режиме программирования ПЭ СП.

Работа устройства может быть прервана (например, по сигналу управляющей машины или оператора) единичным импульсом, поступающим на вход 34 устройства. В случае необходимости перепрограммирования ПЭ в СП на новый алгоритм и решения зада-чи с заданным алгоритмом функционирование устройства происходит аналогично рассмотренному.

Формула изобретения

1, Микропрограммное устройство управления, содержащее блок памяти про

7

а5

10

15

54192

грамм, блок управляющей памяти, первый и второй регистры адреса, первый и второй регистры микрокоманд, мультиплексор логических условий, триггер пуска, триггер программирования, генератор тактовых импульсов,первый и второй коммутаторы, два. элемента ИПИ, два элемента И и первый элемент задержки, причем выход первого коммутатора соединен с информационным входом первого регистра адреса, выход первого регистра адреса подключен к адресному входу блока памяти программ, выход которого соединен с информационным входом первого регистра микрокоманд, выход поля адреса следующей микрокоманды первого регистра микрокоманд подключен

2Q к первому информационному входу первого коммутатора, вход запуска устройства соединен с единичным входом триггера пуска, выход которого подключен к входу запуска генератора

25 тактовых импульсов, выход второго

коммутатора соединен с информационным входом второго регистра Адреса, выход которого подключен к адресному входу блока управляющей памяти, выход

30 которого соединен с информационным входом второго регистра микрокоманд, выход поля логических условий второго регистра микрокоманд подключен к первому входу мультиплексора логиче,. ских условий, второй вход которого является входом логических условий устройства, выход поля адреса следующей микрокоманды второго регистра микрокоманд подключен к первому.ин40 формационному входу второго коммутатора, выход первого элемента ИЛИ подключен к нулевому входу триггера пуска, первый и второй входы первого элемента ИЛИ соединены соответствен- но с входом прерывания устройства и выходом поля признака выполнения микропрограммы второго регистра микрокоманд, первый и второй входы и выход второго элемента ИЛИ подключены соответственно к модифицируемому разряду поля адреса следующей микрокоманды второго регистра микрокоманд, выходу мультиплексора логических усовий и модифицируемому разряду первого информационного входа второго

коммутатора, отличающееся тем, что, с целью расширения области применения за счет реализации программируемой динамической адаптации маршрутов передачи данных, оно содержит регистр управления, блок формирования адреса, мультиплексор программирования, третий, четвертый, пятый, шестой и седьмой элементы ИЛИ, второй, третий и четвертый элементы задержки, при этом выход первого элемента И соединен с входом синхронизации первого регистра адреса и входом первого элемента, задержки, выход которого подключен к входу разрешения обращения блока памяти программ и входу синхронизации первого регистра микрокоманд, первый и второй входы третьего элемента ИЛИ соединены соответственно с выходом второго элемента задержки и входом запуска устройства, выход третьего элемента ИЛИ подключен к входам сброса первого регистра адреса и первого регистра микрокоманд, вход и выход четвертого элемента ИЛИ соединены соответственно с выходом первого регистра адреса и управляющим входом первого коммутатора, первый, второй и третий входы первого элемента И подключены соответственно к выходу генератора тактовых импульсов, выходу поля признака обработки регистра управления и инверсному выходу триггера программирования, первый и второй информационные входы управляющий вход и выход мультиплексора программирования соединены соответственно с выходом поля кода операции первого регистра микрокоманд, выходом поля кода операции регистра управления, выходом поля признака обработки регистра управления и выходом кода операции устройства, вход сброса, первый и второй тактовые входы, информационньй выход и выход признака индексации блока формирования адреса подключены соответственно к входу запуска устройства, выходу третьего элемента задержки, выходу поля метки перепрограммирования регистра управления, выходу кода операции устройства и первому входу пятого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом поля конца микропрограммы первого регистра микрокоманд и входом второго элемента задержки, единичньй и нулевой входы и прямой выход триггера программирования подключены соответственно к выходу пятого элемента ИЛИ, входу признака перепрограммирования устройства и пер0

5

0

вому входу второго элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, который подключен также к входу третьего элемента задержки, выход второго элемента И соединен с входом синхронизации второго регистра адреса и входом четвертого элемента задержки, выход которого подключен к входу разрешения обращения блока управляющей памяти и входу синхронизации второго регистра микрокоманд, выходы поля конфигурации, поля приема данных, поля адреса записи, поля адреса считывания и поля выдачи данных которого соединены с одноименными выходами устройства, вход сброса, информационный вход, вход синхронизации и выход поля начального адреса регистра управления подключены, соответственно к входу запуска устройства,входу кода операции устройства, входу синхронизации устройства ивторо5 му информационному входу второго коммутатора, первый и второй входы и выход шестого элемента ИЛИ соединены соответственно с выходом поля признака выполнения 1 шкропрограммы второго регистра микрокоманд, входом запуска устройства и входами сброса второго регистра адреса и второго регистра микрокоманд, а вход и выход седьмого элемента ИЛИ подключены соответственно к выходу второго регистра адреса и управляющему входу второго коммутатора.

2. Устройство по П.1, отличающееся тем, что блок формирования адреса содержит счетчик индексации столбцов, четьфе элемента И, счетчик индексации строк, регистр адреса, два элемента ИЛИ, два одновибратора и элемент задержки,

g вход и выход которого соединены соответственно с выходом первого элемента И и входом синхронизации реги - стра адреса, первьш и второй входы и выход первого элемента И подключены соответственно к первому и второму тактовым входам блока и счетному входу счетчика индексации столбцов, выход которого соединен с первым информационным входом регистра адреса и входом второго элемента И, выход которого подключен к первому входу третьего элемента И и входу Первого одновибратора, вход сброса блока соединен с входом сброса ре0

5

0

0

5

1

гистра адреса и первыми входами первого и второго элементов ИЛИ, второй и третий входы и выход первого элемента ИЛИ подключены соответственно к выходу-первого одновибрато- ра, выходу второго одновибратора и входу сброса счетчика индексации столбцов, второй вход и выход второго элемента ИЛИ соединены соответственно с выходом второго одновибратора и входом сброса счетчика и-ндек сации строк, выход которого подключен к второму информационному входу

54192

регистра адреса.и первому входу четвертого элемента И, второй вход которого соединен с выходом йторого элемента И, выход че1 вертого элемента И подключен к выходу признака индексации блока и входу второго оцновибратора, второй вход и выход третьего элемента И соединены соответственно с выходом первого элемента И и тактовым входом счетчика индексации строк, а выход регистра адреса подключен к информационному выходу блока. . I

10

Фиг.1

а

А

W

48

v 61

р«

Ч1Г

15

«Pwe.f

. J

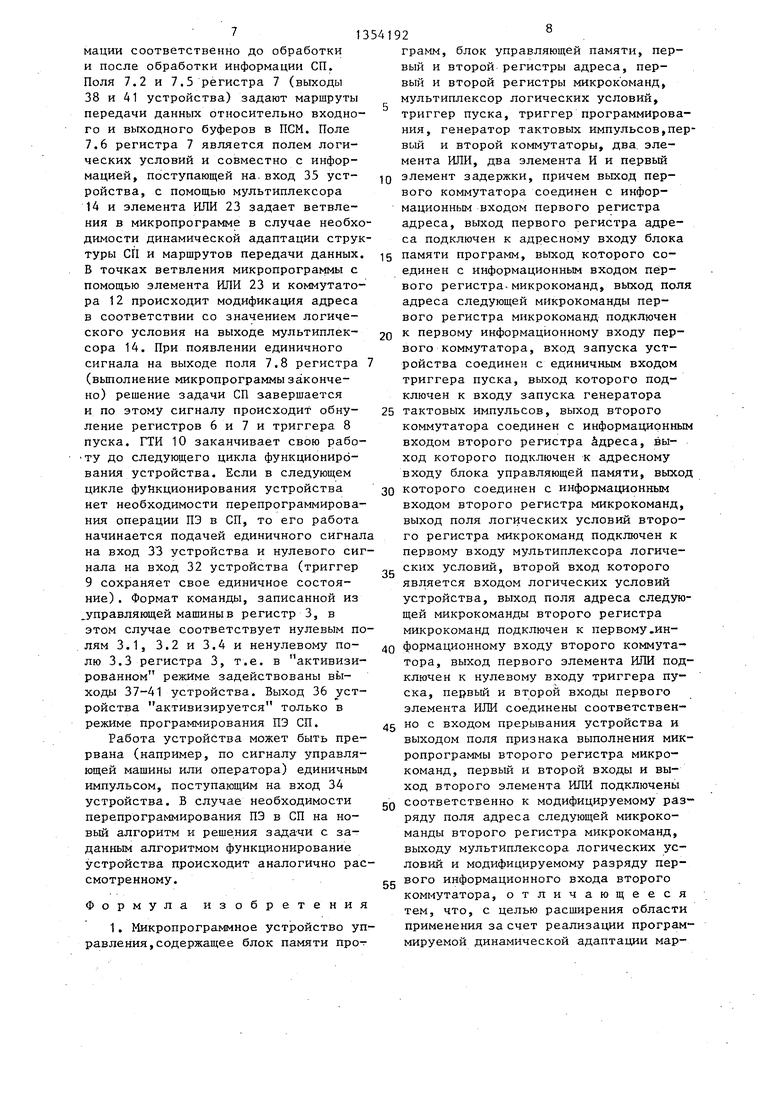

Настройка ПЗ s СП на SIMD или MiMD обра- Вотку

Решение задачи на систоли1 еско процессоре

пок.усл „ выполнено о /нет

Динамическая адапта- ци1 структуры СП H/ifjjfi наршрутов nodavu донных

Фае. If

Составитель Г.Виталиев Редактор Н.Бобкова Техред А.КравчукКорректор Л. Пшшпенко

. ,,, и---«м - -«---

Заказ 5695/44 Тираж 671Подписное

ВШШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1495789A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств управления систолических, матричных, конвейерных и других мультипроцессорных систем, использующих параллельную обработку информации. Цель изобретения - расширение области применения за счет реализации программируемой динамической адаптации маршрутов передачи данных. Для этого в устройство, содержащее блок памяти .программ, блок управляющей памяти, два регистра адреса, два регистра микрокоманд, мультиплексор логических УСЛОВИЙ, триггеры пуска и программирования, генератор тактовых- импульсов, два коммутатора, два элемента ИЛИ, два элемента И и первый элемент задержки, введены регистр управления, блок формирования адреса, мультиплексор программирования, с третьего по седьмой элементы ИЛИ и с второго по четвертый элементы задержки с соответствующими связями. 1 з.п. ф-лы, 4 ил. (Л

| Бахтиаров Г.Д | |||

| Цифровая обработка сигналов | |||

| Проблемы и основные направления повьппения эффективности | |||

| - Зарубежная радиоэлектроника, 1984, № 12, с.48-66 | |||

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-23—Публикация

1985-10-28—Подача