1

Р эобретение относится к автоматике и измерительной технике и -может быть использовано в автоматических переключающих устройствах.

Цель изобретения - уменьшение пот- ребления электрической энергии при оДмовреме ННЬм расширении функциональных возможностей за счет снижения постоянной рассеиваемой мощности и обеспечения возможности автоматичес- кого изменения периодов заряда-разряда конденсатора и периода переключения.

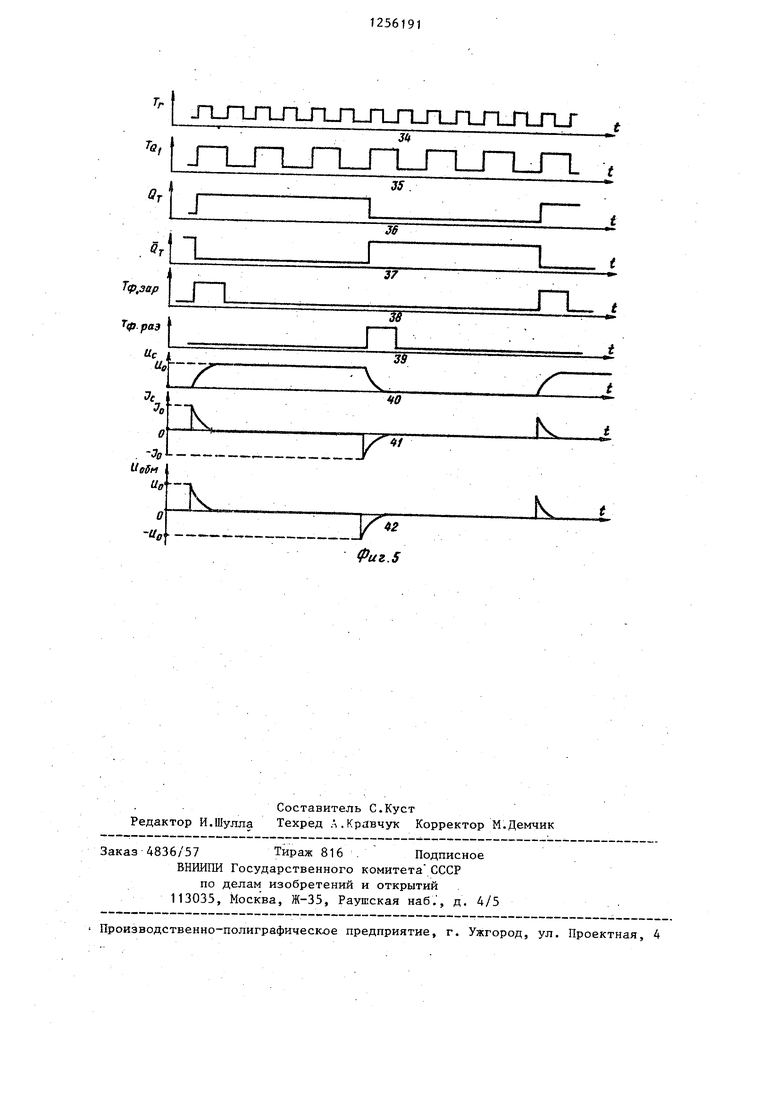

На фиг.1 приведена структурная . схема переключающего устройства; на фиг.2 - схема транзисторно-оптронного блока гальванической развязки; на фиг«3 - схема формирователя импульсов управления зарядом или разрядом по. :: первому варианту; на фиг.4, - то же, по второму варианту; на фиг.5 - временная диаграмма работы переключающего устройства.

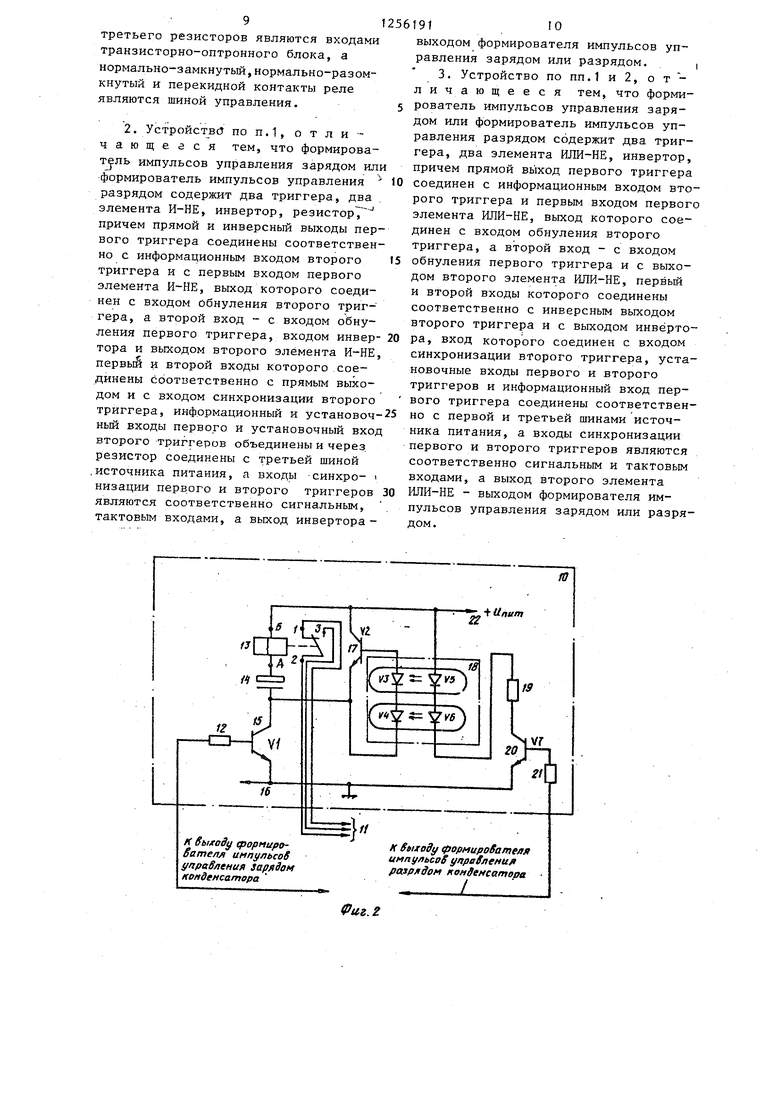

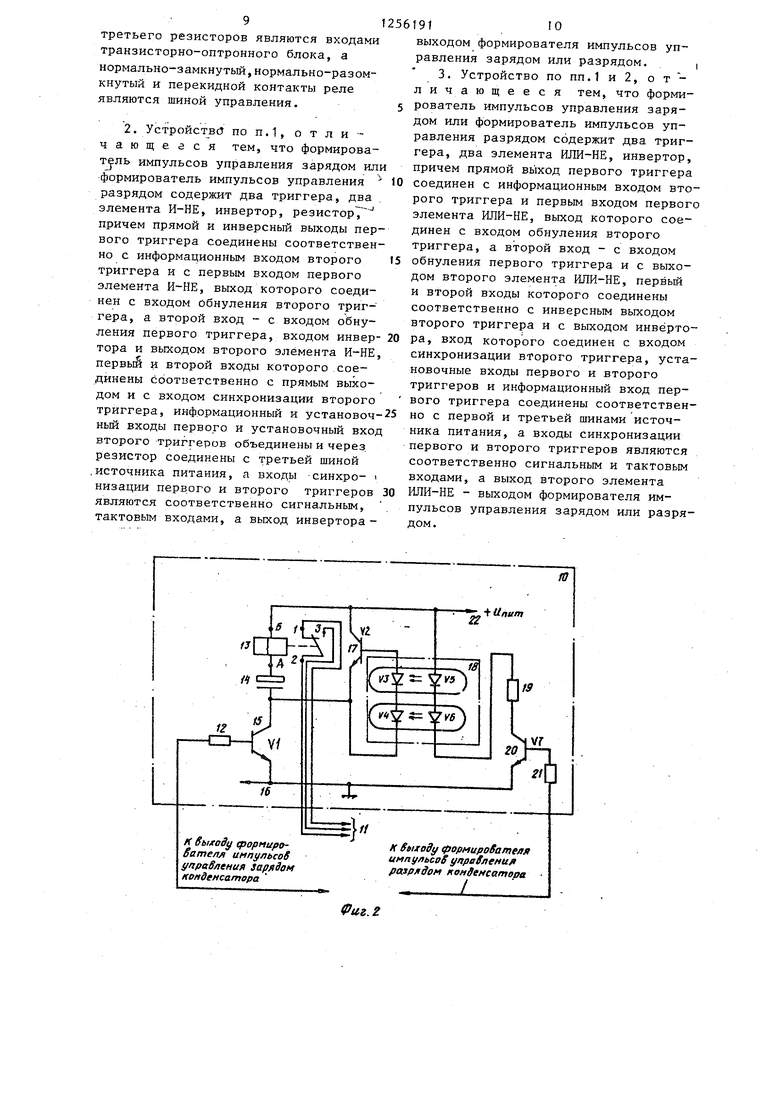

Переключающее устройство содержит кварцевьй генератор 1, выход которого соединен с входом N-разрядного делителя 2 частоты, мультиплексор 3 периода переключения, выход которого соединен с входом триггера 4, задат-- чик 5 кода периодов, выходы которого соединены с мультиплексором 6 периода заряда-разряда и входом мультиплексора 3 периода переключения, а выход мультиплексора 6 .соединен с тактовыми входами блока 7 формирователей импу- льсов управления зарядом-разрядом, со.стоящих из формирователей 8 и 9 им- пульсов управления заряда и разряда соответственно, сигнальные входы которых соединены соответственно с прямым и ин- версным выходами триггера 4, а выходы соединены с входами транзисторно-оптронного блока 10 гальванической развязки, выходы которого являются щиной 11 управления. Выходы N-разрядного делителя 2 частоты соединены с соответствующими входами мультиплексора 3 периода переключения и мультиплексора 6 периода заряда-разряда. Транзистор- но-оптр1онный блок 10 содержит первый резистор 12, реле 13, конденсатор 14, первый транзистор 15, первую шину 16. источника пита.ния, второй транзистор 17, блок 18 фотодиодных .оптронов, второй резистор 1.9, третий транзистор 20, третий резистор 21 и вторую шину 22 источника питания.

1912

Первый вывод первого резистора 12 соединен с выходом формирователя 8 импульсов управления зарядом, а второй вывод - с базой первого п - р - п-транзистора 15, эмиттер которого соединен с первой шиной 16 источника питания, а коллектор - с эммитером второго п - р - п-транзистора 17, первым выходом блока 18 фотодиодных оптронов и общей точкой электролитического конденсатора 14 и обмотки реле 13, контакты которого соединены с шиной 11 управления, а второй вывод обмотки реле 13 - с второй шиной

22источника питания И с коллектором второго п - р - п-транзистора 17, база которого соединена с вторым выходом блока 18 фотодиодных оптронов, первый вход которого соединен с второй шиной 22 источника питания, а первый вход через второй резистор 19 соединен с коллектором третьего п - р - п-транзистора 20, эмиттер которого соединен с.первой шиной 16 источника питания, а база через третий резистор 21 соединена с выходом формирователя 9 импульсов управления

разрядом конденсатора 14. I

Формирователь 8 импульсов управления зарядом конденсатора 14 или формирователь 9 импульсов управления . разрядом конденсатора 14 блока 7 формирователей импульсов управления зарядом-разрядом конденсатора 14 по первому варианту схемы содержит первый триггер 23, первда элемент И-НЕ 24, резистор 25, второй триггер 26, второй элемент И-НЕ .27 и инвертор 28, Вход синхронизации первого триггера

23является сигнальным входом формирователя 8 и 9 и соединен с выходом триггера 4, а прямой Q-и инверсный Q-вы- ходы первого триггера 23 соединены соответственно с информационным входом второго триггера 26 и с первым входом первого элемента И-НЕ 24, выход которо го соединен с входом обнуления второго триггера 26, а второй вход - с входом обнуления первого триггера .23, входом инвертора 28 и выходом второго элемента И-НЕ- 27, первьш и второй входы которого соединены соответственно с прямым выходом и входом синхронизации второго триггера 26. Установочный вход второго 26 и информационный и установочный входы первого 23 триггера объединены и через резистор 25 соединены с третьей шиной источника

(+5 В). Вход синхронизации второго триггера 26 является тактовым входом формирователя 8 или 9 импульсов управления зарядом И.ПИ разрядом Конденсатора и соединен с выходом нуль- типлексора 6 периода заряда-разр яДа конденсатора. Выход инвертора 28 является выходом формирователя 8 или 9 импульсов управления зарядом или разрядом конденсатора и соединен с входом транзисторно-оптронного блока 10.

Формирователь 8 импульсов управления зарядом или формирователь 9 импульсов управления разрядом конден- сатора 14 блока 7 по второму вариант схемы содержит первый триггер 29, первый элементИЛИ-НЕ 30, второй триггер 31, инвертор 32, второй элемент ИЛИ-НЕ 33.

Прямой выход первого триггера 29 соединен с информационным входом второго триггера 26 и первым входом первого элемента ИЛИ-НЕ 30, выход которого соединен с входом обнуления второго триггера 31, а второй вход - с входом обнуления первого триггера 29 и выходом второго элемента ИЛИ-НЕ 33, первый и второй входы которого соединены соответственно с инверсным выходом второго триггера 31 и выходо инвертора 32, вход которого соединен с входом синхронизации второго триггера 31. Установочные входы второго 31 и первого 29 триггеров и информационный вход первого триггера 29 соединены соответственно с первой шиной 16 и третьей шиной источника питания (+5 в) . Входы синхронизации первого 29 и второго 31 триггеров являются соответственно сигнальным и тактовым входами формирователи 8 или 9 импульсов управления зарядом или разрядом конденсатора и соединены с выходом триггера 4 и выходом мультиплексора 6 периода заряда-разряда конденсатора. Выход второго элемента ИЛИ-НЕ 33 является выходом формирователя 8 или 9 импульсов управления зарядом или разрядом конденсатора и соединен с входом транзисторно-оптронного блока 10.

На фиг. 5 приведена последовате- .льность импульсов 34 кварцевого генератора 1, сигнал 35 меандр с первого Q,-выхода N -разрядного делителя 2 частоты, сигнал 36 меандр с прямого Q-выхода триггера 4, сигнал 37 ме

5 10

(5 20

25 о 0 5 0

5

5

андр с инверсного Q-вьгхода триггера 4, форма импульсного сигнала 38 на выходе формирователя 8, управляющего зарядом конденсатора 14, форма импульсного сигнала 39 на выходе формирователя 9, управляющего разрядом конденсатора 14, напряжение 40 на конденсаторе 14, формы тока 41 и напряжения 42 в обмотке реле 13.

Переключающее устройство работает следующим образом.

Кварцевый генератор 1 формирует последовательность импульсов стабильной частотой повторения f . N-разряд- ный делитель 2 частоты с разрядных выходов Q,.,..., Q|,..., QN - сетку кратких частот f, f„,. .., f,..., f. Например, для двоичного делителя сетка частот будет 1/2fg, 1/4fg,..., 1 /2 f , . . . , 1 /2 fp или для периодов . повторения импульсов соответственно 2То, 4Т, ,..., 2 Т„,..., 24, где Т(, - период повторения импульсов кварцевого генератора 1. Импульсные сигналы типа меандр с кратными частотами и периодами повторения поступают на соответствующие входы мультиплексора 6 периода заряда-разряда конденсатора 14 и на входы мультип лексора 3 периода переключения двух- позИционного двустабильного поляризованного электромагнитного реле 13. В зависимости от кода, формируемом в задатчике 5 кода периодов либо вручную, либо от управляющей микро- ЭВМ или микропроцессора, через мультиплексор 6 от делителя 2 частоты проходит один из N сигналов с периодом повторения Т(, а через мультиплексор 3 - один из сигналов с периодом повторения Т, при этом должно вьшолняться неравенство Т Т,. Сигнал с выхода мультиплексора 6 подается -на тактовые С-входы вторых DRS- триггеров 26 формирователей 8 и 9 импульсов управления зарядом и разрядом конденсатора 14. Сигнал с выхода мультиплексора 3 периода переключения реле 13 подается на вход Т-триггера 4. На прямом Q- и инверсном Q-выходах Т-триггера 4 образуются противофазные импульсные колебания типа меандр с удвоенным периодом их повторения Т-гр , для которого вьтолняется условие Ттр 2X2 Т, . Эти колебания подаются соответственно на сигнальные С-входы первых ПЕЗ-триггеров формирователей

S1256

и 9 импульсов управления зарядом разрядом конденсатора 14.

На информационный D-вход и устаноочный S-вход первого 23 и установочый S-вход второго 26, DRS-триг- g еров через резистор 25 от- тре- .; ьей шины источника питания (+5 В) ействует постоянный сигнал с уровнем огической 1. При поступлении на С-вх5д с йнхронйзации первого DRS- 10 .триггера 23 .сигнала меандр с ровнем логичесл ой 1 на его прямом - и инверсном Q-выходах появляются напряжения с уровнем логической 1 и О, которые подаются соответствен- 15 но на D-вход .второго DRS- триггера ; 26 и первый вход первого элемента И-НЕ 24. На выходе второго элемента И-НЕ 27 действует напряжение с уровнем логической 1, которое подается 20 на R-вход DRS-триггера 23 и второй вход первого элемента И-НЕ 24, на выходе которого появляется напряжение с уровнем логической 1, при этом на R-входах DRS-триггеров 23 и 26 25 действует напряжение с уровнем логической 1, которое не изменяет состояния выходов этих триггеров.

При появлении н-i С-входе синхронизации второго DRS-триггера 26 первого тактового импульса с выхода мультиплексора 6 на прямом выходе второго DRS-триггера 26 появляется напряжение с уровнем логической 1 которое действует на первый вход второго эле-35 мента И-НЕ 27, на второй вход которого действует также уровень логической 1 с первого тактового импульса мультиплексора 6, в результате на выходе второго элемента И-НЕ 27 появ- ляется напряжение с активным уровнем логического О, которое действует на R-вход обнуления первого триггера 32 и обнуляет его (-выход, при этом на его инверсном Q-выхрде появляется напряжение с уровнем логической 1. При переходе первого тактового импульса к полупериоду логического О на выходе второго элемента И-НЕ 27 в соответствии.с таблицей истинности ° появляется напряжение с уровнем логической 1 которое действует на второй вход первого элемента И-НЕ 24, на выходе которого появляется напряжение с активным логическим уровнем 55 О, который обнуляет прямой Q-выход второго PRS-триггера 26 и на выходе второго элемента И-НЕ 27 появляется

1916

напряжение с уровнем логической 1, а на выходе инвертора 28 - напряжение с уровнем логического О.

Второй и последующие тактовые импульсы с выхода мультиплексора 6 в период действия сигнального импульса с выхода Т-триггера 4 не изменяют состояния выхода формирователей 8 и 9, поскольку прямые Q-выходы DRS- триггеров 23 и 26 находятся в состоянии логического О. Таким образом, из более продолжительного сигнального импульса Т-триггера 4 на выходе формирователя 8 или 9 импульсов управления зарядом или разрядом конденсатора 14 формируется более короткий импульс, длительность которого управляется задатчиком 5 кода периодов.

Принцип действия формирователей 8 и 9 импульсов управления зарядом или разрядом конденсатора на фиг,4 аналогичен принципу действия формирователей 8 и 9 на фиг.3.

Выходные импульсы управления зарядом и разрядом конденсатора от формирователей 8 и 9 подаются на входы транзисторно-оптронного блока 10.

Транзисторно-оптронный блок 10 работает следующим образом.

Выходные импульсы 38 и 39 (фиг.5) формирователей 8 и 9 через резисторы 12 и 21 подаются на базы п - р - п- транзисторов 15 и 20, которые работают в ключевом режиме. При высоком логическом уровне.импульса, управляющего зарядом конденсатора, транзистор 15 переводится в режим насыщения и через насьщ енный транзистор 15, электролитический конденсатор 14 и сопротивление поляризованного двух- позиционного двустабияьного электромагнитного рел.е 13 от второй пганы 22 течет ток заряда конденсатора 14. В обмотке реле 13 формируется поло- жительный экспоненциальный импульс .напр яж ёния и тока, магнитное поле которого, взаимодействуя с магнитным полем постоянного магнита поляризованного реле, переключает его якорь в одно из устойчивых положений равновесия, при этом транзисторы 20 и 1 находятся в состоянии отсечки тока коллекторов, поскольку с выхода формирователя 9 импульсов управления разрядом формируется низкий логический уровень напряжения (фиг.5; 39). В результате конденсатор 14 заряжается в течение периода тактового импульса мультиплексора 6, По окончании действия тактового импульса мультиплексора 6 транзистор 15 переходит в режим отсечки тока коллектора и заряженный конденсатор 14 сохраняет свой заряд.

При появлении на базе транзистора 20 импульса, управляющего разрядом конденсатора 14, транзистор 20 переходит в режим насыщения тока коллектора и через насьпценный транзистор 20

и V, блока

О

резистор 19 и светодиоды V

18 фотодиодных оптронов от второй

шины 22 течет ток, в результате светодиоды Vj и V излучают свет, ко- 15 лания зарядом и формирователя импуль. торый преобразуют в удвоенную фото- ЭДС фотодиоды V, и Уц , которая открывает разрядный п - р - п-транзистор 17 и переводит его в режим насьпцения.

Вследствие этого образуется цепь раз-20 разряда и входами мультиплексора периоряда заряженного конденсатора 14 через насьпденный транзистор 17 и обмотку реле 13, При разряде электролитического конденсатора 14 через сопротивление обмотки реле 13 в последней 25 лючения, прямой и инверсный выходы

формируются отрицательные экспоненциальные импульсы напряжения и тока, электромагнитная сила меняет знак и происходит переключение якоря реле 13 в первоначальное положение устой- 30 чивого равновесия. При использовании в транзисторно-оптронной схеме согласованных п - р - п-транзисторов 15 и 17 достигается равенство сопротивлений насьпцения зарядного и разрядного 35 транзисторов 15 и 17, и следовательно, модулей токов заряда-разряда коненсатора 14, а также электромагнитных сил, переключающих якорь реле 13 с равными временами в устойчивые по- 40 ожения равновесия.

Технический эффект от использования предлагаемого переключающего устройства заключается в уменьшении потребления электрической энергии при одновременном расширении функциональных возможностей за счет снижения постоянной рассеиваемой мощности- и обеспечения возможности автоматического изменения периодов, заряда- -50 разряда конденсатора и периода переключения .

Формула изобретения

1. Переключающее устройство,содержащее кварцевый генератор, выход ко- торого соединен с входом N-разрядного

Делителя частоты, транзисторно-опт- ронный блок гальванической развязки с выходной шиной управления, о т -. личающееся тем, что, с

целью уменьшения потребления электрической энергии при одновременном расширении функциональных возможностей, в устройство введены мультиплексор периода заряда-разряда, мультиплексор периода переключения, задатчик кода периодов, триггер, блок формирователей импульсов управления зарядом- оазрядом, вьтолненный из двух иден- тичных-формирователя импульсов управсов управления разрядом конденсатора, причем выходы N-разрядного делителя частоты соединены с соответствующими входами мультиплексора периода зарядада переключения, управляющие входы ко-; торых соединены с выходом задатчй са кода периодов, вход триггера соединен с выходом мультиплексора периода перек3035 0

0 5

триггера соединены с сигнальными входами формирователей импульсов управления зарядом и разрядом блока формирователей импульсов управления заряда-разряда, тактовые входы которых соединены с выходом мультиплексора периода заряда-разряда, а выходы - с входами транзисторно-оптронного блока гальванической развязки, который образован из трех транзисторов, трех резисторов, последовательной цепи из конденсатора и обмотки реле, блока фотодиодных оптронов, причем эмиттер первого транзистора соединен с первой шиной источника питания, база, - с

первым выводом первого резистора, коллектор с эмиттером второго транзистора, первым выходом блока фотодиодных оптронов и с первым выводом посГледовательной цепи из конденсатора и обмотки реле, второй вывод которой соединен с второй шиной источника питания и с коллектором второго транзистора, база которого соединена с вторым выходом блока фотодиодных оптронов, первый вход которого подключен к второй шине источника питания, а второй вход через второй резистор - к коллектору третьего транзистора, эмиттер которого соединен с первой шиной, источника питания, а база - с первым выводом третьего резистора, вторые выводы первого и

третьего резисторов являются входами транзисторно-оптронного блока, а нормально-замкнутый,нормально-разомкнутый и перекидной контакты реле являются шиной управления.

2. Устройстве по П.1, о т л и - чающегся тем, что формирователь импульсов управления зарядом или формирователь импульсов управления разрядом содержит два триггера, два , элемента И-НЕ, инвертор, резистор причем прямой и инверсный выходы первого триггера соединены соответственно с информационным входом второго триггера и с первым входом первого элемента И-НЕ, выход которого соединен с входом обнуления второго триг- гера, а второй вход - с входом обнуления первого триггера, входом инвер- тора и выходом второго элемента И-НЕ, первый и второй входы которого соединены соответственно с прямым выходом и с входом синхронизации второго триггера, информационный и установочный входы первого и установочный вход второго триггеров объединены и через, резистор соединены с третьей шиной .источника питания, а входы -синхро- низации перв.ого и второго триггеров являются соответственно сигнальным, тактовым входами, а выход инверторавыходом формирователя импульсов управления зарядом или разрядом. |

3. Устройство по ПП.1 и 2, о т - личающееся тем, что формирователь импульсов управления зарядом или формирователь импульсов управления разрядом содержит два триггера, два элемента ИЛИ-НЕ, инвертор, причем прямой выход первого триггера соединен с информационным входом второго триггера и первым входом первого элемента ИЛИ-НЕ, выход которого соединен с входом обнуления второго триггера, а второй вход - с входом обнуления первого триггера и с выходом второго элемента ИЛИ-НЕ, первый и второй входы которого соединены соответственно с инверсным выходом второго триггера и с выходом инвертора, вход которого соединен с входом синхронизации второго триггера, установочные входы первого и второго триггеров и информационный вход первого триггера соединены соответственно с первой и третьей шинами источника питания, а входы синхронизации первого и второго триггеров являются соответственно сигнальным и тактовым входами, а выход второго элемента ИЛИ-НЕ - выходом формирователя импульсов управления зарядом или разрядом.

Фиг.З

16

29

С вы хода

Чпит

триггера fc

J}

/f

С ёылода мультиплексора периода зарпда-разрл а /гонден са- тора .

-

Фиг.It

8.f

Не fxfi трамяас- торно Оптрвнно - to блока

3f

Q

На ход транзис- тор ft о- оптрон- ного ff/roKu

306

JJ

г

fr

EH

ллл.

TlJ-lJlJ J-lJ J lJ l.J

| название | год | авторы | номер документа |

|---|---|---|---|

| Переключающее устройство | 1984 |

|

SU1181129A1 |

| Способ управления подачей инструмента на электроэрозионном станке с емкостным генератором импульсов и устройство для его осуществления | 1980 |

|

SU1351523A3 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для реакции на аварию в схеме управления потребителями электроэнергии | 1990 |

|

SU1795495A1 |

| Двухтональное устройство для звуковой предупредительной сигнализации | 1989 |

|

SU1728873A1 |

| ФОРМИРОВАТЕЛЬ КОМАНД УПРАВЛЕНИЯ | 2003 |

|

RU2244960C2 |

| Устройство для защиты трехфазного частотно-регулируемого привода от неполнофазного режима питания | 1985 |

|

SU1377950A1 |

| Реле времени | 1987 |

|

SU1497726A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

Изобретение относится к автоматике и измерительной технике. Цель изобретения - уменьшение потребления электричесйой энергии и расширение функциональных возможностей. Переключающее устройство содержит кварцевый генератор 1, N-разрядный делитель 2 частоты и транзисторно-оптронный блок 10 гальванической развязки. Введение мультиплексора 3 периода переключений, триггера 4, задатчика 5 кода периодов, мультиплексора 6 периода заряда-разряда, блока 7 формирователей импульсов управления заряд ом-раз- рядом, выполненного в виде двух формирователей 8 и 9 импульсов управления зарядом и разрядом, и образование новых связей снижают постоянную рассеиваемой мощности и обеспечивают и возможность автоматического изменения периодов заряда-разряда конденсатора и периода переключения. 2 з. п. ф-лы, 5 ил. JSyf-f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| О.Ю.Шмидта АН СССР | |||

| Переключающее устройство | 1984 |

|

SU1181129A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-07—Публикация

1985-02-11—Подача