Изобретение относится к электротехнике и может быть использовано дл фазового управления статическими преобразователями на управляемых вентилях и -мощных стабилизированных источниках питания, в электроприводе и других электротехнических установках

Цель изобретения - повьппение надежности работы устройства и упрощение схемы, а также предотвращение срывов управляющих импульсов.

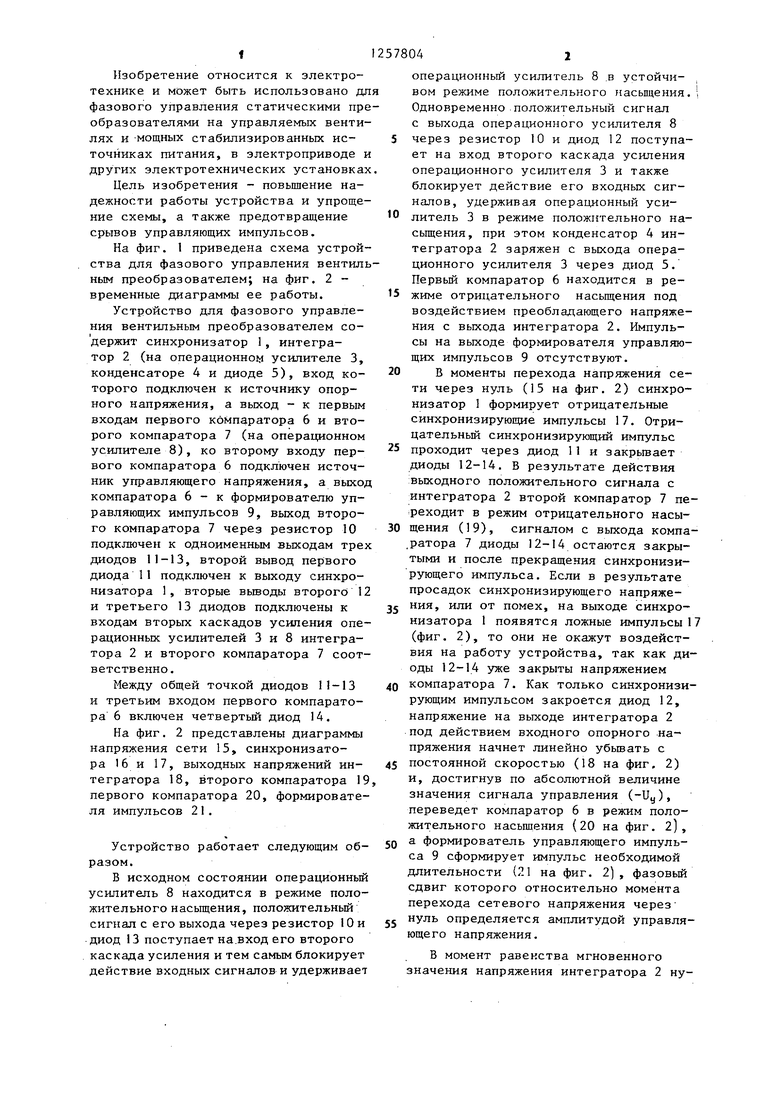

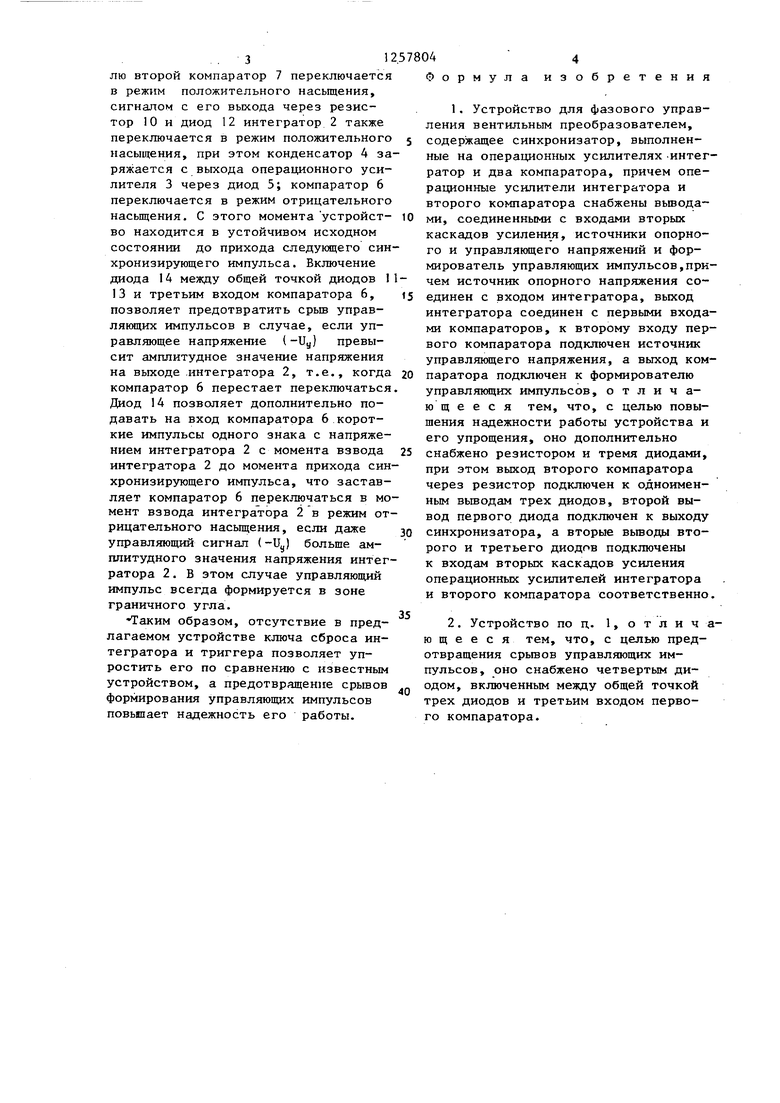

На фиг. 1 приведена схема устройства для фазового управления вентильным преобразователем; на фиг. 2 - временные диаграммы ее работы.

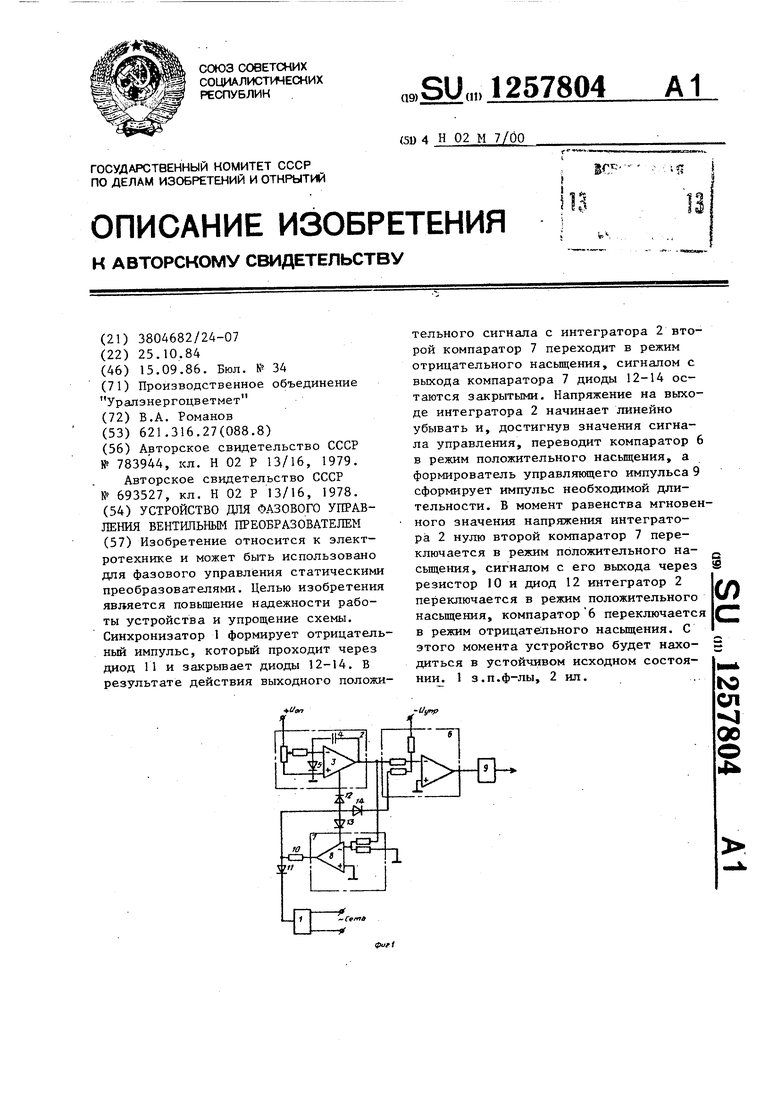

Устройство для фазового управления вентильным преобразователем содержит синхронизатор 1, интегратор 2 (на операционном усилителе 3, конденсаторе 4 и диоде 5), вход которого подключен к источнику опорного напряжения, а выход - к первым входам первого компаратора 6 и второго компаратора 7 (на операционном усилителе 8), ко второму входу первого компаратора 6 подключен источник управляющего напряжения, а выход компаратора 6 - к формирователю управляющих импульсов 9, выход второго компаратора 7 через резистор 10 подключен к одноименным выходам трех диодов 11-13, второй вывод первого диода 11 подключен к выходу синхронизатора 1, вторые вьюоды второго 12 и третьего 13 диодов подключены к входам вторых каскадов усипения операционных усилителей 3 и 8 интегратора 2 и второго компаратора 7 соответственно.

Между общей точкой диодов 11-13 и третьим входом первого компаратора 6 включен четвертьй диод 14.

На фиг. 2 представлены диаграммы напряжения сети 15, синхронизатора 16 и 17, выходных напряжений интегратора 18, второго компаратора 19 первого компаратора 20, формирователя импульсов 21.

Устройство работает следующим образом.

Б исходном состоянии операционньй усилитель 8 находится в режиме положительного насьпцения, полозкительный сигнал с его выхода через резистор 10 и диод 13 поступает на.вход его второго каскада усиления и тем самым блокирует действие входных сигналов и удерживает

операционный усилитель 8 .в устойчивом режиме положительного насыщения.1 Одновременно положительный сигнал с выхода операционного усилителя 8

через резистор 10 и диод 12 поступает на вход второго каскада усиления операционного усилителя 3 и также блокирует действие его входных сигналов, удерживая операционный усилитель 3 в режиме положительного насыщения, при этом конденсатор 4 интегратора 2 заряжен с выхода операционного усилителя 3 через диод 5. Первый компаратор 6 находится в режиме отрицательного насьпцения под воздействием преобладающего напряжения с выхода интегратора 2. Импульсы на выходе формирователя управляющих импульсов 9 отсутствуют.

В моменты перехода напряжения сети через нуль (15 на фиг. 2) синхронизатор 1 формирует отрицательные синхронизирующие импульсы 17. Отрицательный синхронизирующий импульс

проходит через диод 11 и закрьтает диоды 12-14. В результате действия выходного положительного сигнала с интегратора 2 второй компаратор 7 переходит в режим отрицательного насыщения (19), сигналом с выхода компа- .ратора 7 диоды 12-14 остаются закрытыми и после прекращения синхронизирующего импульса. Если в результате просадок синхронизирующего напряжения, или от помех, на выходе синхронизатора 1 появятся ложные импульсы 1 7 (фиг. 2), то они не окажут воздействия на работу устройства, так как диоды 12-14 уже закрыты напряжением

компаратора 7. Как только синхронизирующим импульсом закроется диод 12, напряжение на выходе интегратора 2 под действием входного опорного напряжения начнет линейно убьшать с

постоянной скоростью (18 на фиг, 2) и, достигнув по абсолютной величине значения сигнала управления (-Uy), переведет компаратор 6 в режим положительного насьппения (20 на фиг. 2,

а формирователь управляющего импульса 9 сформирует импульс необходимой длительности (21 на фиг. 2), фазовьш сдвиг которого относительно момента перехода сетевого напряжения через

нуль определяется амплитудой управляющего напряжения.

В момент равенства мгновенного значения напряжения интегратора 2 ну

лю второй компаратор 7 переключается в режим положительного насьпцения, сигналом с его выхода через резистор 10 и диод 12 интегратор 2 также переключается в режим положительного насыщения, при этом конденсатор 4 заряжается с выхода операционного усилителя 3 через диод 5; компаратор 6 переключается в режим отрицательного насыщения. С этого момента устройст- во находится в устойчивом исходном состоянии до прихода следующего синхронизирующего импульса. Включение диода 14 между общей точкой диодов 1 13 и третьим входом компаратора 6, позволяет предотвратить срьш управляющих импульсов в случае, если управляющее напряжет1е (-Uy) превысит амплитудное значение напряжения на выходе .интегратора 2, т.е., когда компаратор 6 перестает переключаться Диод 14 позволяет дополнительно подавать на вход компаратора 6 короткие импульсы одного знака с напряжением интегратора 2 с момента взвода интегратора 2 до момента прихода синхронизирующего импульса, что заставляет компаратор 6 переключаться в момент взвода интегратора 2 в режим отрицательного насыщения, если даже управляющий сигнал (-U,,) больще амплитудного значения напряжения интегратора 2. В этом случае управляющий импульс всегда формируется в зоне граничного угла.

Таким образом, отсутствие в предлагаемом устройстве ключа сброса интегратора и триггера позволяет упростить его по сравнению с известным устройством, а предотвращение срывов формирования управляющих импульсов повыпает надежность его работы.

04

Формула и

4

3 о

бретения

20

j ю 15 зо

25

5

0

1. Устройство для фазового управления вентильным преобразователем, содержащее синхронизатор, выполненные на операционных усилителях -интегратор и два компаратора, причем операционные усилители интегратора и второго компаратора снабжены вьшода- ми, соединенными с входами вторых каскадов усиления, источники опорного и управляющего напряжений и формирователь управляющих импульсов,причем источник опорного напряжения соединен с входом интегратора, выход интегратора соединен с первыми входами компараторов, к второму входу первого компаратора подключен источник управлякяцего напряжения, а выход компаратора подключен к формирователю управляющих импульсов, отличающееся тем, что, с целью повышения надежности работы устройства и его упрощения, оно дополнительно снабжено резистором и тремя диодами, при этом выход второго компаратора через резистор подключен к одиоимен- ным выводам трех диодов, второй вывод первого диода подключен к выходу синхронизатора, а вторые вьшоды второго и третьего диодов подключены к входам вторых каскадов усиления операционных усилителей интегратора и второго компаратора соответственно.

2. Устройство по д. 1, о т л и ч а- ю щ е е с я тем, что, с целью предотвращения срьшов управляющих импульсов, оно снабжено четвертым диодом, включенным между общей точкой трех диодов и третьим входом первого компаратора.

1

(риг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в частоту | 1983 |

|

SU1182678A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Многоканальный синхронизатор | 1973 |

|

SU562046A1 |

| Таймер | 1981 |

|

SU995328A1 |

| ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2216846C2 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| Способ импульсной стабилизации постоянного напряжения и устройство для его осуществления | 1982 |

|

SU1120304A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU936353A1 |

| Преобразователь напряжение - интервал времени | 1986 |

|

SU1483638A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

Изобретение относится к электротехнике и может быть использовано для фазового управления статическими преобразователями. Целью изобретения является повышение надежности работы устройства и упрощение схемы. Синхронизатор 1 формирует отрицательный импульс, которьй проходит через диод 11 и закрьгоает диоды 12-14. В результате действия выходного положительного сигнала с интегратора 2 второй компаратор 7 переходит в режим отрицательного насыщения, сигналом с выхода компаратора 7 диоды 12-14 остаются закрытьми. Напряжение на выходе интегратора 2 начинает линейно убывать и, достигнув значения сигнала управления, переводит компаратор 6 в режим положительного насыщения, а формирователь управл5пощего импульса 9 сформирует импульс необходимой длительности. В момент равенства мгновенного значения напряжения интегратора 2 нулю второй компаратор 7 переключается в режим положительного насыщения, сигналом с его выхода через резистор 10 и диод 12 интегратор 2 переключается в режим положительного насыщения, компаратор 6 переключается в режим отрицательного насьщения. С этого момента устройство будет находиться в устойчивом исходном состоянии. 1 з.п.ф-лы, 2 ил. r-V I сл ю сд 00

| Устройство для фазового управления тиристорами | 1978 |

|

SU783944A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для фазового управления вентильным преобразователем | 1977 |

|

SU693527A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-09-15—Публикация

1984-10-25—Подача