личающееся тем, что, с целью улучшения качества стабилиза1Ц1и выходного напряжения, первый вход введенного логического элемента И-НЕ подключен к выходу Q введенно1о триггера управлегшя, второй вход логического элемента И-НЕ - к выходу компаратора, а выход - через первый введенный развязывающий диод к вхо304

ду R триггера управле тя, Q которого подключен к входу введенного формирователя импульсов сброса, выход генератора хинхрокизиругацих импульсов подключен непосредственно к входу С синхронизации триггера управле1шя и через введенный второй развязываклдий диод - к входу R триггера управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный многофазный импульсный преобразователь постоянного напряжения | 1986 |

|

SU1355965A1 |

| Устройство для управления многофазным преобразователем | 1982 |

|

SU1066026A1 |

| Устройство для широтно-импульсного управления преобразователем | 1980 |

|

SU907759A1 |

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

| Преобразователь напряжения в интервал времени | 1977 |

|

SU1014140A1 |

| Преобразователь напряжения с защитой от асимметрии | 1990 |

|

SU1772877A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1559407A2 |

| Устройство для определения степени затухания измерительных магнитоэлектрических преобразователей | 1988 |

|

SU1628028A1 |

| Устройство для измерения скорости ультразвука в агрессивных средах | 1980 |

|

SU945676A1 |

1. Способ импульсной стабилизации постоянного напряжения стабилизированного преобразователя, при котором формируют импульсы синхрониза - ции и в моменты времени, совпаданяцие с передним фронтом этих импульсов, включают силовой ключ стабилизатора, измеряют выходное напряжение стабилизатора, сравнивают его с заданным напряжением, полученный сигнал рассогласования интегрируют, проинтегрированный сигнал сравнивают с пороговым напряжением и в момент их равенства выключают силовой ключ стабилизатора, при этом на периоде следования импульсов синхронизации формируют импульс сброса интегратора в исходное состояние, задний фронт которпго является началом следующего периода интегрирования, отличающийся тем, что, с целью улучшения качества стабилизации выходного напряжения, указанный импульс сброса интегратора в исходное состояние формируют в момент выключения силового ключа стабилизатора, а постоянную времени интегрирования интегратора устанавливают исходя из условия достижения напряжения на выходе интегратора величины порогового напряжения за время, равное периоду импульсов синхронизации при равенстве выходного напряжения заданному. i 2.Способ по п. 1, отличающий с я тем, что силовой ключ ста(Л С билизированного преобразователя выключают в моменты времени, совпадающие с приходом заднего фронта импульсов синхронизации в случае длительности вкл оченного состояния силорого управления ключа, стремящейся к длительности периода следования указанных импульсов синхронизации. 3.Устройство для импульсной стабилизации постоянного напряжения, содержащее включенные между входными и выходными выводами силовой ключ, LCp-фильтр, генератор синхронизирующих импульсов, источник опорного и порогового напряжений, первьм выходом соединенный с первым входом интегратора, а вторым выходом - с первым входом компаратора, вторым входом соединенного с выходом интегратора, соединенного вторым входом с выходом делителя выходного напряже1шя, ключ сброса, подключенный параллельно выходу интегратора, о т

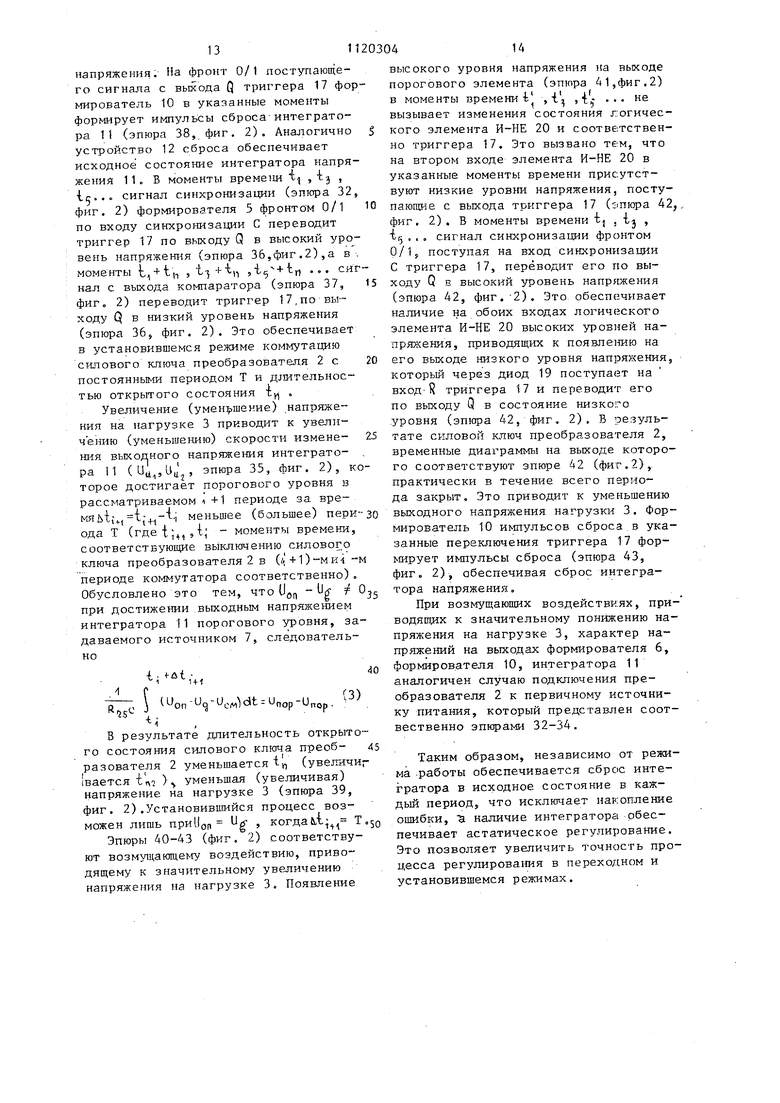

Изобретение относится к электротехнике и может быть использовано в устройствах электропитания радиоэлектронных приборов, в частности, для управления импульсными стабилиsaTOpabfli постоянного напряжения. Известен способ управления на ос нове приндапа релейного (двухпозиционного) регулирования, при котором сравнивают сигналы постоянного тона, один из которых является опорным, а другой - сигналом, пропорциональным величине входного или вькод него напряжения, в зависимости.от знака результата сравнения включают или выключают силовой управляемый ключ ll , Известно устройство для стабилизации постоянного напряжения, реализующее принцип релейного регулирования, содержащее силовой управляемы ключ, подключенный через согласующий элемент к выходу релейного элемента, вход которого подключен к выходу ста билизатора lj Недостатк.зми релейного способа и устройства для его осуществления являются отж сительно большая амплитуда пульса р{и выходной регулируемой в личины, а также зависимость частоты переключи иия силовых коммутирующих -элементов от воздействия дестабилизи рующих факторов и наличие статической ошибки регулируемой величины. Известен способ, импульсной стабилизации постоянного напряжения на основе шиpoтнo-и myльcнoй модуляции, при котором сравнивают сигнал пилообразной формы с сигналом постоянного тока и переключают силовой управляемый ключ в момент равенстЕ а этих сигналов 2J , Известно устройство для стабилизации постоянного напряжения, реализующее принцд1п широтно-импульсной модуляции, содержащее, силовой управляемый ключ, выход которого подключен через согласующий элемент к выходу широтно-импульсного модулятора, один выход которого соединен с выходом нагрузки, а другой - с генератором пилообразного напряжения 2j . Недостатком данного способа и устройства для его осуществле 1ия является малое быстродействие системы управления, в результате которого при резких изменениях входного напряжения на выходе стабилизатора наблюдаются выбросы и провалы напряжения, величина и длительность которых определяется конкретными динамическими характеристиками данного способа управления, а новое установивщееся значегше выходной регулируемой величины отличается от предыдущего квазиустановившегося.состояния. Наиболее близким к изобретению яв- лйется способ импульсной стаб1ялиэации постоянного напряжения стабил1г1зированного преобразователя, при котором формируют импульсы синхрониза:1дии и в моменты времени, совпадающие с передним (задним) фронтом этих импульсов, включают (выключают) силовой ключ стабилизатора, измеряют зыходное напряжение стабилизатора, сравнивают его с заданным напряжением, полученный сигнал рассогласования подают на вход интегратора, напряжение с выхода интегратора сравнивают с пороговым напряжением и в момент их равенства выключайт (включают) силовой клю стабилизатора, при этом на периоде следования нг-шульсов синхрониза1СНИ формируют импульс сброса интегратора в исходное состояние, задний фронт которого яв.г1яется началом следующ(-Г( лериода иитегрирования. Достоинством способа, использующего „ к омп е НС а Ц1 он и о-пара матриц ее кое регулировага- е является высокая скорость отработки входного напряжения. Устройство для осуществления извес ного способа содержит силовой ключ, 1С1)-фильтр, генератор синхронизирующих импульсов, источник опорного и порогового напряжений, первым выходом соединенный с пер.иым входом генератора, а BTopbiM выходом - с первь м входом компаратора, вторым гзходом соединенного с выходом интегратора, соединенного, вторым входом с выходом делителя выходного напряжения, и ключ сброса, подключенный параллельно выходу интегратора з1 Недостатком известных способа и устройства является статизм выходног напряжения в установившемся режиме, поскольку для работы цепи обратной связи принц1-тиально необходимо откло нение выходного напряжения от .заданной величины. Цель изобрете тя - повышение качества стабилизации выходного напряжения стабилизр рованиого преобразователя путем обеспечения астатического регулирова - ия, Эта цель достигается тем, что сог ласно способу импульсной .стабилизаци постоянного напряйсения стабилизированного преобразователя, при котором формируют и myльcы синхронизации и в моменты времени, совпадающие с передним фронтом этих импульсов, включают силовой ключ стабилизатора, измеряют выходное напряжение стабилиза тора, сравнивают его с заданным напряжением, полученный сигнал рассогл сова1гшя подают на вход интегратора, напряжение с выхода интегратора срав нивают с пороговым напряжением и в момент их равенства выключают силово ключ стабилизатора, цри этом на пери де cлeдoвaraiя импульсов синхронизации формируют импульс сброса интегра тора в исходное состояние, задний фронт которого является началом следугацего периода интегрирования, указанныЛ и шyльc сброса интегратора в исходное состояние формируют в момент выключения силового ключа стабилизатора, а постоянную времени интегрирования интегратора устанавливают исходя из условия достижения напряжения на выходе интегратора величины порогового напряжения за время, равное периоду импульсов синхронизации при равенстве выходного напряжения заданному. Кроме того, для улучшения переход ных процессов силовой ключ стабилизированного преобразователя выключают в моменты времени, совпаданщие с приходом заднего фронта импульсов синхронизации в случае длительности включенного состояния силового управляемого ключа, стремящейся к длительности периода следования указанных импульсов синхронизации. При этом в устройстве для импульсной стабилизации постоянного напряжения, содержащем включенные между входными и выходными выводами, силовой ключ, 1СО-4)Ильтр, генератор синхронизирующих импульсов, источник опорноРЬ и порогового напряжений, первым выходом соединенный с первым входом интегратора, а вторым выходом - с первым входом коьтаратора, вторым входом соединенного с выходом интегратора, соединенного вторым входом с выходом делителя выходного напряжения, и ключ сброса, подключенный параллельно выходу интегратора, первый вход введенного логического элемента И-НЕ подключен к выходу Q введенного триггера управления, второй вход логического элемента И-НЕ - к выходу компаратора, а выход - через первый введенный развязывающий диод к входу R триггера управления, выход Q которого подключен к входу введенного формирователя импульсов сброса, выход генератора синхронизирующих импульсов подключен непосредственно к входу С синхронизации триггера управления и через введенный второй развязывающий диод - к входу R триггера управления. На фиг. 1 представлена блок-схема на фиг. 2 - временные диаграммы напряжений5 на фиг. 3 - электрическая схема устройства. Преобразование электрической энер-. гии первичного источника 1 питания (фиг. 1) осуществляется стабилизироваиньм преобразователем 2 постоянного напряжения, который может быть выпаинен в зависимости от предъявляемых нагрузкой 3 требований по любой, из известных однофазных импульсньас

схем, с согласугацей цепью и силовьв-м комкуткpyю) элементами - силовой ключ э I С 0-4зил ьт р .

Блок 4 форм фовакия управляющего сигнала содержит генератор 5 иьтульсов си 1хронизации5 формирователь 6 сигнала управлеш-гя, источник 7 опорного и порогового напряжений, компаратор 8, делитель 9 выходного напряжения, форГетрователь 10 ИI iпyльcoв сброса, интегратор 11 напряжения,схему 12 сброса, источник 13 постоянного смещения и 14 сравнения (фиг,1)

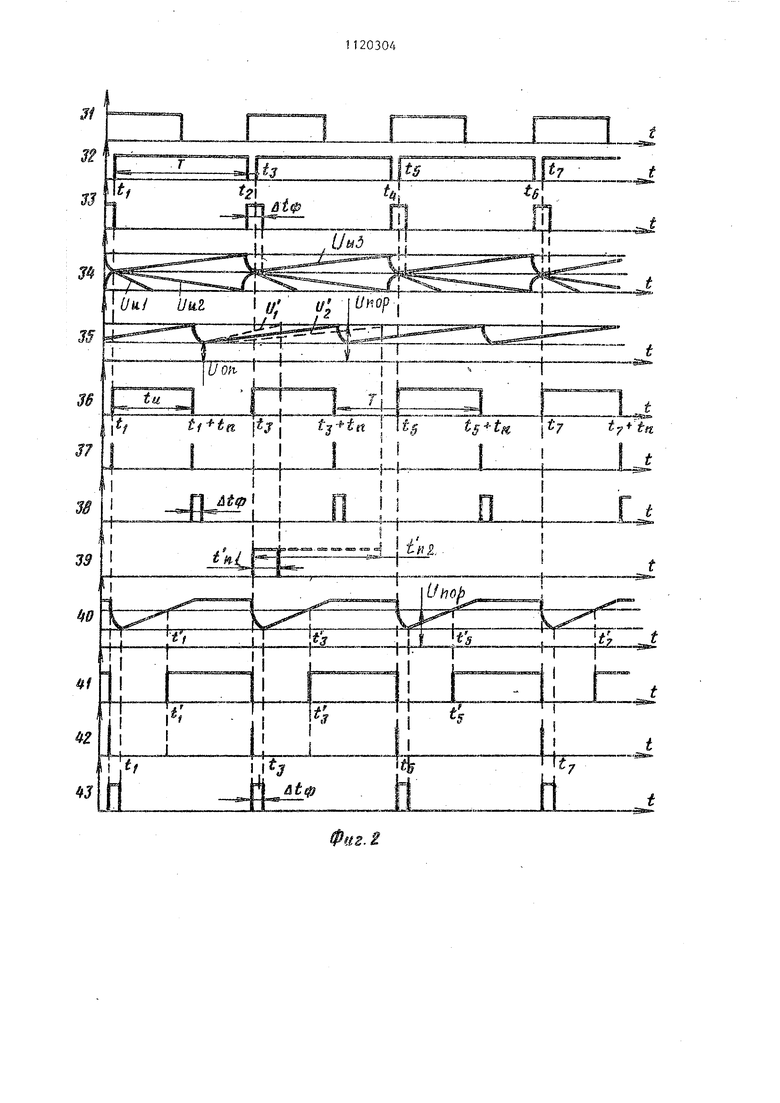

На фиг. 3 представлена С5:ема устройства для реализацни предложенного способа и.шульсной стабилизации К выходу первичного источника i питания постоянного напряжения Е/ подключен входом стабилизированный преобразователь 2 постоянного напряжекия выходом подключенный к нагрузке 3, а управляющш 1 входом - к выходу блока

4формирователя управлягацего сигнала Устройство формирования управо1яю1дего сигнала (фиг- 3) содеряшт генератор

5И1 шульсов синхронизации, формглрова тель 6 сигнала управления источ1-шк

опорного и порогового напряжений; компаратор Q делитель 9 выходного напряжения, формирователь 10 иьшульсов сброса, интегратор 11 напряжения схему 12 сброса, два источника вспомогательных напряжений: источник 13 Ег (фиг. 3)J питающий элементы аналоговой техники, источник 14 Е,. (фиг, 3)S питающий элементы цифровой техники. При этом генератор 5 импульсов синхронизации выполнен из генератора 15 прямоугольных импульсов и формирователя 16 коротких ит шульсов, формирователь 6 сигнала управления из триггера 17 управления, двук развязываювдта диодов 18 и 19 и логического элемента И-НЕ 20, формярователь 10 сброса - из Р -триггера 21, вре-мязадающей цепочки 22 и инвертора 23, интегратор 11 напряжения яз операционного усилителя 2А, конденсатора 25, резисторов 26-28, схемь-и сброса из ключа 29 сброса и согласую щсго элемента 30

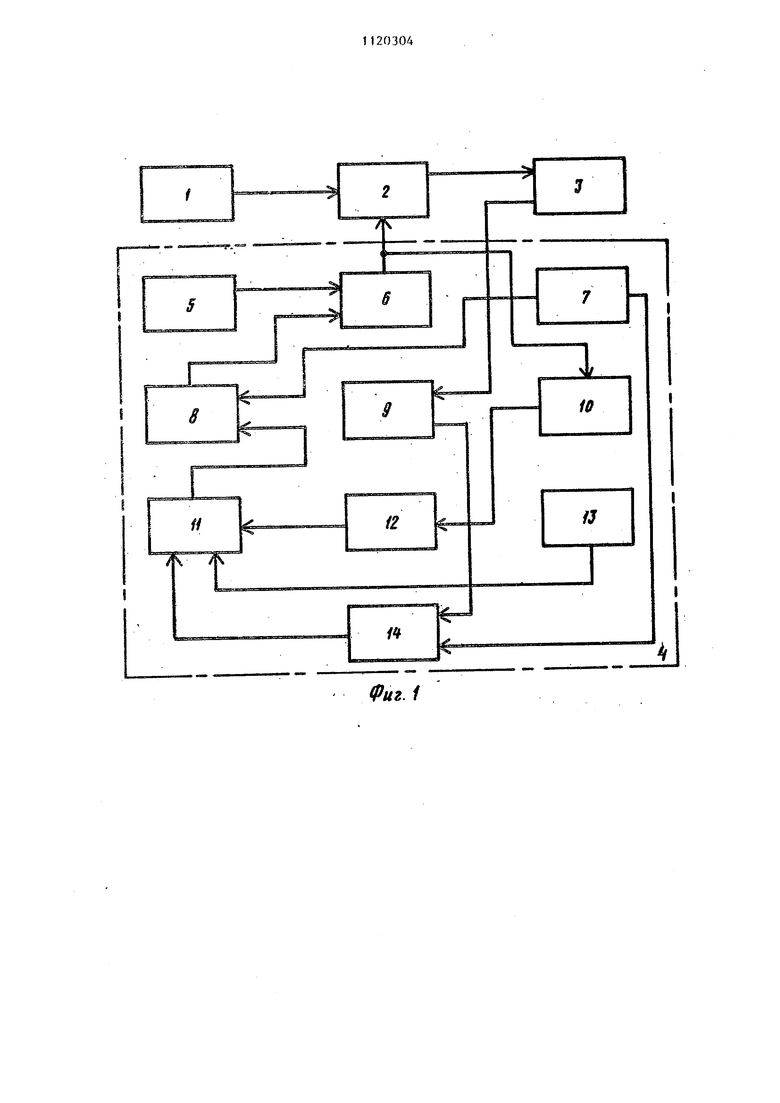

На фиг, 2 показаны временные диаrpaм fы напряжений; 31 - на выходе генератора 15 пряноуг9яьных импульсов;

32- на выхсде формирователя 16 коротких 15;-шульсов (для случая значительного уменьшегош напряжения на нагрузке 3 и на выходе триггера 17, вькоде упраапяемого ключа преобразователя 2)

33- на выходе формирователя 10 им-, пульсов синхрогшзации, 34 - на выходе интегратора 11 (установивгшкся режим) j 35 - на выходе интегратора И напряжения; 36 - на вьгходе триггера 17,, 37 - на выходе компарато)а 8 напряжений, 38 - на выходе фор в1рователя 10 и шульсов сброса (режим малых отклонений процесса регулирозаки -), 39 - на выходе триггера 17 (:зе;Еим значительного увеличения напря/кений на нагрузке 3), 40 - на выходе интегратора 11. 41 на выходе компаратора 8, 42 - на вькоде триггера 17, 43 -на выходе формкроваталя 10 импульсов сброса

Одноименные звенья блок-схемы фиг , . и устройства фигьЗэреализуюцсие предложенный способ импульсной стабилизации., имеют следующие взаимосвязи. Входные СРШОвые цепи однофазного импульсного преобразователя 2 электрической энергии подключены к вькодным )1шнам перЕичного источника 1 питания, выходные силовые цепи - к нагрузке 3,, а входные цепи управления - к блоку 4 формировагшя управлггющего сигнала- Выход генератора 5 иштульсов синхроиизации подкл сгчен к одному из входов формирователя 6 сигнала управления5 к другому входу которого подключен выход комхгаратора 8, один из входов которого подключен к источнику- 7 опорного и порогового напряжений, другой - к выходу интегратора 11 напряжения. Выход формирователя 6 сигнала управления подключен к входу управления стабилизированного пре эбразователя 2 и к входу формнроват&ля 10 импульсов сброса, выход которого соединен с входом схемы 12 сброCEj выходом подключенной к интегратору 11 напряжения. Выход нагрузки 3 подкл очек к делителю 9 напряжения, входные цепи схемы 14 сравнения (фиг„ 1) - к источнику 7 опорного напряжения и делителю 9 выходного напряженияр Выход схемы 14 сравнеHSiH (фиг, 1) подю1ючен к одноьгу из входов интегратора 11 напряжения, на другой вход которого подключен источжгк 13 постоянного смеш,(,

В устройстве (фиг. 3) функции схемы сравнения и интегратора напряжения совмещены путем подключения выхода операционного усилителя 24 через конденсатор 25 к его инвентирующему входу, который подключен через резистор 27 к источ1шку 7 опорного напряжения и через резистор 26 к источнику постоянного функци источника 13 (фиг. 1) постоянного смещения в устройстве (фиг. 3) реализует источник 7 опорного напряжения, при этом напряжение постоянного смещения .ц равно напряжению U опорного источника 7. В общем случае работа интегратора 11 не меняется, если резистор 26 подключить одним выводом к неинвертирующему входу операционного усилителя 24, а другим выводом - к источнику 7 порогового напряжения с выходным напряжением Uf,aр. При этом напряжение постоянного смещения определяется ijflp-U on з. при Unop 2l)o5, Параллельно времязадающему конденсатору 25 интегратора 11 напряжения подключен ключ 29 сброса, вход которого соединен через согласующий элемент 30 с выходом формирователя 10 импульсов сброса. Выход порогового устройства 8 подключен к одному из входов логического элемента 20, на другой вход которого подается напряжение с выхода Q триггера 17 управления, выход Q которого подключен к входу синхронизации триггера 21 формирователя 10 импульсов сброса. Выход логического элемента И-НЕ 20 подключен чере развязывающий диод 19 к входу R триггера 17 управления. Кроме того, вход R триггера 17 управления родключен через развязывающий диод 18 к общей точке соединения входа синхронизации С триггера 17 и к выходу генератора 5 импульсов синхронизации Генератор .15 прямоугольных импульсов выходом подключен к входу формирователя 16 коротких импульсов. Источник вспомогательного напряжения 14 Ес (фиг. 3)обеспечиваетэлек ропитанием блоки 5, 6 и 10. Кроме того, полюсовая шина источника 14 (фиг. 3 ) подключена к,входам1) - триггеров 17 и 21. Источник 13 (фиг. 3) вспомогательного напряжения (E,j) обеспечивает электропитанием блоки 7, 8, 11 и 12.

Сущность способа за1слючается в следующем. .

Импульсные системы регулирования с широтно-импульсным модулированием характеризуются постоянным периодом квантования, но переменной скважностью работы регулирукщего элемента при изменениях коэффициента заполнения 0 Kj i 1. В случае, если возмущающие воздействия приводят к насыщению шйротно-импульсного модулятора ШИМ (при этом коэ.ффициент заполнения равен или нулю, или единице) сигнал на выходе усилителя постоянного тока (на входе ШИМ) может значительно отличаться от граничных значений (при коэффициенте заполнения равном нулю или единице). Накопление ошибок приводит к увеличению времени переходного процесса. Кроме того, наличие статической ошибки также ухудшает качество вькодного напряжения. В предлагаемом способе указанные недостатки устраняются следующим образом.

Генератор 5 воздействует на вход формирователя 6 импульсами синхронизации, например, вида, представленного эпюрой 32, формирователь 6 обеспечивает независимо от режима работы включение силового ключа стабилизированного преобразователя 2 в моменты времени i, , t, tj. .. (эпюра 32,фиг.2), совпадаюпще с передним фронтом, положительных (или задним фронтом отрицательных) импульсов синхронизации. Формирователь 6 выключает сило вой ключ преобразователя 2 в случае воздействия на любой из его входов или сигнала с выхода компаратора 8, или сигнала с выхода генератора 5.

Рассмотрим случай, когда управляющий сигн.ал на выходе компаратора 8 отсутствует (это происходит или при включении преобразователя, или при возмущающих воздействиях, отклоняющих напряжение на нагрузке значительно ниже требуемого). В данном случае формирователь 6 в моментц времени iji, i,ig... обеспечивает запирание силового ключа преобразователя 2 и появление на выходе формирователя 10 импульсов сброса (эпюра 32, фиг.2) интегратора. Указанные импульсы сбрасывают интегратор 11 напряжения в исходное состояние . В результате в указанном режиме работы силовой ключ преобразователя 2 открыт практически в течение каждого периода (если пренебречь временем его включения, то его выходное напряжение совпадает с эпюрой 32, фиг. 2), а интегратор 11 напряжения в начале каждого периода установлен в исходное состо ние. Здесь и далее будем полагать что характер изменения во времени напряжения на выходе силового клю.ча преобразователя 2 совпадает с характером иэменения напряжения на выходе формирователя 6. В результате силовой ключ преобразователя 2 практически открыт весь период коммутации. Это приводит к увеличению напряжения на нагрузке 3. При дости жении напряжением на нагрузке 3 треб емой величины напряжение на выходе делителя 9 (на входе схемы сравнения фиг. 1) равно напряжению источника 7 опорного напряжения и приращение напряжения - сигнал рассогласования - на выходе схемы 14 сравнения (фиг. 1) равно нулю. Постоянная времени интегратора 11 напряжения выбирается из условия достижения его вольтсекундным напряжением заданного источником 7 ур ня напряжения за время, равное пери ду следования иютульсов синхронизации. Так как сигнал рассогласования на выходе схемы 14 сравнения (фиг. для рассматриваемого режима работы равен нулю, то изменение вольт-секундного напряжения на выходе интегратора обеспечивается источником 1 (фиг. 1) постоянного смещения. В мо мент равенства напряжений на входах компаратора 8 на его выходе (входе, формирователя 6) появляется управля щий сигнал. При наличии указанного сигнала формирователь 6 обеспечивае выключение силового ключа преобразо вателя 2 и сброс интегратора 11 в исходное состояние воздействием через формирователь 10 на схему 12 сб са. Характер изменения напряжений в времени для квазиустановившегося ре жима работы на выходах генератора 5, интегратора 11, формирователя 6, компаратора В, формирователя 10 импульсов сброса соответственно пред ставлен на эпюрах 32, 35, 36 и 38 (фиг. 2). Таким образом, включение лового ключа преобразователя 2 прои водится независимо от режима работы в момент времени i, , i j-tj , i:-j ... (эпюры 32 и 36, фиг. 2). Выключение ключа производится или сигналом с в хода генератора 5 в конце каждого периода в моменты времени i . i , , ... (эпюра 32, фиг. 2), если нет управляющего сигнала на выходе компаратора 8, или сигналом с выхода компаратора 8, например, в моменты времени i, 4-i ,i +i,.,, (эпюра 36, фиг. 2) при наличии управляю- . щего сигнала на выходе компаратора 8 (эпюра 37, фиг. 2). Причем в квазиуетановившемвя режиме сигнал рассогласования, т.е. разность выходного напряжения делителя 9 и заданного опорного IJ(jf| источника 7, равен нулю. При этом выключегдае силового ключа производится через интервал времени, равный периоду сигнала синхронизации генератора 5. Это обеспечивается выбором постоянной времени интегрирования интегратора 11 и величиной напряжения источника 13 постоянного смещения. При увеличении (уменьшении) напряжения на нагрузке 3 напряжение на выходе делителя 9 увеличивается (уменьшается), соответственно на выходе схемы 14 сравнения (фиг. 1) появляется сигнал рассогласования. Появление сигнала рассогласования на входе интегратора 11 приводит к увел1-ше№ ю (уменьшению) скорости изменения пилообразного напряжения на его выходе, В резуи;1 тате напряжение на выходе, интегратора 11 достигает порогового уровня раньше У 5 эпюра 35 фиг. 2 (позже -Uo V длительность открытого состояния управляемого ключа уменьшается - i эпюра За, фиг. 2 - (увеличится tnJ . Соответственно напряжение на нагрузке 3 уменьшается (увеличивается) . Установившийся процесс возможен лишь в случае равенства напряясеннй на выкоде делителя 9 и на выходе источника 7 опорного напряжения, лишь в этом случае интервал между моментами выключения равен периоду сигнгила синхронизации генератора 5. На примере реализации устройства фиг. 3 рассмотрим основные релсимы работы данного способй импульсной стабили ции. В момент подключения источника 1 пита1ия к преобразователю 2 нгшряжение на нагрузке 3 равно нулю. Считаем, что источники 13 и 14 (фиг. 3) вспомогательных напряжений /включаются или раньше, игш одновременно с источником 1. Напряжение, подаваемое на инвертирующий вход операционного усилителя 24, определяется соотношением резисторов 27 и 26. Для данного режима они образуют делитель напряжения опорного источника 7. Напряжение, подаваемое на неинвертирующий вход операиионного усилителя 24 с выхода делителя 9, равно нулю, поэтому напряжение на выходе интегратора 11 практически совпадает с осью времени эпюры 34 (фиг „ 2). На входе компаратора 8 управляющий сигнал отсутст вует (выходное напряжение равно практически нулю). Характер вькодного напряжения на выходе силового ключа пре образователя 2 полностью совпадает с характером сигнала синхронизации генератора 5 (эпюра 32, фиг. 2). В момент времени t, , t , -tg ... сигнал син хронизации перепадом 0/1 переводит триггер 17 управления по выходу Q в .состояние высокого 10 уровня (эпюра 32, фиг. 2), так как по входу S триггера 21 присутствует высокий уровень ( с источника 14 (фиг. 3). В рассматриваемом режиме работы управляюшрй сигнал с выхода компаратора 8 отсутствует, поэтому переключение триггера 17 по выходу Q с высокого уровня напряжения в низкий уровень происходит в конце каждого периода в моменты времени, tj , t4 6 отрицательным перепадом 1/0 синхронизации (эпюра 32, фиг. 2). Указан ный сигнал синхронизации подается че рез развязывающий диод 18 на вход R триггера 17. Соответственно на выходе Q триггера 17 в Указанные моменты времени появляются высокие уровни напряжения. На перепад 0/1 напряжения выхода Q триггера 17 управления формирователь 10 импульсов сброса формирует положительный импульс (эпю ра 33, фиг. 2), длительность которого задается выбором параметров времязадающей цепочки 22 и выбирается и условия обеспечения сброса интегратора II в исходное состояние. Сброс интегратора 11 производится ключом 29 сброса, открываемым на интервале вре мени сигналом, поступающим через согласукяций элемент- 30 с формирователя 10. Поскольку ключ преобразователя 2 практически открыт в течение всего периода (эпюра 32, фиг. 2), то напряжение на нагрузке 3 увеличивается. По мере приближения напряжения на нагрузке 3 к установившемуся значению напряжение на выходе инте- гратора 11 последовательно занимает положение, совпадающее с осью sp&мениЦ ,Uj,, и (( (эпюра 34, фиг. 2) и в установившемся режиме имеет вид, представленный эпюрой 35 (фиг. 2). Данный режим работы характеризуется равенством напряжений Одп g подаваемых на входы схемы 14 (фиг.1) сравнения с источника 7 опорного напряжения и делителя 9 выходного напряжения. В устройстве, показанном на фиг. 3, функции схемы сравнения совмещены в операционном усилителе 24, работающем в режиме интегрирования благодаря емкостной обратной связи через конденсатор 25 (С)i Для данного схематического решения (фиг.З) параметры элементов выбираются из условия обеспечения интервала межд моментами выключения силового ключа преобразователя 2, равного периоду синхронизации Т: . Соотношение (1) позволяет определить входное сопротивление R интегратора 11 при заданном С или кондент сатора емкостной обратной связи при заданном S,, , например, для С имеем - пор -оп Выбор параметров устройства (фиг. 3) согласно соотношения (2) обеспечивает в установившемся состоянии достижение вольт-секундного напряжения на выходе интегратора 11 порогового значения за время, рав-г нов Т. При этом напряжение на выхрде делителя Urt равно напряжению .U . В моменты времени t, t , t + у 5 Ц на выходе компаратора 8 появляется управляющий сигнал - высокий уровень напряжения (эпюра 37, фиг. 2), поступающий на один из входов элемента И-НЕ 20. На другом входе логического элемента 20 в указанные моменты времени присутствуют Е ысокие уровни напряжений, поступающие с выхода .Q триггера 17 (эпюра 36, фиг. 2).Это обеспечивает появление низкого уровня напряжения на выходе элемента И-НЕ 20, который, проходя через диод 19 на вход триггера 17, переключает выход Q с высокого на низкий уровень 131 напряжения. На фронт 0/1 поступающего сигнала с выхода Q триггера 17 фо мирователь 10 в указанные моменты формирует импульсы сбросаинтегратора 11 (эпюра 38, фиг. 2). Аналогично устройство 12 сброса обеспечивает исходное состояние интегратора напря жений 11. В моменты времетш i , tj , ic..o сигнал синхронизации (эпюра 32 фиг. 2) формирователя 5 фронтом 0/1 по входу синхронизации С переводит триггер 17 по выходу Q в высокий уро вень напряжения (эпюра 36,фиг.2),а в моменты t, + t,T , си нал с выхода компаратора (эпюра 37, фиг о 2) переводит триггер 17,по выходу Q в низкий уровень напряжения (эпюра 36, фиг. 2). Это обеспечивает в установившемся режиме коммутации) силового ключа преобразователя 2с постоянными периодом Т и длительностью открытого состояния Ту , Увеличение (уменьшение) напряжения на агрузке 3 приводит к увеличению (уменьшению) скорости изменеНИН выходного напряжения интегратора П (, эпюра 35, фиг. 2), к торое достигает порогового уровня в рассматриваемом i +1 периоде за вре MHbt,, меньшее (большее) пери ода Т (где i;., Д; -HI- моменты времени, соответствующие выключению силового ключа преобразователя 2 в (4+1)-ми1 периоде коммутатора соответственно). Обусловлено это тем, что ( i при достижении выходным напряжением интегратора 11 порогового уровня, за даваемого источником 7, следовательноЧ, 7 Uon-U 3-U,.,,)dtrUnop-Unop. с5 , . в результате длительность открыто го состояния силового ключа преобразователя 2 уменьшается t,, (увеличи вается t ) уменьшая (увеличивая) напряжение на нагрузке 3 (эпюра 39, фиг. 2).Установившийся процесс возможен лишь при ПОР Ug- , когдаЬ,г Т Эпюры 40-43 (фиг. 2) соответствуют вoзмyu aюш, воздействию, приводящему к значительному увеличению напряжения на нагрузке 3. Появление 4 высокого уровня напряжения на выходе порогового элемента (эпюра 41,фиг.2) в моменты времени i , i, , V- не вызывает изменения состояния логического элемента И-НЕ 20 и соотве:тственно триггера 17. Это вызвано тб1м, что на втором входе элемента И-НЕ 20 в указанные моменты времени присутствуют низкие уровни напряжения, поступающие с выхода триггера 17 (эпюра 42,, фиг. 2). В моменты времени tj , ij , 5- сигнал синхронизации фронтом 0/1, поступая на вход синхронизации С триггера 17, переводит его по выходу Q Б высокий уровень напр шения (эпюра 42, фиг. -2). Это обеспечивает наличие на обоих входах логического элемента И-НЕ 20 высоких уровней напряжения, приводящих к появлению на его выходе низкого уровня напряжения, которьш через диод 19 поступает на вход-R триггера 17 и переводит его по выходу Q в состояние низкого уровня (эпюра 42, фиг, 2). В результате силовой ключ преобразователя 2, временные диагранмь на выходе которого соответствуют эпюре 42 (фиг.2),. практически в течение всего периода закрыт. Это приводит к уменьшению выходного напряжения нагрузки 3. Формирователь 10 и fflyльcoв сброса, в указанные переключения триггера 17 фор шpyeт импульсы сброса (эпюра 43, фиг. 2), обеспечивая сброс интегратора напряжения, При возмущающих воздействиях, приВОДЯШД1Х к значительному понижению напряжения на нагрузке 3, характер напряжений на выходах формирователя 6, формирователя 10, интегратора 11 аналогичен случаю подключения преобразователя 2 к первичному источнику питания, который представлен соотвественно эпюрами 32-34. Таким образом, независимо от режима .работы обеспечивается сброс интегратора в исходное состояние в каждый период, что исключает накопление ошибки, а наличие интегратора обеспечивает астатическое регулирование. Это позволяет увеличить Точность процесса регулирования в переходном и установившемся режимах.

f1

М/

10

fj

Фиг.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бокуняев А.А | |||

| Релейные стабилизаторы постоянного напряжения.М., Энергия, 1978, с | |||

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| (Проектирование и расчет) | |||

| Под ред | |||

| Ю.И.Конева | |||

| М., Советское радио, 1967, с | |||

| Канатное устройство для подъема и перемещения сыпучих и раздробленных тел | 1923 |

|

SU155A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-10-23—Публикация

1982-07-30—Подача