Изобретение относится к импульсной технике, а именно к устройствам с несколькими устойчивыми состояниями.

Цель изобретения - увеличение надежности путем упрощения устройства,

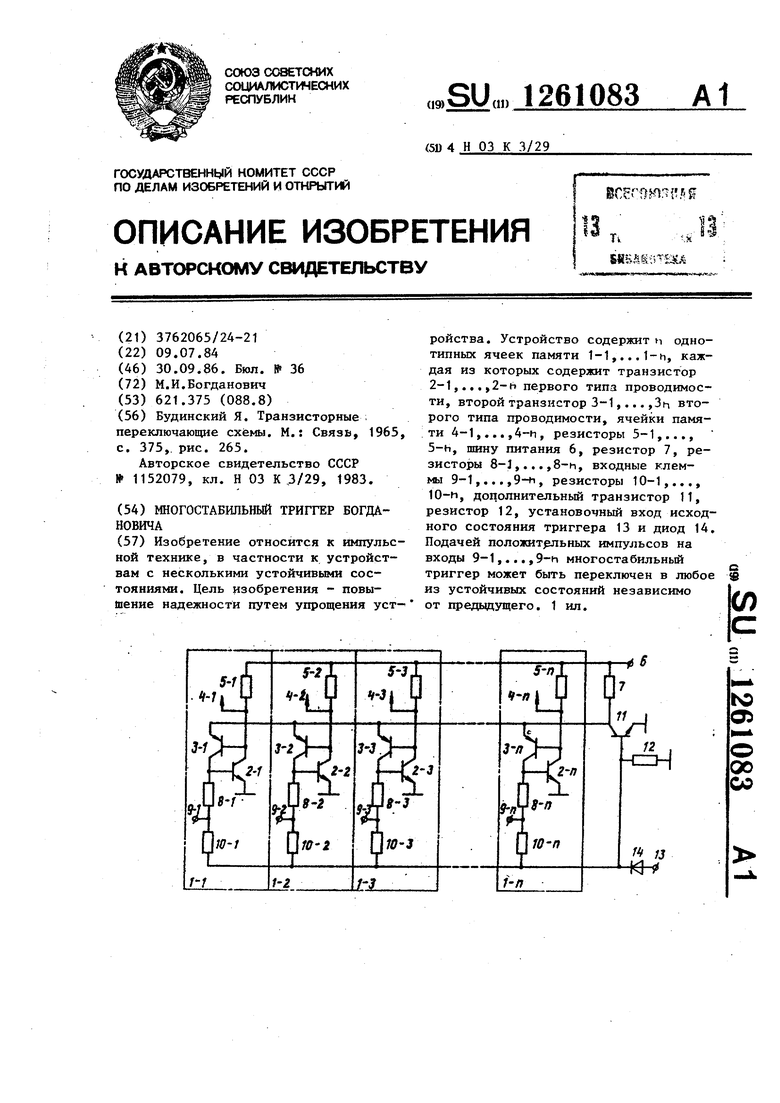

На чертеже приведена принципиальная электрическая схема многостабильного триггера.

Многоетабильный триггер содер- ашт м однотипных ячеек памяти 1-15,.., 1-h, каждая из которых содержит первый транзистор 2-1,.,.,2-h первого ипа проводимости, эмиттер которого Соединен с общей шиной, база и коллектор соединены соответственно с коллектором и базой второго транзистора 3-1,...,3-й второго типа про- йодимости, коллектор первого тран- фистора соединен с выходной шиной 5|1чейки памяти 4-1,...,4-h и через первый резистор 5-5,...,5-и подключен к шине питания 6. Эмиттеры вторых транзисторов 3-1,... ,3-и через общий для всех ячеек второй резис- top 7 подключены к шине питания 6. Базы первых транзисторов 2-1,...,

2-ь через соответствукщие третьи резисторы 8-1,...,8-h соединены с установочными входами 9-1,... 9-h , - Которые через четвертые резисторы 10-1,...,10-и соединены с базой дополнительного транзистора 11, которая через пятый резистор 12 соединена с змиттером и общей шиной, коллектор дополнительного транзистора р1 соединен с змиттером вторых транзисторов ячеек.

Установочный вход 13 исходного состояния триггера через диод 14 соединен с базой транзистора 11.

Многостабильный триггер работает следующим образом.

При включении питания все ячейки памяти 1-1,... 1-h триггера выключены, все транзисторы закрыты. На всех выходах высокие потенциалы. В этом исходном состоянии триггер практически не потребляет энергии от источника питания.

При поступлении положительного импульса на один из входов 9-1,..., 9-h, например на вход 9-1, возникает ток через резистор 8-1, который открывает и насыщает транзистор 2-1. Потенциал на выходе становится ным нулю.Одновременно возникает через резистор 10-1, который открывает и

0

переключает в насыщенное состояние транзистор 11.

После окончания импульса на входе 9-1 транзистор 11 закрывается быстрее, чём транзистор 2-1, так как степень насыщения транзистора 2-1 значительно вьпие степени насыщения транзистора 11 (для чего необходимо соответствующим образом выбрать величины резисторов 9-1 и 10-1). Потенциал на коллекторе транзистора 11, а следовательно, на эмиттерах транзисторов 3-1J..., возрастает, что приводит к открыванию транзистора , ток коллектора которого прекращает рассасывание неосновных носителей в базе транзистора 2-1, и транзистор 2-1 остается в насыщенном состоянии за счет тока коллектора транзистора 3-1, т.е. ячейка 1-1 остается во включенном состоянии после окончания импульса на входе 9-1.

Если в этом состоянии многостабильного триггера поступает положите- льный импульс на любой из входов, кроме первого 9-1, то происходит следующее. Допустим, поступает импульс на вход 9-h , через резистор возникает ток, который открывает и насыщает транзистор 2-и . Одновременно возникает ток через резистор 10-ь,открывается и входит в насыщение транзистор 11. Потенциал на эмиттерах транзисторов 3-1,...,3-h снижается до нуля, исчезает ток эмиттера транзистора 3-1, что приводит к закрьшанию последнего. Исчезает ток коллектора транзистора 3-1 и тран- зиотор 2-1 также закрывается, что 0 приводит к выключению первой ячейки. Потенциал на шине 4-н уменьшается до нуля. После окончания импульса на входе 9-h транзистор 11 закрывается быстрее, чем транзистор 2-h, и по- этому открывается транзистор 3-h и ячейка 1-h остается во включенном состоянии.

0

)

5

5

Таким образом, подачей положитель- ных импульсов на входы 9-1,...,9-h многостабильный триггер может быть переключен в любое из устойчивых состояний независимо от предьздущего.

При поступлении положительного им- пульса на вход 13 транзистор 11 входит в насьш;ение и все ячейки выключаются, т.е. триггер переключается в исходное состояние.

Формула изобретений

Многостабильный триггер, содержащий п однотипных ячеек памяти, каждая из которых содержит установочный вход, 5 первый транзистор первого типа проводимости, эмиттер которого соединен с общей шиной, а Эаза и коллектор соединены соответственно с коллектором и базой второго транзистора ,второго типа проводимости, коллектор первого транзистора соединен с выходной шиной ячейки памяти и через первый резистор соединен с шиной питания, и общий для всех ячеек второй 5 резистор, первый вывод которого соещ и и с я

тем, что, с целью увеличения надежности, эмиттеры вторых транзисторов всех ячеек соединены с вторым выводом второго резистора, базы первых трензисторов всех ячеек соединены соответственно через третьи резисторы с установочными входами ячеек, которые через четвертые резисторы соединены с базой дополнительного транзистора, общего для всех ячеек, и катодом диода, анод которого соединен с установочным входом исходного состояния триггера, база дополнительного транзистора через первый резистор соединена с эмит тером и общей шиной,а коллектор соеди-

динен с шиной питания, отличаю- иен с вторым выводом второго резистора,

й

1261083

щ и и с я

тем, что, с целью увеличения надежности, эмиттеры вторых транзисторов всех ячеек соединены с вторым выводом второго резистора, базы первых трензисторов всех ячеек соединены соответственно через третьи резисторы с установочными входами ячеек, которые через четвертые резисторы соединены с базой дополнительного транзистора, общего для всех ячеек, и катодом диода, анод которого соединен с установочным входом исходного состояния триггера, база дополнительного транзистора через первый резистор соединена с эмиттером и общей шиной,а коллектор соеди-

| название | год | авторы | номер документа |

|---|---|---|---|

| Многостабильный триггер | 1986 |

|

SU1309263A1 |

| Многостабильный триггер Богдановича | 1984 |

|

SU1211855A1 |

| Многостабильный триггер М.И.Богдановича | 1983 |

|

SU1152079A1 |

| Многостабильный триггер | 1988 |

|

SU1554113A1 |

| МНОГОСТАБИЛЬНЬШ ТРИГГЕР | 1973 |

|

SU375801A1 |

| Кольцевой счетчик | 1988 |

|

SU1539997A1 |

| Кольцевой счетчик | 1988 |

|

SU1539998A1 |

| Четырехуровневый триггер | 1982 |

|

SU1056268A1 |

| Многостабильный триггер | 1979 |

|

SU819971A1 |

| Многостабильный триггер | 1983 |

|

SU1160542A1 |

Изобретение относится к импульсной технике, в частности к устройствам с несколькими устойчивыми состояниями. Цель изобретения - повышение надежности путем упрощения уст-ройства. Устройство содержит ц однотипных ячеек памяти 1-1,...1-ц, каждая КЗ которых содержит транзистор 2-1,...,2-Н первого типа проводимости, второй транзистор 3-1,... ,3h второго типа проводимости, ячейки памяти 4-1,...,4-п, резисторы 5-1,..., 5-h, шину питания 6, резистор 7, резисторы 8-J,...,8-h, входные клем- 9-1,...,9-ь, резисторы 10-1,..., 10-и, дополнительный транзистор 11, резистор 12, установочный вход исходного состояния триггера 13 и диод 14. Подачей положительных импульсов на входы 9-1,...,9-h многостабильньй триггер может быть переключен в любое из устойчивых состояний независимо от предыдущего. 1 ил. (Л S и - i

| Будинский Я | |||

| Транзисторные; переключающие схемы | |||

| М.: Связь, 1965, с | |||

| Ручной дровокольный станок | 1921 |

|

SU375A1 |

| САННЫЙ ВЕЛОСИПЕД С ВЕДУЩИМ КОЛЕСОМ, СНАБЖЕННЫМ ШИПАМИ | 1921 |

|

SU265A1 |

| Многостабильный триггер М.И.Богдановича | 1983 |

|

SU1152079A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-30—Публикация

1984-07-09—Подача