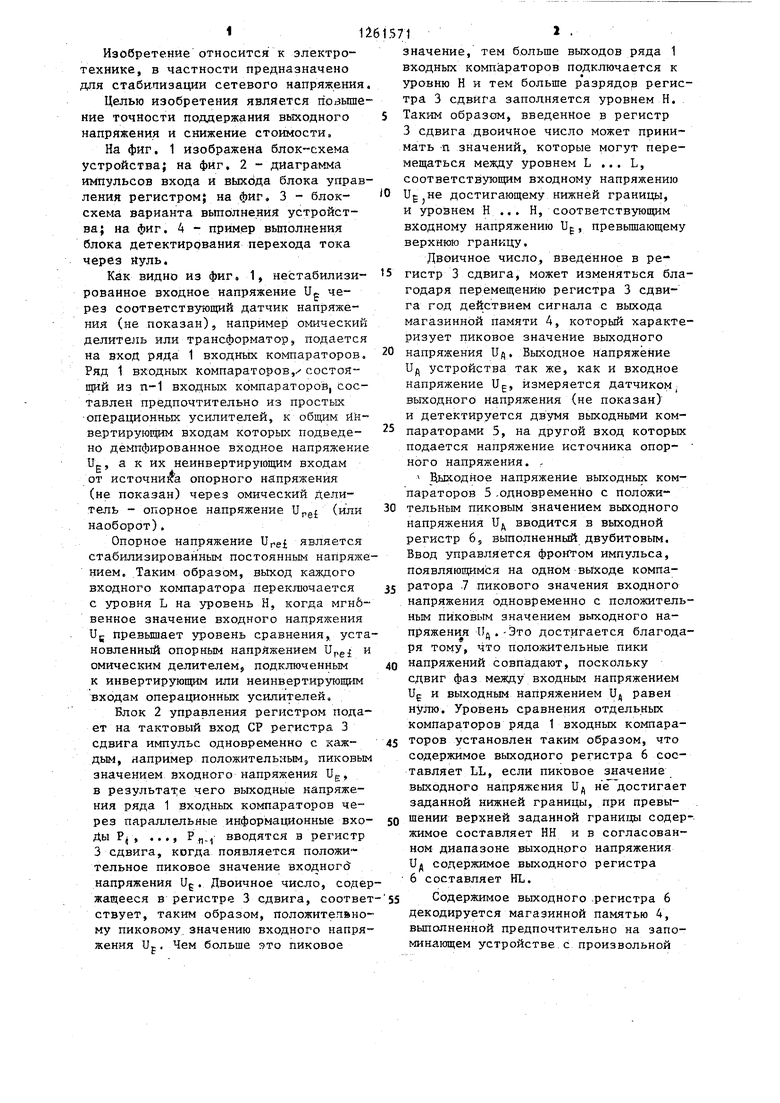

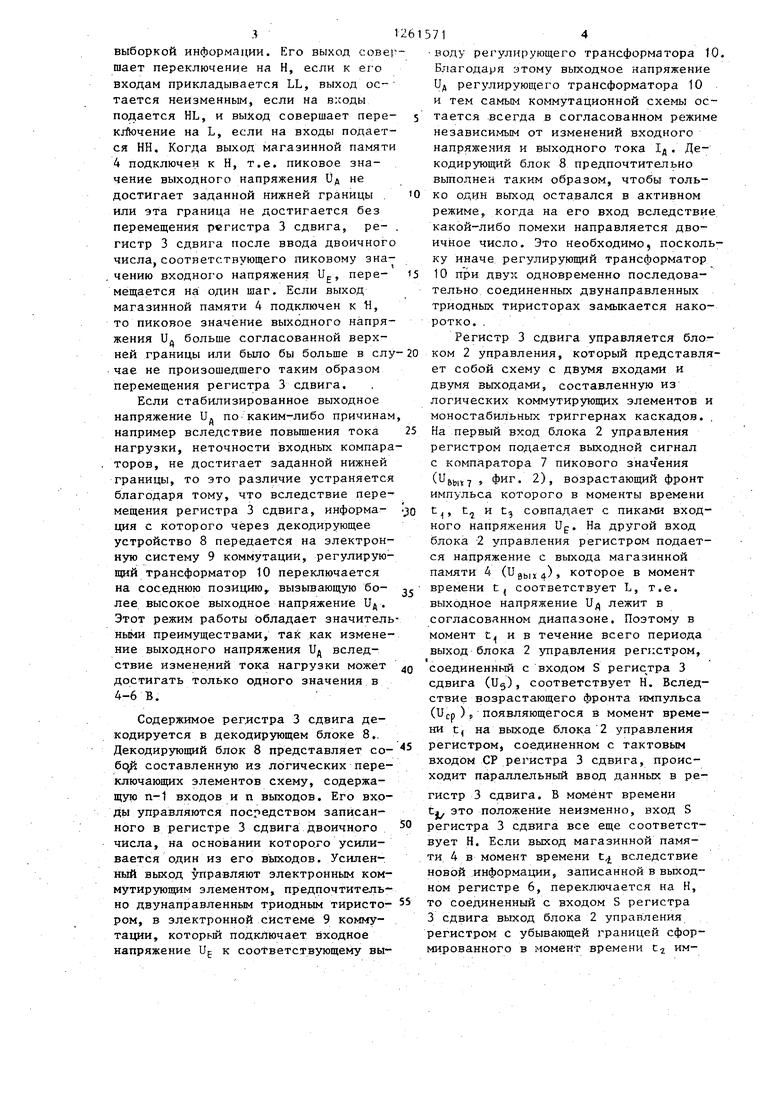

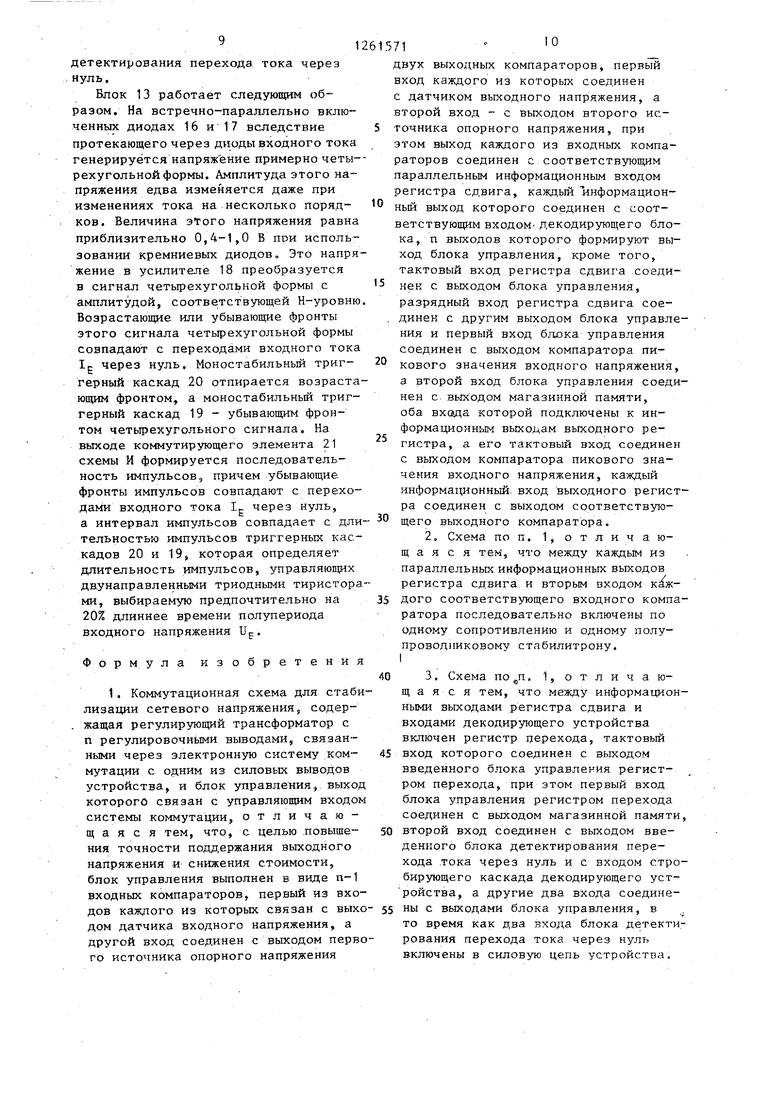

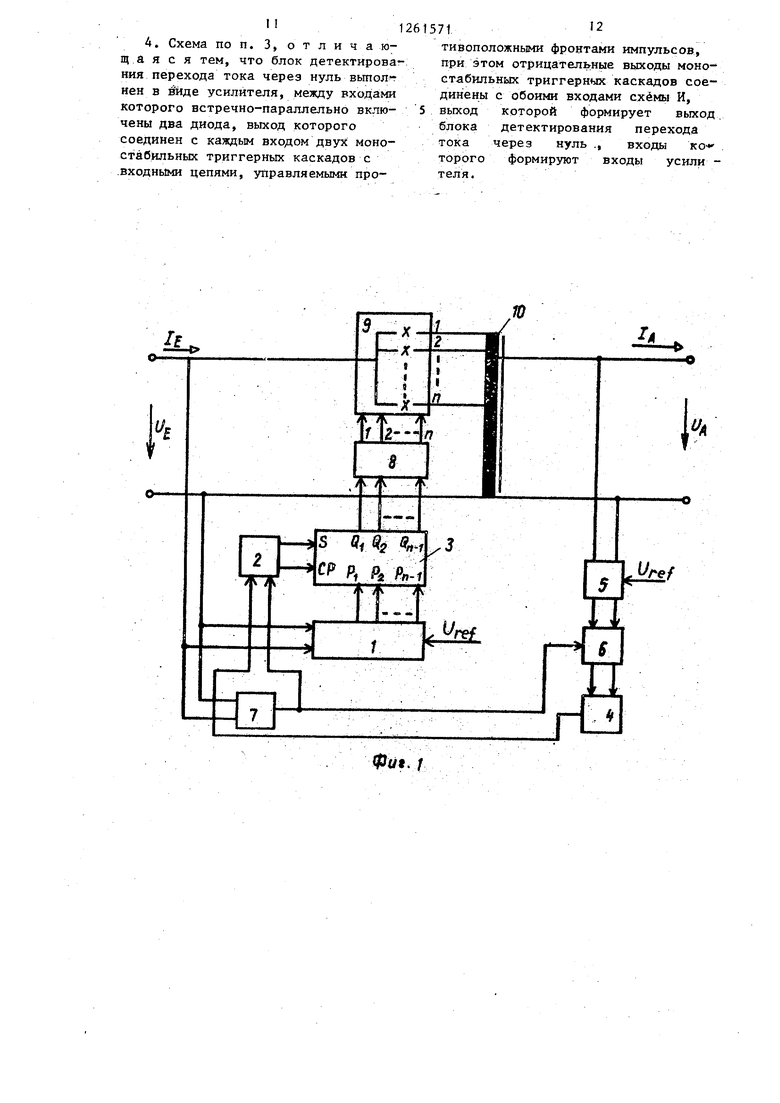

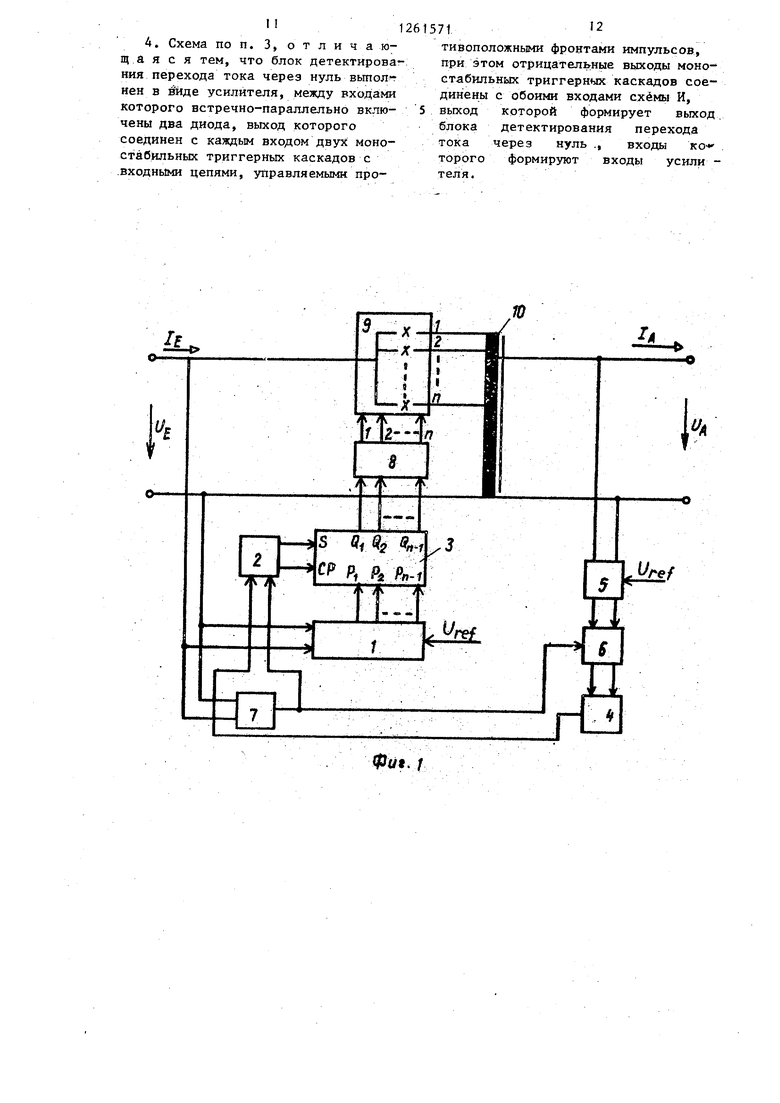

Изобретение относится к электротехнике, в частности предназначено для стабилизации сетевого напряжения Целью изобретения является повыше ние точности поддержания выходного напряжения и снижение стоимости. На фиг. 1 изображена блок-схема устройства; на фиг, 2 - диаграмма импульсов входа и выхода блока управ ления регистром; на фиг, 3 - блоксхема варианта вьтолнения устройства; на фиг, 4 - пример вьтолнения блока детектирования перехода тока через нуль. Как видно из фиг, 1, нестабилизированное входное напряжение U через соответствующий датчик напряжения (не показан), например омический делитель или трансформатор, подается на вход ряда 1 входных компараторов Ряд 1 входных компараторов, состоящий из п-1 входных компараторов, составлен предпочтительно из простых операционных усилителей, к общим йй вертирующим входам которых подведено демпфированное входное напряжени Ug, а к их неинвертирующим входам от источника опорного напряжения (не показан) через омический. Делитель - опорное напряжение Upg (или наоборот) . Опорное напряжение является стабилизированным постоянным напряж нием, .Таким образом, выход каждого входного компаратора переключается с уровня L на уровень Н, когда мгнб венное значение входного напряжения Ug превышает уровень сравнения, уст новленный опорным напряжением Upg.f омическим делителем, подключенным к инвертирующим или неинвертирующим входам операционных усилителей. Блок 2 управления регистром пода ет на тактовый вход СР регистра 3 сдвига импульс одновременно с к;1ждым, например положительныМэ пиковы значением, входного напряжения Ug, в результате чего выходные напряжения ряда 1 входных компараторов через параллельные информационные вхо ды PJ, ..., Pfl-v вводятся в регистр 3 сдвига, когда появляется положительное пиковое значение входногд напряжения Ug, Двоичное число, соде жащееся в регистре 3 сдвига, соотве ствует, таким образом, положитепйно му пиковому,значению входного напря жения UE. Чем больше это пиковое значение, тем больше выходов ряда 1 входных компараторов подключается к уровню Н и тем больше разрядов регистра 3 сдвига заполняется уровнем Н. Таким образом, введенное в регистр 3 сдвига двоичное число может принимать п значений, которые могут перемещаться между уровнем L ,.. L, соответствующим входному напряжению Ug не достигающему нижней границы, и уровнем Н .,, Н, соответствующим входному напряжению Ug, превьшающему верхнюю границу. Двоичное число, введенное в регистр 3 сдвига, может изменяться благодаря перемещению регистра 3 сдвига год действием сигнала с выхода магазинной памяти 4, который характеризует пиковое значение выходного напряжения U, Выходное напряжение Цд устройства так же, как и входное напряжение U, измеряется датчиком: выходного напряжения (не показан) и детектируется двумя выходными комлараторами 5, на другой вход которых подается напряжение источника опорного напряжения, , Дыходное напряжение выходных компараторов 5 .одновременно с положительным пиковым значением выходного напряжения Ид вв.одится в выходной регистр 6, вьтолненный двубитовым. Ввод управляется фронтом импульса, появляющимся на одном выходе компаратора 7 пикового значения входного напряжения одновременно с положительным пиковым значением выходного напряжения Un , -Это достигается благода ч ря тому, что положительные пики напряжений совпадают, поскольку сдвиг фаз между входным напряжением Ug и выходным напряжением U равен нулю. Уровень сравнения отдельных компараторов ряда 1 входных компараторов установлен таким образом, что содержимое выходного регистра 6 составляет LL, если пиковое значение выходного напряжения U не достигает заданной нижней границы, при превышении верхней заданной границы содержимое составляет НН и в согласованном диапазоне выходного напряжения Цд содержимое выходного регистра 6 составляет HL, Содержимое выходного .регистра 6 декодируется магазинной памятью 4, выполненной предпочтительно на запоминающем устройстве с произвольной л выборкой информации. Его выход сове шает переключение на Н, если к его входам прикладывается LL, выход остается неизменным, если на входы подается HL, и выход совершает пере кЛйчение на L, если на входы подает ся НН. Когда выход магазинной памят 4 подключен к Н, т.е. пиковое значение выходного напряжения Од не достигает заданной нижней границы . или эта граница не достигается без перемещения регистра 3 сдвига, регистр 3 сдвига после ввода двоичног числа, соответствующего пиковому зна чению входного напряжения Ug, перемещается на: один шаг. Если выход магазинной памяти 4 подключен к Н, то пиковое значение выходного напря жения и больше согласованной верхней границы или было бы больше в сл чае не произошедшего таким образом перемещения регистра 3 сдвига. Если стабилизированное выходное напряжение U по каким-либо причинам например вследствие повьппения тока нагрузки, неточности входных компара торов, не достигает заданной нижней границы, то это различие устраняется благодаря тому, что вследствие перемещения регистра 3 сдвига, информация с которого через декодирующее устройство 8 передается на электронную систему 9 коммутации, регулирующий трансформатор 10 переключается на соседнюю позицию,, вызывающую более высокое выходное напряжение Пд. Этот режим работы обладает значитель ными преимуществами, тай как изменение выходного напряжения ид вследствие изменений тока нагрузки может достигать только одного значения в 4-6 В. Содержимое регистра 3 сдвига декодируется в декодирующем блоке 8.. Декодирующий блок 8 представляет собс составленную из логических переключающих элементов схему, содержащую п-1 входов и п выходов. Его входы управляются посредством записанного в регистре 3 сдвига двоичного числа, на основании которого усиливается один из его выходов. Усиленный выход управляют электронным коммутирующим элементом, предпочтительно двунаправленным триодным тиристо ром, в электронной системе 9 коммутации, который подключает входное напряжение U к соответствующеь гу вы714 воду регулирующего трансформатора 10. Благодаря этому выходное напряжение Уд регулирующего трансформатора 10 и тем самым коммутационной схемы остается всегда в согласованном режиме независимым от изменений входного напряжения и выходного тока 1д. Декодирующий блок 8 предпочтительно выполнен таким образом, чтобы только один выход оставался в активном режиме, когда на его вход вследствие какой-либо помехи направляется двоичное число. Это необходимо, поскольку иначе регулирующий трансформатор 10 при двух одновременно последовательно соединенных двунаправленных триодных тиристорах замыкается накоротко. . Регистр 3 сдвига управляется блоком 2 управления, который представляет собой схему с двумя входами и двумя выходами, составленную из логических коммутирующих элементов и моностабильных триггернах каскадов. На первый вход блока 2 управления регистром подается выходной сигнал с компаратора 7 пикового значения ( , фиг. 2), возрастающий фронт импульса которого в моменты времени t, t и t совпадает с пиками входного напряжения Up. На другой вход блока 2 управления регистром подается напряжение с выхода магазинной памяти 4 (U8bix4- которое в момент времени t соответствует L, т.е. выходное напряжение U лежит в согласованном диапазоне. Поэтому в момент t;| ив течение всего периода выход блока 2 управления регистром, . - ., соединенный с входом S регистра 3 сдвига (Ug), соответствует Н. Вследствие возрастающего фронта импульса (и (.р ) 5 появляющегося в момент времени t( на выходе блока2 управления регистром, соединенном с тактовым входом СР регистра 3 сдвига, происходит параллельный ввод данных в регистр 3 сдвига. В момент времени tj это положение неизменно, вход S регистра 3 сдвига все еще соответствует И. Если выход магазинной памяти 4 в момент времени с вследствие новой информации, записанной в выходном регистре 6, переключается на Н, то соединенный с входом S регистра 3 сдвига выход блока 2 управления егистром с убывающей границей сфорированного в момент времени с им512

пульса одновременно переключается на LC В свкзи с возрастающей границей сформированного в момент времени t,, импульса на входе СР регистра 3 сдвига происходит смещение вместо ввода в регистр 3 сдвига. После этого оба выхода блока 2 управления регистра возвращаются в исходное состояние, и в момент времени t описанный выше процесс повторяется до тех пор, пока выходное напряжение ид не превысит заданную верхнюю границу, вследствие чего содержимое магазинной памяти 4 (и тем самым ее выход) переключается на L,

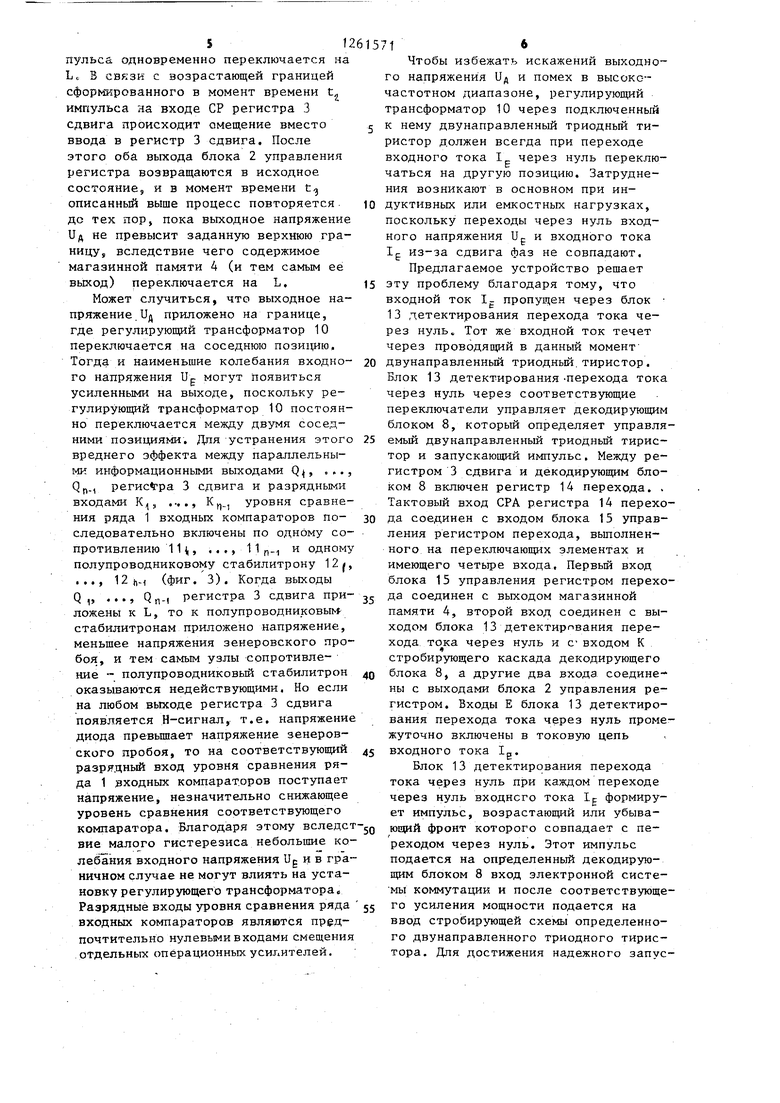

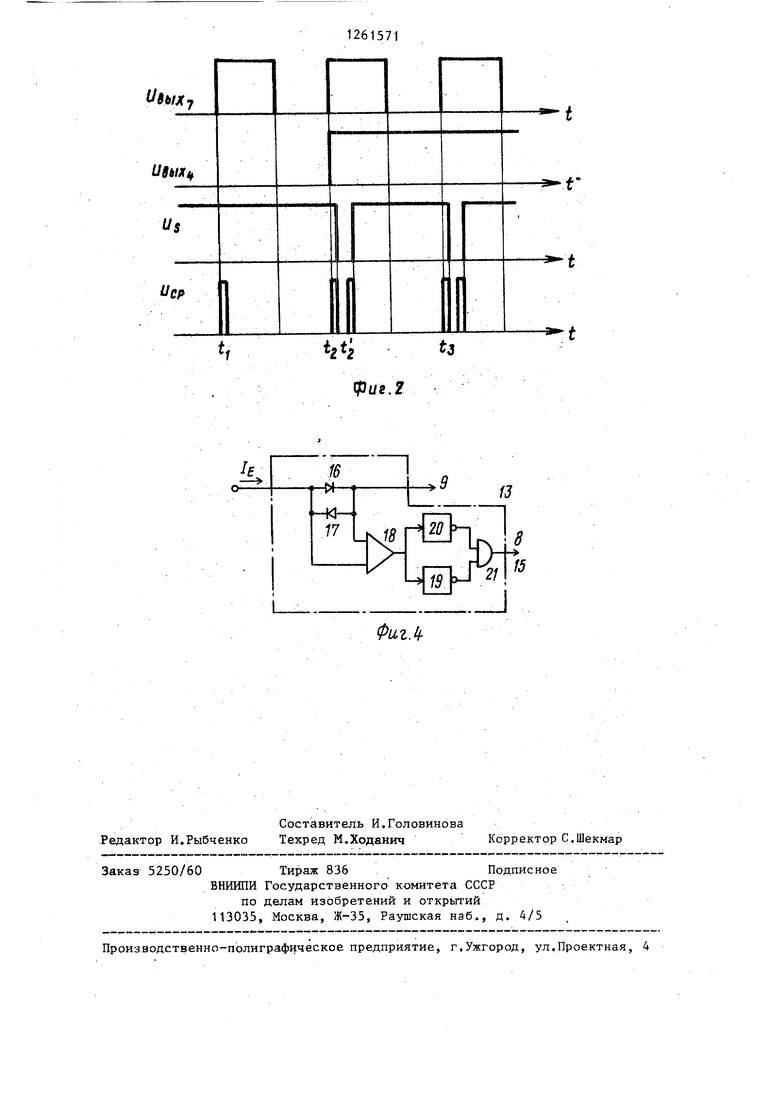

Может случиться, что выходное напряжение Цд приложено на границе, где регулирующий трансформатор 10 переключается на соседнюю позицию. Тогда и наименьшие колебания входного напряжения Ug могут появиться усиленными на выходе, поскольку регулирующий трансформатор 10 постоянно переключается между двумя соседними позиция. Для устранения этого вреднего эффекта между параллельными информационными выходами Q , .,., Qp., регис«гра 3 сдвига и разрядными

входами К

К

, уровня сравнения ряда 1 входных компараторов последовательно включены по одному сопротивлению 1 1 , ..., 11f,-i и одному полупроводниковому стабилитрону 12j, ..., 12)1-1 (фиг. 3). Когда выходы Q,, ..., Q., регистра 3 сдвига приложены к L, то к полупроводниковьм стабилитронам приложено напряжение, меньшее напряжения зенеровского пробоя, и тем самым узлы сопротивление полупроводниковый стабилитрон оказываются недействующими. Но если на любом выходе регистра 3 сдвига появляется Н-сигнал, т.е. напряжение диода превышает напряжение зенеровского пробоя, то на соответствующий разрядньй вход уровня сравнения ряда 1 входных компараторов поступает напряжение, незначительно снижающее уровень сравнения соответствующего компаратора. Благодаря этому вследствне малого гистерезиса небольшие колебания входного напряжения Ug и в граничном случае не могут влиять на установку регулирующего трансформатора. Разрядные входы уровня сравнения ряда входных компараторов являются предпочтительно нулевыми входами смещения отдельных операционных усилителей,

716

Чтобы избежать искажений выходного напряжения Кд и помех в высокочастотном диапазоне, регулирующий трансформатор 10 через подключенньм к нему двунаправленный триодный тиристор должен всегда при переходе входного тока I через нуль переключаться на другую позицию. Затруднения возникают Б основном при индуктивных или емкостных нагрузках, поскольку переходы через нуль входного напряжения U и входного тока 1 из-за сдвига фаз не совпадают.

Предлагаемое устройство решает эту проблему благодаря тому, что входной ток I- пропущен через блок 13 детектирования перехода тока через нуль. Тот же входной ток течет через проводяп5ий в данный момент двунаправленный триодный.тиристор. Блок 13 детектирования -перехода тока через нуль через соответствующие переключатели управляет декодирующим блоком 8, который определяет управляемый двунаправленный триодный тиристор и запускающий импульс. Между регистром 3 сдвига и декодирующим блоком 8 включен регистр 14 перехода. . Тактовый вход СРА регистра 14 перехода соединен с входом блока 15 управления регистром перехода, выполненного на переключающих элементах и имеющего четьфе входа. Первый вход блока 15 управления регистром перехода соединен с выходом магазинной памяти 4, второй вход соединен с выходом блока 13 детектирования перехода, тока через нуль и с- входом К . стробирующего каскада декодирующего блока 8, а другие два входа соедине- ны с выходами блока 2 управления регистром. Входы Е блока 13 детектирования перехода тока через нуль промежуточно включены в токовую цепь входного тока Ig.

Блок 13 детектирования перехода тока через нуль при каждом переходе через нуль входного тока Ig формирует импульс, возрастающий или убывающий фронт которого совпадает с переходом через нуль. Этот импульс подается на определенный декодирующим блоком 8 вход электронной системы коммутации и после соответствующего усиления мощности подается на ввод стробирующей схемы определенного двунаправленного триодного тиристора. Для достижения надежного запуска и при малых токах нагрузки длительность импульса должна выбиратьс на 20% выше времени полупериода входного напряжения U, При такой длительности импульса может случиться, что пик входного напряжения Up из-за неомической нагрузки упаде до момента, когда запускающий импульс будет подан на ввод стробирующей схемы двунаправленного триодного тиристора. Но одновременне с пиковым значением входного напряжения Ug может измениться .содержимое регитра 3 сдвига, вследствие чего запускающее напряжение может быть приложено также к вводу стробирующей схемы другого двунаправленного триодного тиристора. В этом случае два двунаправленных триодных тиристора одновременно находились бы в проводщем режиме, вследствие чего два вывода регулирующего трансформатора 10 были бы замкнуты накоротко. Во избежание этого служит включенный между регистром 3 сдвига и декодирующим устройством 8 регистр 14 перехода, содержимое которого может быть изменено лишь в том случае, если запускающее напряжение не прикладывается к вводам стробирующей схемы двунаправленных триодных тиристоров Это может быть достигнуто благодаря благоприятному выбору момента пере дачи информации от регистра 3 сдвига в регистр 14 перехода, например передача информации должна быть выполнена после срабатьшания запускающего напряжения одновременно с убывающим фронтом импульса, формирующегося на выходе блока 13 детектирования перехода тока через нуль. Для достижения быстрой стабилизации передача информации должна быть совершена в короткое время, когда оконче ны параллельный ввод и возможное перемещение в регистре 3 сдвига. Таким образом, если на выходе блока 13 детектирования перехода тока через нуль не появляется импульс и выход приложен к L-уровню, то передача информации должна происходить согласно фиг. 2 одновременно параллепьно с убывающим фронтом тактового импульса СР, вызьгаающим параллельный ввод в регистр 3 сдвига. Если Н-уровень прикладьшается к выходу ма.газинной памяти 4, как это имеет место на фиг. 2 с момента времени

t, то передача информации может проходить только после перемещения регистра 3 сдвига, т.е. после момента времени t , одновременно с возрастающим фронтом импульса S. Возможно, что переход входного тока Ig через нуль попадает на момент времени между t и . Если бы в этом случае передача информации проoходила одновременно с убывающим фронтом тактового импульса, вызывающего параллельный ввод в регистр 3 сдвига, то ближайшая позиция регулирующего трансформатора 10 опреде5лялась бы содержимым, имевшимся до перемещения, и была бы ошибочной. После этого было бы выполнено перемещение регистра 3 сдвига в момент времени t, и измененное содержимое

0 регистра 3 сдвига было бы передано в регистр 14 перехода одновременно с убывающим фронтом импульса, появляющимся на выходе блока -13 детектирования перехода тока через нуль.

5 Тогда позиция регулирующего транс- . форматора 10, отличающаяся от предыдущей неправильной позиции, была бы правильной, и из двух постоянно меняющихся позиций регулирующего транс0форматора 10 одна позиция была бы все время ошибочной. Согласно изобретению этот эффект устраняется благодаря блоку 15 управления регистром перехода, составленному из логичес-.

5 ких переключающих элементов, которьй в соответствующий момент времени вьщает возрастающий фронт импульса на тактовый вход СРА регистра 14 перехода.

0

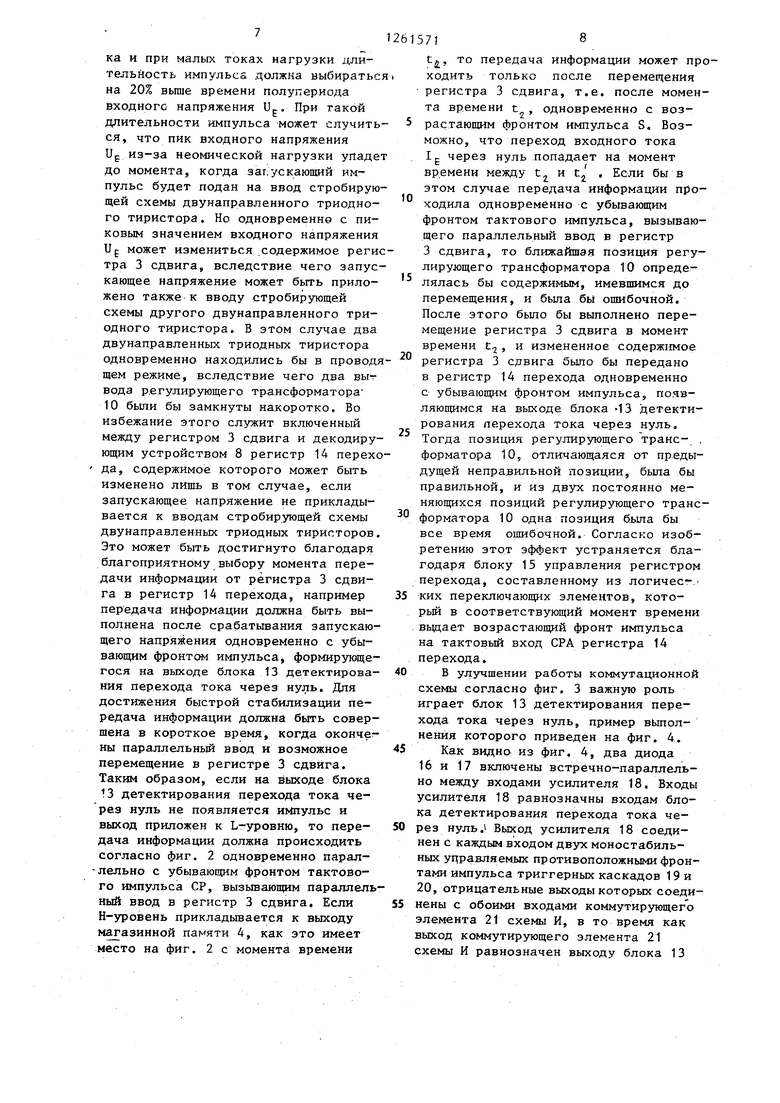

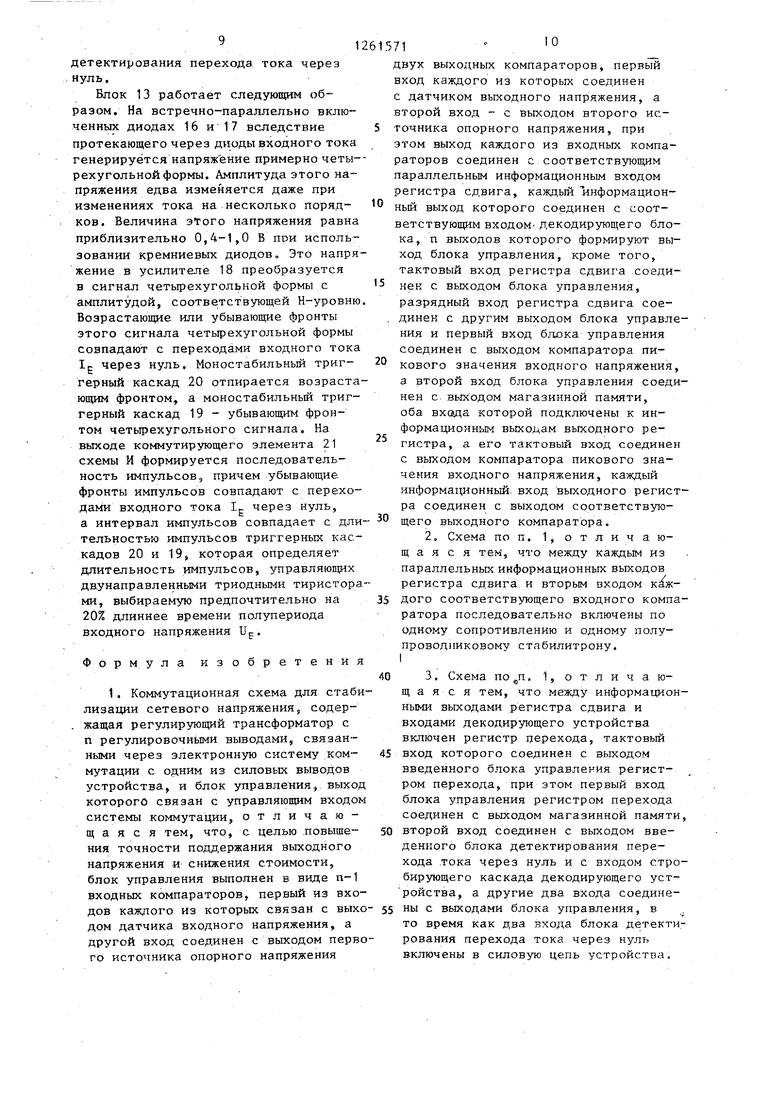

В улучшении работы коммутационной схемы согласно фиг, 3 важную роль играет блок 13 детектирования перехода тока через нуль, пример выполнения которого приведен на фиг. 4,

5

Как видно из фиг. 4, два диода 16 и 17 включены встречно-параллельно между входами усилителя 18. Входы усилителя 18 равнозначны входам блока детектирования перехода тока через нуль. Выход усилителя 18 соединен с каждым входом двух моностабильных управляемых противоположными фронтами импульса триггерных каскадов 19 и 20, отрицательные выходы которых соединены с обоими входами коммутирующего элемента 21 схемы И, в то время как выход коммутирующего элемента 21 схемы И равнозначен выходу блока 13 детектирования перехода тока через . нуль. Блок 13 работает следующим образом. На встречно-параллельно включенных диодах 16 и 17 вследствие протекающего через диоды входного тока генерируется напряжение примерно четырехугольнойформы. Амплитуда этого напряжения едва изменяется даже при изменениях тока на несколько порядков. Величина этого напряжения равна приблизительно 0,4-1,0 В при использовании кремниевых диодов. Это напря жение в усилителе 18 преобразуется в сигнал четырехугольной формы с амплитудой, соответствующей Н-уровню Возрастающие или убывающие фронты этого сигнала четырехугольной формы совпадают с переходами входного тока 1г через нуль. Моностабильньй триггерный каскад 20 отпирается возраста ющим фронтом, а моностабильный триггерный каскад 19 - убывающим фронтом четырехугольного сигнала. На выходе коммутирующего элемента 21 схемы И формируется последовательность импульсов, причем убывающие фронты импульсов совпадают с переходами входного тока Ig через нуль, а интервал импульсов совпадает с дл тельностью импульсов триггерных кас кадов 20 и 19, которая определяет длительность импульсов, управляюлщх двунаправленными триодными тиристор ми, выбираемую предпочтительно на 20% длиннее времени полупериода входного напряжения U. Формула изобретени 1. Коммутационная схема для стаб лизации сетевого напряжения содер. жащая регулирующий трансформатор с п регулировочными выводами, связанными через электрОнную систему коммутации с одним из силовых выводов устройства, и блок управления, выхо которого связан с управляющим входо системы коммутации, отличающаяся тем, что, с целью .повышения точности поддержания выходного напряжения и снижения стоимости, блок управления выполнен в виде п-1 входных компараторов, первый из вхо дов каждого из которых связан с вых дом датчика входного напряжения, а другой вход соединен с выходом перв го источника опорного напряжения 1 О вух выходных компараторов, первый ход каждого из которых соединен датчиком выходного напряжения, а торой вход - с выходом второго исочника опорного напряжения, при том выход каждого из входных компааторов соединен с соответствующим араллельным информационным входом егистра сдвига, каждьгй информационый выход которого соединен с соотетствующим входом- декодирующего блока, п выходов которого формируют выход блока управления, кроме того, тактовый вход регистра сдвига .соединен с выходом блока управления, разрядный вход регистра сдвига соединен с другим выходом блока управления и первый вход близка управления соединен с выходом компаратора пикового значения входного напряжения, а второй вход блока управления соединен с. выходом магазинной памяти, оба входа которой подключены к информационным выходам выходного регистра, а его тактовый вход соединен с выходом компаратора пикового значения входного напряжения, каждый информационный вход выходного регистра соединен с выходом соответствующего выходного компаратора. 2.Схема по п. 1, отлича ющ а я с я тем, что между каждым из параллельных информационных выходов регистра сдвига, и вторым входом каждого соответствующего входного компаратора последовательно включены по одному сопротивлению и одному полупроводниковому стабилитрону. 3.Схема , 1, отличающ а я с я тем, что между информационными выходами регистра сдвига и входами декодирующего устройства включен регистр перехода, тактовый вход которого соединен с выходом введенного блока управления регистром перехода, при этом первый вход блока управления регистром перехода соединен с выходом магазинной памяти, второй вход соединен с выходом введенного блока детектирования перехода .тока через нуль и с входом стробирующего каскада декодирующего устройства, а другие два входа соединены с выходами блока управления, в то время как два входа блока детектирования перехода тока через нуль включены в силовую цепь устройства. II 4. Схема по п. 3, о т л и ч а rant а я с я тем, что блок детектирова ния перехода тока через нуль вьтол г ней в йиде усилителя, между входаш которого встречно-параллельно включены два диода, выход которого соединен с каждым входом двух моностабильных триггерных каскадов с .входными цепями, управляемыми про712тивоположными фронтами импульсов, при этом отрицательные выходы моностабильных триггерных каскадов соединены с обоими входами схемы И, вькод которой формирует выход. блока детектирования перехода тока через нуль ., входы ко торого формируют входы усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для устранения бросков тока при включении сетевых трансформаторов | 1983 |

|

SU1269755A3 |

| РАДИОПЕРЕДАЮЩАЯ СИСТЕМА ВРЕМЕННОЙ ОБЛАСТИ И РАДИОПЕРЕДАТЧИК | 1989 |

|

RU2105415C1 |

| Устройство для двусторонней связи | 1975 |

|

SU553950A3 |

| Устройство для синхронного перевода | 1985 |

|

SU1364249A3 |

| Устройство защиты от перегрузки усилителя мощности | 1978 |

|

SU910136A3 |

| Автоматическое переговорное устройство | 1984 |

|

SU1386051A3 |

| Цифровой измеритель пикового значения импульсных воздействий | 1984 |

|

SU1167734A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Устройство для цифрового измерения частоты медленно меняющихся процессов | 1987 |

|

SU1413542A1 |

| СПОСОБ АВТОНАСТРОЙКИ КОМПЕНСАЦИИ ЕМКОСТНОЙ И АКТИВНОЙ СОСТАВЛЯЮЩИХ ПРИ ДУГОВЫХ ЗАМЫКАНИЯХ НА ЗЕМЛЮ | 1994 |

|

RU2074473C1 |

Изобретение относится к области электротехники и предназначено ;цля стабилизации сетевого напряжения. Цель изобретения - повышение точности поддержания выходного напряжения и снижение стоимости. Дпя стабилизации сетевоТо напряжения изменяют коэффициент трансформации регулирующего трансформатора 10 изменением состояния электронной системы 9 коммутации. Электронная система 9 коммутации управляется сигналом, пропорциональным входному напряженшо с выхода ряда 1 входных компараторов. Сигнал, с выхода ряда 1 входных компараторов изменяется благодаря перемещению регистра 3 сдвига через действие сигнала, характеризующего пиковое значение выходного напряжения, за счет чего повышается точность поддерСО жания ВЫХОДНОГ0 напряжения, т.е. достигается поставленная цель. 3 з.п. ф-ды,. 4 .ид.. см

«Ptff-7

(риг. г

ФигЛ

| Патент США 3970918, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США 4011499, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-09-30—Публикация

1983-03-03—Подача