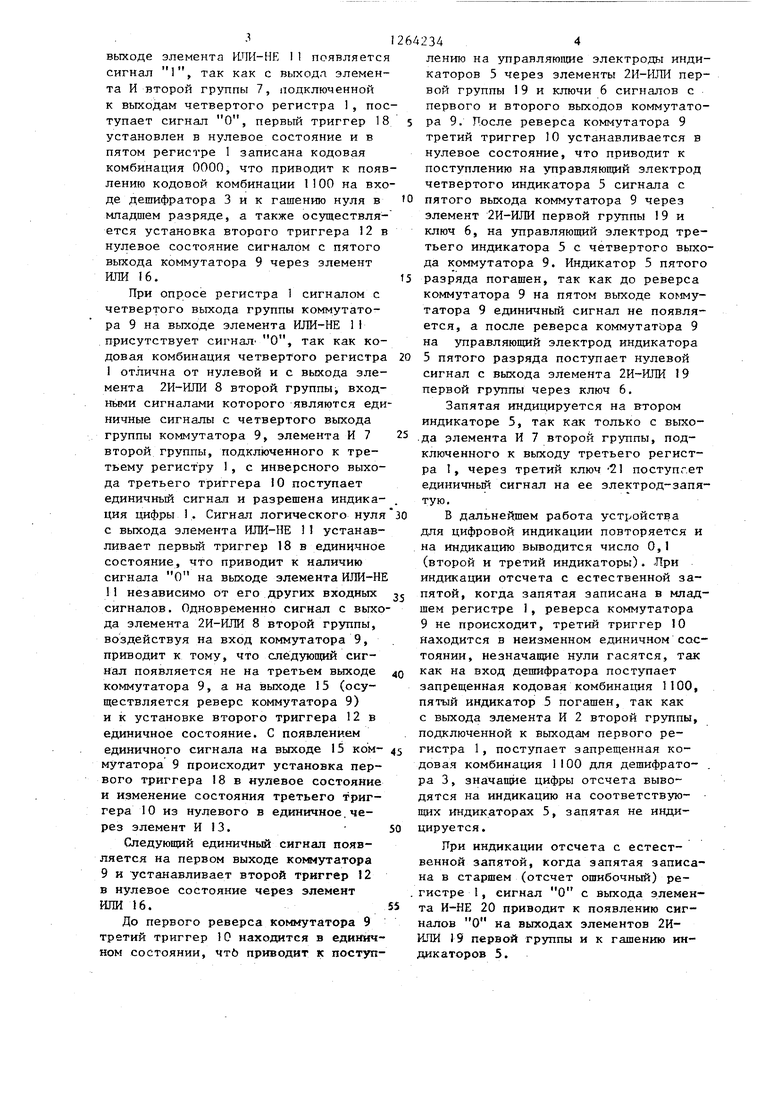

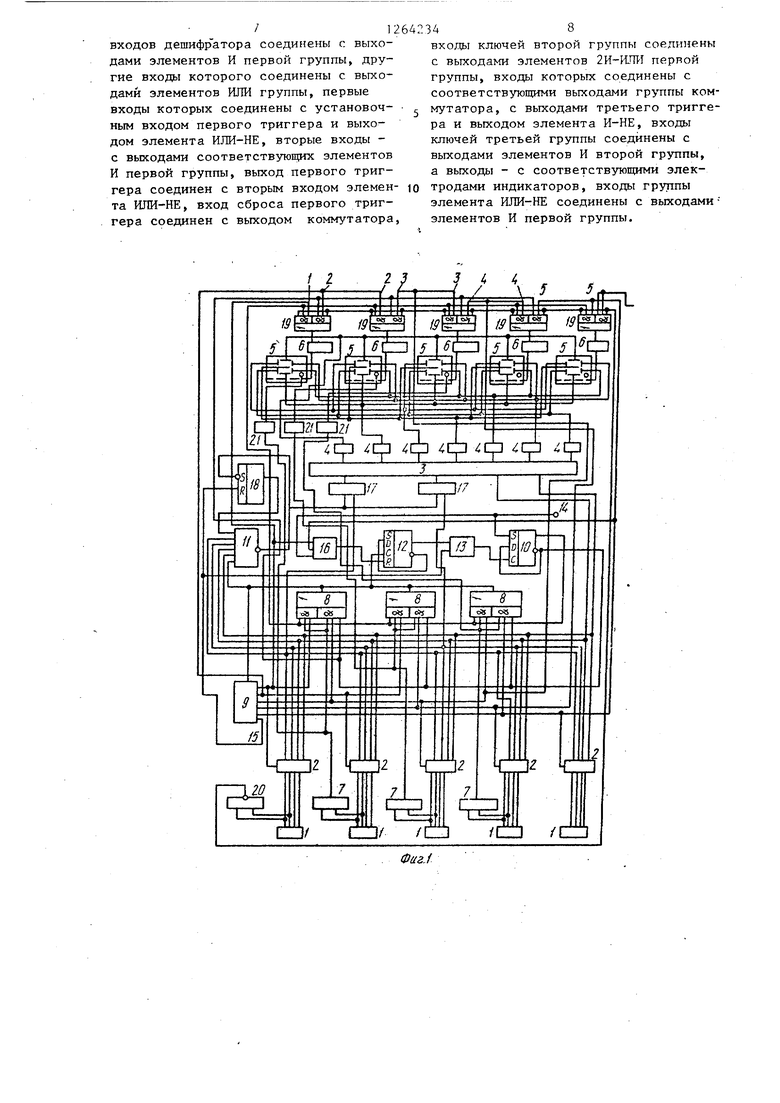

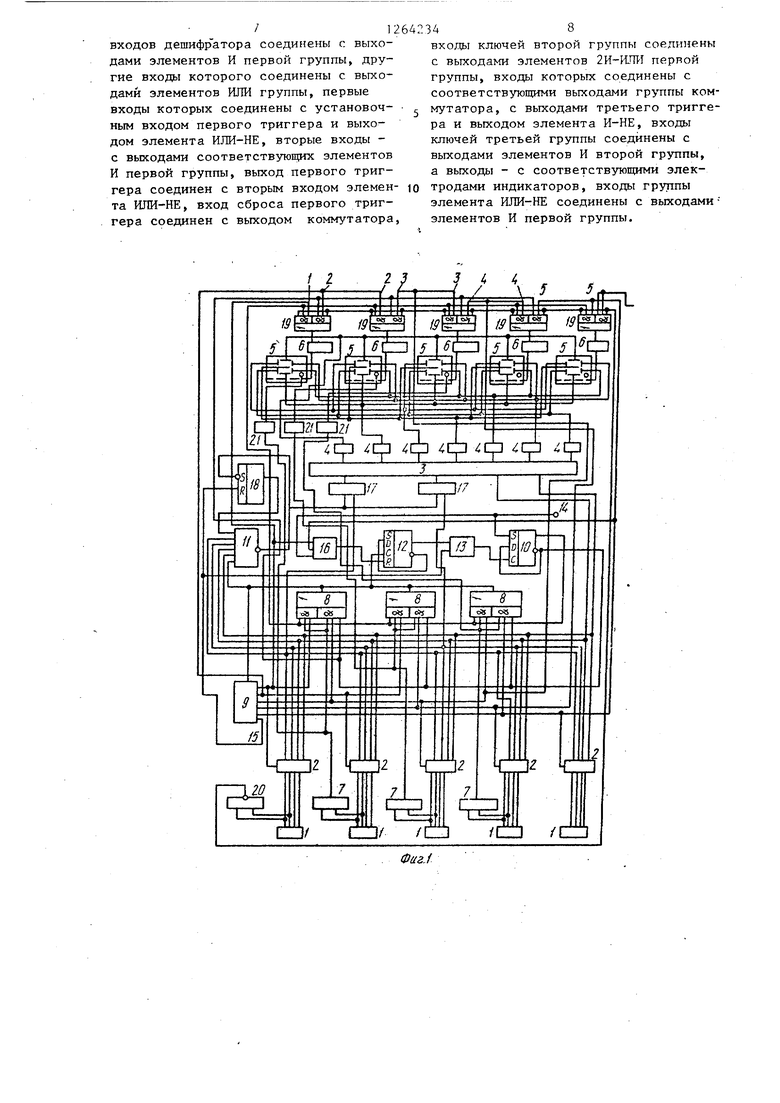

(Л С , Устройство относится к автоматике и вычислительной технике и предназна чено для вьшода информации в цифровой аппаратуре. Целью изобретения является повыше ние точности устройства. На фиг.1 представлена схема устройства для индикации; на фиг.2 схема дешифратора. Устройство для индикации содержит регистры 1, элементы И 2 первой груп пы, дешифратор 3, ключи 4 первой группы, индикаторы 5, ключи 6 второй группы, элементы И 7 второй группы, элементы 2И-ИЛИ 8 второй группы, ком мутатор 9, третий триггер 10, элемен ИЛИ-НЕ 11, второй триггер 12, элемен И 13, шина питания 14, выход 15 коммутатора 9, элемент ИЛИ 16, группа элементов ИЛИ 17, первый триггер 18, элементы 2И-ИЛИ 19 первой группы, элемент И-НЕ 20, ключи 21 третьей группы, дешифратор, содержащий элементы И-НЕ 22-36 и элементы И 37-42, осуществляющие декбдирование двоично десятичного кода в семисегментный, Устройство для цифровой индикации работает следующим образом. Информация о целой части числа, запятой и дробной части числа записы вается в регистры 1, причем запятой соответствует кодовая комбинация, отличная от кодовых комбинаций цифр, например 1100 в коде 8-4-2-1. При отсутствии запятой на выходе элемента И 7 второй группы присутствует уровень О и сигнал 1 при наличии запятой. Сигналы с выхода коммутатора 9 поступают на входы элементов И 2 пер вой группы, разрешая поочередно прохождение сигналов с выходов регистров 1 через элементы ИЖ 17 на вход дешифратора 3. Сигналы с выхода дешифратора 3 через ключи 4 постзппают на информационные электроды индикаторов 5, и при условии наличия сигнала на их управляю1Щ1х электродах с выхода коммутатора 9 через элементы 2И-Ш1И 19 первой группы и ключи 6 происходит последовательная во време ни индикация содержимого регистров 1 Рассмотрим работу устройства при индикации пятиразрядного отсчета. В регистрах 1 записано число 00,10. В исходном состоянии (при включении питания) второй триггер 12 через элемент ИЛИ 16 устанавливается в нулевое состояние и третий триггер10 устанавливается в единичное состояние импульсом, сформированным на шине 14, а сигналом с выхода 15 коммутатора 9 обнуляется первый триггер 18. При появлении импульса опроса на первом выходе коммутатора 9 на входе элемента ИЛИ-НЕ 11 присутствуют сигналы О с выхода первого триггера 18, с выхода элемента И 2 первой группы (кодовая комбинация первого регистра 1-0000) и с выхода элемента 2И-ИЛИ 8 второй группы, так как с выхода элемента, И 7 второй группы, подключенной к выходам второго регистра 1, поступает сигнал О (запятая отсутствует) и подтверждается нулевое состояние второго триггера 12 через элемент ИЛИ 16. Сигнал 1 с выхода элемента ИЛИ-НЕ 11 приводит к появлению кода 1100 на входе дешифратора 3, воспринимаемого им как запрет. Поэтому нуль в старшем разряде индицироваться не будет. При появлении импульсов опр.оса на втором выходе коммутатора 9 единичный сигнал с, выхода элемента И 7 второй группы, подключенного к выходу третьего регистра I (запятая присутствует), через элемент 2И-Ш1И 8 второй группы приводит к появлению Сигнала О на выходе элемента ИЛИ-НЕ I1 и установке первого триггера 18 в единичное состояние. Следовательно, на выходе элемента ИЛИ-НЕ 11 присутствует сигнал О и разрешена индикада я нуля во втором разряде. Сигнал с выхода элемента 2И-ИЛИ 8 второй группы, воздействуя на вход коммутатора 9, приводит к тому, чтс следующий сигнал появляется не на третьем выходе группы коммутатора .9, а на выходе 15 (осуществляется реверс коммутатора 9). Одновременно . сигнал с выхода элемента 2И-ИЛИ 8 второй группы приводит к установке второго триггера 12 в единичное состояние. С появлением единичного сигнала на управляющем вьйсоде коммутатора 9 происходит Установка первого триггера 18 и третьего триггера 10 через элемент И 13 в нулевое состояние, Следзтощей единичный сигнал появляется на пятом вькоде группы коммутатора. При опросе пятого регистра 1 на выходе элемента ИПИ-ИЕ 11 появляетс сигнал , так как с выхода элемен та И второй группы 7, подключенной к выходам четвертого регистра О тупает сигнал и , первый триггер 1 установлен в нулевое состояние и в пятом регистре 1 записана кодовая комбинация 0000, что приводит к поя лению кодовой комбинации 1100 на вх де дешифратора 3 и к гашению нуля в младшем разряде, а также осуществля ется установка второго триггера 12 нулевое состояние сигналом с пятого выхода коммутатора 9 через элемент ИЛИ 16. При опросе регистра 1 сигналом с четвертого выхода группы коммутатора 9 на выходе элемента ИЛИ-НЕ 1I присутствует сигнал О, так как ко довая комбинация четвертого регистра Iотлична от нулевой и с выхода элемента 2И-ИЛИ 8 второй группыi входными сигналами которого являются еди ничные сигналы с четвертого выхода группы коммутатора 9, элемента И 7 второй группы, подключенного к третьему регистру , с инверсного выхода третьего триггера 10 поступает единичный сигнал и разрешена индикация цифры 1. Сигнал логического нуля с выхода элемента ИЛИ-НЕ 11 устанавливает первый триггер 18 в единичное состояние, что приводит к наличию сигнала О на вькоде элемента ИЛИ-Н I1независимо от его других входных сигналов. Одновременно сигнал с выхо да элемента 2И-ШШ 8 второй группы, воздействуя на вход коммутатора 9, приводит к тому, что следующий сигнал появляется не на третьем выходе коммутатора 9, а на выходе 15 (осуществляется реверс коммутатора 9) и к установке второго триггера 12 в единичное состояние. С появлением единичного сигнала на выходе 15 коммутатора 9 происходит установка первого триггера 18 в нулевое состояние и изменение состояния третьего триггера 10 из нулевого в единичное. через элемент И I3. Следующий единичный сигнал появляется на первом выходе коммутатора 9 и устанавливает второй триггер 12 в нулевое состояние через элемент ИЛИ 16. До первого реверса коммутатора 9 третий триггер 10 находится в единичном состоянии, чтб приводит к поступлению на управляющие электроды индикаторов 5 через элементы 2И-1-ШИ первой группы 19 и ключи 6 сигналов с первого и второго выходов коммутатора 9. После реверса коммутатора 9 третий триггер 10 устанавливается в нулевое состояние, что приводит к поступлению на управляющий электрод четвертого индикатора 5 сигнала с пятого выхода коммутатора 9 через элемент 2И-ИЛИ первой группы 19 и ключ 6, на управляющий электрод третьего индикатора 5 с четвертого выхода коммутатора 9. Индикатор 5 пятого разряда погашен, так как до реверса коммутатора 9 на пятом выходе коммутатора 9 единичный сигнал не появляется, а после реверса коммутатора 9 на управляющий электрод индикатора 5 пятого разряда поступает нулевой сигнал с выхода элемента 2И-ИЛИ 19 первой группы через ключ 6, Запятая индицируется на втором индикаторе 5, так как только с выхо.да элемента И 7 второй группы, подключенного к выходу третьего регистра I, через третий ключ 21 поступг.ет единичный сигнал на ее электрод-запятую, В дальнейшем работа устройства для цифровой индикации повторяется и на индикацию выводится число О,1 (второй и третий индикаторы). Лри индикации отсчета с естественной запятой, когда запятая записана в младшем регистре 1, реверса коммутатора 9 не происходит, третий триггер 10 находится в неизменном единичном состоянии, незначащие нули гасятся, так как на вход дешифратора поступает запрещенная кодовая комбинация 1100, пятый индикатор 5 погашен, так как с выхода элемента И 2 второй группы, подключенной к выходам первого регистра 1, поступает запрещенная кодовая комбинация 1100 для дешифрато- . ра 3, зна чащйе цифры отсчета выводятся на индикацию на соответствую- щих индикаторах 5, запятая не индицируется. При индикации отсчета с естественной запятой, когда запятая записана в старшем (отсчет ошибочный) регистре 1, сигнал О с выхода элемента И-НЕ 20 приводит к появлению сигналов О на выходах элементов 2ИШШ 19 первой группы и к гашению индикаторов 5. При индикации отсчета без естест венной запятой реверса коммутатора 9 не происходит, третий триггер 10 не изменяет свое единичное состояние, незначащие нули гасятся, так как на вход дешифратора 3 поступае запрещенная кодовая комбинация 1100 значащие цифры отсчета выводятся н индикацию на соответствующих индик торах 5, Преобразование двоично-десятичн го Кода в семисегментный деншфрато ром 3 осуществляется на двух уровнях. На элементах И-НЕ 22-35 собра преобразователь двоично-десятичног кода в десятичный, причем появлени О на выходах элементов И-НЕ 26-3 соответствует дешифрации кодовых к бинаций цифр 0-8 и запрещенной код вой комбинации. На элементах И 37и элементе И-НЕ 36 собран преобраз ватель десятичного кода в семисегментный. Появление сигналов 1 н выходах данных элементов приводит индикции данных сегментов на инди каторах 5. Соответствие выходных сигналов дешифратора 3 его входным сигналам отражено в таблице. Кодовая Выходные сигналы дешифратора комбинация а b с d е f g на входе дешифратора0000000 111 1 J о 01 г о о о о 1 1 о 1 о 1 I 11001 011001 1011011 1011111 1 1 10000 1111111 1111011 34 Из таблицы следует, что кодовая комбинация 1100 является запретом для дешифратора 3. Применение группы элементов ИЛИ, трех триггеров, третьей группы ключей, элементов 2И-ИЛИ первой и второй групп, элемента И, элементов И-НЕ, ИЛИ-НЕ, элемента ИЛИ, делает возможным гашение незначащих нулей в отсчете при индикации чисел с естественной запятой, что позволяет повысить точность при индикации. Формула изобретения I. Устройство для индикации, содержащее регистры, соединенные с входами элементов И первой группы, дешифратор, выходы которого соединены с входами ключей первой группы, выходы которых соединены с информационными электродами индикаторов, управляющие электроды которых соединены с выходами ключей второй группы, элементы И второй группы, входы которых соединены с вьгходами двух старших разрядов регистров, кроме первого и последнего, и коммутатор, выходы группы которого соединены с входами элементов И первой группы, отличающееся тем, что, с целью повьш1ения точности устройства, в него вве--. дены группа элементов ИЛИ, элемент ИЛИ, три триггера, элемент И, элемент ИЛИ-НЕ, элемент И-НЕ, ключи третьей группы, первая и вторая группы элементов 2И-ИЛИ, входы которых соединены с соответствующими выхода№1 когФ1утатора, третьего триггера и с выходами элементов И второй группы, выходы элементов 2И-ИЛИ второй группы соединены с входом коммутатора, с первым входом элемента ИЛИ-НЕ и с четным входом второго триггера, прямой выход которого соединен с первьж входом элемента И, второй вход которого соединен с выходом коммутатора, выход элемента И соединен со счетным входом третьего триггера, установочный вход которого соединен с первым входом элемента ИЛИ и с шиной питания, второй и третий входы которого , соединены с соответствующими выходами группы коммутатора, а выход - с входом сброса второго триггера, инверсный выход которого и инверсный выход третьего триггера соединены с информационньв га входами, одни из

/12642

входов дешифратора соединены с выходами элементов И первой группы, другие входы которого соединены с выходами элементов ИЛИ группы, первые входы которых соединены с установочным входом первого триггера и выходом элемента ИЛИ-НЕ, вторые входы с выходами соответствующих элементов И первой группы, выход первого триггера соединен с вторьм входом элемен- ю та ИЛИ-НЕ, вход сброса первого триггера соединен с выходом коммутатора,

348

входы ключей второй группы соединены с выходами элементов 2И-ИЛТ-1 первой группы, входы которых соединены с соответствующими выходами группы коммутатора, с выходами третьего триггера и выходом элемента И-НЕ, входы ключей третьей группы соединены с выходами элементов И второй группы, а выходы - с соответствующими электродами индикаторов, входы группы элемента ИЛИ-НЕ соединены с выходами элементов И первой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1983 |

|

SU1156123A1 |

| Устройство для индикации | 1982 |

|

SU1057982A1 |

| Устройство для индикации | 1983 |

|

SU1176373A1 |

| Устройство для цифровой индикации | 1981 |

|

SU970437A1 |

| Устройство для индикации | 1983 |

|

SU1149306A1 |

| Устройство для индикации | 1986 |

|

SU1354244A1 |

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Устройство для индикации | 1982 |

|

SU1163349A1 |

| Устройство для цифровой индикации | 1979 |

|

SU903961A1 |

| Счетчик импульсов с цифровой индикацией | 1986 |

|

SU1336230A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для вьшода информации в цифровой аппаратуре. Целью изобретения является повышение точности устройства. Поставленная цель достигается за счет введения в устройство группы элементов ИЛИ, элемегта ИЛИ, трех триггеров, элементов И, ИЛИ-НЕ, И-НЕ и ключей третьей группы. Введенная совокупность элементов делает возможные гашение незначащих нулей в отсчете при индикации чисел с гстественной запятой, что позволяет повысить точность при индикации. 2 ил.

/ I

| Устройство для индикации | 1982 |

|

SU1057982A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для индикации | 1982 |

|

SU1022211A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-10-15—Публикация

1984-10-25—Подача