которого является выход первого сумматора, причем (к+О-й арифметический блок содержит первый и второй сумматоры, элемент НЕ, первый и второй умножители комплексных чисел и умножитель на постоянный коэффициент, выход которого подключен к первому входу первого сумматора и входу элемента НЕ, выход которого подключен к первому входу второго сумматора, выход которого подключен к первому входу первого умножителя комплексных чисел, выход которого является выходом второго операнда

98534

блока, выходом первого операнда которого является выход второго умиожи теля комплексных чисел, первый вход которого подключен к выходу первого сумматора, второй вход которого соединен с вторым входом второго сумматора и является входом второго операнда блока, входом второго операнда которого является вход умножителя на постоянный коэффициент, а вторые входы первого и второго умножителей на коэффициент являются соответственно входами первого и вто рого коэффициентов блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления быстрого преобразования Фурье с основанием 6 | 1986 |

|

SU1334156A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для вычисления быстрого преобразования Фурье с основанием 3 | 1985 |

|

SU1302292A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Каскадное устройство для быстрого преобразования Фурье | 1983 |

|

SU1265794A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ХАРТЛИ-ФУРЬЕ | 1999 |

|

RU2190874C2 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для выполнения быстрого преобразования фурье | 1987 |

|

SU1520538A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1312611A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ ПО ОСНОВАНИЮ ДВА, содержащее logaN (N размер преобразования коммутаторов, logjN арифметических блоков и 21og2N элементов задержки, причем выход

Изобретение относится к цифровой обработке сигналов и может быть использовано в радиолокации, системах связи, при анализе речевых сигналов и двумерных изображений.

Цель изобретения - упрощение устройства.

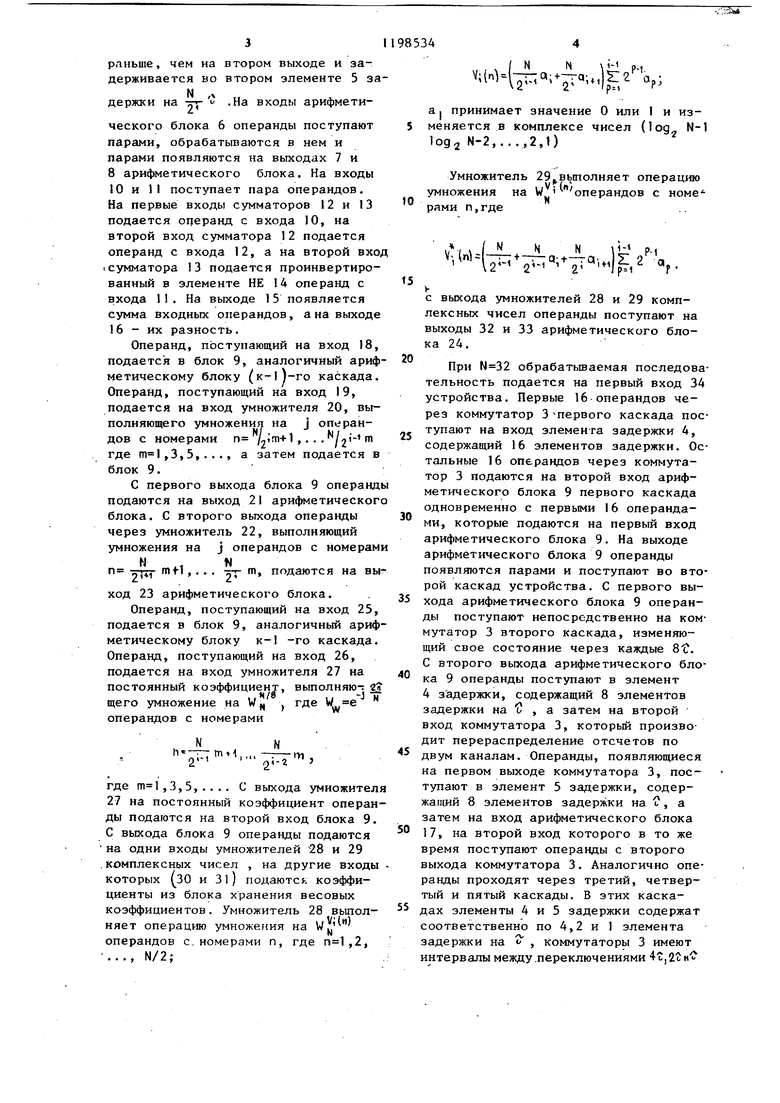

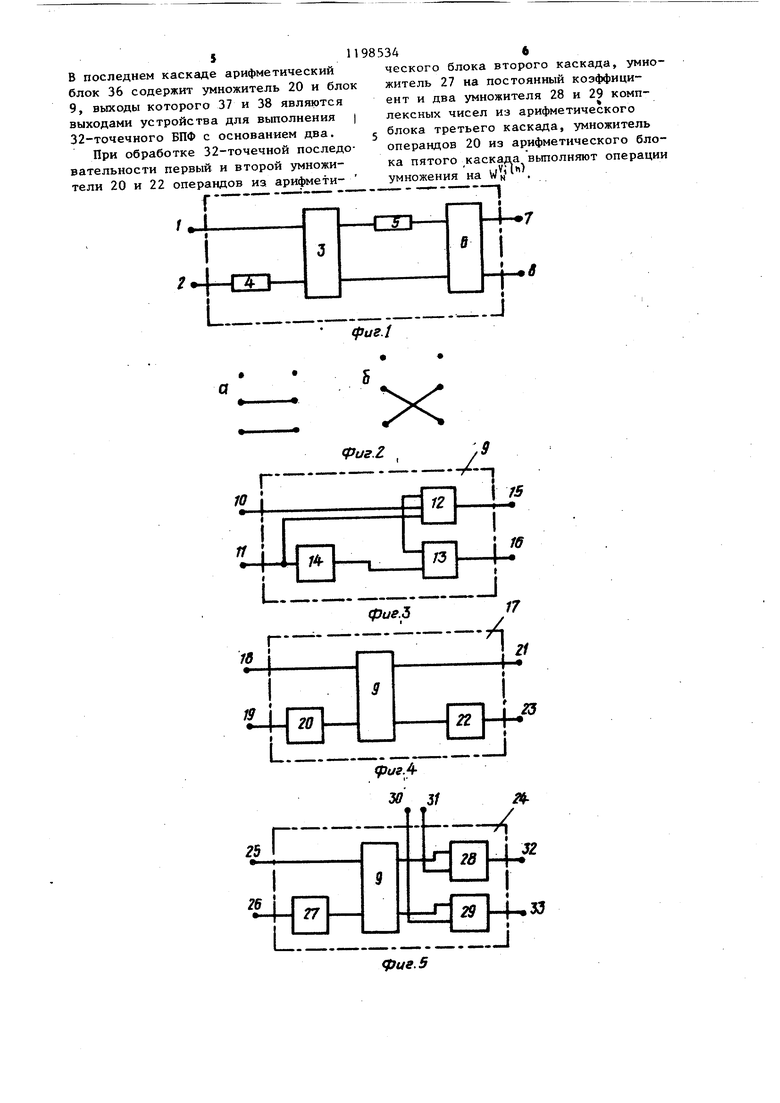

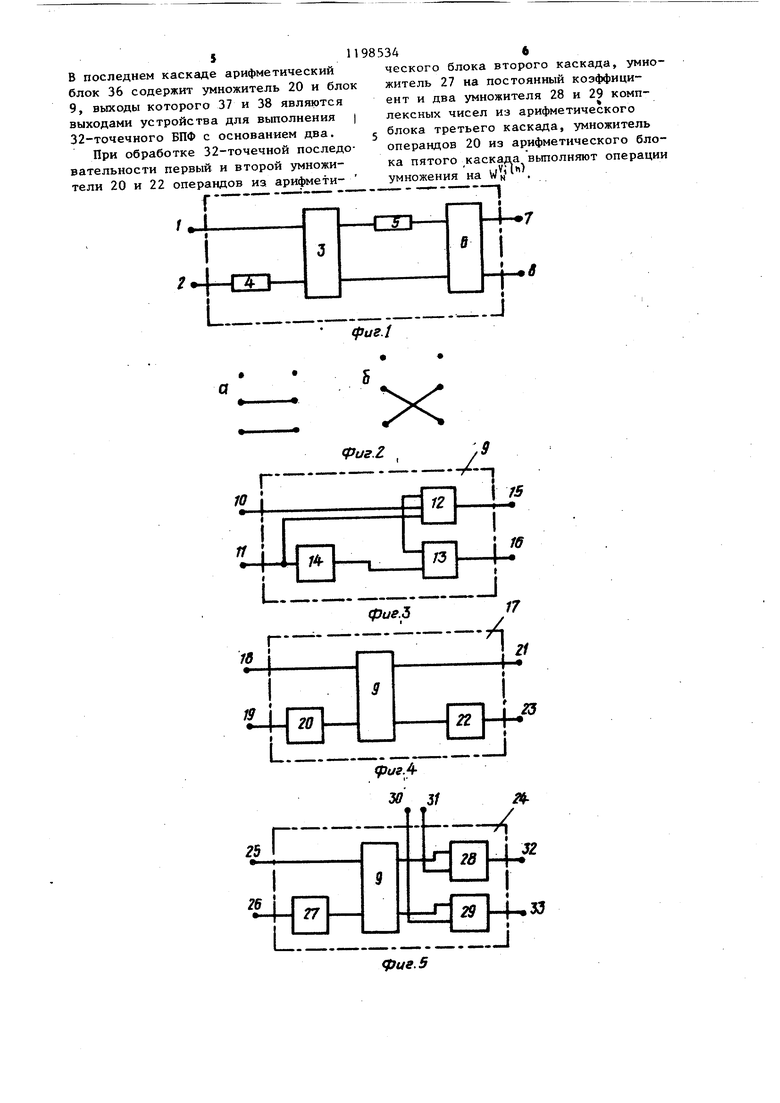

На фиг. приведена схема одного каскада устройства; на фиг. 2а, б схема переключения коммутатора; на фиг. 3 - схема к-1 -го арифметического блока; на фиг. 4 - схема к-го арифметического блока; на фиг. 5 - схема (к+1)-го арифметического блока; на фиг. 6 - пример выполнения устройства для .

Каскад устройства (фиг. ) содержит 1 и 2 устройства, коммутатор 3, элементы 4 и 5 задержки, арифметический блок 6, выходы 7 и 8 ариф метического блока.

(k-1)-й арифметический блок 9 (фиг. 3) содержит; входы 10 и П, сум маторы 12 и 13, элемент НЕ 14, выходы 15 и 16; к-й арифметический блок 17 / фиг. 4) содержит: входы 18 и 19, арифметический блок 9, умножитель 20 на постоянный коэффициент, выход 21 умножитель 22 на постоянный коэффициент, выход 23. (k+1)-й арифметический блок 24 (фиг. 5) содержит входы 25 и 26, арифметический блок 9, умножитель 27 на постоянный коэффициент, умножители 28 и 29 комплексных чисел с входами 30 и 31, выходы 32 и 33 блока.

Устройство для (фиг. 6) содержит входы 34, 35, коммутатор 3, элементы 4 и 5 задержки, арифметические блоки 9, 17, 24, 36, умножители 20, 22, 27, 28, 29, выходы 37 и 38.

Устройство работает следующим образом.

На входы 1 и 2 поступают по N/2 операндов. Группа операндов, поданная на вход 1, поступает на первый вход коммутатора 3, а другая группа операндов проходит через первый элемент 4 задержки, осуществляющий задержку на N/2 с, где i - номер каскада (,2,3,...), - интервалы поступления операндов, и через

N

поступает на второй вход коммутатора -3, который производит перераспределение операндов, поступающих на его входы между его выходами.

N л. Первые yj- о коммутатор 3 соединяет

первый и второй входы соответственно с первым и вторым выходами (фиг. 2а),

следующие yj- с/ - первый и второй

входы соответственно с вторым и первым выходом (фиг. 2б . Затем эти положения коммутатора повторяются. На выходах коммутатора 3 появляются

N две группы по у операндов, причем

группа операндов на первом выходе коммутатора 3 появляется на N/2 о

втором выходе и завтором элементе 5 за.На входы арифметического блока 6 операнды поступают парами, обрабатываются в нем и парами появляются на выходах 7 и 8 арифметического блока. На входы 10 и II поступает пара операндов. На первые входы сумматоров 12 и 13 подается операнд с входа 10, на второй вход сумматора 12 подается операнд с входа 12, а на второй вход 1 сумматора 13 подается проинвертированный в элементе НЕ 14 операнд с входа 11. На выходе 15 появляется сумма входных операндов, а на выходе 16 - их разность.

Операнд, поступающий на вход 18, подается в блок 9, аналогичный арифметическому блоку (x-lJ-ro каскада. Операнд, поступающий на вход 19, подается на вход умножителя 20, выполняющего умножения на j оп грандов с номерами п ,. . где ,3,5,..., а затем подается в блок 9.

С первого выхода блока 9 операнды подаются на выход 2I арифметического блока. С второго выхода операнды через умножитель 22, выполняющий умножения на j операндов с номерами

«4.1

2ТЙ- ,... ji

m, подаются на выход 23 арифметического блока.

Операнд, поступающий на вход 25, подается в блок 9, аналогичный арифметическому блоку к-1 -го каскада. Операнд, поступающий на вход 26, подается на вход умножителя 27 на постоянный коэффициент, вьтолняю- gj щего умножение на Ущ j где W е операндов с номерами

N

N

m ti

где ,3,5,.... С выхода умножителя 27 на постоянный коэффициент операнды подаются на второй вход блока 9. С выхода блока 9 операнды подаются на одни входы умножителей 28 и 29 .комплексных чисел , на другие входы которых (20 и 3l) подаются коэффициенты из блока хранения весовых коэффициентов. Умножитель 28 выполVUH)

няет операцию умножер{ия на W м

операндов с. номерами п, где ,2, ..., N/2;

ипЬ(«;Ла;.,1ёе%р;

а I принимает значение О или I и изменяется в комплексе чисел (log. N-1 log N-2,...,2,1)

Умножитель (полняет операцию умножения на W операндов с номе10рами п, где

i

1- 0-1

.-Fi

-га

«-1 2

с выхода умножителей 28 и 29 комплексных чисел операнды поступают на выходы 32 и 33 арифметического блока 24.

При обрабатьшаемая последовательность подается на первый вход 34 устройства. Первые 16 операндов через коммутатор 3 первого каскада поступают на вход элемента задержки 4, содержащий 16 элементов задержки. Остальные 16 операндов через коммутатор 3 подаются на второй вход арифметического блока 9 первого каскада одновременно с первыми 16 операндами, которые подаются на первый вход арифметического блока 9. На выходе арифметического блока 9 операнды появляются парами и поступают во второй каскад устройства. С первого выхода арифметического блока 9 операнды поступают непосредственно на коммутатор 3 второго каскада, изменяющий свое состояние через каждые ВС. С второго выхода арифметического блока 9 операнды поступают в элемент 4 задержки, содержащий 8 элементов задержки на D , а затем на второй вход коммутатора 3, который производит перераспределение отсчетов по двум каналам. Операнды, появляющиеся на первом выходе коммутатора 3, поступают в элемент 5 задержки, содержащий 8 элементов задержки на о , а затем на вход арифметического блока 17, на второй вход которого в то же время поступают операнды с второго выхода коммутатора 3. Аналогично операнды проходят через третий, четвертый и пятый каскады. В этих каскадах элементы 4 и 5 задержки содержат соответственно по 4,2 и 1 элемента задержки на tJ , коммутаторы 3 имеют интервалы между .переключениями 4, 2 и В последнем каскаде арифметический блок 36 содержит умножитель 20 и бл 9, выходы которого 37 и 38 являются выходами устройства для выполнения 32-точечного БПФ с основанием два. При обработке 32-точечной послед вательности первый и второй умножители 20 и 22 операндов из арифметиf J

1Г

г..J

фиг./

X

Риг.2 ,.S

„.«J

fffue.S 34« ческого блока второго каскада, умножитель 27 на постоянный коэффициент и два умножителя 28 и 29 комплексных чисел из арифметического блока третьего каскада, умножитель операндов 20 из арифметического блока пятого каска; а вьшолняют операции умножения на WN М-7 I

t-й ItOOMof

ff i .itofMof

3-ft fffCffff

л

тан

df

n

| Патент США 3816729, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3588460, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-15—Публикация

1984-06-26—Подача