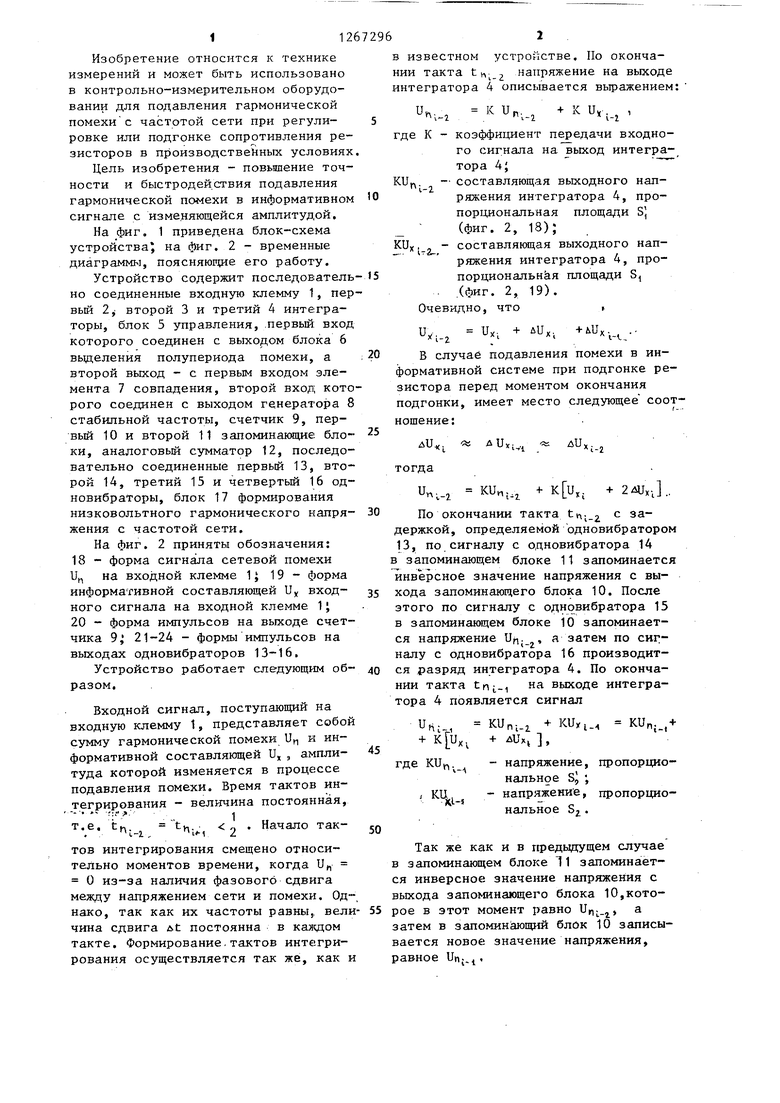

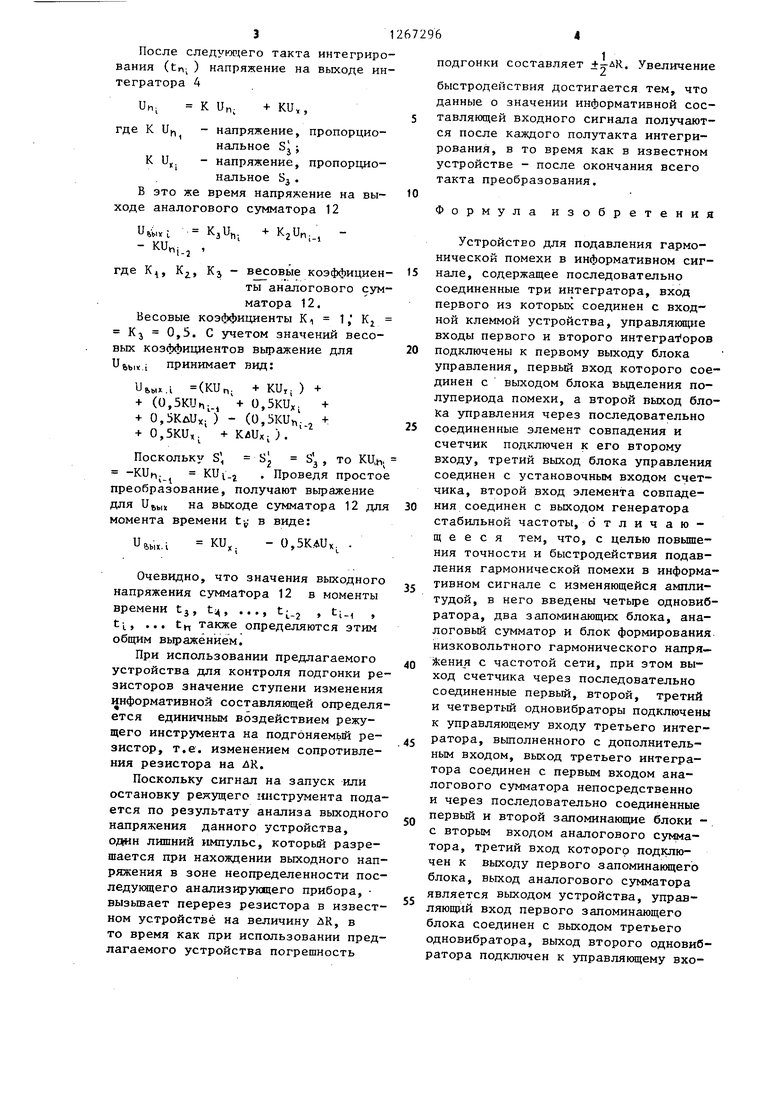

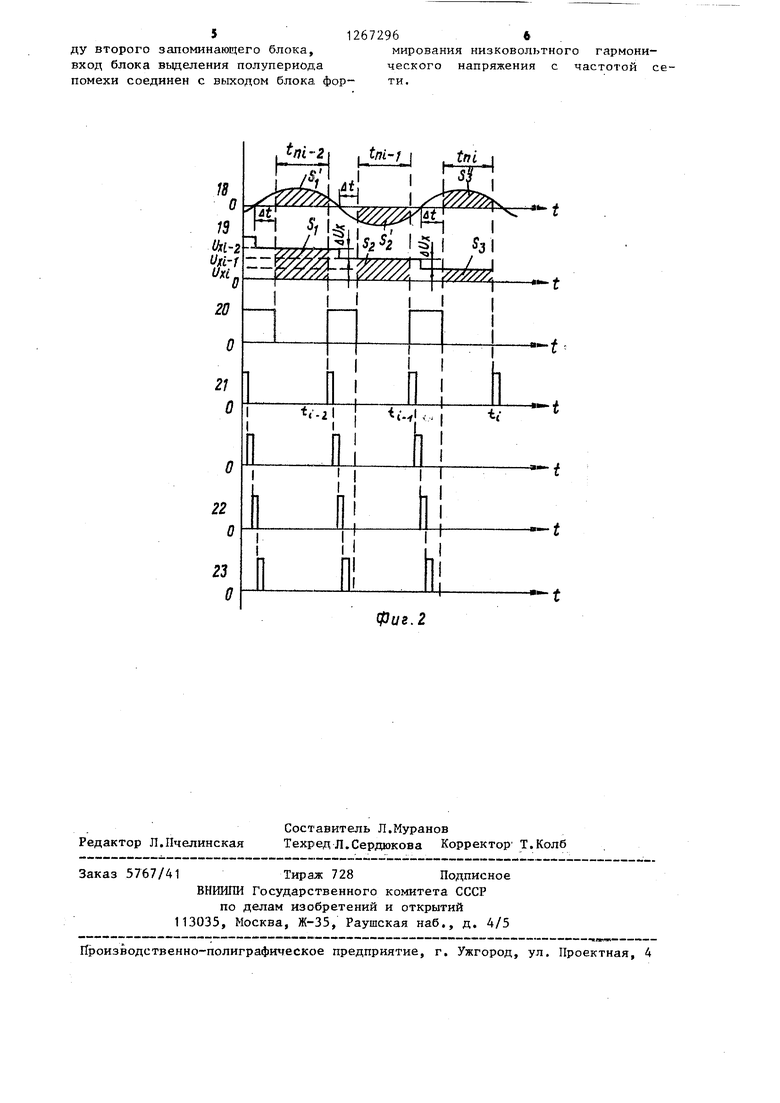

Изобретение относится к технике измерений и может быть использовано в контрольно-измерительном оборудовании для подавления гармонической помехис частотой сети при регулировке или подгонке сопротивления ре зисторов в производственных условия Цель изобретения - повышение точ ности и быстродействия подавления гармонической помехи в информативно сигнале с изменяющейся амплитудой, На фиг. 1 приведена блок-схема устройстваj на фиг. 2 - временные диаграммы, поясняюпще его работу. Устройство содержит последовател но соединенные входную клемму 1, пе вый 2 второй 3 и третий 4 интеграторы, блок 5 управления, ,первый: вхо которого соединен с Bbixofi;oM блока 6 вьщеления полупернода помехи, а второй выход - с первым входом элемента 7 совпадения, второй вход кот рого соединен с выходом генератора стабильной частоты, счетчик 9, первый 10 и второй 11 запоминакщие бло ки, аналоговый сумматор 12, последо вательно соединенные первьй 13, вто рой 14, третий 15 и четвертьй 16 од новибраторы, блок 17 формирования низковольтного гармонического напря жения с частотой сети, На фиг, 2 приняты обозначения: 18 - форма сигнала сетевой помехи на входной клемме 1J 19 - форма информативной составляющей Uy входного сигнала на входной клемме 1; 20 - форма импульсов на выходе счет чика 9 21-24 - формы импульсов на выходах одновибраторов 13-16. Устройство работает следующим об разом. Входной сигнал, поступающий на входную клемму 1, представляет собо сумму гармонической помехи U и информативной составляющей U, , амплитуда которой изменяется в процессе подавления помехи. Время тактов интегрирования - величина постоянная, - г;.,;, Начало такТ.е. t. Ч-1, 2 тов интегрирования смещено относительно моментов времени, когда U О из-за наличия фазового сдвига между напряжением сети и помехи. Од нако, так как их частоты равны,, вел чина сдвига &t постоянна в камодом такте. Формирование,тактов интегрирования осуществляется так же, как в известном устройстве. По окончании такта trt 2 напряжение на выходе интегратора 4 описывается выражением: К и, г где К - коэффициент передачи входного сигнала на выход интегратора 4; составляющая выходного налряжения интегратора 4, пропорпдональная площади S (фиг. 2, 18); составляющая выходного напряжения интегратора 4, пропорциональнёя площади S . .(фиг. 2, 19). Очевидно, что и... + uU, 1-г ,В случае подавления помехи в информативной системе при подгонке резистора перед моментом окончания подгонки, имеет место следующее соотношение:ди(/ ди тогда + ,. + .J.. Un,., ки„., По окончании такта tf. с задержкой, определяемой одновибратером 13, по сигналу с одновибратора 14 запоминающем блоке 11 запоминается инверсное значение напряжения с выхода запоминающего блока 10. После этого по сигналу с одновибратора 15 в запоминающем блоке 10 запоминается напряжение U., а затем по сигналу с одновибратора 16 производится разряд интегратора 4. По окончании такта , на выходе интеграора 4 появ-ляется сигнал KUni.i KUxi., KUn. ,+ + , + дих, , де Ки,. -напряжение, пропорциональное Sj ; -напряжение, . %-, пропорциональное S, . Так же как и в гфедыдущем случае запоминаюп(ем блоке 11 запоминаетя инверсное значение напряжения с ыхода запоминающего блока 10,котоое в этот момент равно и„, а атем в запомин щий блик 10 записыается новое значение напряжения, авное Un., 3 После следуто его такта интегриро вания (tn ) напряжение на выходе ин тегратора 4 Uh. К Un; где К Uf, -напряжение, пропорциональное Sj ; К и. -напряжение, пропорциональное БЗ . В это же время напряжение на выходе аналогового сумматора 12 Кзи,. + .., - KU,j. , где К, К, К} - весовые коэффициен ты аналогового сум матора 12. Весовые коэффициенты К 1, К Kj 0,5. С учетом значений весовых коэффициентов выражение для Uftbix-i принимает вид: иьых.1 (KUn; + KU,i ) + + (0,5KL4.., + 0,5KUx; + + 0,5KuUxi ) - (0,5KUn;.2 + 0,5KU,. + KiUxi). Поскольку S, S 3 TO -KU. KUi.j . Проведя просто преобразование, получают вьфажение для на выходе сумматора 12 дл момента времени tf в виде: Ки. - 0,5K.AUx. Очевидно, что значения выходного напряжения сумматора 12 в моменты времени tj, tцt.j , t;., , tL, ... tt, также определяются этим общим выражением. При использовании предлагаемого устройства для контроля подгонки ре зисторов значение ступени изменения информативной составляющей определя ется единичным воздействием режущего инструмента на подгоняемьй резистор, т.е. изменением сопротивления резистора на ДК. Поскольку сигнал на запуск или остановку режущего Ш1струмента пода ется по результату анализа выходног напряжения данного устройства, один лишний импульс, которьй разрешается при нахождении выходного нап ряжения в зоне неопределенности пос ледуклцего анализирующего прибора, вызывает перерез резистора в извест ном устройстве на величину ДК, в то время как при использовании пред лагаемого устройства погрешность подгонки составляет . Увеличение быстродействия достигается тем, что данные о значении информативной составляющей входного сигнала получаются после каждого полутакта интегрирования, в то время как в известном устройстве - после окончания всего такта преобразования. Формула изобретения Устройство для подавления гармонической помехи в информативном сигнале, содержащее последовательно соединенные три интегратора, вход первого из которых соединен с входной клеммой устройства, управлякяцие входы первого и второго HHTerpaiiopoB подключены к первому выходу блока управления, первый вход которого соединен с выходом блока вьщеления полупериода помехи, а второй выход блока управления через последовательно соединенные элемент совпадения и счетчик подключен к его второму входу, третий выход блока управления соединен с установочным входом счетчика, второй вход элемента совпадения соединен с вькодом генератора стабильной частоты, отлич аю- щ е е с я тем, что, с целью повышения точности и быстродействия подавления гармонической помехи в информативном сигнале с изменяющейся амплитудой, в него введены четыре одновибратора, два запоминающих блока, аналоговый сумматор и блок формирования низковольтного гармонического напря- йсения с частотой сети, при этом выход счетчика через последовательно соединенные первый, второй, третий и четвертый одновибраторы подключены к управляющему входу третьего интегратора, вьшолненного с дополнительным входом, выход третьего интегратора соединен с первьм входом аналогового сумматора непосредственно и через последовательно соединенные первый и второй запоминающие блоки с вторым входом аналогового сумматора, третий вход которого подключен к выходу первого запоминающего блока, выход аналогового сумматора является выходом устройства, управляющий вход первого запоминающего блока соединен с выходом третьего одновибратора, выход второго одновибратора подключен к управляющему вхо5 1267296«

ду второго запоминающего блока, мирования низковольтного гармонивход блока выделения полупериода ческого напряжения с частотой сепомехи соединен с выходом блока фор- ти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутационный фазометр | 1977 |

|

SU732761A1 |

| СЛЕДЯЩИЙ ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU434593A1 |

| Амплитудно-фазовый анализатор гармоник | 1984 |

|

SU1307371A1 |

| Измеритель амплитуды синусоидального напряжения | 1979 |

|

SU792158A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА | 2004 |

|

RU2263300C1 |

| Преобразователь действующего значения переменного напряжения в постоянное | 1980 |

|

SU911355A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU342296A1 |

| Аналоговое запонинающее устройство для узкополосного сигнала | 1988 |

|

SU1695391A1 |

| Устройство синхронизации электроразведочных приемников | 1987 |

|

SU1449961A1 |

| Анализатор гармоник | 1985 |

|

SU1347033A2 |

фиг.2

| Соколов В.Н | |||

| и др | |||

| Анализ мето дов помехозащищенности аналого-цифровых интегрирующих преобразователе в системах передачи информации | |||

| Приборы и системы управления, 1977, № 2, с | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Шляндин В.М | |||

| Цифровые измеритель ные устройства | |||

| - М.: Высшая школа, 1981, с | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-10-30—Публикация

1985-04-08—Подача