1

14/-i99f)

Изобретение относится к технической физике, в частности к геоэлектро- разведочной аппаратуре, и может быть использовано для автономной синхронизации измерителей вызванной ноляри- зации (ВП).

Цель изобретения - уменьшение ошибки синхронизации.

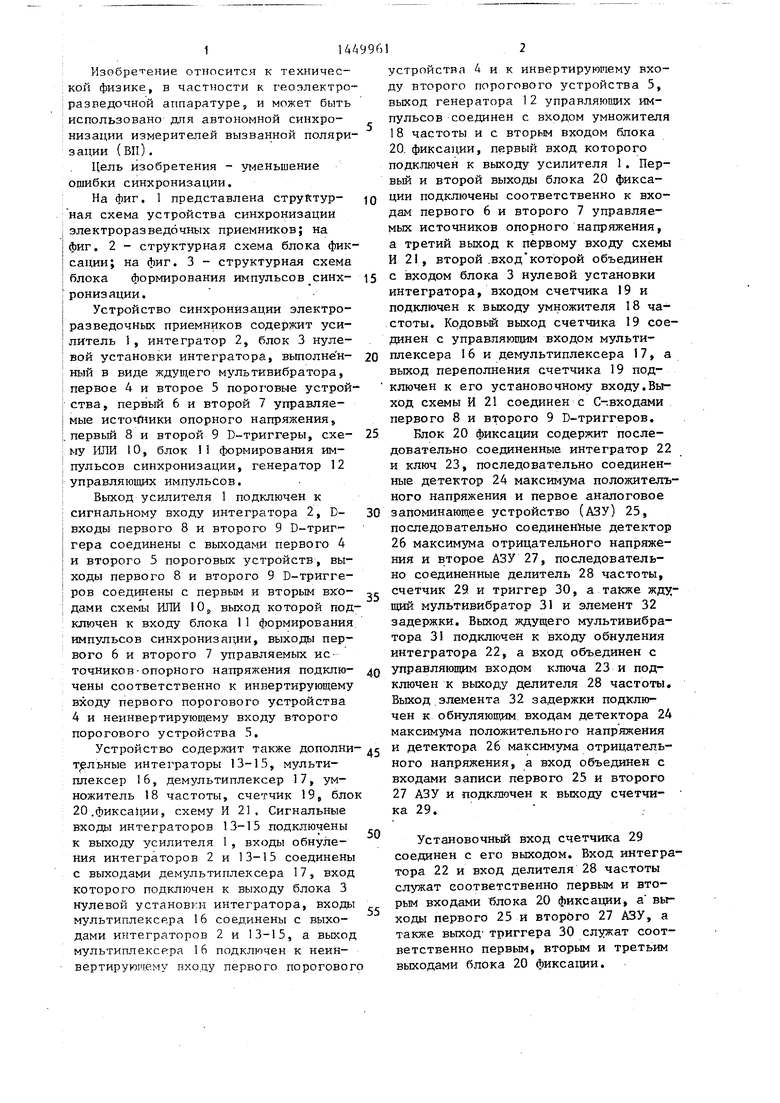

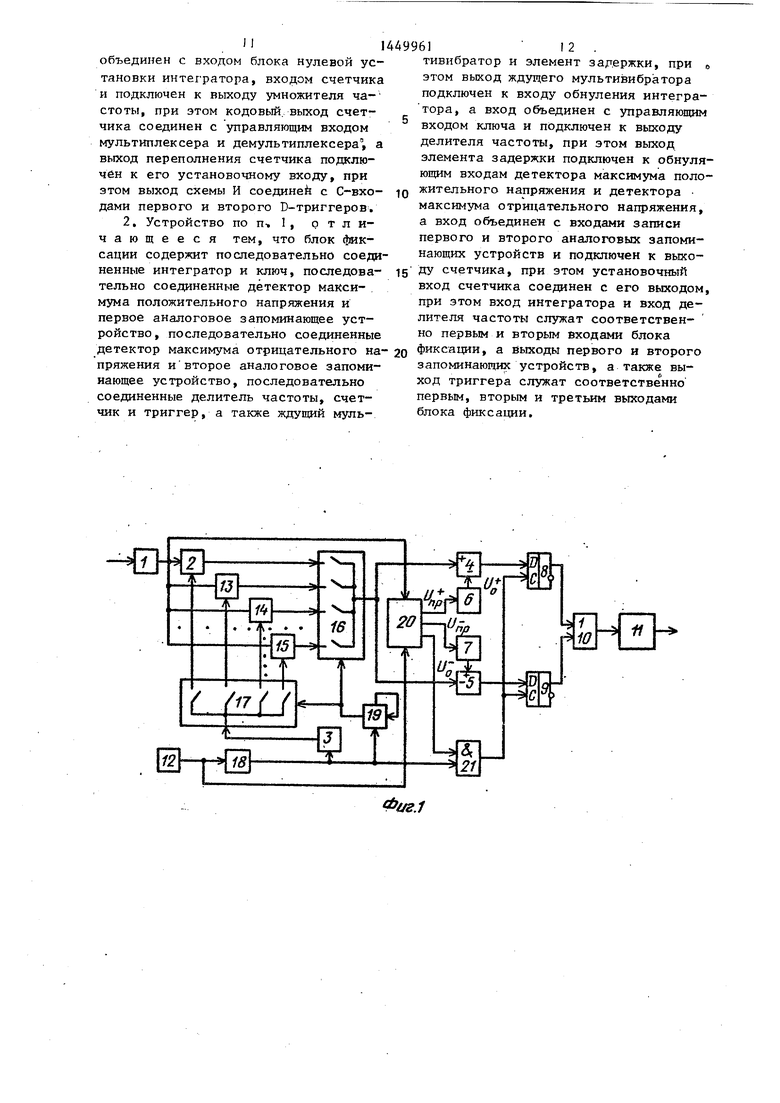

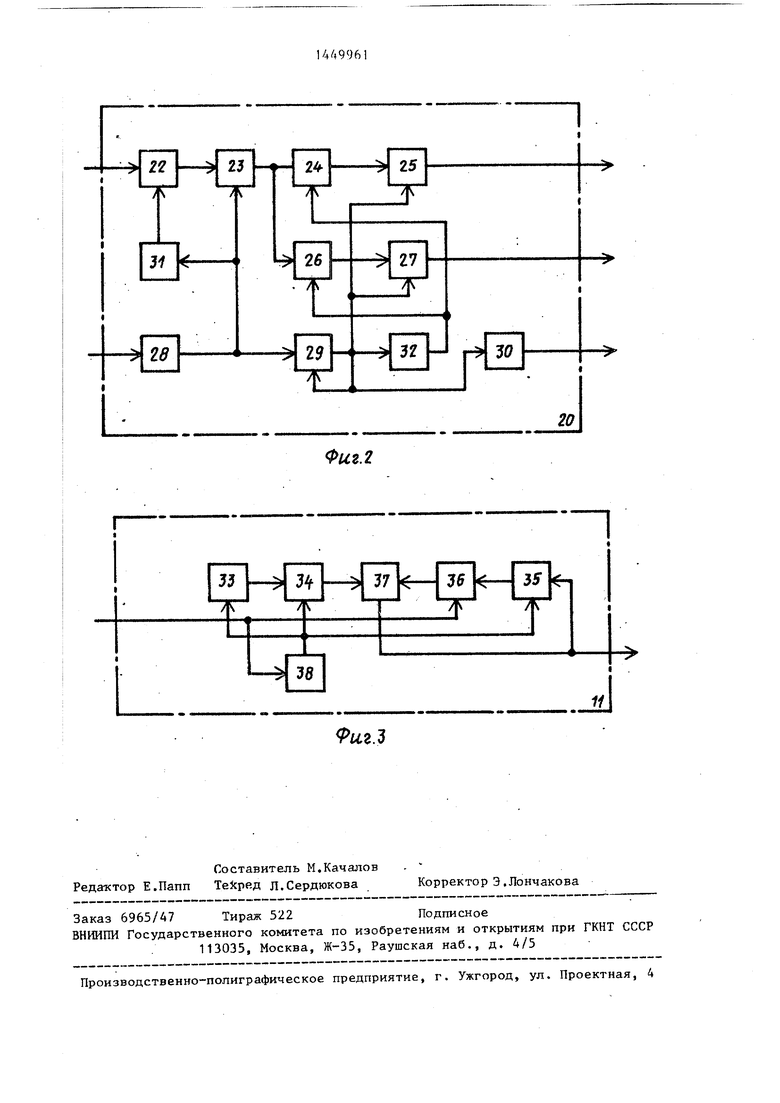

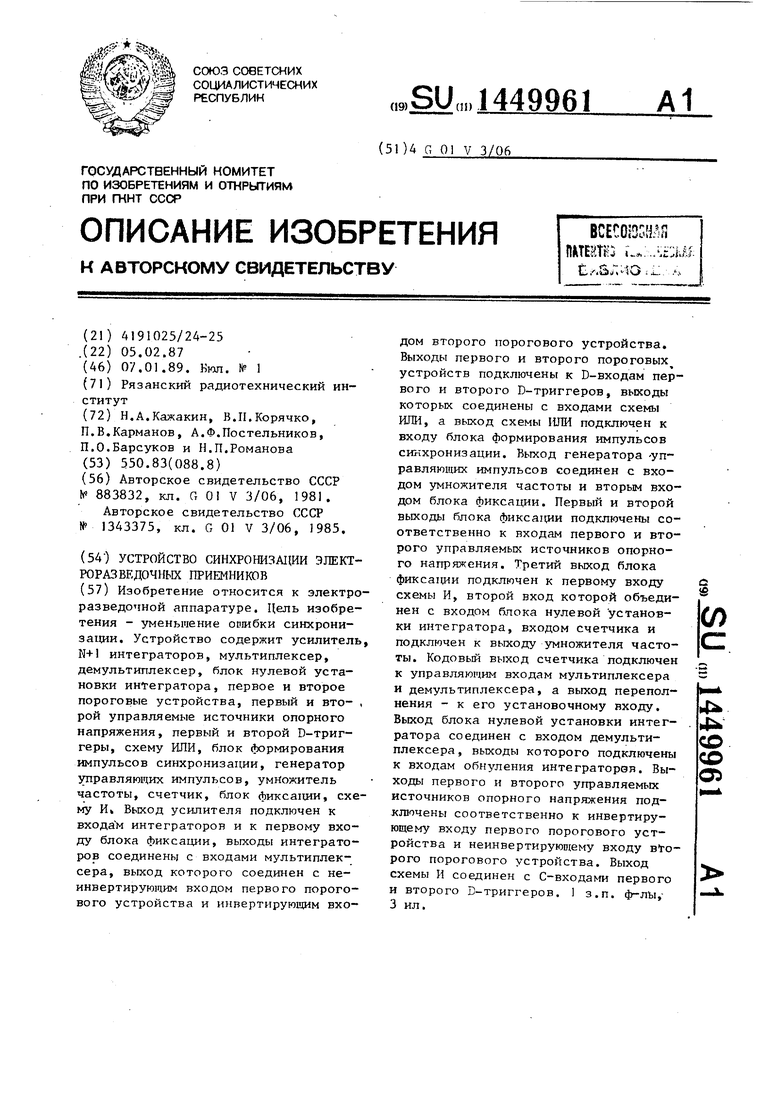

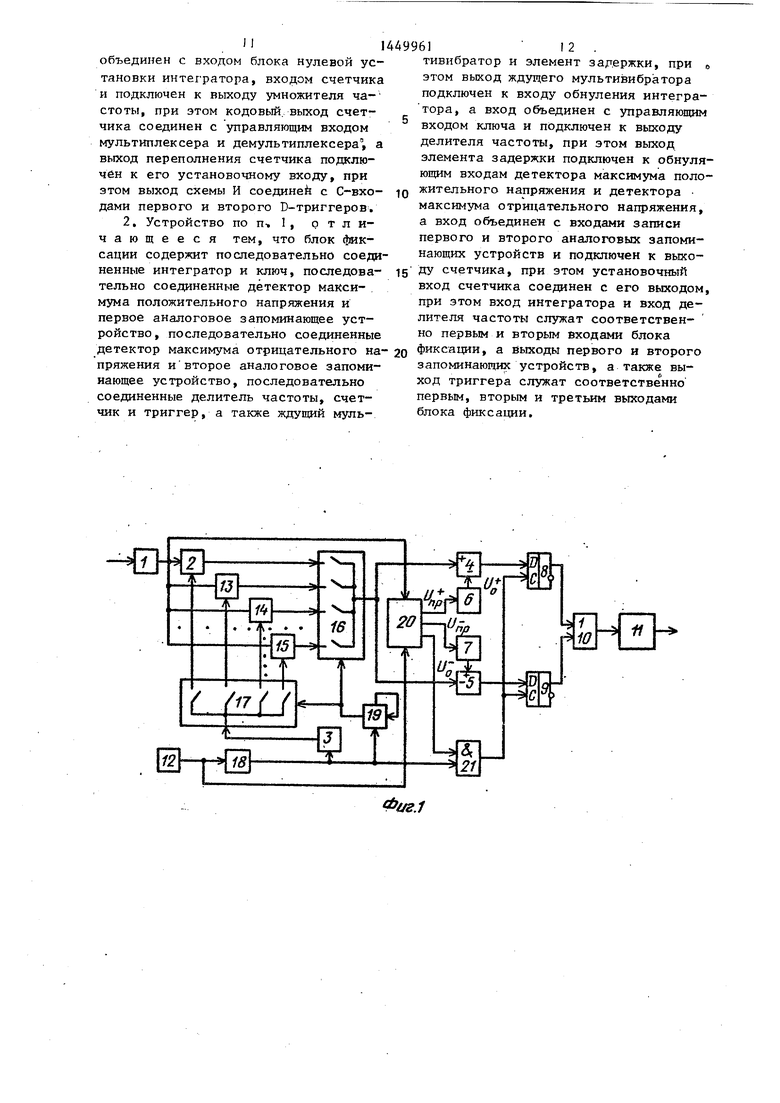

На фиг. 1 лредставлена структур- ная схема устройства синхронизации электроразведочных приемников; на фиг. 2 - структурная схема блока фиксации; на фиг. 3 - структурная схема блока формирования импульсов синх- ронизации.

Устройство синхронизации электроразведочных приемников содержит усилитель 1, интегратор 2, блок 3 нуле- i вой установки интегратора, вьтолнён-

ный в виде ждущего мультивибратора, первое 4 и второе 5 пороговые устрой- г ства, первьш 6 и второй 7 управляе- I мые истогй№ки опорного напряжения S I. первый 8 и второй 9 D-триггеры, схе- I ry 1ШИ 10, блок П формирования им- ; пульсов синхронизации, генератор 12 управляющих импульсов.

Выход усилителя 1 подключен к ; сигнальному входу интегратора 2, D- I входы первого 8 и второго 9 D-триг- I гера соединены с выходами первого 4 I и второго 5 пороговых устройств, вы- ходы первого 8 и второго 9 D-тригге- 1 ров соединены с первым и вторым вх о- дами схемы ИЛИ 10,, выход которой подключен к входу блока 11 формирования импульсов синхронизaiyra, выходы первого 6 и второго 7 управляемых источников -опорно го напряжения подкпю- чены соответственно к инвертирующему входу первого порогового устройства 4 и неинвертирующему входу второго порогового устройства 5.

Устройство содержит также дополни тыльные интеграторы 13-15, мульти- плексер 16, демультиплексер 17, умножитель 18 частоты, счетчик 19, бло 20.фиксации, схему И 21, Сигнальные входы интеграторов 13-15 подключены к выходу усилителя 1, входы обнуления интеграторов 2 и 13-15 соединены с выходами демультиплексера 17, вход которого подключен к выходу блока 3 нулевой установки интегратора, входы мультиплекср,ра 16 соединены с выходами интеграторов 2 и 13-15, а вькод мультиплексора 16 подключен к неин- вертирую1цему входу первого пороговог

5

0 с о

д

5

12

устройства 4 и к инвертирующему входу второго порогового устройства 5, выход генератора 12 управляющих импульсов соединен с входом умножителя 18 частоты и с вторым входом блока 20. фиксации, первый вход которого подключен к выходу усилителя 1. Первьш и второй выходы блока 20 фиксации подключены соответственно к входам первого 6 и второго 7 управляемых источников опорного напряжения, а третий выход к первому входу схемы И 21, второй .вход которой объединен с входом блока 3 нулевой установки интегратора, входом счетчика 19 и подключен к выходу умножителя 18 ча стоты. Крдовьй выход счетчика 19 сое- данен с управляющим входом мульти- плексера 16 и демультиплексера 17, а выход переполнения счетчика 19 подключен к его установочному входу.Выход схемы И 21 соединен с С-.входами первого 8 и второго 9 D-триггеров,

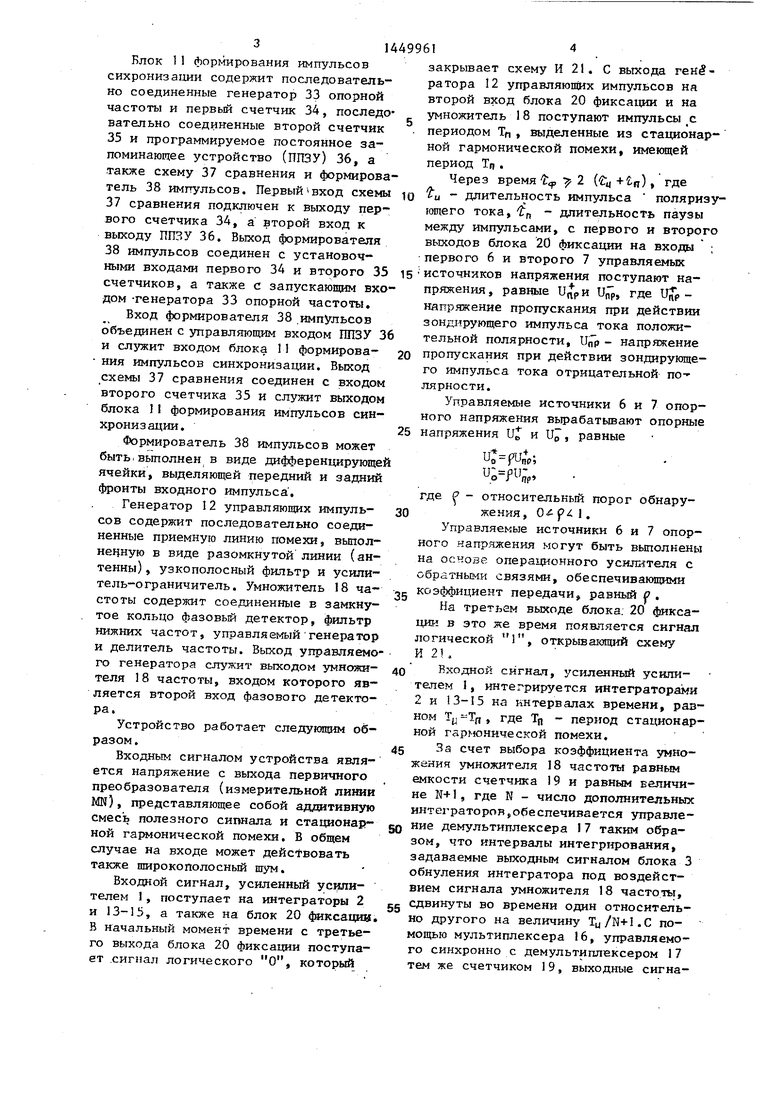

Блок 20 фиксации содержит последовательно соединенные интегратор 22 и ключ 23, последовательно соединенные детектор 24 максимума положительного напряжения и первое аналоговое запоминающее устройство (АЗУ) 25, последовательно соединенные детектор

26максимума отрицательного напряжения и второе АЗУ 27, последовательно соединенные делитель 28 частоты, счетчик 29 и триггер 30, а также ждущий мультивибратор 31 и элемент 32 задержки. Выход ждущего мультивибратора 3 подключен к входу обнуления интегратора 22, а вход объединен с управляющим входом ключа 23 и подключен к выходу делителя 28 частоты, Выход.элемента 32 задержки подключен к обнуляющим входам детектора 24 максимума положительного напряжения

и детектора 26 максимума отрицательного напряжения, а вход объединен с входами записи первого 25 и второго

27АЗУ и подключен к выходу счетчи- ка 29. .

Установочный вход счетчика 29 соединен с его выходом. Вход интегратора 22 и вход делителя 28 частоты служат соответственно первым и вторым входами Шока 20 фиксации, а выходы первого 25 и второго 27 АЗУ, а также ВЫХОД триггера 30 служат соответственно первым, вторым и третьим выходами блока 20 фиксации.

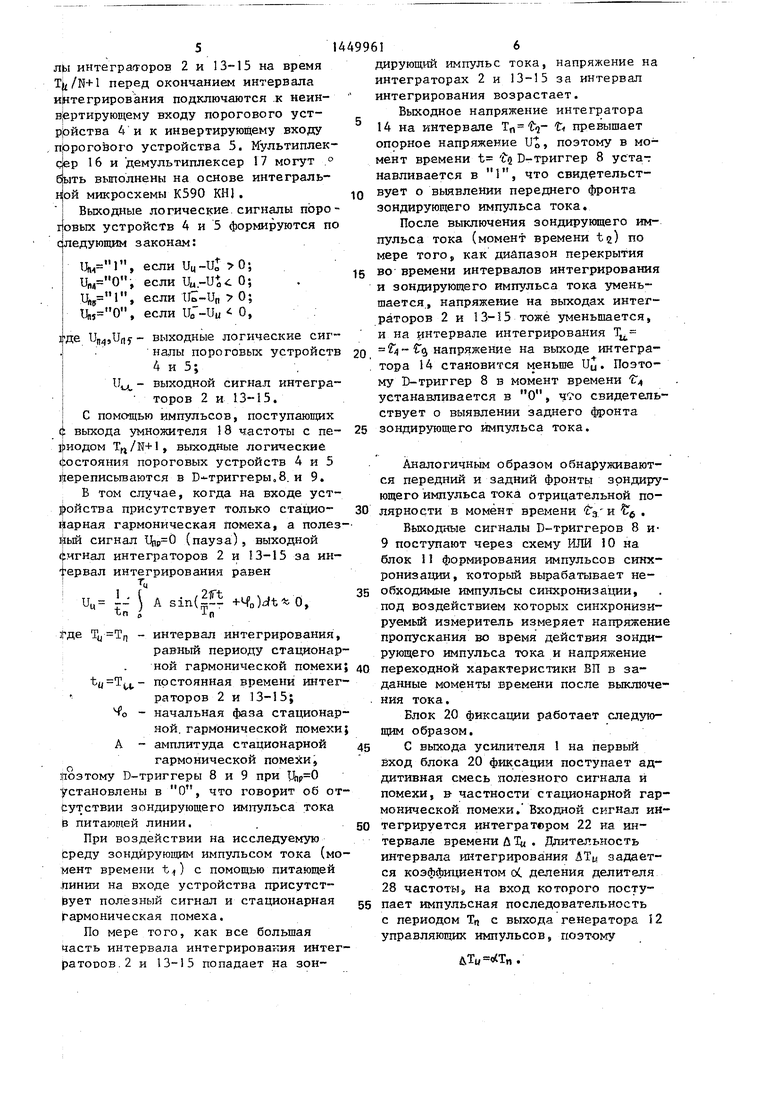

Блок 11 формирования импульсов сихронизации содержит последовательно соединенные генератор 33 опорной частоты и первый счетчик 34, последовательно соединенные второй счетчик 35 и программируемое постоянное запоминающее устройство (ППЗУ) 36, а также схему 37 сравнения и формирователь 38 импульсов. Первый ВХОД схемы

37сравнения подключен к выходу первого счетчика 34, а второй вход к выходу ППЗУ 36. Выход формирователя

38импульсов соединен с установоч14499614

закрывает схему И 21. С выхода ратора 12 управляющих импульсов ня второй вход блока 20 фиксации и на g умножитель 18 поступают импульсы с периодом Тп, выделенные из стационарной гармонической помехи, имеющей период Тп.

Через время t, 2 (), где 10 и длительность импульса поляризующего тока, tf, - длительность паузы между импульсами, с первого и второго вькодов блока 20 фиксации на входы

.ход.™, „ерес™ ,1 С 35 ,s Г„:Г:,.

«::™:;:ра4ПГо :оТ:™г™ - ™ ™- Вход формирователя 38 .импульсов объединен с управляющим входом ППЗУ 36 и служит входом блока 11 формирова- ния импульсов синхронизации. Выход схемы 37 сравнения соединен с входом второго счетчика 35 и служит выходом блока II формирования импульсов синхронизации.

Формирователь 38 импульсов может быть.вьтолнен в виде дифференцирующей ячейки, выделяющей передний и задний фронты входного импульса ,

30

Генератор 12 управляющих импульсов содержит последовательно соединенные приемную линию помехи, выпол- нечную в виде разомкнутой линии (антенны) , узкополосный фильтр и усили1 1 Г (1г

напряжение пропускания при действии зондирующего импульса тока положительной полярности, Ufll) - напряжение

20 пропускания при действии зондирующего импульса тока отрицательной пО лярности.

Управляемые источники 6 и 7 опорного напряжения вырабатывают опорные

25 напряжения U и Uj, равные

,;,

где - относительный порог обнаружения, 0 р 1.

Управляемые источники 6 и 7 опорного напр.яжения могут быть выполнены на основе операционного усилителя с обратными связями, обеспечивакицими

Т 18 ча- . коэффициент передачи, равный7. стоты содержит соединенные в замкну- На третьем выходе блока 20 икса- тое кольцо фазовый детектор, фильтр цин в это же время появляется нижних частот, управляемь.й генератор логической 1 Ч Le и делитель частоты. Выход управляемо-. И 2.ткрывающий схему

40

ГО генератора служит выходом умножителя 18 частоты, входом которого является второй вход фазового детектора.

Устройство работает следующим образом .

Входным сигналом устройства является напряжение с выхода первичного преобразователя (измерительной линии MN), представляющее собой адгдативную

Входной сигнап, усиленный усилителем 1, интегрируется интеграторг№}и 2 и 13-15 на интервалах времени, равном Tf. -Tf,, где Тр - период стационарной гар юнической помехи. 45 За счет выбора коэффициента умножения умножителя 18 частоты равным емкости счетчика 19 и равным величине N+1, где N - число дополнительных интеграторов,обеспечивается управленГ.-г.г .:„ ,г--г

ной гагмонической помехи. В общем случае на входе может действовать также щирокополосный шум.

Входной сигнал, усиленный ускьпи- телем 1, поступает на интеграторы 2 и 13-15, а также на блок 20 4жксации В начальный момент времени с третьего выхода блока 20 фиксации поступает .сигнал логического О, который

зом, что интервалы интегрирования, задаваемые выходным сигналом блока 3 обнуления интегратора под воздействием сигнала умножителя 18 частоты, 55 сдвинуты во времени один относительно другого на величину Тц/N+l.C помощью мультиплексера 16, управляемого синхронно с демультиштексером 17 тем же счетчиком 19, выходные сигна ™ ™- 0

(1г

напряжение пропускания при действии зондирующего импульса тока положительной полярности, Ufll) - напряжение

0 пропускания при действии зондирующего импульса тока отрицательной пО лярности.

Управляемые источники 6 и 7 опорного напряжения вырабатывают опорные

5 напряжения U и Uj, равные

,;,

где - относительный порог обнаружения, 0 р 1.

Управляемые источники 6 и 7 опорного напр.яжения могут быть выполнены на основе операционного усилителя с обратными связями, обеспечивакицими

коэффициент передачи, равный7. На третьем выходе блока 20 икса- цин в это же время появляется логической 1 Ч Le И 2.ткрывающий схему

40

Входной сигнап, усиленный усилителем 1, интегрируется интеграторг№}и 2 и 13-15 на интервалах времени, равном Tf. -Tf,, где Тр - период стационарной гар юнической помехи. 45 За счет выбора коэффициента умножения умножителя 18 частоты равным емкости счетчика 19 и равным величине N+1, где N - число дополнительных интеграторов,обеспечивается управле .:„ ,г--г

.:„ ,г--г

зом, что интервалы интегрирования, задаваемые выходным сигналом блока 3 обнуления интегратора под воздействием сигнала умножителя 18 частоты, сдвинуты во времени один относительно другого на величину Тц/N+l.C помощью мультиплексера 16, управляемого синхронно с демультиштексером 17 тем же счетчиком 19, выходные сигналМ интеграггоров 2 и 13-15 на время TL/N+1 перед окончанием интервала интегрирования подключаются .к неин- в ртирующему входу порогового уст- р|ойства 4 и к инвертирующему входу , порогового устройства 5. Мультиплек- сер 16 и демультиплексер 17 могут .° быть выполнены на основе интеграль- микросхемы К590 KHI .

Выходные логичес 1сие сигналы пороговых устройств 4 и 5 формируются по цледующим законам:

, если UK-U 0-, , если 0; и,, если Ul-Un 0; H,0, если Uo -Uu О,.

14499616

дирующий импульс тока, напряжение на интеграторах 2 и 13-15 за интервал интегрирования возрастает,

Выходное напряжение интегратора 14 на интервале t превышает опорное напряжение Ut, поэтому в момент времени t ffj D-триггер 8 уста-г

навливается в

Т

что свид тельст15

1Q вует о выявлении переднего фронта зондирующего импульса тока.

После выключения зондирующего импульса тока (момент времени tj) по мере того 5 как диапазон перекрытия во времени интервалов интегрирования и зондирующего импульса тока уменьшается, напряжение на выходах интеграторов 2 и 13-15 тоже уменьшается, и на интервале интегрирования Т f4 Г напряжение на выходе интегратора 14 становится меньше и. Поэтому D-триггер 8 в момент времени t устанавливается в О, свидетельствует о выявлении заднего фронта зондирующего импульса тока.

iffle - выходные логические сигналы пороговых устройств 4 и 5;.

выходной сигнал интеграторов 2 и 13-15.

С помощью импульсов, поступающих ф выхода умножителя 18 частоты с пе- 1|)иодом Tft/N+1, выходные логические фостояния пороговых устройств 4 и 5 1 1ереписьгоаются в Б-триггеры,8. и 9.

В том случае, когда на входе уст- | ойства присутствует только стацио- 1Црная гармоническая помеха, а пояез фьш сигнал (пауза), выходной Сигнал интеграторов 2 и 13-15 за ин

тервал интегрирования равен

2П

1- А sin(lii ч-4 Jdt О, --Ln

tn

де интервал интегрирования, равный периоду стационарной гармонической помехи; 40 переходной характеристики ВП в за- ,- постоянная времени интег- данные моменты времени после выключераторов 2 и 13-15; , ния тока. Ч о - начальная фаза стационар- Блок 20 фиксации работает следуюяой. гармонической помехи; щим образом. А - амплитуда стационарной

гармонической помехи, поэтому D-триггеры 8 и 9 при

45

С выхода усипителя 1 на первый вход блока 20 фиксации поступает аддитивная смесь полезного сигнала и помехи, в- частности стационарной гармонической помехи, Входной сигнал инустановлены в О , что говорит об от- Ьутствии зондирующего им1тульса тока питающей линии.

При воздействии на исследуемую Среду зондирующим импульсом тока (мо- :мент времени t) с помощью питающей Линии на входе устройства присутствует полезный сигнал и стационарная Гармоническая помеха.

По мере того, как все большая Часть интервала интегрирования интеграторов. 2 и 13-15 попадает на зоннавливается в

Т

что свид тельст

вует о выявлении переднего фронта зондирующего импульса тока.

После выключения зондирующего импульса тока (момент времени tj) по мере того 5 как диапазон перекрытия во времени интервалов интегрирования и зондирующего импульса тока уменьшается, напряжение на выходах интеграторов 2 и 13-15 тоже уменьшается, и на интервале интегрирования Т f4 Г напряжение на выходе интегратора 14 становится меньше и. Поэтому D-триггер 8 в момент времени t устанавливается в О, свидетельствует о выявлении заднего фронта зондирующего импульса тока.

Аналогичным образом обнаруживаются передний и задний фронты зондирующего имдульса тока отрицательной полярности в момент времени t g и .

Выходные сигналы D-триггвров 8 и- 9 поступают через схему ИШ 10 на блок 1I формирования импульсов синхронизации, который вырабатывает необходимые импульсы синхронизации, под воздействием которых синхронизируемый измеритель измеряет напряжение пропускания во время действия зондирующего импульса тока и напряжение

щим образом.

С выхода усипителя 1 на первый вход блока 20 фиксации поступает аддитивная смесь полезного сигнала и помехи, в- частности стационарной гармонической помехи, Входной сигнал интегрируется интегратвром 22 на интервале времени ЛI . Длительность интервала интегрирова ния АТи задается коэффициентом о(. деления делителя 28 частоты, на вход которого поступает импульсная последовательность с периодом Тп с выхода генератора 12 управляющих импульсов, поэтому

йТц)4Тп .

Коэффициент (X деления выбирается из условия

о( fu/2,

что обеспечивает с одной стороны глубокое подавление стационарной гармонической помехи за счет кратности интервала интегрирования периоду стационарной гармонической помехи, а с другой стороны лопадание не менее одного полного интервала АTU интегрирования на время действия зондиру ющего импульса тока. Обнуление интегратора 22 осуществляется выходным сигналом ждущего мультивибратора 31, который запускается выходными импульсами на выходе делителя 28 частоты. Выходной сигнал интегратора 22 в конце интервала -интегрирования ДТн подключается с помощью ключа 23 к входам детектора 24 максимзт а положительного напряжения и детектора 26 максимума отрицательного напряжения, которые после прохождения импульсов зондирующего тока положительной и отрицательной полярности фиксируют соответственно напряжения Unp и Unp. Через интервал времени Сер 2(( ), задаваемый емкостью счетчика 29, выходные напряжения и детектора 24 максимума положительного напряжения и детектора 26 максимума отрицательного напряжения переписываются в АЗУ 25 и 27 .под воздействием импульса, который вьфабатывается счетчиком 29. Кроме этого, импульс, вы-. рабатываемый счетчиком 29, устанавливает триггер 30 в состояние 1, а через некоторое время, определяемое элементом задержки, обнуляет детектор 24 максимума положительного напряжения и детектора 26 максимзта отрицательного напряжения. В дальнейшем работа узлов блока 20 фиксации повторяется.

Таким образом, блок 20 фиксации вырабатывает через время D jp после включения на третьем входе сигнал Jjo- гической 1, а на первом и втором выходах значения напряжений Unp и Unp которые через интервал времениt уточняются по мере возможности, изменений входного сигнала из-за нестабильности источника тока генераторной установки, а также изменения напряжения собственной поляризации приемных электродов.

Блок I1 формирования импульсов « синхронизации работает следующим образом.

Выходные сигналы D-триггеров 8 и ,9, логически объединенные с помощью схемы ИЛИ 10, поступают на вход блока 11 формирования импульсов синхронизации, под воздействием которого 10 формирователе 38 импульсов в момент времени 2 , -4 , и 4 вырабатывает короткие импульсы. Первый же импульс в момент времени tq с выхода формирователя 38 запускает генератор 15 33 опорной частоты, а счетчики 34 и 35 устанавливаются в исходное состояние .

В счетчике 34 фиксируется код под воздействием импульсов опорной ча- Q стоты, пропорциональный текущему времени действия зондирующего импульса |тока, который поступает на первый вход схемы 37 сравнения. На второй шход схемы 37 сравнения поступает 5 код с выхода ПГОУ 36, пропорциональ- ньш заданному моменту измерения напряжения пропускания. В момент равенства кодов схема 37 сравнения вырабатывает импульс, который поступает Q на выход блока 1 формирования импульсов синхронизации для запуска синхронизируемого измерителя, 1-1мпульс с выхода формирователя 38 импульсов в момент времени Гл уста- навливается в исходное состояние счетчика 34 и 35. С момента времени ta счетчик 34 начинает накапливать код, пропорциональный текзгщему времени паузы. Под воздействием входного Q сигнала на входе формирователя I импульсов синхронизации, который на интервале времени Г -fs равен О, из ППЗУ 36 выиграются коды, пропорциональные моментам измерения напря- д жения переходной характеристики ВП. Очередность выбора моментов измерения напр5таения Ug из ППЗУ 36 определяет счетчик 35, подавая код на адресный вход ППЗУ 36,

50

В момент равенства кодов схема 37 вырабатывает импульс, поступающий на выход блока I1 формирования импульсов синхронизации, а также посту- gg пающий на вход счетчика 35, который увеличивает свой код, выбирая из ППЗУ 36 очередной код, пропорциональный следующему моменту.измерения напряжения ВП. С течением времени рабоta всех узлов блока 11 формирования Импульсов синхронизации повторяется. Генератор 12 управляющих импуль- сов работает следующим образом.

На входе приемной линии помехи, : ыполнённой в виде разомкнутой ли- 1ии (антенны), действует стационарная гармоническая помеха, имеющая та сую же частоту, что и стационарная гармоническая помеха на измеритель- юй линии MN, НО отличающаяся по ровню и начальным сдвигом фазы.

Принимаемая приемной линией помехи Стационарная гармоническая помеха, пройдя узкополоснь1й фильтр, настроенный на частоту стационарной гармонической помехи, усиливается усилителем-ограничителем, после чего она лревращается в поток прямоугольных «мпульсов с периодом То и поступает на выход генератора 12 управляющих :импульсов.

I Умножитель 18 частоты работает радующим образом.

I На второй вход фазового детектора постзшает периодическая последо- ательность импульсов с периодом Тд На первый вход фазового детекто- jpa с выхода делителя частоты пь:сту- ают прямоугольные импульсы типа . Меандр с периодом следования Тд . множитель 1Ь частоты представляет робой классическое кольцо фазовой автоподстройки частоты, поэтому в (Установившемся режиме работы справед пиво соотношение Т , и, следовательно, период быходного сигнала ум- |ножителя 1 8 частоты равен Т /К, где |Кд - коэффициент деления делителя . частоты.

Таким образом, введение N дополнительных интеграторов 13-15, муль- типлексера 16, демультиплексера 17, умножителя 18 частоты, счетчика 19, блока 20 фиксации и схемы И 21 и новых связей позволяет уменьшить временной интервал оценки входного сигнала без уменьшения длительности интервала интегрирования интеграторов 2 и 13-15, определяемого перидом стагшонарной гармонической помехи, а также обеспечивает слежение опорных напряжений за изменениями н Пряжения пропускания, поддерживая постоянным относительный порог обнаружения, что позволяет уменьшить среднее значение ошибки синхронизации и средкеквадратическое отклоне

5

0

ние ошибки синхронизации от среднего значения.

Формула изобретения

1. Устройство синхронизации электроразведочных приемников, содержат щее усилитель, интегратор, блок нулевой установки интегратора, первое и второе пороговые устройства, первый и второй управляемые источники опорного напряжения, первый и второй D-триггеры, схему ИЛИ, блок формирования импульсов синхронизации, генератор управляющих импульсов, при этом в.ьгход усилителя подключен к сигнальному входу интегратора, D-входы первого и второго D-триггеров соединены с выходами первого и второго пороговых устройств выходы первого и второго D-триггеров соединены с первым и вторым входами, схемы ШШ, выход которой подключен к входу бло5 ка формирования импульсов синхрониза- циу, выходы первого и второго управляемых источников опорного напряжения подключены соответственно к инвертирующему входу первого порогового устройства и неинвертирующему входу второго порогового устройства, отличающееся тем, что, с целью уменьшения ошибки синхронизации, р него дополнительно введены К-интег- раторов, мультиплексер, демультиплек- сер, умножитель частоты, счетчик, блок фиксации, схема И, при этом сигнальные входы дополнительно введенных интеграторов подключены к выходу усилителя, входы обнуления интеграторов соединены с выходами демультиплексе- ра, вход которого подключен к выходу блока нулевой установки интегратора, входы мультиплексера соединены с выходами интеграторов, а выход мультиплексера подключен к неинвертирующему входу первого порогового устройства и к инвертирующему входу второго порогового устройства, выход генератора управляющих импульсов соединен с входом умножителя частоты и с вторым входом блока фиксащте, первый вход котЬрого подключен к выходу усилителя, при этом первьй и второй выходы блока

g фиксации подключены соответственно к входам первого и второго управляемых источников опорного чапряже- ния, а третий выход - к первому входу схемы И, второй вход которой

0

5

0

5

0

объединен с входом блока нулевой установки интегратора, входом счетчика и подключен к выходу умножителя ча- сто ты, при этом кодовый.-выход счетчика соединен с управляющим входом мультиплексера и демультиплексера , а выход переполнения счетчика подключен к его установочному входу, при этом выход схемы И соединей с С-вхо- дами первого и второго D-триггеров. 2, Устройство по П-, 1 , отличающееся тем, что блок (фиксации содержит последовательно соединенные интегратор и ключ, последовательно соединенные детектор максимума положительного напряжения и первое аналоговое запоминающее устройство , последовательно соединенные детектор максимума отрицательного напряжения и второе аналоговое запоминающее устройство, последовательно соединенные делитель частоты, счетчик и триггер, а также ждущий муль449961

12

тивибратор и элемент задержки, при в этом выход ждущего мультивибратора подключен к входу обнуления интегра- тора, а вход объединен с управляющим входом ключа и подключен к выходу делителя частоты, при этом выход элемента задержки подключен к обнуляющим входам детектора максимума поло Q жительного напряжения и детектора максимума отрицательного напряжения, а вход объединен с входами записи первого и второго аналоговых запоминающих устройств и подключен к выхо15 ДУ счетчика, при этом установочный вход счетчика соединен с его выходом, при этом вход интегратора и вход делителя частоты служат соответствен- но первым и вторым входами блока

20 фиксации, а выходы первого и второго запоминающих устройств, а также выход триггера служат соответстве нно первым, вторым и третьим выходами блока фиксации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации электроразведочных приемников | 1985 |

|

SU1343375A1 |

| Устройство синхронизации электроразведочных приемников | 1989 |

|

SU1659941A2 |

| Многоканальный широтно-импульсный регулятор температуры (его варианты) | 1981 |

|

SU962883A1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| АВТОКОРРЕЛЯЦИОННОЕ УСТРОЙСТВО ВСКРЫТИЯ СПЕКТРАЛЬНО-ВРЕМЕННОЙ СТРУКТУРЫ СИГНАЛОВ ЦИФРОВЫХ СИСТЕМ СВЯЗИ | 2008 |

|

RU2365051C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1985 |

|

SU1414127A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ | 1991 |

|

RU2020595C1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

Изобретение относится к электроразведочной аппаратуре. Цель изобретения - уменьшение овмбки синхронизации. Устройство содержит усилитель, N+1 интеграторов, мультиплексер, демультиплексер, блок нулевой установки интегратора, первое и второе пороговые устройства, первый и вто- , рой управляемые источники опорного напряжения, первый и второй D-триг- геры, схему ИЛИ, блок формирования импульсов синхронизации, генератор управляющих импульсов, умножитель частоты, счетчик, блок Ликса1щи, схему И Выход усилителя подключен к входа м интеграторов и к первому входу блока фиксации, выходы интеграторов соединены с входами мультиплек- сера, выход которого соединен с неинвертирующим входом первого порогового устройства и и)1вертирующим входом второго порогового устройства. Выходы первого и второго пороговых устройств подключены к D-входам первого и второго D-триггеров, выходы которых соединены с входами схемы ИЛИ, а выход схемы ИЛИ подключен к входу блока формирования импульсов синхронизации. Выход генератора -управляющих импульсов соединен с входом умножителя частоты и вторым входом блока фиксации. Первый и второй выходы блока фикса1Ц1и подключены соответственно к входам первого и второго управляемых источников опорного напряжения. Третий выход блока фиксации подключен к первому входу схемы И, второй вход которой объединен с входом блока нулевой установки интегратора, входом счетчика и подключен к выходу умножителя частоты. Кодовый выход счетчика подключен к управляю1цим входам мультиплексера и демультиплексера, а выход переполнения - к его установочному входу. Выход блока нулевой установки интегратора соединен с входом демультиплексера, выходы которого подключены к входам обнуления интеграторэн. Выходы первого и второго управляемых источников опорного напряжения подключены соответственно к инвертирующему входу первого порогового устройства и неинвертирующему входу второго порогового устройства. Выход схемы И соединен с С-входаьш первого и второго D-триггеров. 1 з.п. ф-лы,- 3 ил. а $ (Л со со о

И

01/2.1

.2

9иг.

| Устройство синхронизации электроразведочных приемников | 1980 |

|

SU883832A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство синхронизации электроразведочных приемников | 1985 |

|

SU1343375A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-01-07—Публикация

1987-02-05—Подача