Изобретение относится к цифровой измерительной технике и может быть использовано в вольтметрах и информационно-измерительных системах при измерении амплитуды синусоидального напряжения, у которого имеется постоянная составляющая и низкая надежность.

Цель изобретения - повьшение надежности в работе путем автоматизации измерения амплитуды синусоидального напряжения при изменении его параметров и исключения случаев переполнения счетчиков.

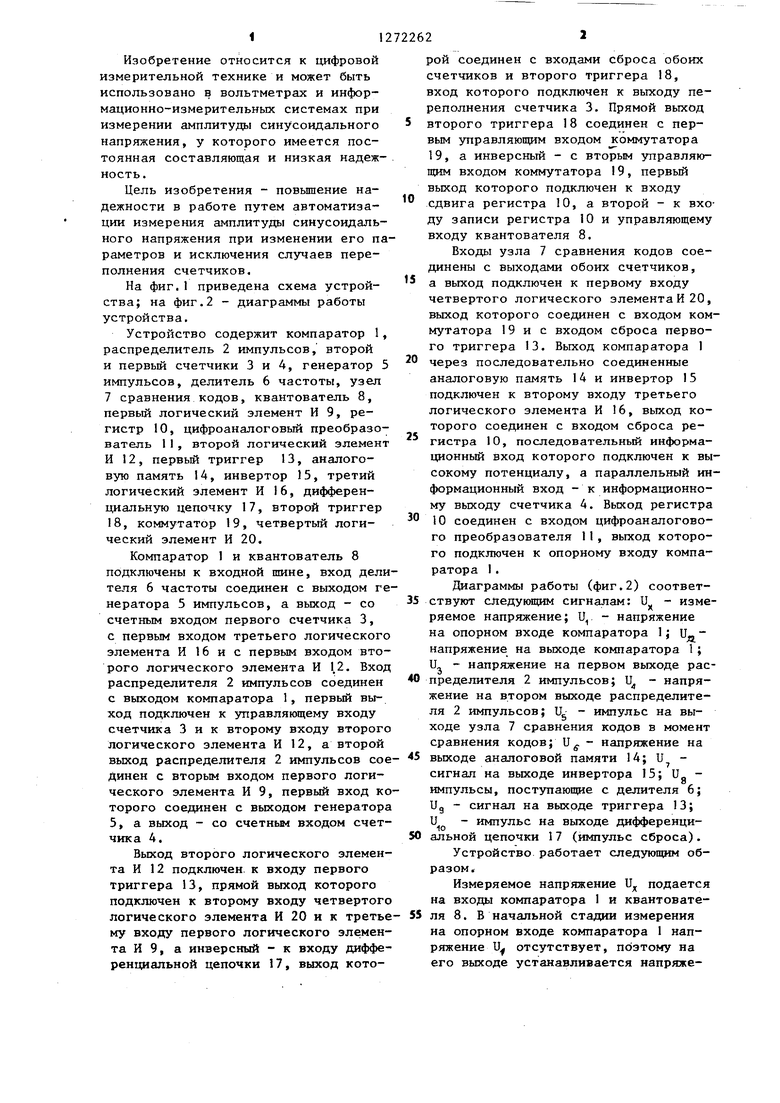

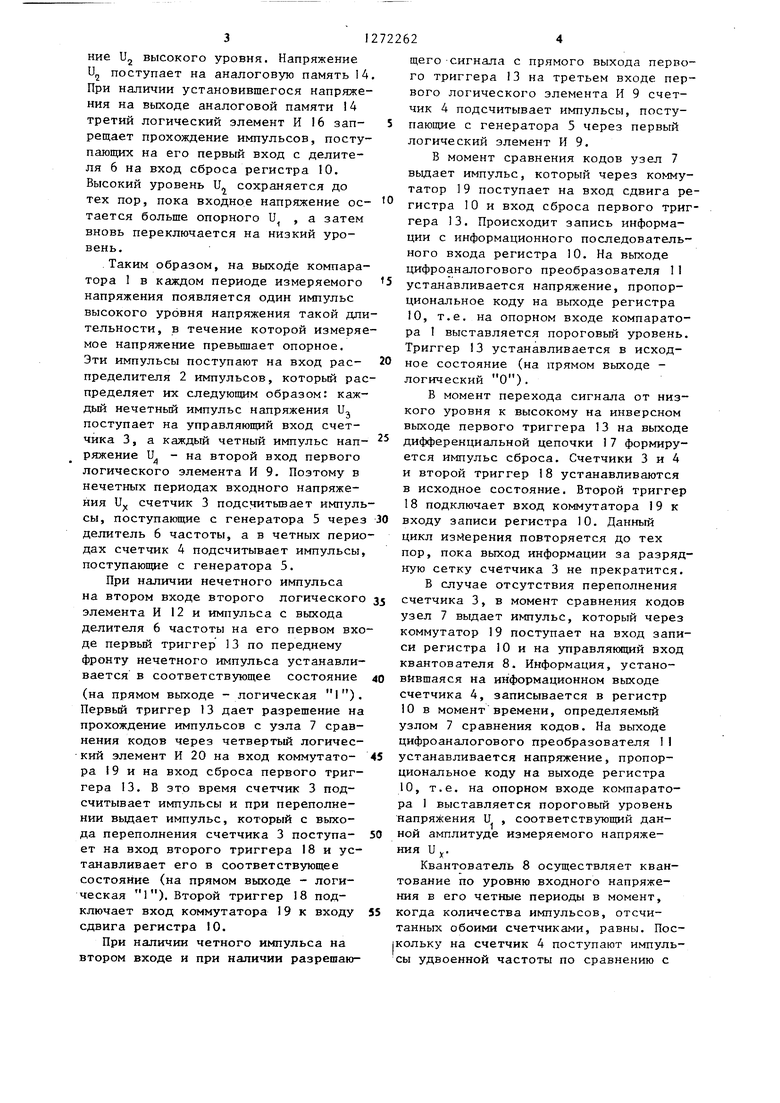

На фиг.1 приведена схема устройства; на фиг.2 - диаграммы работы устройства.

Устройство содержит компаратор 1, распределитель 2 импульсов, второй и первый счетчики 3 и 4, генератор 5 импульсов, делитель 6 частоты, узел 7 сравнения кодов, квантователь 8, первый логический элемент И 9, регистр 10, цифроаналоговый преобразователь 11, второй логический элемент И 12, первый триггер 13, аналоговую память 14, инвертор 15, третий логический элемент И 16, дифференциальную цепочку 17, второй триггер 18, коммутатор 19, четвертый логический элемент И 20.

Компаратор 1 и квантователь 8 подключены к входной шине, вход делителя 6 частоты соединен с выходом генератора 5 импульсов, а выход - со счетным входом первого счетчика 3, с первым входом третьего логического элемента И 16 и с первым входом второго логического элемента И 1.2. Вход распределителя 2 импульсов соединен с выходом компаратора 1, первый выход подключен к управляющему входу счетчика 3 и к второму входу второго логического элемента И 12, а второй выход распределителя 2 импульсов соединен с вторым входом первого логического элемента И 9, первый вход которого соединен с выходом генератора 5, а выход - со счетньм входом счетчика 4.

Выход второго логического элемента И 1 2 подключен, к входу первого триггера 13, прямой выход которого подключен к второму входу четвертого логического элемента И 20 и к третьему входу первого логического элемента И 9, а инверсный - к входу дифференциальной цепочки 17, выход которой соединен с входами сброса обоих счетчиков и второго триггера 18, вход которого подключен к выходу переполнения счетчика 3. Прямой выход

второго триггера 18 соединен с первым управляющим входом коммутатора 19, а инверсный - с вторым управляющим входом коммутатора I9, первый выход которого подключен к входу

сдвига регистра 10, а второй - к входу записи регистра 10 и управляющему входу квантователя 8.

Входы узла 7 сравнения кодов соединены с выходами обоих счетчиков,

а выход подключен к первому входу четвертого логического элемента И 20, выход которого соединен с входом коммутатора 19 и с входом сброса первого триггера 13. Выход компаратора 1

через последовательно соединенные

аналоговую память 14 и инвертор 15 подключен к второму входу третьего логического элемента И 16, выход которого соединен с входом сброса регистра 10, последовательный информационный вход которого подключен к высокому потенциалу, а параллельный информационный вход - к информационному выходу счетчика 4. Выход регистра

10 соединен с входом цифроаналогового преобразователя 11, выход которого подключен к опорному входу компаратора I .

Диаграммы работы (фиг.2) соответ5 ствуют следующим сигналам: U - измеряемое напряжение; Ц - напряжение на опорном входе компаратора 1; и„напряжение на выходе компаратора 1; и - напряжение на первом выходе рас0 пределителя 2 импульсов; 11 - напряжение на втором выходе распределителя 2 импульсов; U - импульс на выходе узла 7 сравнения кодов в момент сравнения кодов; U - напряжение на

5 выходе аналоговой памяти 14; U

сигнал на выходе инвертора 15; U импульсы, поступающие с делителя 6; Ug - сигнал на выходе триггера 13; и - импульс на выходе дифференци0 альной цепочки 17 (импульс сброса).

Устройство работает следующим образом.

Измеряемое напряжение U подается на входы компаратора 1 и квантовате5 ля 8. В начальной стадии измерения на опорном входе компаратора 1 напряжение U отсутствует, поэтому на его выходе устанавливается напряжение Uj высокого уровня. Напряжение и поступает на аналоговую память 14 При наличии установившегося напряже ния на выходе аналоговой памяти I4 третий логический элемент И 16 запрещает прохождение импульсов, посту пающих на его первый вход с делителя 6 на вход сброса регистра 10. Высокий уровень U сохраняется до тех пор, пока входное напряжение ос тается больше опорного U , а затем вновь переключается на низкий уровень. Таким образом, на выходе компара тора 1 в каждом периоде измеряемого напряжения появляется один импульс высокого уровня напряжения такой дли тельности, в течение которой измеря мое напряжение превышает опорное. Эти импульсы поступают на вход распределителя 2 импульсов, который ра пределяет их следующим образом: каждый нечетный импульс напряжения U поступает на управляющий вход счетчика 3, а каждый четный импульс напряжение U - на второй вход первого логического элемента И 9. Поэтому в нечетных периодах входного напряжения и счетчик 3 подсчитьшает импуль сы, поступающие с генератора 5 через делитель 6 частоты, а в четных перио дах счетчик 4 подсчитывает импульсы поступающие с генератора 5. При наличии нечетного импульса на втором входе второго логического элемента И 12 и импульса с выхода делителя 6 частоты на его первом вхо де первый триггер 13 по переднему фронту нечетного импульса устанавливается в соответствующее состояние (на прямом выходе - логическая 1). Первый триггер 13 дает разрешение на прохождение импульсов с узла 7 сравнения кодов через четвертый логический элемент И 20 на вход коммутатора I9 и на вход сброса первого триггера 13. В это время счетчик 3 подсчитывает импульсы и при переполнении выдает импульс, который с выхода переполнения счетчика 3 поступает на вход второго триггера 18 и устанавливает его в соответствующее состояние (на прямом выходе - логическая 1), Второй триггер 18 подключает вход коммутатора 19 к входу сдвига регистра 10. При наличии четного импульса на втором входе и при наличии разрешающего -сигнала с прямого выхода первого триггера 13 на третьем входе первого логического элемента И 9 счетчик 4 подсчитывает импульсы, поступающие с генератора 5 через первый логический элемент И 9. В момент сравнения кодов узел 7 выдает импульс, который через коммутатор I9 поступает на вход сдвига регистра 10 и вход сброса первого триггера 13. Происходит запись информации с информационного последовательного входа регистра 10. На выходе цифроаналогового преобразователя 11 устанавливается напряжение, пропорциональное коду на выходе регистра 10, т.е. на опорном входе компаратора I выставляется пороговый уровень. Триггер 13 устанавливается в исходное состояние (на прямом выходе логический О). В момент перехода сигнала от низкого уровня к высокому на инверсном выходе первого триггера 13 на выходе дифференциальной цепочки 17 формируется импульс сброса. Счетчики 3 и 4 и второй триггер 18 устанавливаются в исходное состояние. Второй триггер 18 подключает вход коммутатора 19 к входу записи регистра 10. Данный цикл измерения повторяется до тех пор, пока выход информации за разрядную сетку счетчика 3 не прекратится. В случае отсутствия переполнения счетчика 3, в момент сравнения кодов узел 7 вьщает импульс, который через коммутатор 19 поступает на вход записи регистра 10 и на управляющий вход квантователя 8. Информация, установившаяся на информационном выходе счетчика 4, записывается в регистр 10 в момент времени, определяемый узлом 7 сравнения кодов. На выходе цифроаналогового преобразователя 11 устанавливается напряжение, пропорциональное коду на выходе регистра 10, т.е. на опорном входе компаратора 1 выставляется пороговый уровень Напряжения U , соответствуюш 1й данной амплитуде измеряемого напряжения и . Квантователь 8 осуществляет квантование по уровню входного напряжения в его четные периоды в момент, когда количества импульсов, отсчитанных обоими счетчиками, равны. Посольку на счетчик 4 поступают импульсы удвоенной частоты по сравнению с

импульсами, поступающими на счетчик 3, то этот момент соответствует середине отрезка времени, в течение которого измеряемое напряжение U больше порогового U, . Исходя из симметричности синусоидального напряжения относительно середины указанного отрезка времени следует, что в этот момент времени, определяемый при помощи узла 7 сравнения кодов, напряжение достигает своего максимального значения.

При изменении амплитуды входного напряжения U автоматически изменяется пороговый уровень напряжения и с выхода цифроаналогового преобразователя 11, т.е. каждому значению входного напряжения U соответствует свой пороговый уровень, что исключает выход информации за разрядную сетку счетчика 3.

В том случае, когда опорное напряжение и больше входного U, на выхода компаратора 1 устанавливается напряжение 11, низкого уровня. На выходе аналоговой памяти 14 напряжение убывает и инвертор 15 разрешает прохождение импульсов, поступающих с делителя 6, через третий логический элемент И 16 на вход сброса регистра 10. Информация на выходе регистра 10 обнуляется и на опорном входе компаратора 1 напряжение U отсутствует. Цикл измерения проходит по описанному принципу.

Формула изобретения

Устройство дпя измерения -амплитуды синусоидального напряжения, содержащее подключенные к входной шине компаратор и квантователь, первый и второй счетчики, генератор импульсов, узел сравнения кодов, входы которого соединены с соответствующими выходами счетчиков, и распределитель импульсов, вход которого соединен с выходом компаратора, а первый выход подключен к управляющему входу первого счетчика, отличающеес я тем, что, с целью повышения надежности в работе в него введены регистр, цифроаналоговый преобразоваель, два триггера, четыре логичесих элемента И, аналоговая память, дифференциальная цепочка, инвертор, коммутатор, делитель частоты, причек

вход делителя частоты соединен с выходом генератора, а выход - со счетным входом первого счетчика, с первым входом третьего логического элемента И и с первым входом второго логического элемента И, первый выход распределителя импульсов соединен с вторым входом второго логического элемента И, а второй выход - с вторым входом первого логического элемента И, первьй вход которого соединен с выходом генератора импульсов, а выход - с счетным входом второго счетчика, выход второго логического элемента И соединен с входом первого

триггера, прямой выход которого соединен с вторым входом четвертого логического элемента И и с третьим входом первого логического элемента И, а инверсный выход - с входом дифференциальной цепочки, выход которой соединен с входами сброса обоих счетчиков и второго триггера, вход которого соединен с выходом переполнения второго счетчика, прямой выход второго триггера соединен с первым управляницим входом коммутатора, а инверсный - с вторым управляющим входом коммутатора, первый выход которого соединен с входом сдвига регистра,

а второй - с входом записи регистра и управляющим входом квантования, выход узла сравнения кодов соединен с первым входом четвертого логического элемента И, выход которого соединен с входом коммутатора и с входом сброса первого триггера, выход компаратора Через аналоговую память и инвертор соединен с вторым входом третьего логического элемента И, выход которого соединен с входом сброса регистра, последовательный информационный вход которого соединен с высоким потенциалом, а параллельный информационный вход - с информационным выходом первого счетчика, выход регистра соединен с входом цифроаналогового преобразователя, выход которого соединен с опорным входом компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения текущей оценки среднего значения | 1984 |

|

SU1363251A1 |

| Преобразователь перемещения в код | 1989 |

|

SU1777240A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| СЕЛЕКТОР СИГНАЛОВ ПО ДЛИТЕЛЬНОСТИ | 1990 |

|

RU2028027C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ СО СЖАТИЕМ | 1984 |

|

SU1177836A1 |

| Устройство для определения функций плотности вероятностей | 1984 |

|

SU1363253A1 |

| Логарифмический аналого-цифровой преобразователь | 1987 |

|

SU1481803A1 |

| Устройство для контроля средств числового программного управления | 1988 |

|

SU1675852A1 |

| Функциональный генератор | 1979 |

|

SU783814A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1988 |

|

SU1547063A1 |

Изобретение относится к цифровой измерительной технике и может быть использовано в вольтметрах и информационно-измерительных системах при измерении амплитуды синусоидального напряжения, у которого имеется постоянная составляющая и низкая надежность. Цель изобретения - расширение функциональных возможностей и повыпение надежности. Устройство содержит компаратор I, квантователь 8, счетчики 3,4, генератор 5 импульсов узел 7 сравнения кодов, распределитель 2 кодов. Введение регистра 10, цифроаналогового преобразователя 11, триггеров 13, 18, логических элементов И 9, 12, 16, 20, аналоговой памяти 14, дифференциальной цепочки 17, инвертора 15, коммутатора 19, делителя 6 частоты позволяет автоматизировать измерение амплитуды синусоидальS ного напряжения при изменении его параметров и исключить случаи пере(Л полнения счетчиков. 2 ил. Ю 1 ю ю о ко

| Устройство для определения моментов экстремумов гармонического сигнала | 1980 |

|

SU941904A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР, № 1045142, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-11-23—Публикация

1985-04-02—Подача