Изобретение относится к телемеханике и может найти применение в системах передачи телеметрической информации с уменьшением избыточности.

Цель изобретения - упрощение устройства, повышение его надежности и быстродействия за счет использования одних и тех же блоков для сжатия передаваемой информации и для аналого-цифрового преобразования существенных выборок, сокращение времени на выявление существенности выборки и суммарного времени, затрачиваемого на циклы аналого-цифрового преобразования сигналов от всех датчиков.

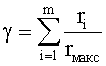

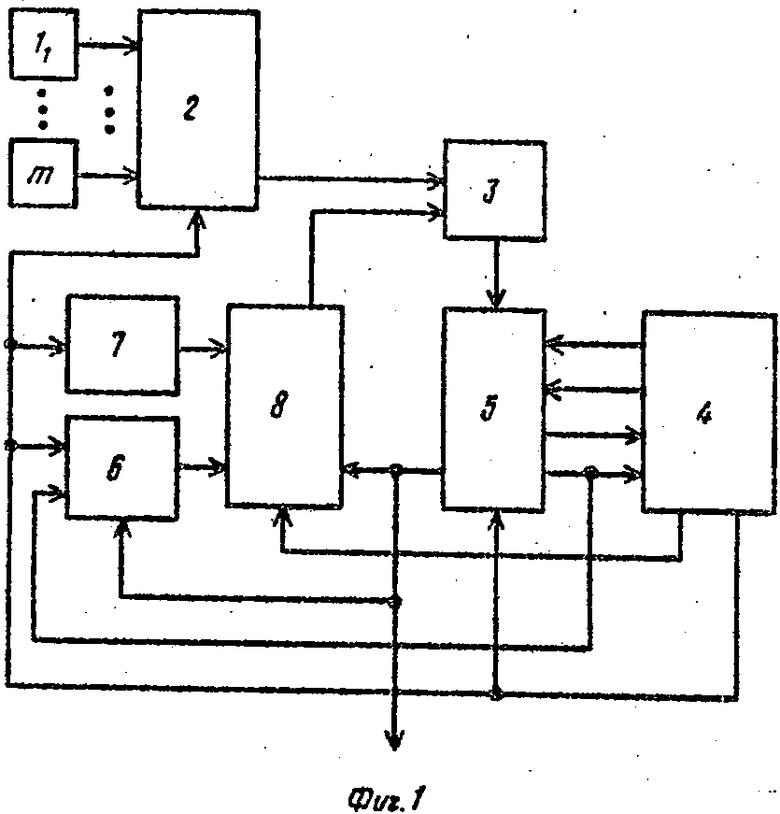

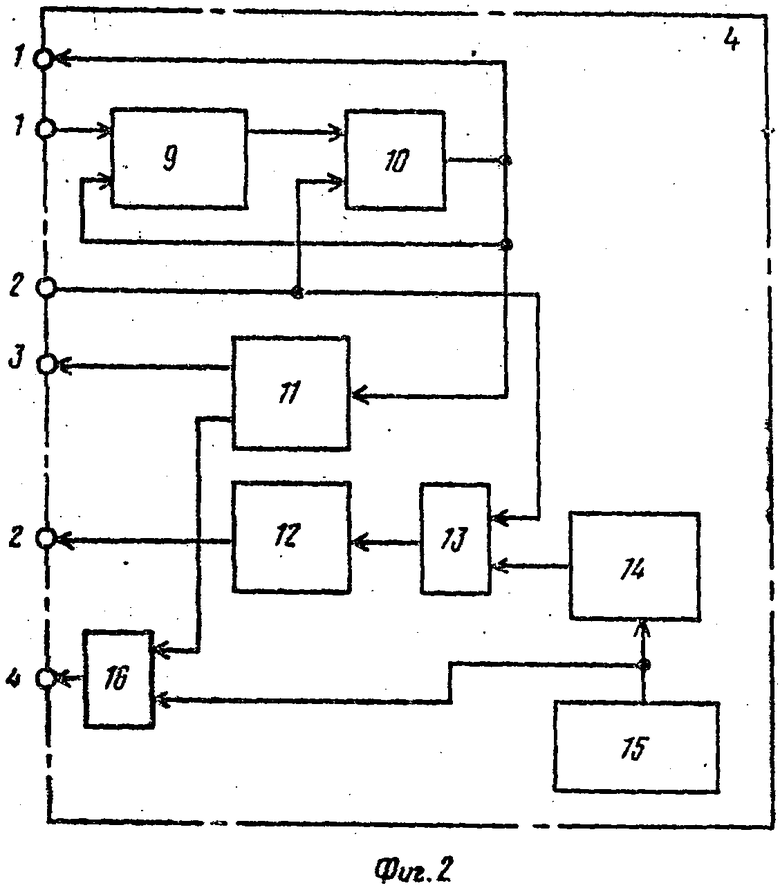

На фиг.1 представлена структурная блок-схема устройства для передачи информации со сжатием; на фиг.2 -структурная схема блока синхронизации и управления; на фиг.3 - структурная схема блока логического управления.

Устройство для передачи измерительной информации (фиг.1) содержит датчики 11-1m, аналоговый коммутатор 2, блок 3 сравнения, блок 4 синхронизации и управления, формирователь 5 длительности выходного кода, блок 6 буферной памяти, блок 7 памяти апертур, коммутируемый цифро-аналоговый преобразователь 8.

Блок 4 синхронизации и управления содержит (фиг.2) формирователь 9 импульсов, триггер 10, формирователи 11 импульсов, двоичный счетчик 12, элемент ИЛИ 13, делитель 14 частоты, генератор 15 тактовых импульсов, элемент И 16.

Формирователь 5 длительности выходного кода содержит (фиг.3) инвертор 17, регистр 18 поразрядного приближения, элемент И 19, второй элемент ИЛИ 20, первые элементы ИЛИ 211 - 21m, элемент 22 памяти, двоичный счетчик 23, регистр 24, цифровой коммутатор 25.

Устройство работает следующим образом.

По сигналу с первого вывода блока 4 синхронизации и управления производится подключение первого информационного входа коммутируемого цифроаналогового преобразователя 8 к блоку 6, отключая одновременно второй его информационный вход от информационного выхода формирователя 5. По сигналам с второго выхода блока 4 синхронизации и управления, подаваемым на управляющий вход аналогового коммутатора 2, производится подключение выхода одного из датчиков 11,...,1m к выходу коммутатора 2 и к первому входу блока 3 сравнения, причем количество датчиков выбирается в зависимости от числа измеряемых параметров или в зависимости от числа точек наблюдения параметров. Одновременно сигналы управления с второго выхода блока 4 синхронизации и управления поступают на вход блока 7 и на управляющий вход блока 6, разрешая выдачу значений апертуры и кода предыдущей существенной выборки, соответствующих датчику, подключенному к первому входу блока 3 сравнения, а также на четвертый вход формирователя 5, синхронизируя его работу с работой всего устройства.

При этом напряжение с выхода блока 7 поступает на отрицательный дифференцирующий вход выходного аналогового сумматора (на фиг.1 не показан) коммутируемого цифроаналогового преобразователя 8, и значение его равно либо нулю, либо величине напряжения, соответствующего значению апертуры. Значения апертуры заносятся в блок 7 соответственно применяемым датчикам 11-1m.

В первом такте сравнения предыдущей существенной выборки, поступившей с одного из датчиков 11-1m с текущим значением сигнала с того же датчика с выхода блока 7 на коммутируемый цифроаналоговый преобразователь 8 подается напряжение, равное нулю, при этом на второй вход блока 3 сравнения поступает напряжение с выхода коммутируемого цифроаналогового преобразователя 8, значение которого равно значению предыдущей существенной выборки. Если значение напряжения на первом входе блока 3 сравнения превышает значение напряжения на втором его входе, то производится второй такт сравнения, в течение которого по сигналу с второго выхода блока 4 синхронизации и управления с выхода блока 7 на переключаемый цифроаналоговый преобразователь 8 поступает напряжение, величина которого равна значению апертуры для соответствующего датчика 11-1m, увеличивая на такую же величину напряжение па выходе коммутируемого цифро-аналогового преобразователя 8.

Если при этом значение напряжения на первом входе блока 3 сравнения меньше значения напряжения на втором его входе, то выборка несущественна, и по сигналу с второго выхода блока 4 синхронизации и управления производится смена подключаемого датчика, а также значений апертуры и предыдущей существенной выборки, и цикл повторяется.

Если значение напряжения на первом входе блока 3 сравнения в первом такте сравнения меньше значения напряжения, поступающего с выхода коммутируемого цифроаналогового преобразователя 8 или не меньше значения напряжения, поступившего с выхода коммутируемого цифроаналогового преобразователя 8 во втором такте сравнения, выборка существенна. При этом выходное напряжение блока 7 вновь становится равным нулю, а по сигналу с первого вывода блока 4 синхронизации и управления производится отключение первого информационного входа коммутируемого цифроаналогового преобразователя 8 и подключение его второго информационного входа к информационному выходу формирователя 5 и к выходу устройства.

Одновременно по сигналам с первого, третьего и четвертого выходов блока 4 синхронизации и управления формирователь 5, блок 3 сравнения и коммутируемый цифроаналоговый преобразователь 8 переводятся в режим аналого-цифрового преобразования, осуществляемого по методу поразрядного уравновешивания.

При этом формирователь 5 изменяет длительность цикла аналого-цифрового преобразования напряжения существенной выборки, согласуя ее со значением апертуры, заданным для соответствующего датчика, от которого поступила последняя существенная выборка, а также количество разрядов, необходимых для образования цифрового кода, соответствующего напряжению существенной выборки.

По окончании цикла аналого-цифрового преобразования на второй вход блока 4 синхронизации и управления, а также на второй управляющий вход блока 6 с второго выхода формирователя поступает управляющий сигнал, по которому производится запись кода существенной выборки в блок 6, после чего устройство возвращается в исходное состояние.

Блок 4 синхронизации и управления работает следующим образом.

Генератор 15 тактовых импульсов вырабатывает тактовые импульсы, поступающие на первый вход элемента 16 И.

В случае несущественности очередной выборки 'с выхода триггера 10 на первый вход первого формирователя 9 импульсов поступает логическая единица, триггер 10 находится в исходном состоянии. При этом на вторые входы триггера 10 и элемента 13 ИЛИ с второго входа блока 4 синхронизации и управления поступает логический ноль, что обеспечивает поступление импульсов счета адреса через двоичный счетчик 12 и второй выход блока 4 синхронизации и управления на управляющие входы коммутатора 2, блока 7, вход формирователя 5 и первый управляющий вход блока 6.

Выборка считается существенной, если логический уровень сигнала, поступающего на первый вход блока 4 синхронизации и управления изменяется на противоположный. При этом сигнал с формирователя 5 через первый вход блока 4 синхронизации и управления поступает на второй вход первого формирователя импульсов 9 и далее - на первый вход триггера 10, переводя его состояние на противоположное. Сигнал с выхода триггера 10 поступает на первый вход первого формирователя 9 импульсов, блокируя дальнейшее поступление сигналов на первый вход триггера 10 с первого блока 4 синхронизации и управления, и далее - на управляющий вход коммутируемого цифроаналогового преобразователя 8, а также на выход второго формирователя 11 импульсов.

Второй формирователь 11 импульсов предназначен для выработки сигналов сброса кода предыдущей существенной выборки на выходе устройства и запуска цикла аналого-цифрового преобразования через промежуток времени, необходимый для завершения перекоммутации цифровых информационных входов коммутируемого цифроаналогового преобразователя 8, поступающих с первого выхода формирователя 11 импульсов. Одновременно на время действия сигнала сброса инвертированным выходным сигналом с второго выхода второго формирователя 11 импульсов перекрывается поступление тактовых импульсов на четвертый выход блока 4 синхронизации и управления.

По завершении цикла аналого-цифрового преобразования с выхода формирователя на вход 2 блока 4 синхронизации и управления поступает сигнал окончания цикла аналого-цифрового преобразования. Этот сигнал поступает далее на второй вход триггера 10, возвращая его состояние в исходное и на второй вход элемента ИЛИ 13, разрешая поступление импульса счета адреса с делителя 14 частоты на двоичный счетчик 12, переключая адресный двоичный код на управляющих входах коммутатора 2, блока 6, формирователя 5 и блока 7, после чего цикл повторяется.

Формирователь 5 работает следующим образом.

На первый вход регистра 24 с формирователя 5 поступает двоичный код, соответствующий адресу подключенного датчика. Выходы двоичного счетчика 23 и выходы элемента 22 памяти подключены в соответствующих разрядах к входам элементов 211-21m ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых подключены к входам элемента ИЛИ 20.

В случае несущественности очередной выборки выход элемента ИЛИ 20 находится в состоянии логического ноля и тактовые импульсы, поступающие с входа формирователя от выхода блока 4 синхронизации и управления на второй выход элемента И 19, не изменяют состояние его выхода, а при переключении входов цифрового коммутатора 25 на его выходе, соединенном с первым выходом формирователя 5, сохраняется постоянный логический уровень сигнала. Информационный выход формирователя 5 соединенный с выходом регистра 18 поразрядного приближения, отключен от второго информационного входа коммутируемого цифроаналогового преобразователя 8.

Если при поступлении очередной выборки сигналы, приходящие с выхода блока 3 сравнения через формирователь 5 на вход регистра 18 поразрядного приближения, а также на первый вход цифрового коммутатора 25 и через инвертор 17 - на второй его вход, изменяет логический уровень сигнала на выходе цифрового коммутатора 25 при переключении его входов синфазно с переключением выходного уровня напряжения блока 7; выборка считается существенной. При этом по сигналу "Сброс" с третьего выхода блока 4 синхронизации и управления, поступающему через формирователь 5 на вторые входы соответственно двоичного счетчика 23 и регистра 18 поразрядного приближения и регистра 24, на выходах во всех разрядах счетчика 23 и регистра 18 вначале устанавливаются логические нули, а в регистр 24 заносится двоичный код, соответствующий адресу подключенного датчика. После этого по сигналу "Пуск", поступающему с того же входа формирователя 5, на выходе регистра 24 устанавливается значение занесенного в него двоичного кода, который, поступая далее на вход элемента 22 памяти, устанавливает на его выходе двоичный код, соответствующий числу тактов аналого-цифрового преобразования, достаточного для данного, подключенного через коммутатор 2, датчика. Одновременно на первом входе элемента И 19 устанавливается логическая единица, разрешающая поступление тактовых импульсов с второго ее входа на ее выход, а регистр 18 поразрядного приближения и двоичный счетчик 23 начинают свою работу. При этом с помощью регистра 18 поразрядного приближения производится цикл аналого-цифрового преобразования существенной выборки, а с помощью счетчика 23 производится подсчет тактов АЦП, равного числу тактовых импульсов, поступающих с выхода элемента И 19 на первый вход регистра 18 поразрядного приближения и первый вход счетчика 23, Сравнение уровней выходных двоичных кодов в соответствующих разрядах элемента 22 памяти и двоичного счетчика 23 производится с помощью элементов 211-21m ИСКЛЮЧАЮЩЕЕ ИЛИ, где m равно количеству разрядов выходного кода элемента 22 памяти и двоичного счетчика 23.

При совпадении двоичных кодов, поступающих с выходов элемента 22 памяти и двоичного счетчика 23, на выходе элемента ИЛИ 20 появляется нолевой логический уровень, исключающий возможность дальнейшего поступления тактовых импульсов на первый вход регистра 18 поразрядного приближения, а также сигнализирующий об окончании цикла аналого-цифрового преобразования, который поступает через второй выход формирователя 5 на второй вход блока 4 синхронизации и управления, и цикл посторяется.

Все блоки устройства, кроме блока 4 синхронизации и управления и формирователя 5, выполняются так же, как в известном устройстве.

Таким образом, устройство производит как временное сжатие передаваемой информации, так и аналого-цифровое преобразование существенных ее выборок, используя общие блоки, что значительно упрощает устройство и повышает его надежность.

Устройство также обеспечивает повышение быстродействия за счет сокращения суммарного времени, затрачиваемого на циклы аналогово-цифрового преобразования напряжений существенных выборок от всех датчиков, а также за счет исключения операционного усилителя, предназначенного для вычисления разности между значением предыдущей, существенной выборки и текущим значением сигнала с соответствующего датчика и имеющего время установленного выходного сигнала, превышающее время срабатывания компаратора в блоке сравнения, что существенно отличает предлагаемое устройство от известных.

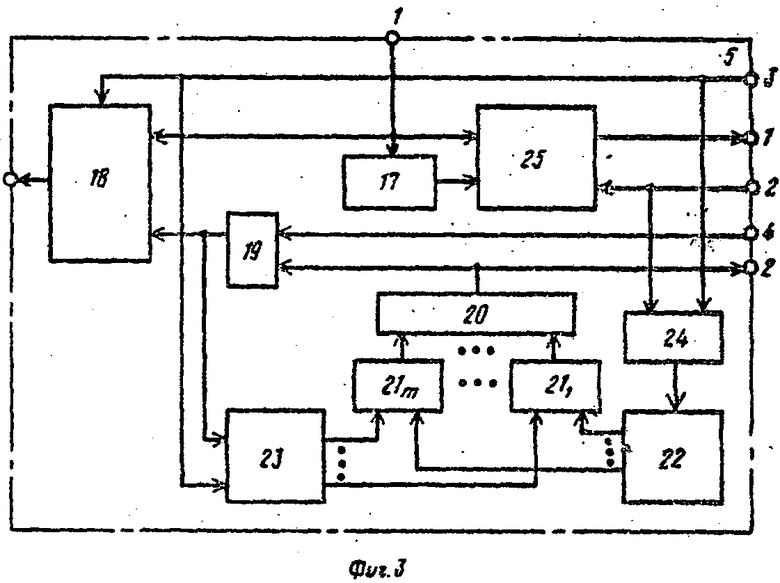

Сокращение указанных затрат времени на циклы аналого-цифрового преобразования напряжений существенных выборок от всех датчиков может быть выражено с помощью коэффициента γ рассчитываемого по формуле

где m=11,…,1m - номера датчиков;

ri - разрядность аналого-цифрового преобразования, соответствующая i-му датчику;

rмакс - максимальное число разрядов аналого-цифрового преобразования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного индикатора | 1984 |

|

SU1292029A1 |

| Гибридное вычислительное устройство | 1983 |

|

SU1113819A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Функциональный преобразователь угла поворота вала в код | 1982 |

|

SU1043704A1 |

| Многоканальная цифровая телеметрическая система | 1985 |

|

SU1280420A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Устройство для преобразования перемещения в код | 1981 |

|

SU978174A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ УРОВНЯ СЫПУЧИХ МАТЕРИАЛОВ | 1998 |

|

RU2138027C1 |

| Устройство для контроля качества изделий | 1983 |

|

SU1171707A1 |

1. Устройство для передачи информации со сжатием, содержащее датчики, выходы которых соединены с информационными входами коммутатора, блок буферной памяти, выход которого соединен с первым информационным входом цифроаналогового преобразователя, блок синхронизации и управления, первый выход которого соединен с управляющим входом цифроаналогового преобразователя, второй выход -с первым управляющим входом блока буферной памяти и управляющим входом блока памяти апертур, и блок сравнения, отличающееся тем, что, с целью упрощения и повышения надежности и быстродействия устройства, в него введен формирователь длительности выходного кода, первый выход которого соединен с вторым информационным входом цифроаналогового преобразователя и информационным входом блока буферной памяти и является выходом устройства, второй выход формирователя длительности выходного кода соединен с объединенными вторым управляющим входом блока буферной памяти и первым входом блока синхронизации и управления, третий выход и первый и второй входы формирователя длительности выходного кода соединены соответственно с вторым входом, третьим и четвертым выходами блока синхронизации и управления, выход коммутатора соединен с первым входом блока сравнения, выход которого соединен с третьим входом формирователя длительности выходного кода, четвертый вход которого и управляющий вход коммутатора подключены к второму выходу блока синхронизации и управления, выход блока памяти апертур соединен с третьим информационным входом цифроаналогового преобразователя, выход которого соединен с вторым входом блока сравнения.

2. Устройство по п. 1, отличающееся тем, что формирователь длительности выходного кода содержит коммутатор, регистры, счетчик, элемент памяти, инвертор, элементы ИЛИ и элемент И, выход регистра соединен с входом элемента памяти, выходы которого соединены с первыми входами соответствующих первых элементов ИЛИ, выходы которых соединены с соответствующими входами второго элемента ИЛИ, выход элемента ИЛИ соединен с первым входом элемента И, выход которого соединен с первыми входами второго регистра и счетчика, выходы счетчика соединены с вторыми входами соответствующих первых элементов ИЛИ, выход инвертора соединен с первым входом коммутатора, объединенные первый вход первого регистра и вторые входы второго регистра и счетчика и объединенные вторые входы первого регистра и коммутатора являются соответственно первым и вторым входами формирователя длительности выходного кода, объединенные третьи входы коммутатора и второго регистра и вход инвертора и второй вход элемента И являются соответственно третьим и четвертым входами формирователя длительности выходного кода, выход второго регистра, выход элемента ИЛИ и выход коммутатора являются соответственно первым, вторым и третьим выходами формирователя длительности выходного кода.

3. Устройство по п. 1,отличающееся тем, что блок синхронизации и управления содержит формирователи импульсов, триггер, счетчик, делитель частоты, генератор тактовых импульсов, элемент ИЛИ и элемент И, выход генератора тактовых импульсов соединен с первым входом элемента И и через делитель частоты - с первым входом элемента ИЛИ, выход которого соединен с входом счетчика, выход первого формирователя импульсов соединен с первым входом триггера, выход которого соединен с первым входом первого формирователя импульсов и входом второго формирователя импульсов, выход которого соединен с вторым входом элемента И, второй вход первого формирователя импульсов, объединенные вторые входы триггера и элемента ИЛИ являются соответственно первым и вторым входами блока синхронизации и управления, выход триггера, выход счетчика, выход второго формирователя и выход элемента И являются соответственно первым, вторым, третьим и четвертым выходами блока синхронизации управления.

Авторы

Даты

1985-09-07—Публикация

1984-03-11—Подача