Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля средств управле- ния многоканальными устройствами числового программного управления, формирующих задание на перемещение подвижных органов станка с ЧПУ.

Цель изобретения -. расширение области применения устройства за счет ввода в него средств имитации движения инструмента,

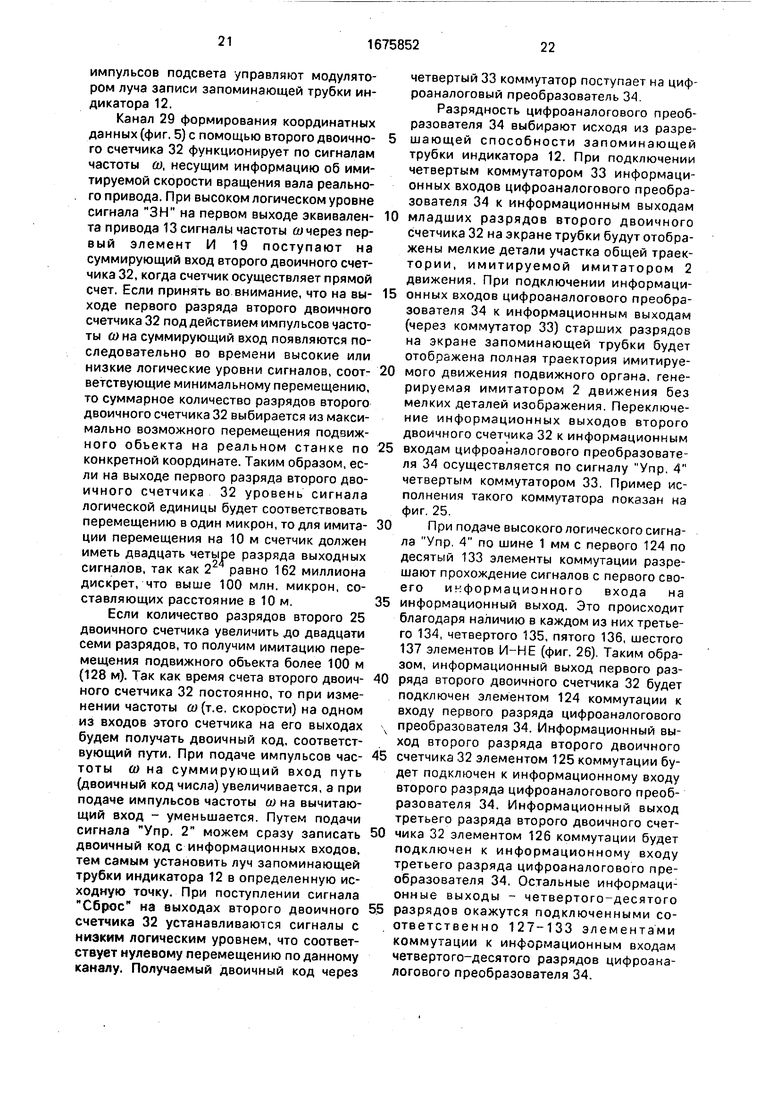

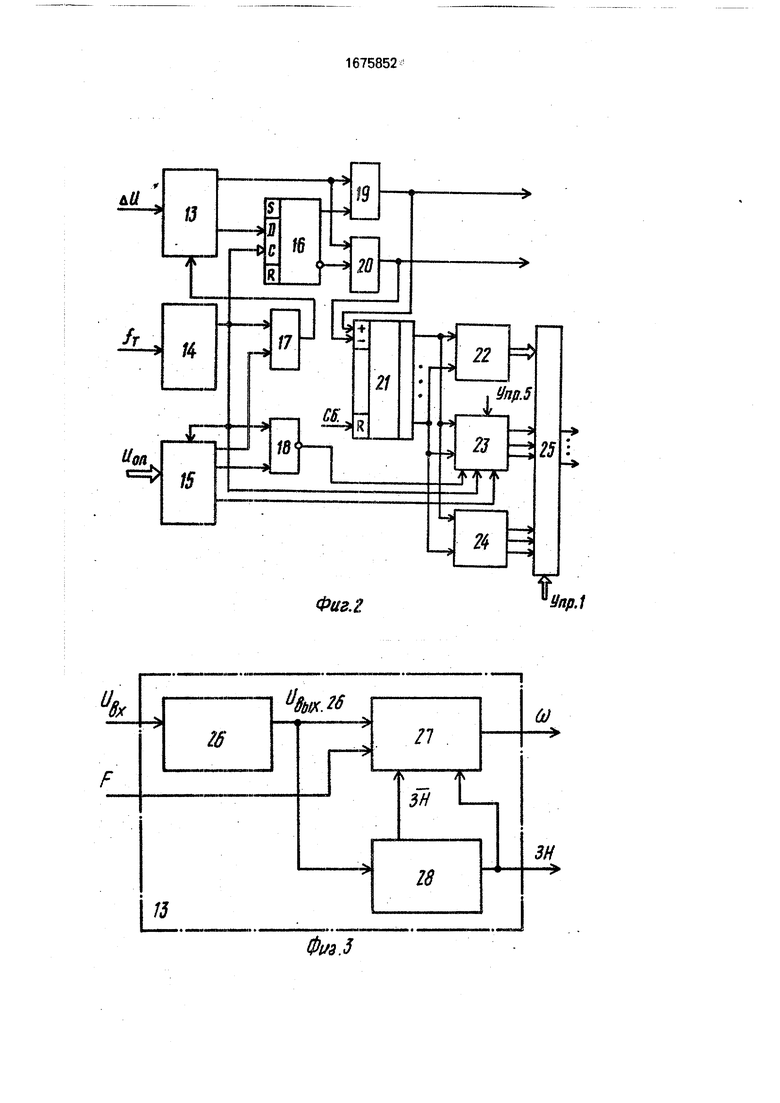

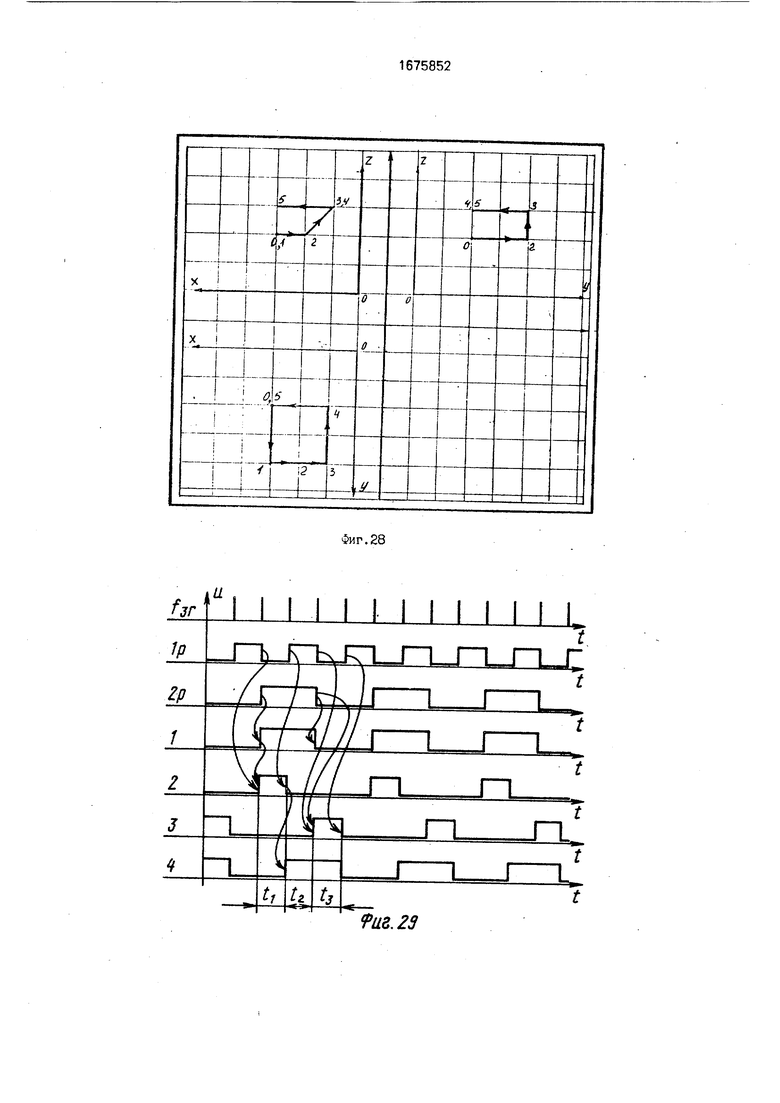

На фиг, 1 представлена блок-схема устройства; на фиг. 2 -схема имитатора движения инструмента; на фиг. 3 - схема эквивалента привода инструмента; на фиг. 4 - блок - схема блока формирования 3 координатных данных перемещений; на фиг. 5 - блок-схема канала 29 формирования данных; на фиг. 6 - блок-схема блока управления смещением изображений; на фиг. 7 - функциональная схема распределителя импульсов; на фиг. 8 - схема первого коммутатора; на фиг. 9 - схема пятого коммутатора; на фиг. 10 - переходной процесс для регулируемого по скорости электропривода при воздействии на его вход ступенчатого напряжения; на фиг. 11 - принципиальная схема блока аналоговой модели регулируемого по скорости электропривода; на фиг. 12 - временные диаграммы рабрты имитатора движения инструмента; на фиг. 13-схема реализации преобразователя напряжения в частоту; на фиг. 14 - схема формирователя знака; на фиг. 15 - схема интегратора; на фиг. 16 - временные диаграммы работы эквивалента привода инструмента; на фиг. 17 - схема блока синхронизации импульсов; на фиг. 18 - временные диаграммы работы блока синхронизации импульсов; на фиг. 19 - схема узла имитации фазового датчика;, на фиг. 20 - схема формирователя маркера фазового датчика; на фиг. 21 - имитатор импульсного датчика; на фиг. 22 - временные диаграммы работы имитатора импульсного датчика; на фиг. 23 - схема Формирователя маркера импульсного датчика; на фиг. 24 - схема второго коммутатора; на фиг, 25 - схема четвертого коммутатора; на фиг. 26 - пример исполнения элементов коммутации четвертого коммутатора; на фиг. 27 - пример исполнения третьего коммутатора; на фиг. 28 - изображение трех проекций движения имитируемого объекта в пространстве на экране запоминающей ЭЛТ; на фиг. 29 - временные диаграммы работы распределителя импульсов; на фиг, 30-32 возможные схемы формирования управляющих и сбросовых сигналов для имитаторов.

На фиг. 1 обозначены задающий генератор 1, имитаторы 2 движения инструмента, блок 3 формирования координатных данных перемещения, формирователь 4 импульсов подсвета, первый коммутатор 5, объект 6 контроля (проверяемое устройство числового программного управления), блок 7 управления смещением изображений, первый 8 и второй 9 сумматоры, пер0 вый 10 и второй 11 усилители отклонения, индикатор 12 на запоминающей электронно-лучевой трубке.

На фиг. 2 обозначены эквивалент привода 13 инструмента, делитель 14 частоты,

5 блок 15 синхронизации импульсов, первый D-триггер 16, третий элемент И 17, первый элемент И-НЕ 18,-первый 19 и второй 20 элементы И, первый счетчик (двоичный) 21, узел 22 имитации (имитатор) импуль0 сного датчика, узел 23 имитации (имитатор) фазового датчика, узел 24 имитации (имитатор) амплитудного датчика, второй коммутатор 25.

На фиг. 3 приведены блок 26 аналоговой

5 модели регулируемого по скорости электропривода, преобразователь 27 напряжения в частоту, формирователь 28 знака сигнала.

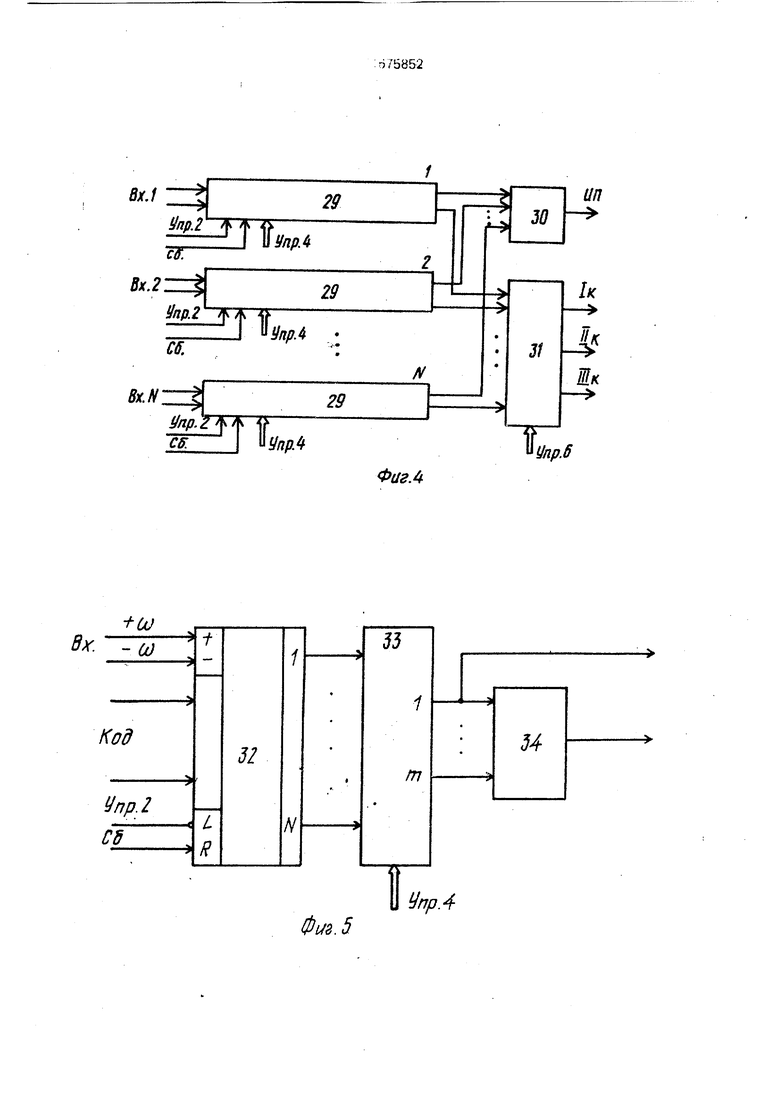

На фиг. 4 изображены каналы 29 формирования координатных данных, первый эле0 мент ИЛИ 30, третий коммутатор 31.

На фиг. 5 обозначены второй двоичный счетчик 32, четвертый коммутатор 33, циф- роаналоговый преобразователь 34.

На фиг. 6 обозначены третий двоичный

5 счетчик 35, блок 36 выбора отображений координатной плоскости (распределитель импульсов), четвертый 37, пятый 38, шестой 39, седьмой 40 элементы И, пятый коммутатор 41,

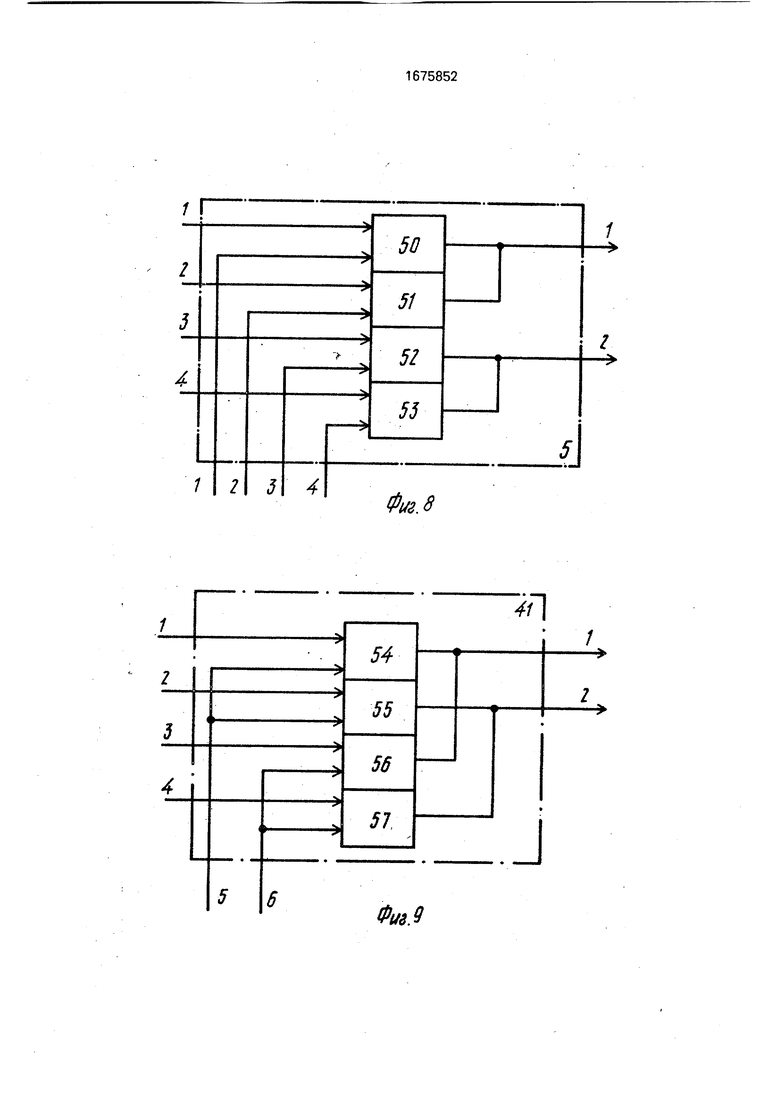

0 На фиг. 7 обозначены первый 42 и второй 43 элементы НЕ, второй 44 и третий 45 элементы ИЛИ, восьмой 46, девятый 47, десятый 48, одиннадцатый 49 элементы И. На фиг. 8 обозначены первый 50, второй

5 51, третий 52, четвертый 53 аналоговые элементы коммутации.

На фиг. 9 обозначены пятый 54, шестой 55, седьмой 56, восьмой 57 аналоговые элементы коммутации.

На фиг. 11 обозначены первое передаточное звено 58, первый инвертирующий усилитель 59, второе передаточное звено 60, суммирующий усилитель 61.

На фиг. 13 обозначены второй инверти5 рующий усилитель 62, девятый аналоговый элемент 63 коммутации, десятый аналоговый элемент 64 коммутации, интегратор 65, первый 66 и второй 67 компараторы, первый 68 и второй 69 элементы 2И-ИЛИ, RS-триг- гер 70, второй D-триггер 71, третий D-тригrep 72, элемент 2НЕ-И 73, третий элемент НЕ 74.

На фиг. 14 обозначены третий компаратор 75, формирователь 76 импульсов, четвертый элемент НЕ 77.

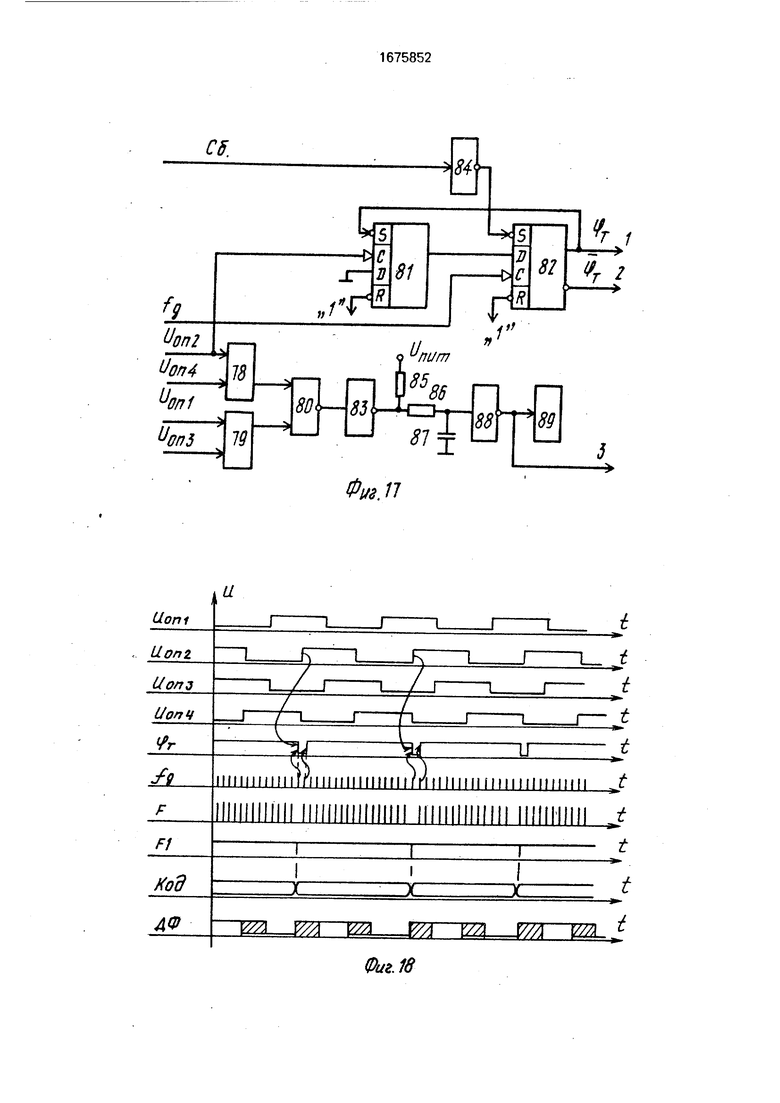

На фиг. 17 изображены первый 78 и второй 79 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, второй элемент И-НЕ 80, четвертый 81 и пятый 82 D-триггеры, пятый 83 и шестой 84 элементы НЕ, первый 85 и вто- рой 86 резисторы, первый конденсатор 87, седьмой элемент НЕ 88, элемент 89 индикации.

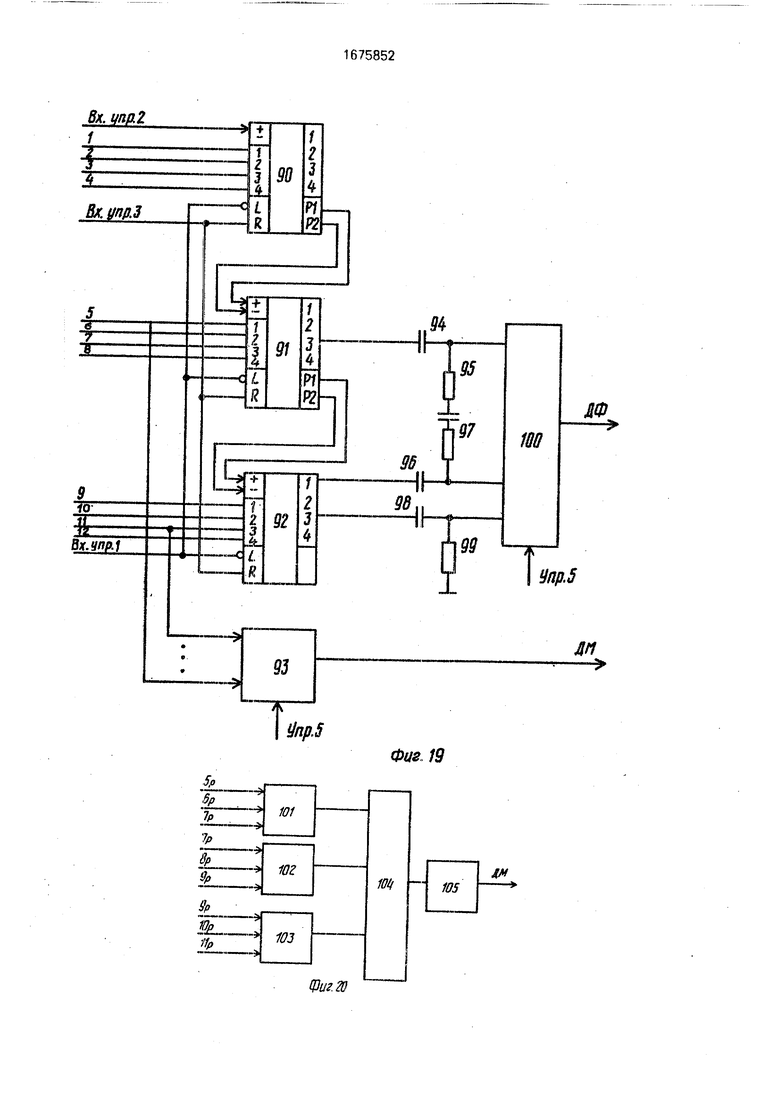

На фиг. 19 изображены четвертый 90, пятый 91 и шестой 92 двоичные счетчики, формирователь 93 маркера фазового датчика, второй конденсатор 94, третий резистор 95, третий конденсатор 96, четвертый резистор 97, четвертый конденсатор 98, пятый резистор 99, шестой коммутатор 100.

На фиг. 20 изображены четырнадцатый 101, пятнадцатый 102, шестнадцатый ЮЗ элементы И, седьмой коммутатор 104, четвертый компаратор 105.

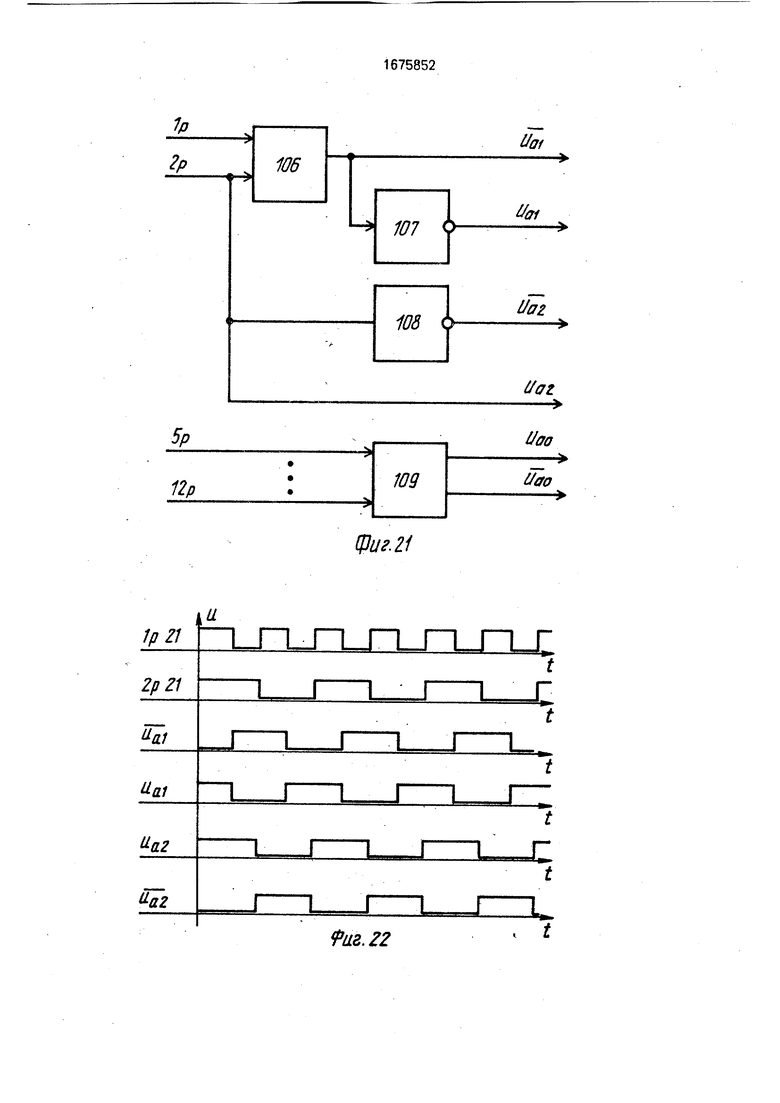

На фиг, 21 изображены третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 106, восьмой 107 и девятый 108 элементы НЕ, формирователь 109 маркера импульсного датчика.

На фиг. 23 изображены семнадцатый элемент И 110, десятый элемент НЕ 111.

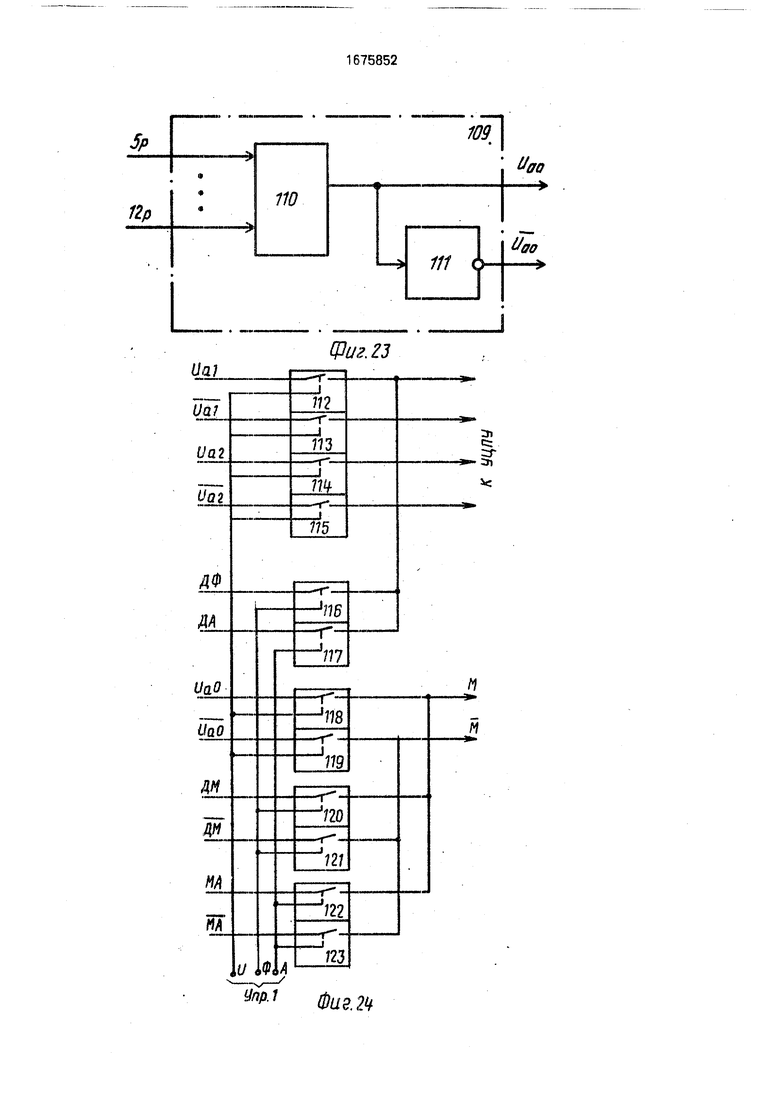

На фиг. 24 изображены с одиннадцатого 112 по двадцать второй 123 аналоговые элементы коммутации.

На фиг. 25 изображены с первого 124 по десятый 133 элементы коммутации.

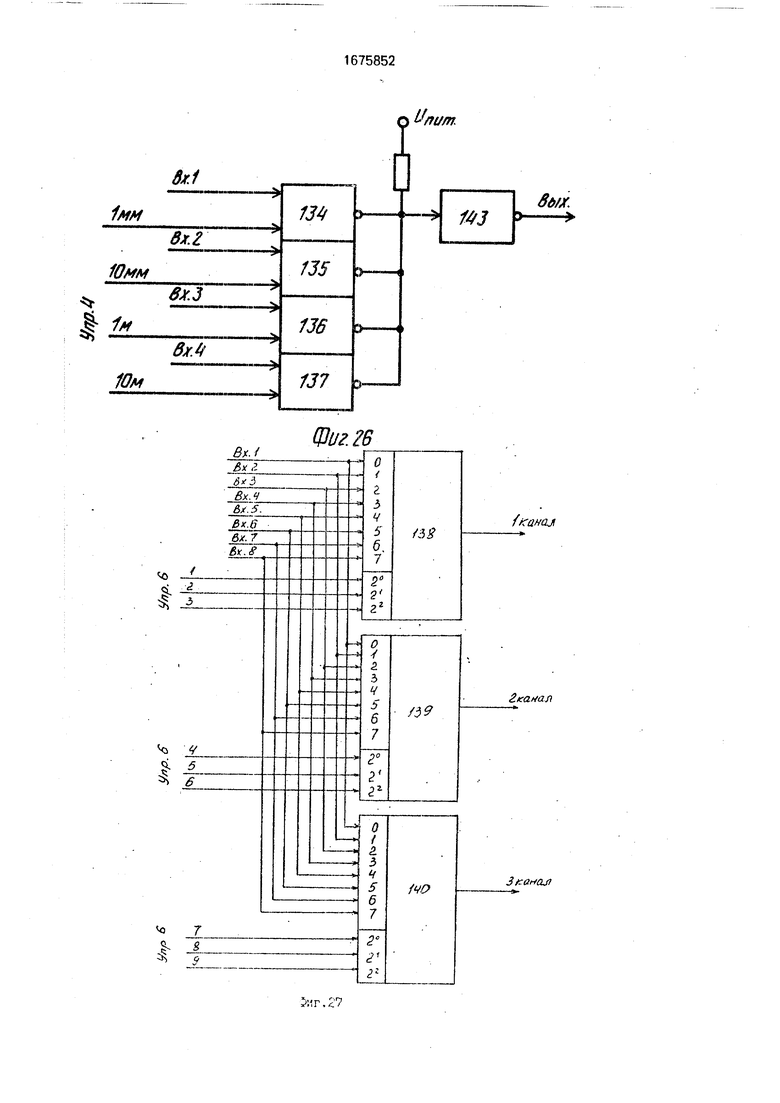

На фиг. 26 изображены третий 134, четвертый 135, пятый 136 и шестой 137 элементы И-НЕ.

На фиг. 27 изображены одиннадцатый 138, двенадцатый 139, тринадцатый 140 элементы коммутации.

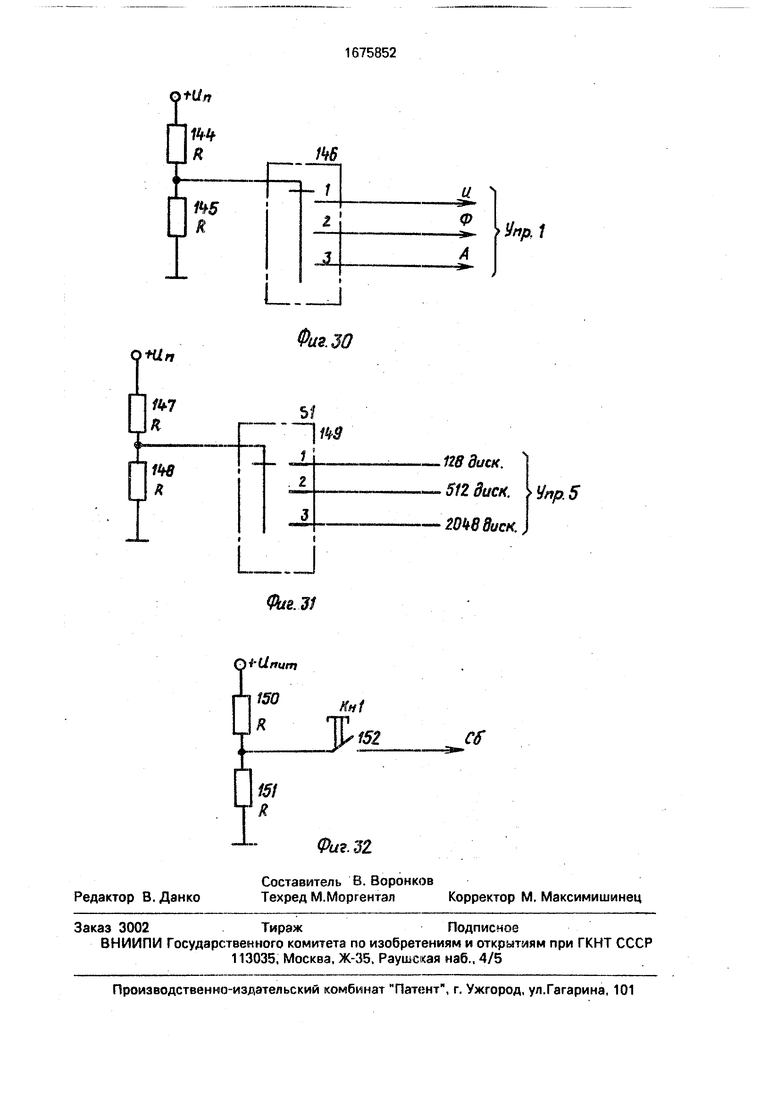

В состав блоков устройства также входят двенадцатый элемент И 141,тринадцатый элемент И 142, одиннадцатый элемент НЕ 143, шестой резистор 144, седьмой ре- зистор 145, первый переключатель 146, восьмой резистор 147, девятый резистор 148, второй переключатель 149, десятый резистор 150, одиннадцатый резистор 151, третий переключатель 152, первый диод 153, второй диод 154, двенадцатый резистор 155, пятый конденсатор 156, третий инвертирующий усилитель 157.

Устройство работает следующим образом.

Импульсы частоты тзг с задающего генератора поступают на вход делителя 14 частоты имитатора 2 движения. Управляющие напряжения с каждого канала управления объекта 6 контроля поступают на

одноименный с номером канала (1-N) имитатор 2 движения, а точнее на вход эквивалента 13 привода.

Если бы это напряжение поступило на вход привода станка, то вал двигателя привода начал бы вращаться. Скорость вращения вала двигателя тем больше, чем больше управляющее напряжение на входе привода, а направление вращения вала двигателя привода зависит от полярности приложенного на входе напряжения.

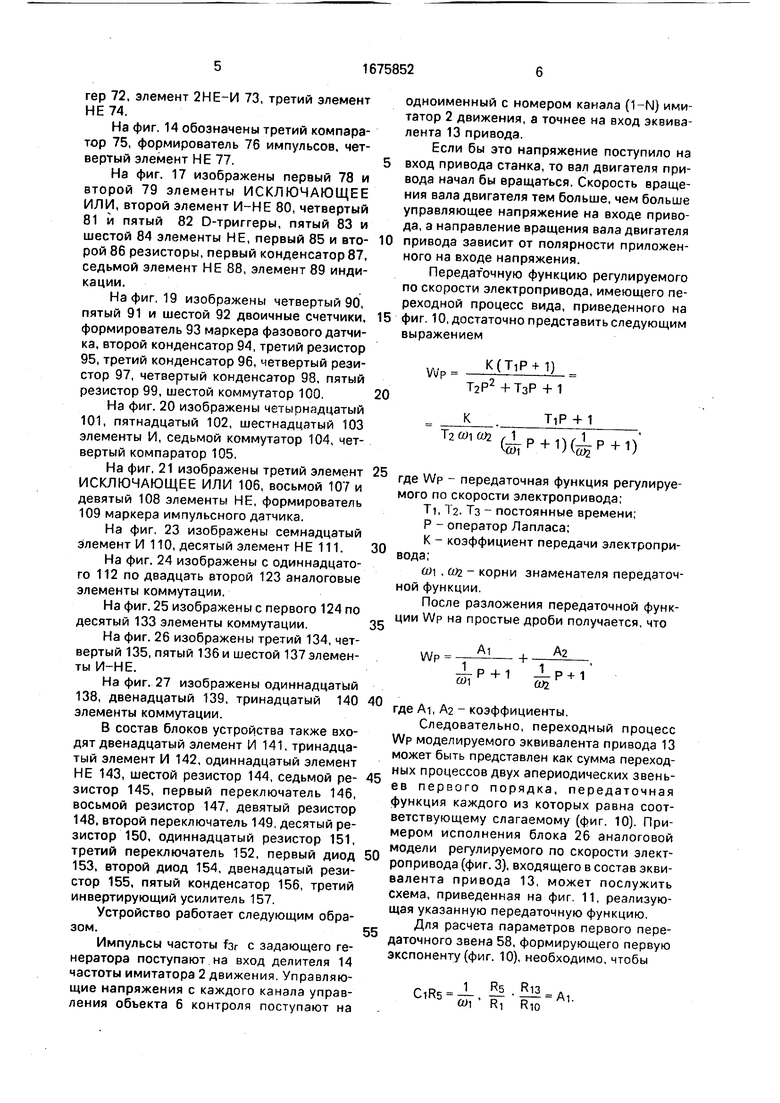

Передаточную функцию регулируемого по скорости электропривода, имеющего переходной процесс вида, приведенного на фиг. 10, достаточно представить следующим выражением

Wp

K(TiP+1)

Т2 + Т3Р + 1

TiP + 1

Tlfflle Јp+1)Јp+1)

где Wp - передаточная функция регулируемого по скорости электропривода;

Ti, Та, Тз - постоянные времени;

Р - оператор Лапласа;

К - коэффициент передачи электропривода;

col , oi - корни знаменателя передаточной функции.

После разложения передаточной функции Wp на простые дроби получается, что

Wp

Ai

-

P + 1

где Ai, Aa - коэффициенты.

Следовательно, переходный процесс Wp моделируемого эквивалента привода 13 может быть представлен как сумма переходных процессов двух апериодических звеньев первого порядка, передаточная функция каждого из которых равна соответствующему слагаемому (фиг. 10). Примером исполнения блока 26 аналоговой модели регулируемого по скорости электропривода (фиг. 3), входящего в состав эквивалента привода 13, может послужить схема, приведенная на фиг. 11, реализующая указанную передаточную функцию.

Для расчета параметров первого передаточного звена 58, формирующего первую экспоненту (фиг. 10), необходимо, чтобы

C1R5 -,- A1.

HI Кю

Для расчета параметров второго передаточного звена 60, формирующего вторую экспоненту (фиг. 10), необходимо, чтобы

CoRq 1 L2K9 ад1 R2 R7 Rn 2

Знак минус возле А2 получен благодаря наличию в блоке 26 инвертирующего усилителя 59.

Благодаря сумммрущему усилителю 61 на его выходе получается суммарное выходные напряжение, формируемое первым 58 и вторым 60 передаточными звеньями.

Задавая сначала на вход блока 26 аналоговой модели регулируемого по скорости привода ступенчатое напряжение, а потом это же напряжение на вход реального привода, очень легко получить близкие по параметрам передаточные функции. При этом двигатель реального привода должен быть на холостом ходу, при пусках и торможениях токоограничение не работает, в прямом канале усиления реального привода ни один из элементов не насыщается.

Так, например, для привода FANUC при ступенчатом изменении входного сигнала определено

Wp 150

(0.022Р +1 )

0,00012 Р2 + 0,0235 Р + 1 15050

0,006 Р + 1 0,017 Р + 1

Откуда

hi(t)150(1-e о-006); t

h2(t) -50(1-e °-017).

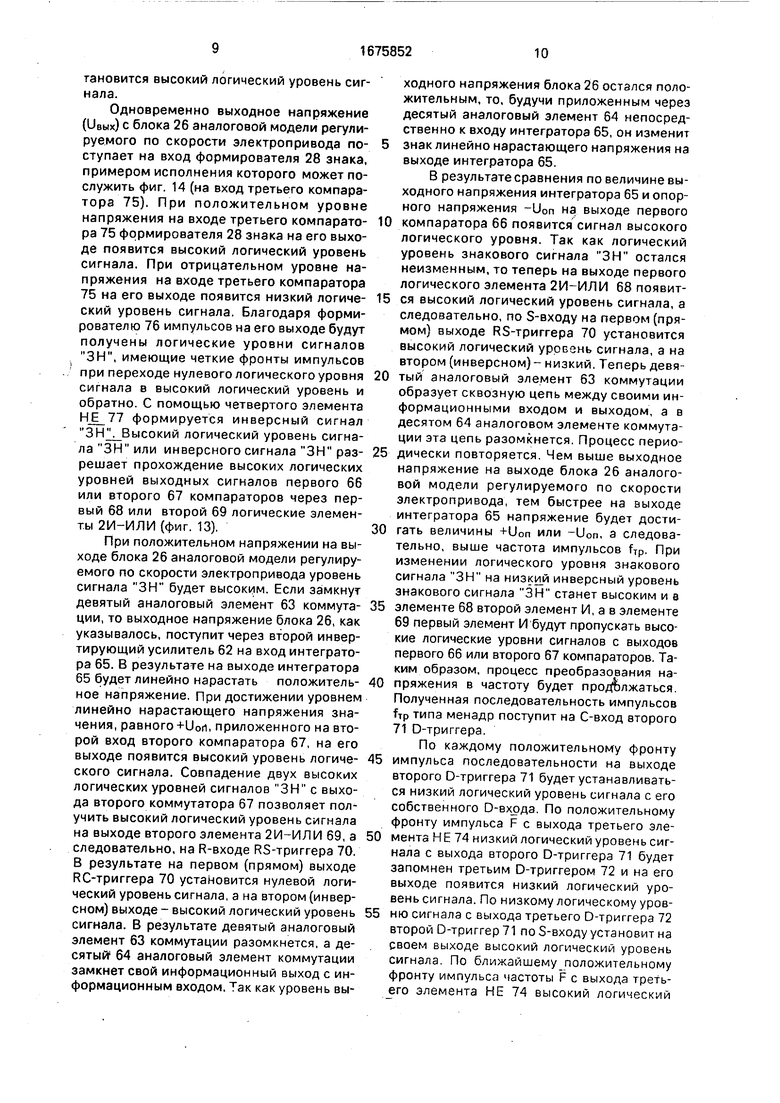

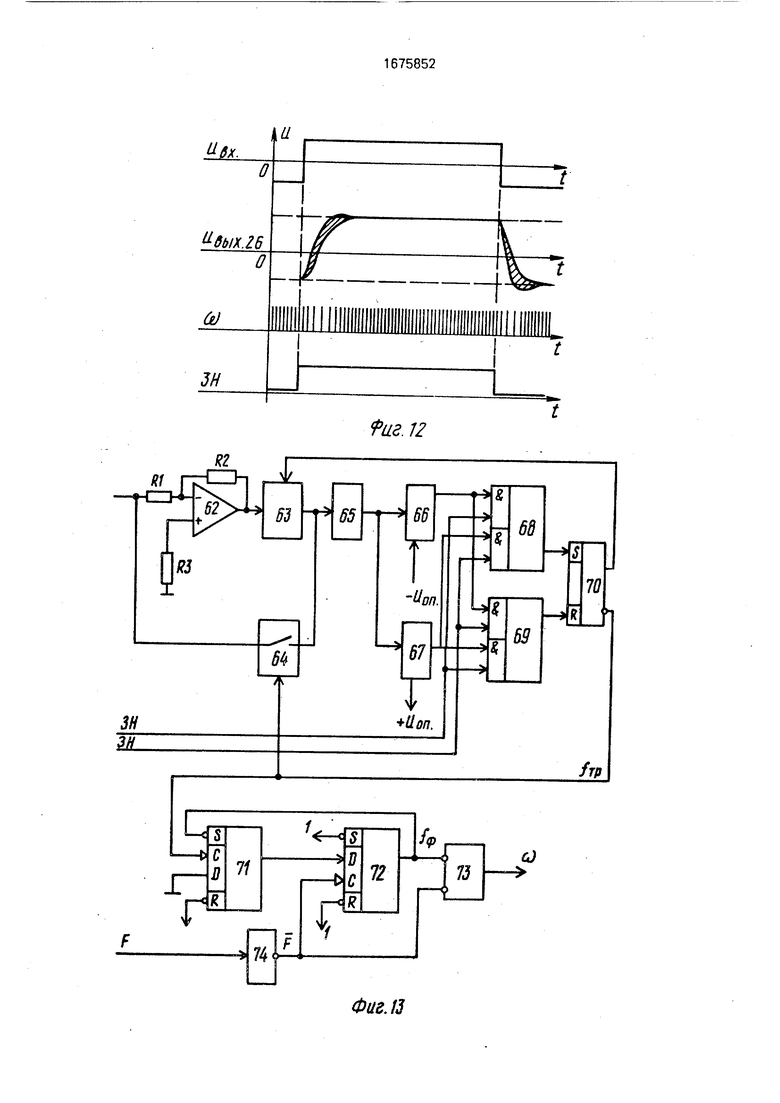

На фиг. 12 приведены временные диаграммы работы эквивалента привода 13. При подаче на вход блока 26 аналоговой модели регулируемого по скорости электропривода ступенчатого напряжения UBX на выходе суммирующего усилителя 61 получаем напряжение Увых, сформированное первым 58 и вторым 60 передаточными звеньями с учетом их передаточных характеристик, близких к передаточным характеристикам реального электропривода. Далее напряжение и0ых поступает на преобразователь 27 напряжения в частоту и одновременно на формирователь 28 знака.

Преобразователь 27 (фиг. 3) при подаче на его вход напряжения Овых позволяет на своем выходе получить последовательность импульсов (w), частота которых пропорциональна оборотам вала двигателя реального электропривода. Формирователь 28 знака одновременно выдает на своем выходе высокий или низкий логический уровень сигнала, указывающий на направление имитируемого движения, подобно направлению вращения вала двигателя реального электропривода.

Основные требования к преобразователю 27 напряжения в частоту - возможность

преобразования входных напряжений положительной (от 0 до +10 В) и отрицательной (от 0 до -10 В) полярности, широкий диапазон выдываемых частот (от 0 до 500 кГц), высокая линейность преобразования для

напряжений, близких к нулю (порядка единиц милливольт), так и напряжений, близких к максимальному значению преобразуемого в частоту напряжения (близкого к 10 В). Примером реализации преобразователя 27 напряжения в частоту может послужить фиг. 13. Она представляет второй инвертирующий усилитель 62, которым значение входного напряжения инвертируется и подается на информационный вход девятого аналогового элемента 63 коммутации. Одновременно прямое значение входного напряжения прикладывается к информационному входу десятого аналогового элемента 64 коммутации. Выходы девятого 63 и

десятого 64 аналоговых элементов коммутации объединены и подключены к входу интегратора 65. Допустим, что в данный момент замкнута цепь с входа на выход в девятом аналоговом элементе 63 коммутации благодаря высокому логическому уровню сигнала на прямом выходе RS- триггера 70. Поэтому инверсное значение ивых. 26 с выхода второго инвертирующе- гоо усилителя 62 поступает на вход интегратора 65. Напряжение на выходе интегратора (фиг. J5) начинает изменяться согласно выражению

ив

ых

-ife u

вх

dt.

Величины R и С выбираются таким образом, чтобы во всем диапазоне изменения напряжения UBX напряжение на выходе интегратора 65 изменялось линейно. Так как с выхода второго инвертирующего усилителя 62 в данный рассматриваемый момент поступает напряжение отрицательной полярности, то на1 выходе интегратора 65 будет

линейно нарастать выходное напряжение (фиг. 16) положительной полярности.

При достижении напряжением на выходе интегратора 65 величины, равной напряжению +Uon, приложенному к второму входу второго 67 компаратора, на его выходе установится высокий логический уровень сигнала.

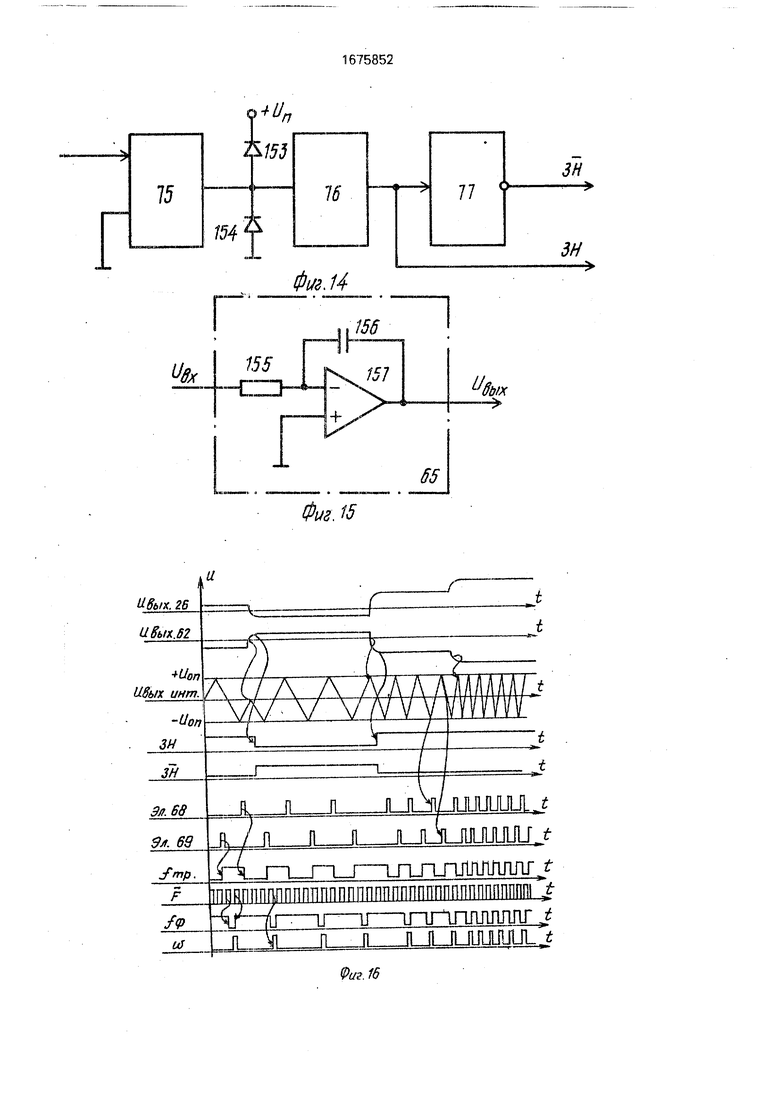

Одновременно выходное напряжение (ивых) с блока 26 аналоговой модели регулируемого по скорости электропривода по- ступает на вход формирователя 28 знака, примером исполнения которого может послужить фиг. 14 (на вход третьего компаратора 75). При положительном уровне напряжения на входе третьего компарато- ра 75 формирователя 28 знака на его выходе появится высокий логический уровень сигнала. При отрицательном уровне напряжения на входе третьего компаратора 75 на его выходе появится низкий логиче- ский уровень сигнала. Благодаря формирователю 76 импульсов на его выходе будут получены логические уровни сигналов ЗН, имеющие четкие фронты импульсов при переходе нулевого логического уровня сигнала в высокий логический уровень и обратно. С помощью четвертого элемента формируется инверсный сигнал ЗН Высокий логический уровень сигнала ЗН или инверсного сигнала ЗН раз- решает прохождение высоких логических уровней выходных сигналов первого 66 или второго 67 компараторов через первый 68 или второй 69 логические элементы 2И-ИЛИ (фиг. 13).

При положительном напряжении на выходе блока 26 аналоговой модели регулируемого по скорости электропривода уровень сигнала ЗН будет высоким. Если замкнут девятый аналоговый элемент 63 коммута- ции, то выходное напряжение блока 26, как указывалось, поступит через второй инвертирующий усилитель 62 на вход интегратора 65. В результате на выходе интегратора 65 будет линейно нарастать положитель- ное напряжение, При достижении уровнем линейно нарастающего напряжения значения, равного+Uort, приложенного на второй вход второго компаратора 67, на его выходе появится высокий уровень логиче- ского сигнала. Совпадение двух высоких логических уровней сигналов ЗН с выхода второго коммутатора 67 позволяет получить высокий логический уровень сигнала на выходе второго элемента 2И-ИЛИ 69, а следовательно, на R-входе RS-триггера 70. В результате на первом (прямом) выходе RC-триггера 70 установится нулевой логический уровень сигнала, а на втором (инверсном) выходе - высокий логический уровен ь сигнала. В результате девятый аналоговый элемент 63 коммутации разомкнется, а десятый1 64 аналоговый элемент коммутации замкнет свой информационный выход с информационным входом. Так как уровень выходного напряжения блока 26 остался положительным, то, будучи приложенным через десятый аналоговый элемент 64 непосредственно к входу интегратора 65, он изменит знак линейно нарастающего напряжения на выходе интегратора 65.

В результате сравнения по величине выходного напряжения интегратора 65 и опорного напряжения -Uon на выходе первого компаратора 66 появится сигнал высокого логического уровня. Так как логический уровень знакового сигнала ЗН остался неизменным, то теперь на выходе первого логического элемента 2И-ИЛИ 68 появится высокий логический уровень сигнала, а следовательно, по S-входу на первом (прямом) выходе RS-триггера 70 установится высокий логический уровень сигнала, а на втором (инверсном)- низкий.Теперь девятый аналоговый элемент 63 коммутации образует сквозную цепь между своими информационными входом и выходом, а в десятом 64 аналоговом элементе коммутации эта цепь разомкнется. Процесс периодически повторяется. Чем выше выходное напряжение на выходе блока 26 аналоговой модели регулируемого по скорости электропривода, тем быстрее на выходе интегратора 65 напряжение будет достигать величины +Uon или -Uon, а следовательно, выше частота импульсов fTp. При изменении логического уровня знакового сигнала ЗН на низкий инверсный уровень знакового сигнала ЗН станет высоким и в элементе 68 второй элемент И, а в элементе 69 первый элемент И будут пропускать высокие логические уровни сигналов с выходов первого 66 или второго 67 компараторов. Таким образом, процесс преобразования напряжения в частоту будет продолжаться Полученная последовательность импульсов ftp типа менадр поступит на С-вход второго 71 D-триггера.

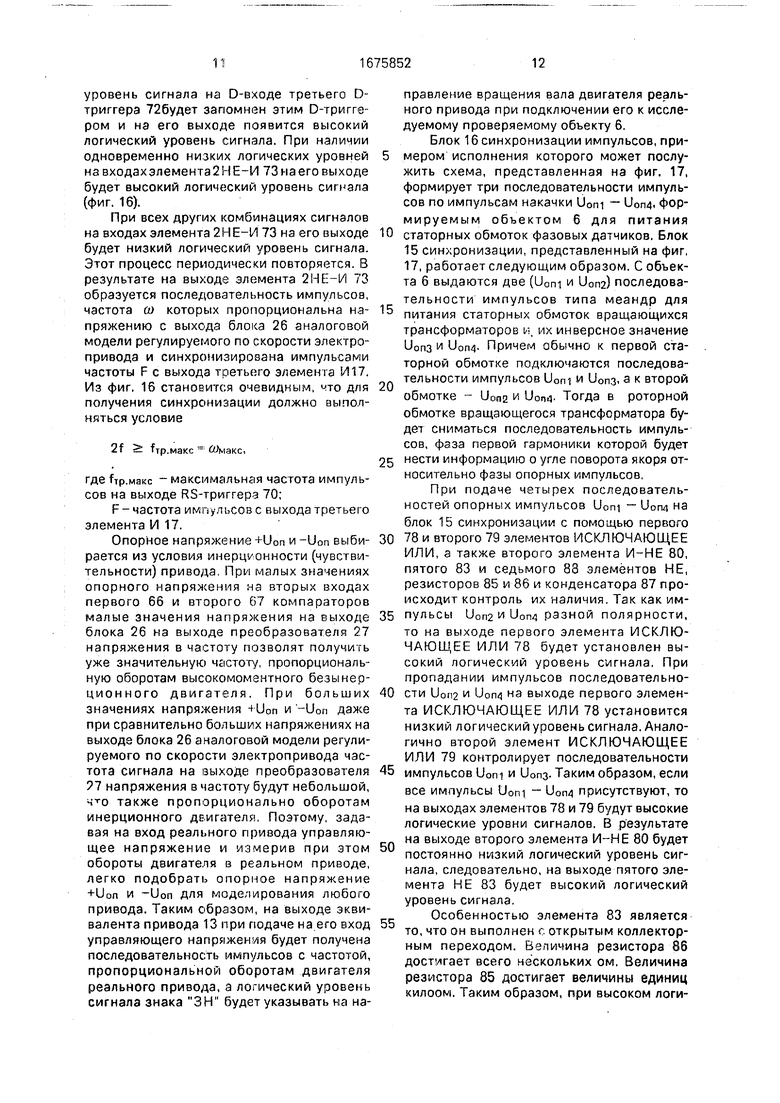

По каждому положительному фронту импульса последовательности на выходе второго D-триггера 71 будет устанавливаться низкий логический уровень сигнала с его собственного D-вхрда. По положительному фронту импульса F с выхода третьего элемента НЕ 74 низкий логический уровень сигнала с выхода второго D-триггера 71 будет запомнен третьим D-триггером 72 и на его выходе появится низкий логический уровень сигнала. По низкому логическому уровню сигнала с выхода третьего D-триггера 72 второй D-триггер 71 по S-входу установит на своем выходе высокий логический уровень сигнала. По ближайшему положительному фронту импульса частоты F с выхода третьего элемента НЕ 74 высокий логический

уровень сигнала на D-входе третьего D- триггера 72будет запомнен этим D-тригге- ром и на его выходе появится высокий логический уровень сигнала. При наличии одновременно низких логических уровней навходахэлементэ2НЕ-И 73наего выходе будет высокий логический уровень сигнала (фиг. 16).

При всех других комбинациях сигналов на входах элемента 2НЕ-И 73 на его выходе будет низкий логический уровень сигнала. Этот процесс периодически повторяется. В результате на выходе элемента 2НЕ-И 73 образуется последовательность импульсов, частота со которых пропорциональна напряжению с выхода блока 26 аналоговой модели регулируемого по скорости электропривода и синхронизирована импульсами частоты F с выхода третьего элемента И17. Из фиг. 16 становится очевидным, что для получения синхронизации должно выполняться условие

2f 15 Ттр.макс ,

где tip.макс - максимальная частота импульсов на выходе RS-триггера 70;

F - частота импульсов с выхода третьего элемента И 17.

Опорное напряжение +U0n и -Uon выбирается из условия инерционности (чувствительности) привода. При малых значениях опорного напряжения на вторых входах первого 66 и второго 67 компараторов малые значения напряжения на выходе блока 26 на выходе преобразователя 27 напряжения в частоту позволят получить уже значительную частоту, пропорциональную оборотам высокомоментного безынерционного двигателя. При больших значениях напряжения +Uon и -Uon даже при сравнительно больших напряжениях на выходе блока 26 аналоговой модели регулируемого по скорости электропривода частота сигнала на выходе преобразователя 77 напряжения в частоту будут небольшой, что также пропорционально оборотам инерционного двигателя. Поэтому, задавая на вход реального привода управляющее напряжение и измерив при этом обороты двигателя в реальном приводе, легко подобрать опорное напряжение +Uon и -Don для моделирования любого привода. Таким образом, на выходе эквивалента привода 13 при подаче на его вход управляющего напряжения будет получена последовательность импульсов с частотой, пропорциональной оборотам двигателя реального привода, а логический уровень сигнала знака ЗН будет указывать на направление вращения вала двигателя реального привода при подключении его к исследуемому проверяемому объекту 6.

Блок 16 синхронизации импульсов, примером исполнения которого может послужить схема, представленная на фиг. 17, формирует три последовательности импульсов по импульсам накачки U0ni - Uon4. формируемым объектом 6 для питания

0 статорных обмоток фазовых датчиков. Блок 15 синхронизации, представленный на фиг. 17, работает следующим образом. С объекта 6 выдаются две (и0щ и Don;) последовательности импульсов типа меандр для

5 питания статорных обмоток вращающихся трансформаторов и. их инверсное значение Уопз и Uon4- Причем обычно к первой ста- торной обмотке подключаются последова- тельности импульсов Uoni и Uona. а к второй обмотке - Uona и Uona- Тогда в роторной обмотке вращающегося трансформатора будет сниматься последовательность импульсов, фаза первой гармоники которой будет

5 нести информацию о угле поворота якоря относительно фазы опорных импульсов.

При подаче четырех последовательностей опорных импульсов Uoni Uonq на блок 15 синхронизации с помощью первого

0 78 и второго 79 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а также второго элемента И-НЕ 80, пятого 83 и седьмого 88 элементов НЕ, резисторов 85 и 86 и конденсатора 87 происходит контроль их наличия. Так как им5 пульсы Uona и Uon4 разной полярности, то на выходе первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 78 будет установлен высокий логический уровень сигнала. При пропадании импульсов последовательноо сти Uon2 и Uon4 на выходе первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 78 установится низкий логический уровень сигнала. Аналогично второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 79 контролирует последовательности

5 импульсов Uoni и Оопз- Таким образом, если все импульсы и0щ - U0n4 присутствуют, то на выходах элементов 78 и 79 будут высокие логические уровни сигналов. В результате на выходе второго элемента И-НЕ 80 будет постоянно низкий логический уровень сигнала, следовательно, на выходе пятого элемента НЕ 83 будет высокий логический уровень сигнала.

Особенностью элемента 83 является то, что он выполнен с открытым коллекторным переходом. Величина резистора 86 достигает всего нескольких ом. Величина резистора 85 достигает величины единиц килоом. Таким образом, при высоком логи0

ческом уровне сигнала на выходе пятого элемента НЕ 83 происходит медленно заряд конденсатора 87, а следовательно, на выходе седьмого элемента НЕ 88 будет некоторое время установлен низкий логический уровень сигнала, а потом высокий, Но достаточно оборвать одну из цепей, передающих сигналы U0ni - U0n4 от объекта 6, на выходе второго 80 элемента И-НЕ установится высокий логический уровень сигнала, а следовательно, на выходе пятого 83 элемента НЕ - низкий логический уровень сигнала. При низком уровне логического сигнала на выходе пятого элемента НЕ 83 конденсатор 87 быстро разряжается из-за малой величины резистора 86. Зато короткие положительные импульсы, возникающие на выходе пятого элемента НЕ 83 при обрыве только сигнала одной последовательности опорных частот из ряда U0ni - U0n4, не успевают зарядить конденсатор 87 из- за сравнительно большой величины резистора 85. Таким образом, на выходе седьмого элемента НЕ 88 будет удерживаться высокий логический уровень сигнала, который по третьему входу управления запретит работу имитатору 23 фазовых импульсов,

Элемент 89 индикации при появлении высокого логического уровня сигнала на выходе седьмого элемента И-НЕ 88 указывает на отсутствие опорных импульсов U0ni - Uon4 от объекта 6 контроля. В качестве элемента 89 индикации используется светодиод, но можно использовать, например, звуковое сигнализирующее устройство. Одна из последовательностей импульсов Uoni - Uon4- синхронизированных импульсами fg с выхода делителя 14 частоты, используется далее для организации работы имитатора 23 фазового датчика.

В исходном состоянии по импульсу Сброс, инвертированному шестым элементом НЕ 84, на первом (прямом) выходе пятого D-триггера 82 установится высокий логический уровень сигнала. Одновременно на втором (инверсном) выходе пятого D-триггера 82 будет низкий логический уровень сигнала. По переднему (положительному) фронту импульса последовательности Uonai приходящего от объекта 6, на выходе четвертого D-триггера 81 будет установлен уровень сигнала D-входа этого триггера. Так как D-вход D-триггера 81 подключен к шине с нулевым логическим потенциалом, то на выходе этого D-триггера по положительному фронту импульса последовательности Uon2 будет установлен низкий

логический уровень сигнала. По ближайшему положительному фронту импульса fg с выхода делителя 14 частоты низкий логический уровень сигнала установится на

первом (прямом) выходе пятого D-триггера 82. Наличие низкого логического уровня на первом выходе пятого D-триггера 82, а следовательно, на S-входе четвертого D- триггера 81 позволит установить на выходе четвертого D-триггера 81 высокий логический уровень сигнала.

По положительному фронту следующего импульса fg с выхода делителя 14 частоты

на выходе пятого D-триггера 82 установится высокий логический уровень сигнала. В результате на первом выходе пятого D- триггера 82 будет сформирован импульс г, а на втором (инверсном) выходе - инверсный импульс. Процесс формирования импульсов (ft и ун периодически повторяется по каждому положительному фронту импульса последовательности U0r. Импульсы рг с первого выхода блока 14 синхронизации поступают на второй вход третьего элемента И 17. В результате (фиг. 18) при поступлении импульса с первого выхода блока 15 синхронизации на второй вход третьего элемента И 17 запрещается прохождение импульса fg с выхода делителя 14 частоты через первый вход третьего элемента И 17 на его выход.

Одновременно с второго выхода блока 15 синхронизации поступает инверсное

значение импульса fa на второй вход первого элемента И-НЕ 18, чем оазоеша- ется прохождение одного импульса fg с первого входа первого элемента И-НЕ 18 на его выход. В результате на выходе первого элемента И-НЕ 18 сформируется короткий импульс, который поступает на первый вход управления имитатора 23 фазового датчика. На второй вход управления имитатора фазового датчика

поступают импульсы fg с выхода делителя 14 частоты. На третий вход управления имитатора 23 фазового датчика поступает импульс сброса с третьего выхода блока 15 синхронизации при отсутствии импульсов

последовательностей U0ni - Uon-q с объекта 6. Последовательность импульсов частоты F с выхода третьего элемента И 17 управляет работой преобразователя 27 напряжения в частоту, Полученные на втором выходе эквивалента привода 13 импульсы поступают на первые входы первого 19 и второго 20 элементов И. По положительному фронту импульса частоты fg на С-входе первого D-триггера 16 (фиг. 2)

логический уровень сигнала ЗН запоминается этим D-триггером.

При высоком логическом уровне сигнала ЗН на D-входе первого D-триггера 16 на первом (прямом) его выходе установит- ся высокий логический уровень сигнала, а на втором инверсном выходе - низкий логический уровень сигнала. Таким образом, на втором входе первого элемента И 19 будет присутствовать высокий логический уровень сигнала, а на втором входе второго 20 элемента И - низкий логический уровень сигнала. В результате через первый элемент И 19 на суммирующий вход первого двоичного счетчика 21 будут прохо- дить импульсы частоты СУ. Второй элемент И 20 из-за наличия низкого логического уровня сигнала на втором собственном входе импульсов частоты со с первого входа на выход не выдает. В результате им- пульсы на вычитающем входе первого двоичного счетчика 21 отсутствуют. В исходное состояние, когда на всех выходах первого счетчика 21 низкие логические уровни, первый счетчик 21 устанавливается сигналом Сброс.

При поступлении импульсов от первого элемента И 19 на информационных выходах первого двоичного счетчика 21 устанавливаются высокие или низкие логические уровни сигнала. Объем (разрядность) счетчика 21 выбирается таким, чтобы двоичный код числа на его выходе равнялся или был больше количества дискрет в шаге фазового датчика. Например, для вращающегося транс- форматора типа ВТМ-1Г число дискрет равно 512 при полном обороте вала датчика. Для датчика типа ДПФ-100Д число дискрет равно 128. Для датчиков типа индуктосин - 2048. Поэтому объем первого счетчика 21 желательно сразу выбрать равным 2048. Для имитации фазового датчика служит имитатор 23 фазового датчика.

Пример исполнения имитатора 23 представлен на фиг. 19. В момент включения устройства первый конденсатор 87 еще не успевает зарядиться. Следовательно, на выходе седьмого элемента НЕ 88 некоторое время удерживается высокий логический уровень сигнала. Наличие высокого логического уровня сигнала на третьем входе управления имитатора фазового датчика, а следовательно, на входах сброса (Р-входах) третьего 90, четвертого 91, пятого 92 двоичных счетчиков, позволяет установить их в исходное состояние, когда на информационных выходах присутствуют низкие логические уровни сигналов. Если объект 6 работает с датчиком типа

ДПФ-100Д, с количеством дискрет 128 в шаге фазового датчика при одном полном повороте вала датчика, то шестой коммутатор 100 под действием сигнала Упр. 5 должен замкнуть первый информационный вход (конденсатор 94 и третий резистор 95) с информационным выходом. Если проверяемый объект 6 работает с датчиком типа ВТМ-1Г или аналогичным, в которых количество дискрет достигает 512, то шестой коммутатор 100 под действием сигнала Упр. 5 должен замкнуть второй информационный вход (третий конденсатор 96 и четвертый резистор 97) с информационным выходом.

Если проверяемое устройство работает с фазовым датчиком типа Индуктосин, в котором количество дискрет достигает 2048 в шаге фазового датчика (изменения фазы на 360°), то под действием сигнала Упр. 5 шестой коммутатор 100 должен соединить свой третий информационный вход (четвертый конденсатор 98 и пятый резистор 99) с информационным выходом при отключенном первом и втором информационных входах

N .

где N - общий коэффициент деления счетчиков;

fg - частота импульсов с выхода делителя 14 частоты;

fuon частота импульсов накачки от одной из последовательностей Uoni - U0n4. выдаваемых проверяемым объектом.

Объем счетчиков 90-92 соответствует объему (разрядности) счетчика 21.

При расчете частоты fg следует учитывать коэффициент N деления счетчиков 90-92 относительно информационного выхода (например, первого выхода пятого двоичного счетчика 92 при работе проверяемого объекта 6 с датчиком ВТМ-1Г или аналогичным, когда ),l, fyon для каждого типа датчика определяется его конструктивными параметрами. Под действием импульсов fg на выходе шестого компаратора 100 формируются низкие или высокие логические уровни сигналов. В результате на выходе шестого коммутатора 100 получим импульсы типа меандр с частотой, равной частоте опорных импульсов Uoni - УОПФ Если двоичный код числа с выхода первого двоичного счетчика 21 равен числу ноль, то на информационном выходе шестого коммутатора 100 импульсы будут с нулевым сдвигом пх фазе.

После записи двоичного кода числа, отличного от нуля, которое сформировано первым двоичным счетчиком 21 в двоичные

счетчики 90-92 по импульсу FI, фаза выходных импульсов смещается. Аналогично при записи нового двоичного кода нового числа устанавливается новое значение фазы сигнала ДФ на информационномвыходе ше- стого коммутатора 100. Таким образом, под действием импульсов частотой и с выхода эквивалента привода 13 на выходе имитатора 23 будет изменяться фаза выходного сигнала ДФ. Используя информацию о пе- ремещении фазы сигнала ДФ, объект 6 будет определять имитируемую величину перемещения по заданному управляющему напряжению AU. Для этого выходДФ имитатора 23 вторым коммутатором 25 по сиг- налу Упр. 1 подключается к своему одноименному по номеру канала измерения (Д1 ...ДМ) объекта 6. Конденсаторы 94, 96, 98 и резисторы 95, 97, 99 устраняют постоянную составляющую в логическом сигнале с выходов пятого 91 и шестого 92 двоичных счетчиков.

Параллельно сигналу ДФ имитатооом 23 фазового датчика формируется сигнал маркера ДМ. Этот сигнал используется в реальных датчиках, устанавливаемых на станках для выхода подвижных органов станка в исходную позицию. Формируется этот сигнал один раз на полный оборот вала датчика. Для датчика ДПФ-100Д длитель- ность такого сигнала соответствует 11° поворота вала датчика. Формирователь 93 маркера фазового датчика позволяет имитировать сигнал маркера для фазовых датчиков (например, датчиков ДПФ-100Д, ВТМ-1Г, индуктосин). Примером реализации узла, формирующего сигналы маркера, ДМ, может послужить схема, представленная на фиг. 20. Седьмой коммутатор 104 синхронно с шестым коммутатором 100 подключает один тринадцатый 101, или четырнадцатый 102, или пятнадцатый 103 элемент И. Входы тринадцатого элемента И 101 для датчика со 128 дискретами подключены к выходам пятого, шестого и седь- мого разрядов первого двоичного счетчика 21. Входы четырнадцатого элемента И 102 для датчика с 512 дискретами подключены к выходам седьмого, восьмого и девятого разрядов первого 21 двоич- ного счетчика. Входы пятнадцатого элемента И 103 для датчика с 2048 дискретами подключены к выходам девятого, десятого, одиннадцатого разрядов первого двоичного счетчика 21.

Чем больше младших разрядов подключено к элементам И 101-103, тем уже импульс будет сформирован на выходах этих элементов. По импульсу на выходе седьмого коммутатора 104 четвертый компаратор

сформирует импульс ДМ. При низком логическом уровне сигнала на выходе седьмого коммутатора 104 четвертый компаратор 105 на своем выходе устанавливает отрицательный уровень сигнала. При высоком логическом уровне сигнала на выходе седьмого коммутатора 104 четвертый компаратор 105 на своем выходе устанавливает положительный уровень сигнала. Таким образом, сигнал маркера ДМ на выходе четвертого компаратора 105 будет двухпо- лярным. Параллельно сигналу ДФ через второй коммутатор 25 подаются сигналы ДМ на входы Д1-ДЫ проверяемого устройства числового программного управления. Таким образом, образована полная имитация привода, который, вращая вал двигателя, перемещает объект, а также вращает ось фазового датчика путем генерации импульсов сигнала знака ЗН и сигналов ДФ и ДМ.

Если объект 6 работает только с импульсными датчиками, то опорные импульсы Uoni - Uon4 для таких датчиков не генерируются. Импульсные датчики вырабатывают две последовательности импульсов типа меандр, но сдвинутые относительно друг друга по фазе на 90°. Для повышения достоверности передачи импульсных сигналов, параллельно основным двум последовательностям импульсных сигналов, передаются еще две дополнительные последовательности сигналов, имеющие инверсные значения логических уровней сигналов по отношению к основным. Информация о перемещении от датчика кодирована кодом Грея. Имитатор 22 импульсного датчика позволяет по двоичному коду, принятому от первого двоичного счетчика 21, сформировать две последовательности импульсов и инверсные им значения импульсов, аналогичные выдаваемым в обычных датчиках, а также сигнал маркера, формируемый для выхода устройства в исходное или заданное состояние. Примером исполнения такого иммтлтора 22 импульсного датчика может послужить схема, приведенная на фиг. 21. От первого двоичного счетчика 21 с выходов первого и второго разрядов поступают изменяющиеся по времени логические уровни сигналов, формируемые импульсами частоты о) с выхода эквивалента привода 13. Третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 106 при различных логических уровнях сигналов первого и второго разрядов на выходе первого двоичного счетчика 21 на своем выходе устанавливает высокий логический уровень сигнала.

Если на выходах первого и второго разрядов первого двоичного счетчика 21 одновременно высокие или низкие логические уровни сигналов, то третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 106 устанавливает на своем выходе сигнал низкого логического уровня (фиг. 22). В результате периодического изменения сигналов на входах третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106 на его информационном выходе будет формироваться последовательность импульсов типа меандр, по форме соответствующая сигналу Uai, в реальном импульсном датчике. Благодаря восьмому элементу НЕ 107 на его выходе формируется сигнал, соответствующий по форме сигналу Ua реального импульсного датчика. Сигнал второго разряда первого двоичного счетчика

21соответствует по форме сигналу U32 и поэтому он проходит на выход имитатора

22импульсного датчика без изменений. Благодаря девятому элементу НЕ 108 на его выходе формируется сигнал, соответствующий сигналу Оа2; реального импульсного датчика,

Для формирования импульсного сигнала маркера в имитаторе 22 импульсного датчика имеется формирователь 109 маркера импульсного датчика. Формирователь 109 маркера импульсного датчика (фиг. 23) позволяет имитировать короткий импульс, соответствующий по длительности импульсу маркера в реальном импульсном датчике, а также инверсный импульс по отношению к основному для повышения достоверности передачи маркерного сигнала. Входы семнадцатого элемента И 110 подключены с пятого по самый старший разряд (двенадцатый разряд). Таким образом, за полный цикл изменения кодов на информационных выходах (что соответствует полному обороту вала импульсного датчика) и при установлении одновременно высоких логических уровней сигналов на входах семнадцатого элемента И 110 на выходе семнадцатого элемента И 110 появится высокий логический уровень сигнала Ua0- Благодаря десятому элементу НЕ 111 будет сформировано инверсное значение сигнала Ua0i что соответствует сигналам маркера реального импульсного датчика.

Имитатор 24 амплитудного датчика по двоичному коду на выходе первого двоичного счетчика 21 формирует аналоговый сигнал ДА. В качестве имитатора 24 амплитудного датчика может послужить циф- роаналоговый преобразователь. Для формирования маркерного сигнала схема

не отличается от приведенной на фиг. 23 для импульсного датчика. Под действием сигнала Упр. 1 второй коммутатор 25 подключает тот датчик, с которым работает объект б.

Примером исполнения второго коммутатора 25 может послужить фиг. 24. Цепь замыкается в элементе аналоговой коммутации при подаче на вход управления

высокого логического уровня сигнала. Поэтому, задавая на один из входов управления А, Ф или И сигнал Упр. 1 высокого логического уровня, будет к объекту 6 подключен соответственно имитатор аналогового 24, фазового 23 или импульсного 22 датчика. Так как количество имитаторов 2 движения инструмента в устройстве соответствует количеству каналов управления, по которым управляет

объект 6, то, задавая отдельно сигнал Упр. 1 на входы И, Ф или А второго 25 коммутатора, для каждого имитатора 2 движения индивидуально можно подобрать любую гамму имитируемых датчиков. Одновременно импульсы частоты а) с выходов первого 19 или второго 20 элементов И (в зависимости от логического уровня сигнала ЗН на первом выходе эквивалента привода 13) поступают на одноименную

по номеру канала информационную группу входов блока 3 формирования координатных данных перемещений.

Блок 3 формирования координатных данных перемещений (фиг. 4) содержит каналы 29 формирования координатных данных, количество которых соответствует количеству имитаторов 2 движения. Первый информационный вход каждого канала 29 принимает сигналы с частотой со с выхода

первого элемента И 19. Второй информационный вход каждого канала 29 формирования координатных данных принимает сигналы с частотой а) с выхода второго элемента И 20. По сигналам частоты а), которые

несут информацию о скорости вращения вала двигателя привода, канал 29 формирования координатных данных формирует на своем втором информационном выходе аналоговое напряжение, пропорциональное

положению объекта на реальном станке с ЧПУ, под действием которого луч записи запоминающей электронно-лучевой трубки индикатора 12 будет установлен в соответствующее этому напряжению положение.

Кроме того, на первом информационном выходе канала 29 формирования координатных данных будут сформированы положительные импульсы, которые через первый элемент ИЛИ 30. формирователь 4

импульсов подсвета управляют модулятором луча записи запоминающей трубки индикатора 12.

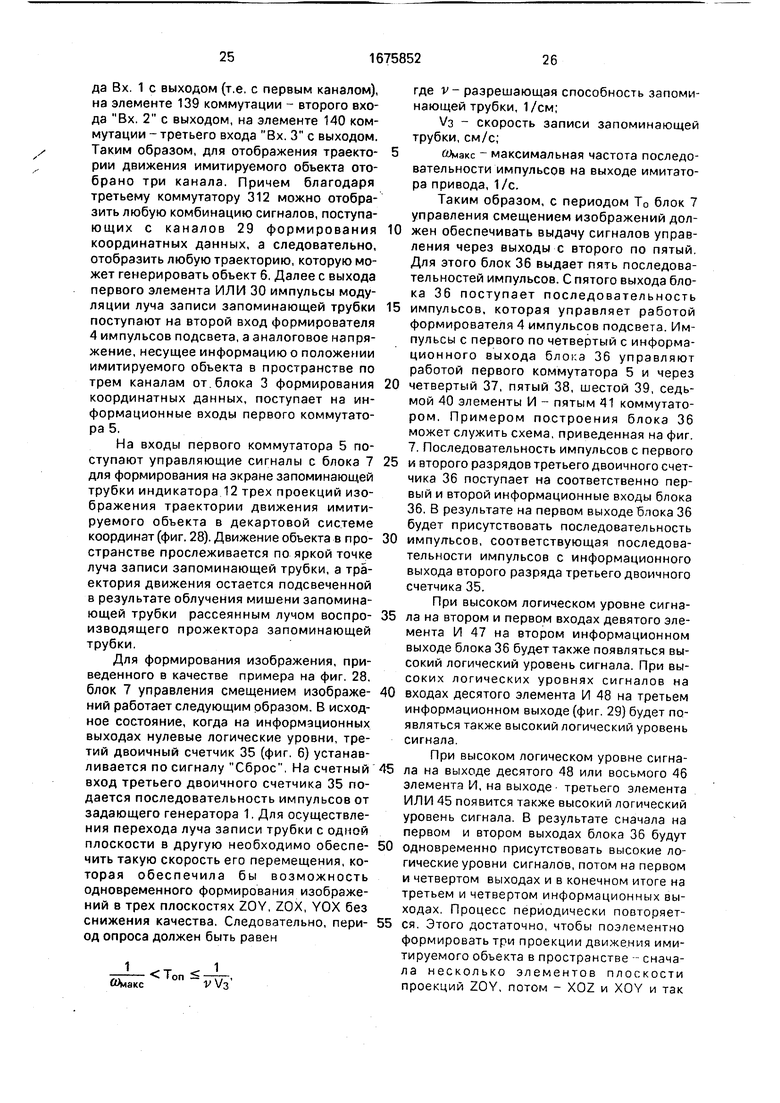

Канал 29 формирования координатных данных (фиг. 5) с помощью второго двоичного счетчика 32 функционирует по сигналам частоты ft), несущим информацию об имитируемой скорости вращения вала реального привода, При высоком логическом уровне сигнала ЗН на первом выходе эквивалента привода 13 сигналы частоты со через первый элемент И 19 поступают на суммирующий вход второго двоичного счетчика 32, когда счетчик осуществляет прямой счет. Если принять во внимание, что на выходе первого разряда второго двоичного счетчика 32 под действием импульсов частоты О) на суммирующий вход появляются последовательно во времени высокие или низкие логические уровни сигналов, соответствующие минимальному перемещению, то суммарное количество разрядов второго двоичного счетчика 32 выбирается из максимально возможного перемещения подвижного объекта на реальном станке по конкретной координате. Таким образом, если на выходе первого разряда второго двоичного счетчика 32 уровень сигнала логической единицы будет соответствовать перемещению в один микрон, то для имитации перемещения на 10 м счетчик должен иметь двадцать четыре разряда выходных сигналов, так как 22 равно 162 миллиона дискрет, что выше 100 млн. микрон, составляющих расстояние в 10 м.

Если количество разрядов второго 25 двоичного счетчика увеличить до двадцати семи разрядов, то получим имитацию перемещения подвижного объекта более 100 м (128 м). Так как время счета второго двоичного счетчика 32 постоянно, то при изменении частоты со (т.е. скорости) на одном из входов этого счетчика на его выходах будем получать двоичный код, соответствующий пути. При подаче импульсов частоты ft) на суммирующий вход путь (двоичный код числа) увеличивается, а при подаче импульсов частоты ш на вычитающий вход - уменьшается, Путем подачи сигнала Упр. 2 можем сразу записать двоичный код с информационных входов, тем самым установить луч запоминающей трубки индикатора 12 в определенную исходную точку. При поступлении сигнала Сброс на выходах второго двоичного счетчика 32 устанавливаются сигналы с низким логическим уровнем, что соответствует нулевому перемещению по данному каналу. Получаемый двоичный код через

четвертый 33 коммутатор поступает на циф- роаналоговый преобразователь 34.

Разрядность цифроаналогового преобразователя 34 выбирают исходя из разре- шающей способности запоминающей трубки индикатора 12. При подключении четвертым коммутатором 33 информационных входов цифроаналогового преобразователя 34 к информационным выходам

младших разрядов второго двоичного счетчика 32 на экране трубки будут отображены мелкие детали участка общей траектории, имитируемой имитатором 2 движения. При подключении информационных входов цифроаналогового преобразователя 34 к информационным выходам (через коммутатор 33) старших разрядов на экране запоминающей трубки будет отображена полная траектория имитируемого движения подвижного органа, генерируемая имитатором 2 движения без мелких деталей изображения. Переключение информационных выходов второго двоичного счетчика 32 к информационным

входам цифроаналогового преобразователя 34 осуществляется по сигналу Упр. 4 четвертым коммутатором 33, Пример исполнения такого коммутатора показан на фиг, 25.

При подаче высокого логического сигнала Упр. 4 по шине 1 мм с первого 124 по десятый 133 элементы коммутации разрешают прохождение сигналов с первого своего информационного входа на

информационный выход, Это происходит благодаря наличию в каждом из них третьего 134, четвертого 135, пятого 136, шестого 137 элементов И-НЕ (фиг. 26). Таким образом, информационный выход первого разряда второго двоичного счетчика 32 будет подключен элементом 124 коммутации к входу первого разряда цифроаналогового преобразователя 34. Информационный выход второго разряда второго двоичного

счетчика 32 элементом 125 коммутации будет подключен к информационному входу второго разряда цифроаналогового преобразователя 34. Информационный выход третьего разряда второго двоичного счетчика 32 элементом 126 коммутации будет подключен к информационному входу третьего разряда цифроаналогового преобразователя 34. Остальные информационные выходы - четвертого-десятого

разрядов окажутся подключенными соответственно 127-133 элементами коммутации к информационным входам четвертого-десятого разрядов цифроаналогового преобразователя 34.

Таким образом, если вес первого разряда соответствует имитируемому перемещению {соответствующему реальному перемещению объекта на станке) в один микрон, то благодаря десятиразрядному цифроаналоговому преобразователю 34 минимальное аналоговое напряжение на выходе его будет соответствовать перемещению луча запоминающей трубки индикатора 12 на величину, соответствующую одной тысячной всего поля изображения, а максимальное значение имитации перемещения объекта величиной в один миллиметр будет отображено на все поле экрана (так как 1 микрон, а следовательно, дискреты).

При подаче сигнала высокого логического уровня Упр. 4 по шине 10 мм элементами коммутации с 124-133 к десяти информационным входам цифроаналого- вого преобразователя будут подключены информационные выходы с пятого по четырнадцатый разряд второго двоичного счетчика 32. Таким образом, на экране запоминающей трубки будет отображена траектория перемещения объекта величиной 16 мм с точностью 32 микрона (так как 2 32, а 214 16284). При подаче сигнала Упр. 4 высоким логическим уровнем по шине Н1М элементами 124-133 коммутации к информационным входам цифроана- логового преобразователя 34 будут соответственно подключены информационные выходы с одиннадцатого по двадцатый разряд второго двоичного счетчика 32. Таким образом, на экране запоминающей трубки будет отображена траектория перемещения объекта на величину более двух метров с точностью два миллиметра (так как 211-2048 дискрет, а тыс. дискрет).

При подаче сигнала Упр. 4 высокого логического уровня по шине 10 мм элементами 124-133 коммутации информационные входы цифроанзлогового преобразователя 34 окажутся подключенными соответственно к информационным выходам с пятнадцатого по двадцать четвертый разрядов второго двоичного счетчика 32. Таким образом, на экране запоминающей трубки будет отображена траектория перемещения объекта величиной 16 метров с точностью 32 мм (так как 215 32368 дискреты, а 224 Т6284 тыс. дискрет).

Информационные выходы второго двоичного счетчика 32 могут подключаться к входам четвертого коммутатора 33 и другим образом, подбирая при этом величину

и точность отображаемой траектории на экране запоминающей трубки.

Для осуществления указанной коммутации в каждом элементе 124-133 коммутации третий 134, четвертый 135, пятый 136, шестой 137 элементы И-НЕ выбраны с открытым коллекторным выходом, что позволяет объединить их выходы. Первые входы элементов И подключаются к ин0 формационным выходам второго двоичного счетчика 32, а вторые входы принимают управляющие сигналы Упр. 4 высокого логического уровня. Тогда при наличии высокого логического уровня сигнала

5 Упр. 4, например, на третьем элементе И-НЕ 134 позволит последовательности логических уровней сигналов на Вх, 1 сформировать последовательность логических уровней сигналов на выходе

0 третьего элемента И-НЕ 134, а следовательно, и на выходе одиннадцатого элемента НЕ 143.

Количество каналов 29 формирования координатных данных определяется коли5 чеством имитаторов 2 движения. С выхода первого разряда четвертого коммутатора 33 через первый информационный выход каждого канала 29 формирования координатных данных выдаются импульсные сиг0 налы на первый элемент ИЛИ 30 для формирования импульсов подсвета (импульсов, управляющих модулятором луча записи запоминающей трубки). С второго информационного выхода каждого канала

5 29 формирования координатных данных поступают аналоговые напряжения, сформированные цифроаналоговым преобразователем 34 на одноименные по номеру информационные входы третьего коммута0 тора 31. Третий коммутатор 31 позволяет по сигналам Упр. 6 подключить любой из информационных входов к выходам первого, второго или третьего канала. Третий коммутатор 31 простейшим образом может

5 быть реализован с помощью трех галетных переключателей, имеющих 11 положений на одно направление или на интегральных микросхемах аналоговых коммутаторов по схеме, приведенной в качестве примера ис0 полнения коммутатора на фиг. 27.

Информационные входы одиннадцатого 138, двенадцатого 139,тринадцатого 140 элементов коммутации объединены по входам и каждый подключается к второму

5 выходу одноименного по номеру канала 29 формирования координатных данных. Задавая трехразрядный двоичный код сигнала Упр. 6 на каждый элемент коммутации происходит подключение, например, на элементе 138 коммутации первого вхо

да Вх. 1 с выходом (т.е. с первым каналом), на элементе 139 коммутации - второго входа Вх. 2 с выходом, на элементе 140 коммутации - третьего входа Вх. 3 с выходом. Таким образом, для отображения траектории движения имитируемого объекта отобрано три канала, Причем благодаря третьему коммутатору 312 можно отобразить любую комбинацию сигналов, поступа- ющих с каналов 29 формирования координатных данных, а следовательно, отобразить любую траекторию, которую может генерировать обьект 6. Далее с выхода первого элемента ИЛИ 30 импульсы модуляции луча записи запоминающей трубки поступают на второй вход формирователя 4 импульсов подсвета, а аналоговое напряжение, несущее информацию о положении имитируемого объекта в пространстве по трем каналам от блока 3 формирования координатных данных, поступает на информационные входы первого коммутатора 5.

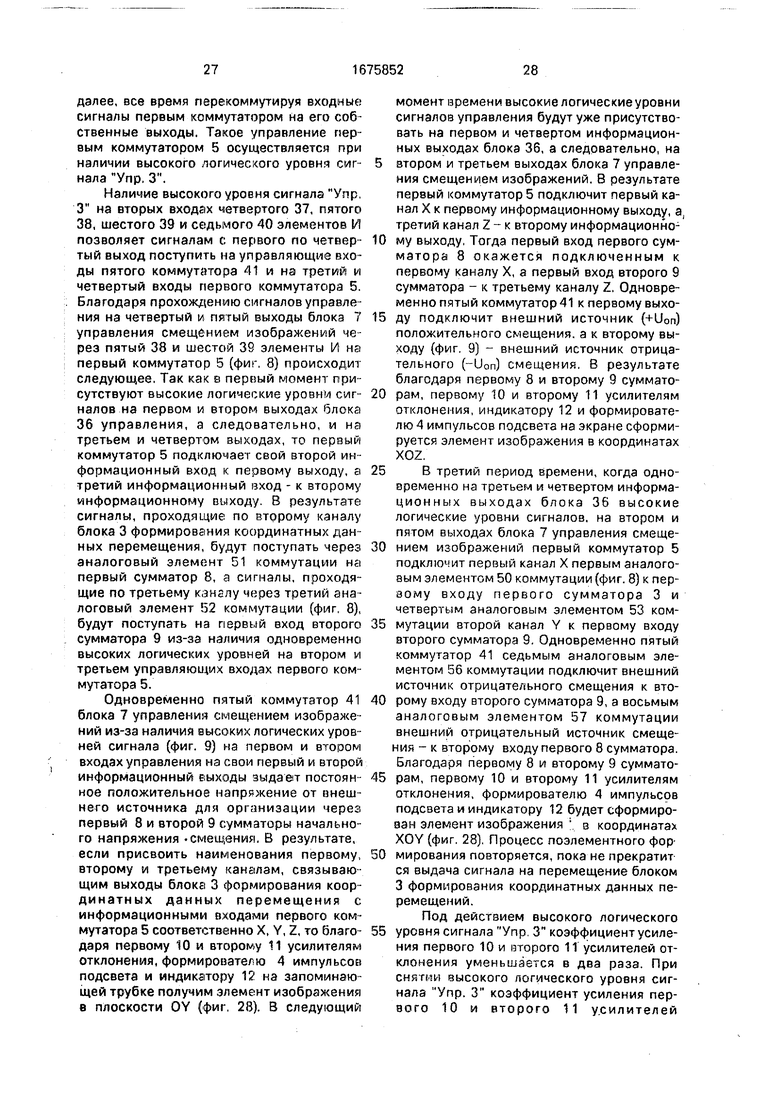

На входы первого коммутатора 5 поступают управляющие сигналы с блока 7 для формирования на экране запоминающей трубки индикатора 12 трех проекций изображения траектории движения имитируемого объекта в декартовой системе координат (фиг, 28). Движение объекта в пространстве прослеживается по яркой точке луча записи запоминающей трубки, а траектория движения остается подсвеченной в результате облучения мишени запоминающей трубки рассеянным лучом воспроизводящего прожектора запоминающей трубки.

Для формирования изображения, приведенного в качестве примера на фиг. 28, блок 7 управления смещением изображений работает следующим образом. В исходное состояние, когда на информационных выходах нулевые логические уровни, третий двоичный счетчик 35 (фиг. б) устанавливается по сигналу Сброс. На счетный вход третьего двоичного счетчика 35 подается последовательность импульсов от задающего генератора 1. Для осуществления перехода луча записи трубки с одной плоскости в другую необходимо обеспечить такую скорость его перемещения, которая обеспечила бы возможность одновременного формирования изображений в трех плоскостях ZOY, ZOX, YOX без снижения качества. Следовательно, период опроса должен быть равен

Т0П

1

W3

где v - разрешающая способность запоминающей трубки, 1/см;

Va - скорость записи запоминающей трубки, см/с;

( - максимальная частота последовательности импульсов на выходе имитатора привода, 1/с.

Таким образом, с периодом Т0 блок 7 управления смещением изображений должен обеспечивать выдачу сигналов управления через выходы с второго по пятый. Для этого блок 36 выдает пять последовательностей импульсов. С пятого выхода блока 36 поступает последовательность

импульсов, которая управляет работой формирователя 4 импульсов подсвета. Импульсы с первого по четвертый с информационного выхода блока 36 управляют работой первого коммутатора 5 и через

четвертый 37, пятый 38, шестой 39, седьмой 40 элементы И - пятым 41 коммутатором. Примером построения блока 36 может служить схема, приведенная на фиг, 7. Последовательность импульсов с первого

и второго разрядов третьего двоичного счетчика 36 поступает на соответственно первый и второй информационные входы блока 36. В результате на первом выходе Ълока 36 будет присутствовать последовательность

импуяьсов, соответствующая последовательности импульсов с информационного выхода второго разряда третьего двоичного счетчика 35.

При высоком логическом уровне сигнала на втором и первом входах девятого элемента И 47 на втором информационном выходе блока 36 будет также появляться высокий логический уровень сигнала. При высоких логических уровнях сигналов на

входах десятого элемента И 48 на третьем информационном выходе (фиг. 29) будет появляться также высокий логический уровень сигнала.

При высоком логическом уровне сигнала на выходе десятого 48 или восьмого 46 элемента И, на выходе третьего элемента ИЛИ 45 появится также высокий логический уровень сигнала. В результате сначала на первом и втором выходах блока 36 будут

одновременно присутствовать высокие логические уровни сигналов, потом на первом и четвертом выходах и в конечном итоге на третьем и четвертом информационных выходах, Процесс периодически повторяется. Этого достаточно, чтобы поэлементно формировать три проекции движения имитируемого объекта в пространстве сначала несколько элементов плоскости проекций ZOY, потом - XOZ и XOY и так

далее, все время перекоммутируя входные сигналы первым коммутатором на его собственные выходы, Такое управление первым коммутатором 5 осуществляется при наличии высокого логического уровня сигнала Упр. 3.

Наличие высокого уровня сигнала Упр. 3 на вторых входах четвертого 37, пятого 38, шестого 39 и седьмого 40 элементов И позволяет сигналам с первого по четвертый выход поступить на управляющие входы пятого коммутатора 41 и на третий и четвертый входы первого коммутатора 5. Благодаря прохождению сигналов управления на четвертый и пятый выходы блока 7 управления смещением изображений через пятый 38 и шестой 39 элементы И на первый коммутатор 5 (фиг. 8) происходит следующее. Так как в первый момент присутствуют высокие логические уровни сигналов на первом и втором выходах блока 36 управления, а следовательно, и на третьем и четвертом выходах, то первый коммутатор 5 подключает свой второй информационный вход к первому выходу, а третий информационный вход - к второму информационному выходу. В результате сигналы, проходящие по второму каналу блока 3 формирования координатных данных перемещения, будут поступать через аналоговый элемент 51 коммутации на первый сумматор 8, а сигналы, проходящие по третьему каналу через третий аналоговый элемент 52 коммутации (фиг. 8), будут поступать на первый вход второго сумматора 9 из-за наличия одновременно высоких логических уровней на втором и третьем управляющих входах первого коммутатора 5.

Одновременно пятый коммутатор 41 блока 7 управления смещением изображений из-за наличия высоких логических уровней сигнала (фиг. 9) на первом и втором входах управления на свои первый и второй информационный выходы выдает постоянное положительное напряжение от внешнего источника для организации через первый 8 и второй 9 сумматоры начального напряжения -смещения, В результате, если присвоить наименования первому, второму и третьему каналам, связывающим выходы блока 3 формирования координатных данных перемещения с информационными входами первого коммутатора 5 соответственно X, Y, Z, то благодаря первому 10 и второму 11 усилителям отклонения, формирователю 4 импульсов подсвета и индикатору 12 на запоминающей трубке получим элемент изображения в плоскости OY (фиг. 28). В следующий

момент времени высокие логические уровни сигналов управления будут уже присутствовать на первом и четвертом информационных выходах блока 36, а следовательно, на

втором и третьем выходах блока 7 управления смещением изображений. В результате первый коммутатор 5 подключит первый канал X к первому информационному выходу, а( третий канал Z - к второму информационно0 му выходу. Тогда первый вход первого сумматора 8 окажется подключенным к первому каналу X, а первый вход второго 9 сумматора - к третьему каналу Z. Одновременно пятый коммутатор 41 к первому выхо5 ду подключит внешний источник (+110п) положительного смещения, а к второму выходу (фиг. 9) - внешний источник отрицательного (-Uon) смещения. В результате благодаря первому 8 и второму 9 суммато0 рам, первому 10 и второму 11 усилителям отклонения, индикатору 12 и формирователю 4 импульсов подсвета на экране сформируется элемент изображения в координатах XOZ.

5 В третий период времени, когда одновременно на третьем и четвертом информа- ционных выходах блока 36 высокие логические уровни сигналов, на втором и пятом выходах блока 7 управления смеще0 нием изображений первый коммутатор 5 подключит первый канал X первым аналоговым элементом 50 коммутации (фиг. 8) к первому входу первого сумматора 3 и четвертым аналоговым элементом 53 ком5 мутации второй канал Y к первому входу второго сумматора 9, Одновременно пятый коммутатор 41 седьмым аналоговым элементом 56 коммутации подключит внешний источник отрицательного смещения к вто0 рому входу второго сумматора 9, а восьмым аналоговым элементом 57 коммутации внешний отрицательный источник смещения - к второму входу первого 8 сумматора. Благодаря первому 8 и второму 9 суммато5 рам, первому 10 и второму 11 усилителям отклонения, формирователю 4 импульсов подсвета и индикатору 12 будет сформирован элемент изображения . в координатах XOY (фиг. 28). Процесс поэлементного фор

0 мирования повторяется, пока не прекратит ся выдача сигнала на перемещение блоком 3 формирования координатных данных перемещений.

Под действием высокого логического

5 уровня сигнала Упр. 3 коэффициент усиления первого 10 и второго 11 усилителей отклонения уменьшается в два раза. При снятии высокого логического уровня сигнала Упр. 3 коэффициент усиления первого 10 и второго 11 усилителей

отклонения восстанавливается, запрещается прохождение импульсов через четвертый 37, пятый 38, шестой 39 и седьмой 40 элементы И, а также через двенадцатый 14 и одиннадцатый 49 элементы И. В результате первый коммутатор 5 постоянно открывает пути прохождения сигналов только первого X и третьего Z каналов на первый вход первого 8 и соответственно второго 9 сумматоров. Импульсы, управляющие формирователем 4 импульсов подсвета, формируются только тринадцатым элементом И 142 и вторым элементом ИЛИ 44. Запрещается пятому коммутатору 41 подключение внешних положительного и отрицательного источников питания к второму входу первого 8 и второго 9 сумматоров. Поэтому на все поле экрана запоминающей трубки индикатора 12 будет формироваться изображение проекции траектории в плоскости XOZ.

Таким образом, с помощью элементов 138, 140 коммутации можно наблюдать любую траекторию, генерируемую любым из каналов 29 формирования координатных данных, путем их избирательного подключения. Формирователь 4 импульсов посвета содержит элемент И, на первый вход которого поступают импульсы подсвета с блока 3 формирования координатных данных и импульсы управления с блока 7 управления смещением изображений.

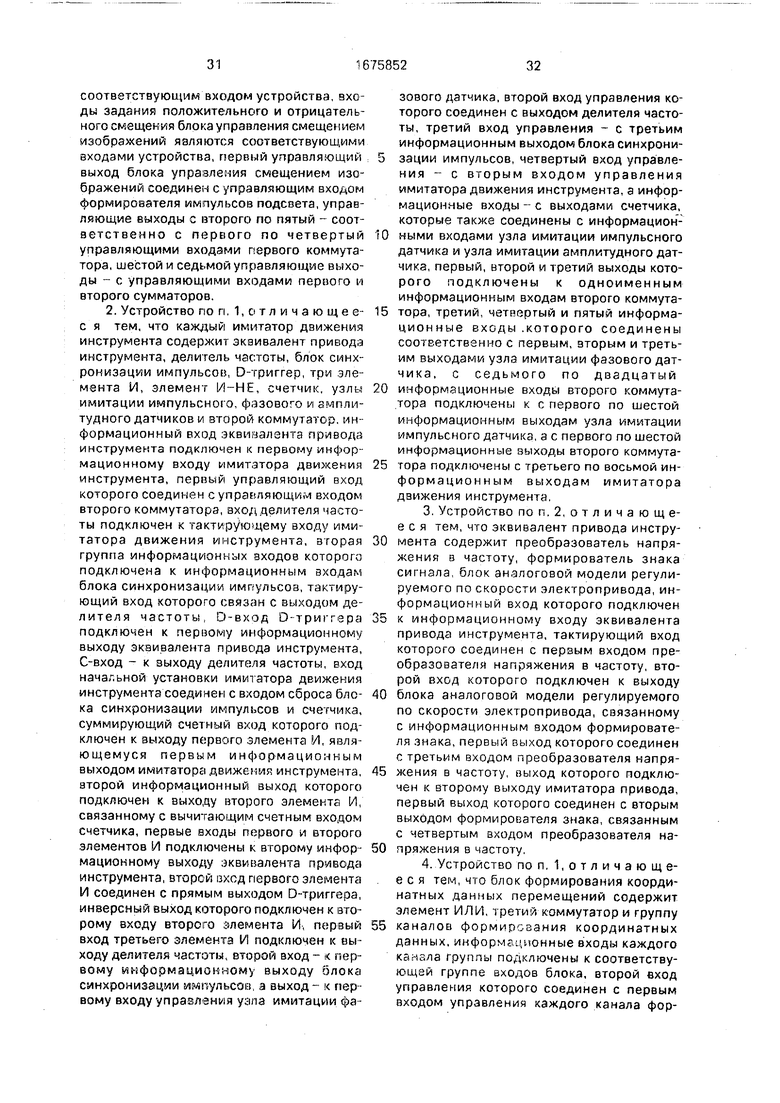

Формула изобретения 1. Устройство для контроля средств числового программного управления, содержащее формирователь импульсов подсвета, индикатор на запоминающей электронно-лучевой трубке, два усилителя отклонения, два сумматора и первый коммутатор, включающий четыре аналоговых элемента коммутации, выход первого усилителя отклонения подключен к входу отклонения луча записи по горизонтали индикатора на запоминающей электроннолучевой трубке, выход второго усилителя отклонения подключен к входу отклонения луча по вертикали индикатора на запоминающей электронно-лучевой трубке, выходы первого и второго сумматоров соединены с информационными входами соответственно первого и второго усилителей отклонения, выход формирователя импульсов подсвета подключен к входу управления модулятором индикатора на запоминающей электронно-лучевой трубке, первый и второй выходы первого коммутатора соединены соответственно с входами слагаемых первого и второго сумматоров, отличающееся тем, что, с целью расширения области применения устройства за счет ввода в него средств имитации движения инструмента, введены задающий генератор,

группа имитаторов движения инструмента, блок формирования координатных данных перемещения и блок управления смещением изображений, тактирующие входы имитаторов движения инструмента группы

0 подключены к выходу задающего генератора, первый и второй входы управления каждого имитатора движения инструмента группы подключены к соответствующим входам устройства, входы начальной уста5 новки - к входу сброса устройства, информационные входы блока формирования координатных данных перемещения, обь- единные попарно, соединены с первыми и вторыми информационными выходами

0 имитаторов движения инструмента, первый, второй и третий входы управления блока формирования координатных данных перемещения соединены с соответствующими входами устройства, а вход

5 начальной установки - с входом сброса устройства, первый выход блока формирования координатных данных перемещения подключен к информационному входу формирователя импульсов подсвета, а три вы0 хода каналов отображения перемещения блока формирования координатных данных перемещения подключены к трем информационным входам первого коммутатора, причем выход второго канала ото5 бражения перемещения блока формирования координатных данных перемещения связан с четвертым информационным входом первого коммутатора, выход третьего канала отображения под0 ключей к третьему информационному входу первого коммутатора, входы управления приводами устройства соединены с первыми информационными входами соответствующих имитаторов движения инструмента,

5 входы питания датчиков перемещения устройства соединены с вторыми информационными входами соответствующих имитаторов движения инструмента, выходы данных о величине перемещений инстру0 мента устройства подключены к информационным выходам с третьего по восьмой соответствующих имитаторов движения инструмента, тактирующий вход блока управления смещением изображений

5 соединен с выходом задающего генератора, вход начальной установки - с входом сброса устройства, первый управляющий вход блока управления смещением изображений и управляющие входы первого и второго усилителей отклонения связаны с

соответствующим входом устройства, входы задания положительного и отрицательного смещения блока управления смещением изображений являются соответствующими аходами устройства, первый управляющий , выход блока управления смещением изображений соединен с управляющим входом формирователя импульсов подсвета, управляющие выходы с второго по пятый - соответственно с первого по четвертый управляющими входами первого коммутатора, шестой и седьмой управляющие выходы - с управляющими входами первого и второго сумматоров.

2. Устройство по п. 1,отличающее- с я тем, что каждый имитатор движения инструмента содержит эквивалент привода инструмента, делитель частоты, блок синхронизации импульсов, D-триггер, три элемента И, элемент И-НЕ, счетчик, узлы имитации импульсного, фазового и амплитудного датчиков и второй коммутатор, информационный вход эквивалента привода инструмента подключен к первому информационному входу имитатора движения инструмента, первый управляющий вход которого соединен с управляющим входом второго коммутатора, вход делителя частоты подключен к тактирующему входу имитатора движения инструмента, вторая группа информационных входов которого подключена к информационным входам блока синхронизации импульсов, тактирующий вход которого связан с выходом де- лителя частоты, D-вход D-триггера подключен к первому информационному выходу эквивалента привода инструмента, С-вход - к выходу делителя частоты, вход начальной установки имитатора движения инструмента соединен с входом сброса блока синхронизации импульсов и счетчика, суммирующий счетный вход которого подключен к выходу первого элемента И, являющемуся первым информационным выходом имитатора движения инструмента, второй информационный выход которого подключен к выходу второго элемента И, связанному с вычитающим счетным входом счетчика, первые входы первого и второго элементов И подключены к второму информационному выходу эквивалента привода инструмента, второй вход первого элемента И соединен с прямым выходом D-триггера, инверсный выход которого подключен к второму входу второго элемента И, первый вход третьего элемента И подключен к выходу делителя частоты, второй вход - к первому информационному выходу блока синхронизации импульсов, а выход - к первому входу управления узла имитации фазового датчика, второй вход управления которого соединен с выходом делителя частоты, третий вход управления - с третьим информационным выходом блока синхронизации импульсов, четвертый вход управления - с вторым входом управления имитатора движения инструмента, а информационные входы - с выходами счетчика, которые также соединены с информацион0 ными входами узла имитации импульсного датчика и узла имитации амплитудного датчика, первый, второй и третий выходы которого подключены к одноименным информационным входам второго коммута5 тора, третий, четвертый и пятый информационные входы которого соединены соответственно с первым, вторым и третьим выходами узла имитации фазового датчика, с седьмого по двадцатый

0 информационные входы второго коммутатора подключены к с первого по шестой информационным выходам узла имитации импульсного датчика, а с первого по шестой информационные выходы второго коммута5 тора подключены с третьего по восьмой ин- формационным выходам имитатора движения инструмента.

3.Устройство по п. 2, о т л и ч а ю щ е- е с я тем, что эквивалент привода инстру0 мента содержит преобразователь напряжения в частоту, формирователь знака сигнала, блок аналоговой модели регулируемого по скорости электропривода, информационный вход которого подключен

5 к информационному входу эквивалента привода инструмента, тактирующий вход которого соединен с первым входом преобразователя напряжения в частоту, второй вход которого подключен к выходу

0 блока аналоговой модели регулируемого по скорости электропривода, связанному с информационным входом формирователя знака, первый выход которого соединен с третьим входом преобразователя напря5 жения в частоту, выход которого подключен к второму выходу имитатора привода, первый выход которого соединен с вторым выходом формирователя знака, связанным с четвертым входом преобразователя на0 пряжения в частоту.

4.Устройство по п. 1, о т л и ч а ю щ е- е с я тем, что блок формирования координатных данных перемещений содержит элемент ИЛИ, третий коммутатор и группу

5 каналов формирования координатных данных, информационные входы каждого канала группы подключены к соответствующей группе входов блока, второй вход управления которого соединен с первым входом управления каждого канала формирования координатных данных группы, второй вход управления каждого канала формирования координатных данных группы связан с первым входом управления блока, вход начальной установки которого соединен с вхо- дом начальной установки каждого канала формирования координатных данных группы, входы элемента ИЛИ подключены к первым выходам каналов формирования координатных данных группы, а выход - к первому выходу блока, информационные входы третьего коммутатора подключены к вторым выходам каналов формирования координатных данных группы, первый информационный выход третьего коммутатора подсоединен к первому выходу канала отображения перемещения блока, второй информационный выход - к второму выходу канала отображения перемещения блока, третий информационный выход - к третьему выходу канала отображения перемещения блока, вход управления третьего коммутатора связан с третьим входом управления блока.

5.Устройство по п. 4, о т л и ч а ю щ е - еся тем, что каждый канал формирования координатных данных группы содержит цифроаналоговый преобразователь, четвертый коммутатор и двоичный счетчик, счетные входы суммирования и вычитания которого подключены соответственно к пер- вому и второму информационным входам канала, вход начальной установки которого подключен к входу начальной установки двоичного счетчика, информационные входы четвертого коммутатора поразрядно подключены к информационным выходам двоичного счетчика, вход управления - к входу управления канала, а информационный выход первого разряда - к первому информационному выходу канала, второй информационный выход которого соединен

с выходом цифроаналогового преобразователя, информационные входы которого поразрядно связаны с информационными выходами четвертого коммутатора.

6.Устройство по п. 1, о т л и ч а ю щ е- еся тем, что блок управления смещением изображений содержит распределитель импульсов, с четвертого по седьмой элементы И, пятый коммутатор и двоичный счетчик, счетный вход которого подключен к тактирующему входу блока, вход начальной установки - к входу начальной установки блока, первый вход распределителя импульсов подключен к выходу первого раз-

ряда двоичного счетчика, выход второго разряда которого соединен с вторым входом распределителя импульсов, первый вход четвертого элемента И подключен к первому выходу распределителя импульсов, являющемуся третьим выходом блока, первый вход пятого элемента И подключен к второму выходу распределителя импульсов, первый вход шестого элемента И - к третьему выходу распределителя импульсов, первый вход седьмого элемента И соединен с четвертым выходом распределителя импульсов, связанным с вторым выходом блока, вторые входы четвертого - седьмого элементов И, а также вход управления распределителя импульсов подключены к первому входу управления блока, первый управляющий вход пятого коммутатора подключен к выходу четвертого элемента И, второй управляющий вход - к выходу пятого элемента И, являющемуся четвертым выходом блока, третий управляющий вход - к выходу шестого элемента И, служащему пятым выходом блока, четвертый управляющий вход - к выходу седьмого элемента И, второй вход блока подключен к первому информационному входу пятого коммутатора, а третий вход блока - к второму информационному входу пятого коммутатора, пятый выход распределителя импульсов связан с первым выходом блока, первый выход пятого коммутатора соединен с шестым выходом блока, седьмой выход блока связан с вторым выходом пятого коммутатора.

7. Устройство по п. 6, о т л и ч а ю щ е- е с я тем, что пятый коммутатор содержит аналоговые элементы коммутации, с пятого по восьмой входы управления пятого и шестого аналоговых элементов коммутации подключены соответственно к первому и второму входам управления пятого коммутатора, информационные входы - к пятому входу пятого коммутатора, информационные входы седьмого и восьмого аналоговых элементов коммутации соединены с шестым входом пятого коммутатора, входы управления подключены соответственно к третьему и четвертому входам пятого коммутатора, первый выход пятого коммутатора соединен с выходами пятого и седьмого аналоговых элементов коммутации, а второй выход - с выходами шестого и восьмого аналоговых элементов коммутации.

Ј М0

| название | год | авторы | номер документа |

|---|---|---|---|

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

| Устройство регистрации энергетических параметров | 1987 |

|

SU1571395A1 |

| Устройство для автоматического регулирования температуры | 1988 |

|

SU1645945A1 |

| Тренажер для обучения сварщиков | 1986 |

|

SU1441446A1 |

| Тренажер сварщика | 1984 |

|

SU1217151A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1683046A1 |

| Устройство для автоматического контроля системы управления тиристорным преобразователем | 1988 |

|

SU1613372A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1383416A1 |

| СИСТЕМА ПРОГРАММНОГО УПРАВЛЕНИЯ СБОРОЧНЫМ УСТРОЙСТВОМ | 1991 |

|

RU2029335C1 |

| ТРЕНАЖЕР ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ КОРАБЕЛЬНЫХ ПАССИВНЫХ РАДИОЛОКАЦИОННЫХ СИСТЕМ | 1989 |

|

SU1841104A1 |

2-гпф

Z989Ј9l

Фив. 5

i

УпрА

ч/TV

v А

ъ

s§

8$

ч

J

/ t V 4 l I t

0 Ю

fc

15

4

I

«ъ

1

4i

I

I

Ьв.

h(t)

еh,(t)

оФаз.W

Фиг. 11

t

КС

Я&,

и

UdblX.Z6

О

(t)

зн

г Г

71

Г Ч

$5&

Рае. 12

72

73

Фиг. /J

Фиг. 15

м

JUULMIPJUL t

Фаз. Л

Фиг. 1в

Т

tinp.5

Фаз. 19

Фиг. 22

ynft1 Фие.21

dd

Фиг. 26

Зиг.27

Uftt/m.

вых.

I

,

Фиг.28

/V

i/

i I I I I I I I I I I I I

IP

lp

z

4

I

5

Li

Д

J II L

I

ri

n

n

u

.23

НЛп

Ы

П- J4

/W

2

.J

Фиг. 3

+Иггит

Kttt

yiSZ

Редактор В. Дан ко

Фиг. 32

Составитель В. Воронков

Техред М.МоргенталКорректор М. Максимишинец

128 диск. 512 Зисн.

20Ь8 8исн.

У пр. 5

Ct

| Устройство для отображения аксонометрических проекций на экране запоминающей электронно-лучевой трубки | 1980 |

|

SU963081A1 |

| кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1991-09-07—Публикация

1988-12-12—Подача