Изобретение относится к аналоговой вычислительной техникб. и может быть использовано при построении раличных устройств автоматики и радиоэлектроники,

Цель изобретения - упрощение и повышение быстродействия.

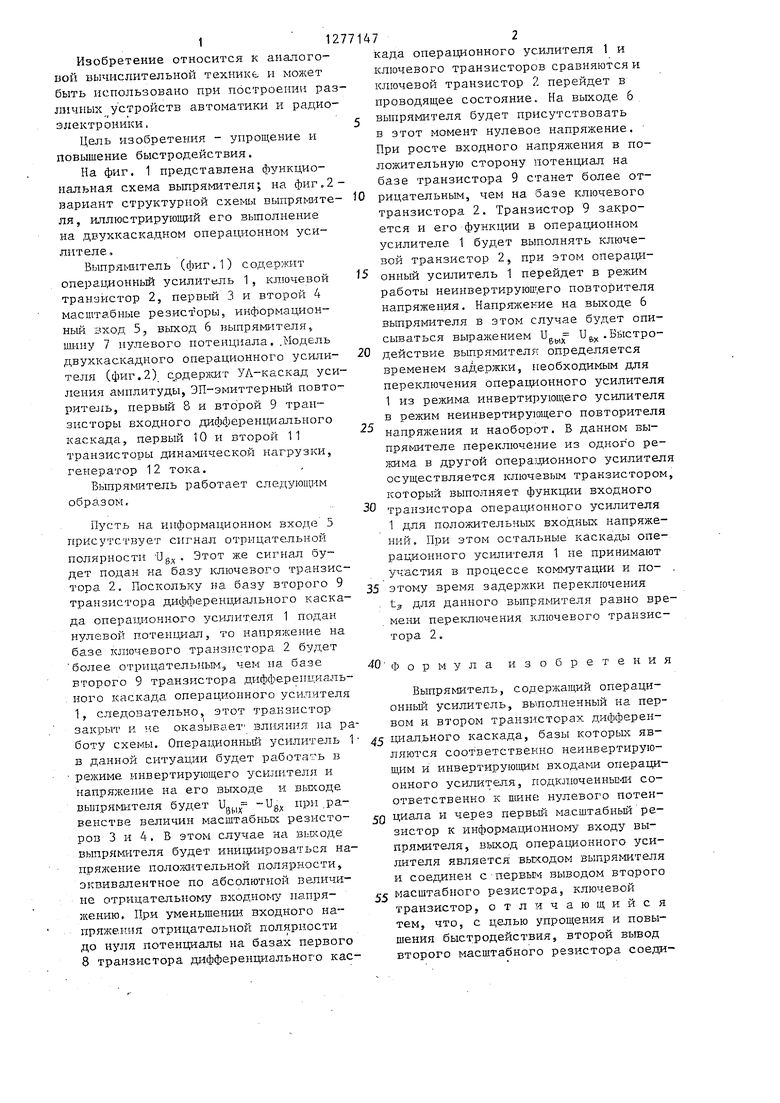

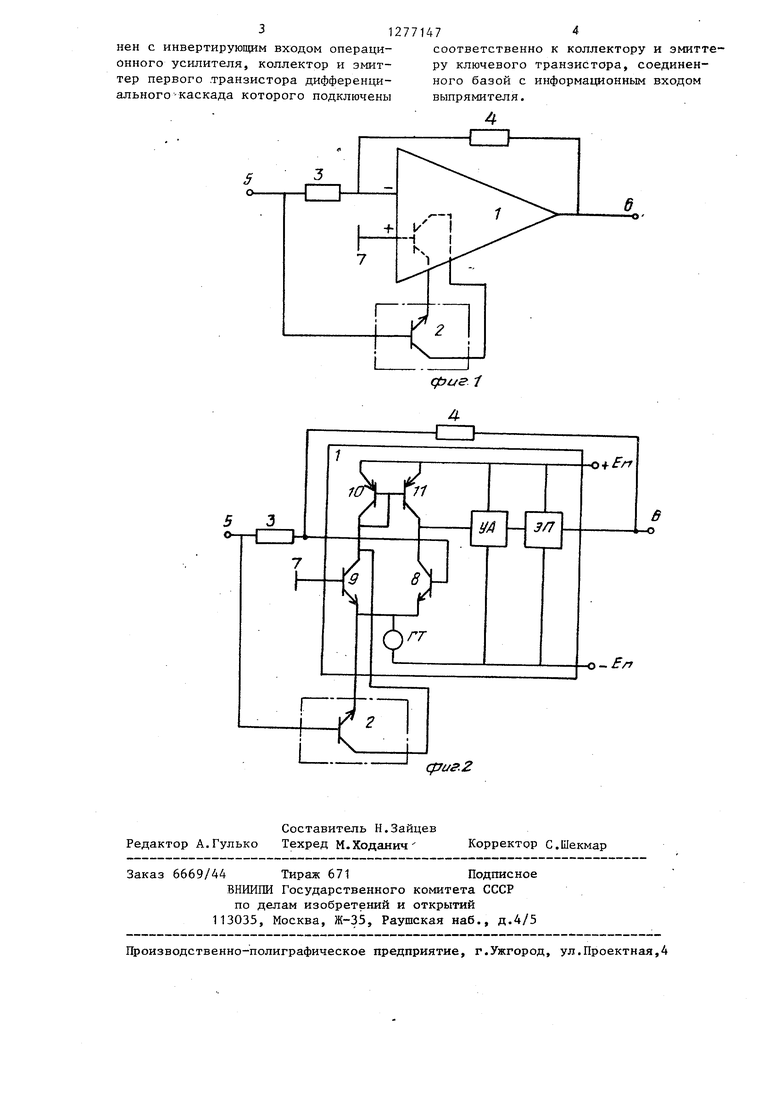

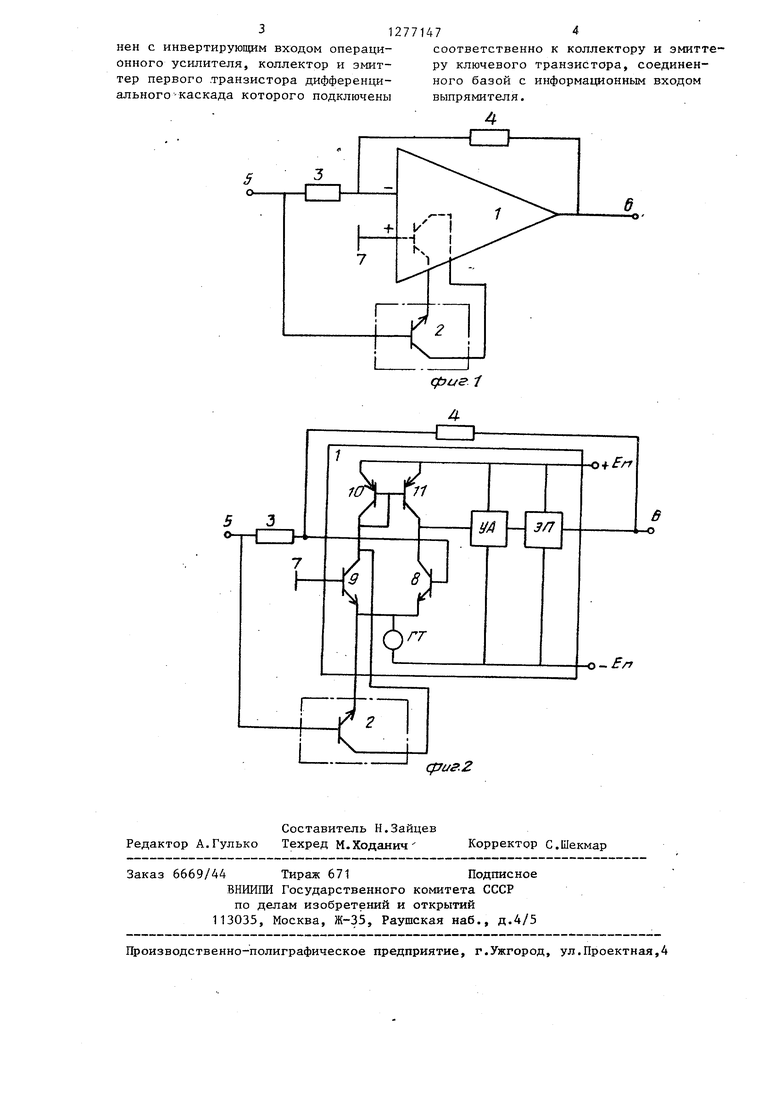

На фиг. 1 представлена функциональная схема вьшрямителя; на фиг.2 вариант структурной схемы выпpя DrIтe ля, иллюстрирующий его выполнение на двухкаскадном операционном усилителе,

Выпряш1тель (фиг,1) содержит операционный усилитель 1, ключевой транзистор 2, первый 3 и второй 4 масштабные резисторы, информационный вход 5, выход 6 выпрямителя, Ш1-1НУ 7 нулевого потенциала. .Модель двухкаскадного операционного усилителя (фиг,2) срдержит УЛ-каскад усиления амплитуды, ЭП-эмиттерный повторитель, первый 8 и второй 9 транзисторы входного дифференциального каскада, первый 10 и второй 11 транзисторы динaмIiчecкoй нагрузки, генератор 12 тока.

Выпрямитель работает следующим образом.

Пусть на информационном входе 5 присутствует сигнал отрицательной

полярности U

8л

Этот же сигнал бует подан на базу ключевого транзисора 2. Поскольку на базу второго 9 ранзистора дифференциального каскаа операционного усилителя 1 подан нулевой noTBHU iari, то напряжение на базе ключевого транзистора 2 будет

более отрицательным, чем на базе второго 9 транзистора дифферендяального каскада операционного усилителя 1, следовательно, этот транзистор закрыт и не оказывает влияния на работу схемы. Операцнонньш усилитель 1 в данной ситуации будет работа ;: ь в

режиме инвертирующего усшш.теля и напряжение на его выходе и вькоде выпря№1теля будет и„,, -U,,.. при раt)I A

венстве величин масщтабных резисторов 3 и 4. В этом случае на вьпаэде выпрямителя будет инихщироваться напряжение пололагтельной полярности, эквивалентное по абсолютной вепичи- не отршдательному входное/ напряжению При уменьшении входного на- пряжек.ия отрицательной полярности до нуля потенциалы на базах первого 8 транзистора дифференциального кас

5

када операционного усилителя 1 и ключевого транзисторов сравняются и ключевой транзистор 2 перейдет в проводящее состояние. На выходе 6 выпрямителя будет присутствовать в этот момент нулевое напряжение. При росте входного напряжения в положительную сторону потенциал на базе транзистора 9 станет более отрицательным, чем на базе ключевого транзистора 2. Транзистор 9 закроется и его функции в операционном усилителе 1 будет выполнять ключевой транзистор 2, при этом операьщ- онный усилитель 1 перейдет в режим работы неинвертирующего повторителя напряжения. Напряжение на выходе 6 выпрямителя в этом случае будет опи0

5

0

5

сываться выражением

и,.г

и„ .Быстродействие выпрямителя определяется временем задержки, необходимым для переключения операционного усилителя 1 из режима инвертирующего усилителя в режим неинвертирующего повторителя напряжения и наоборот. В данном вы- пpя штeлe переключение из одног о режима в другой оператдионного усилителя осуществляется ключевым транзистором, который выполняет функции входного транзистора операционного усилителя 1 для положительных входных напряжений. При этом остальные каскады операционного усилителя 1 не принимают участия в процессе коммутации и по- . этому время задержки переключения tj для данного выпрямителя равно времени переключения ключевого транзистора 2.

0 ф о р м у л а изобретени

Выпрямитель, содержащий операционный усилитель, выполненный на первом и втором транзисторах дифферен45 цнального каскада, базы которых являются соответственно неинвертирую- щцм и инвертирующим входами операционного усилителя, подключенньпф соответственно к йнне нулевого потен50 циала и через первый масштабный резистор к информационному входу выпрямителя, выход операционного усилителя является выходом выпрямителя и соединен с первм выводом второго

масштабного резистора, ключевой транзистор, отличающийся тем, что, с целью упрощения и повышения быстродействия, второй вывод второго масщтабного резистора соеди31277147

нен с инвертирующим входом операци- соответственно к коллектору и эмитте- онного усилителя, коллектор и эмит- РУ ключевого транзистора, соединен- тер первого .транзистора дифференци- него базой с информационным входом ального-каскада которого подключены выпрямителя.

qbue 1

1 (jjuff

| название | год | авторы | номер документа |

|---|---|---|---|

| Ограничитель | 1984 |

|

SU1267444A1 |

| Функциональный преобразователь | 1982 |

|

SU1111181A1 |

| Усилитель-ограничитель | 1982 |

|

SU1092526A1 |

| СИНХРОННЫЙ ГЕНЕРАТОР С ПРЕЦИЗИОННОЙ СИСТЕМОЙ УПРАВЛЕНИЯ | 2005 |

|

RU2295192C1 |

| Электронный коммутатор | 1984 |

|

SU1188874A2 |

| Электронный коммутатор | 1979 |

|

SU801249A1 |

| Логарифмический преобразователь | 1984 |

|

SU1160446A1 |

| ЭЛЕКТРОМЕТРИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ТОКА | 2005 |

|

RU2277294C1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| Интегратор | 1985 |

|

SU1287195A1 |

Изобретение относится к области аналоговой вычислительной техники и может быть использовано при построении различных устройств автоматики и радиоэлектроники. Цель изобретения - упрощение и повьшение быстродействия. Быстродействие вьтрямителя определяется временем задержки, необходимым для переключения операционного усилителя из режима инвертирующего усилителя в режим неинвертирующего повторителя напряжения и наоборот. Переключение осуществляется за счет соответствующего включения ключевого транзистора. 2 ил. (Л

Составитель Н.Зайцев Редактор А.Гулько Техред М.Ходанич

Заказ 6669/44 Тираж 671Подписное

БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Алексенко А.Г., Коломбет Е.А | |||

| и Стародуб Г.И | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М.: Радио и связь, 1981, с.106 | |||

| Шило В.Л | |||

| Линейные интегральные схемы | |||

| М.: Советское радио, 1979, с.184, рис.4.22,д. | |||

Авторы

Даты

1986-12-15—Публикация

1984-12-26—Подача