(54) АНАЛОГОВОЕ ЗАПОМИНМ)ЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Аналоговое запоминающее устройство | 1986 |

|

SU1325566A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Усилитель | 1988 |

|

SU1720146A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU826565A1 |

| Коммутатор аналоговых сигналов | 1981 |

|

SU978345A1 |

| Преобразователь напряжения в код Грея | 1984 |

|

SU1182687A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Высоковольтный измеритель пробивных напряжений транзисторов | 1977 |

|

SU693277A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1152040A1 |

Изобретение относится к вычисли- тельной технике И может быть использовано в аналоговых и аналого-цифровых вычислительных устройствах.

Известно аналоговое запоминающее устройство разомкнутого типа, содержащее повторитель напряжения, усилитель, накопительный элемент и четыре ключа. В режиме выборки устройство не охвачено отрицательной обратной связью и поэтому характеризуется высоким быстродействием 1.

Недостатком устройства является низкая точность из-за отсутствия компенсации напряжения смещения нуля усилителя и большой коммутационной помехи, вызванной прониканием на накопительный элемент паразитного заряда из цепи управления ключом при переходе устройства из режима выборки в режим хранения.

Наиболее близким по технической сущности к предлагаемому является аналоговое запоминающее устройство, содержащее повторитель напряжения, вход которого соединен с выходом и входом соответственно первого и второго ключей, причем вход первого ключа является входом устройства, а выход второго ключа является выходом

устройства, выход повторителя напряжения соединен с накопительным элементом,например, одной обкладкой конденсатора, другая обкладка которого подключена к инвертирующему входу усилителя и через третий ключ к выходу устройства и выходу усилителя, неинвертирующий вход которбго соединен с шиной нулевого потенциа10ла С 2 .

В этом устройстве устранено влияние напряжения смещения нуля усилителя на точность устройства. Однако, поскольку переход от режима вы15борки к режиму хранения сопровождается изменением выходного напряжения от нуля до напряжения на входе устройства, то имеет место прохождение паразитного заряда через емкость

20 закрытого третьего ключа на накопительный элемент. Кроме того, в режиме хранения третий ключ находится под ;напряжением, близким к выходному напряжению, и накопительный эле25мент разряжается током, протекающим через сопротивление закрытого ключа. Поскольку для увеличения быстродействия устройства емкость накопительного элемента стремятся умень30шить, то составляющая погрешности.

вызванная конечным сопротивлением третьего ключа и его емкостью в закрытом состоянии, возрастает и становится доминирующей в устройствах, рассчитанных на максимальное быстро™ действие.

. Цель изобретения - повышение точности устройства.

Поставленная цель достигается тем что в аналоговое запоминающее устройство,, содержащее повторитель напряжения, вход которого соединен с выходом и входом соответственно первого и второго ключейf причем вход первого клича является входом устройства, а выход второго ктаоча является выходом устройства, выход пов торителя напряжения соединен с накопительнья- элементом., например, с одной обкладкой конденсатора, другая об-сладка которого соединена с входом третьего к.шоча, введен пе рО1;лю1аемый усилитель,- первый инверТ1чр;ло1г1ий вход и выход которого соединены с выходом второго ключа, первый неинвертирующий вход переключаемого усилителя соединен с входог. повторителя напряжения, второй инвертирующий вход - с входом третьего кл:оча, второй нершвертирующий вход с выходом третьего ключа и шиной нулевого потенциала.

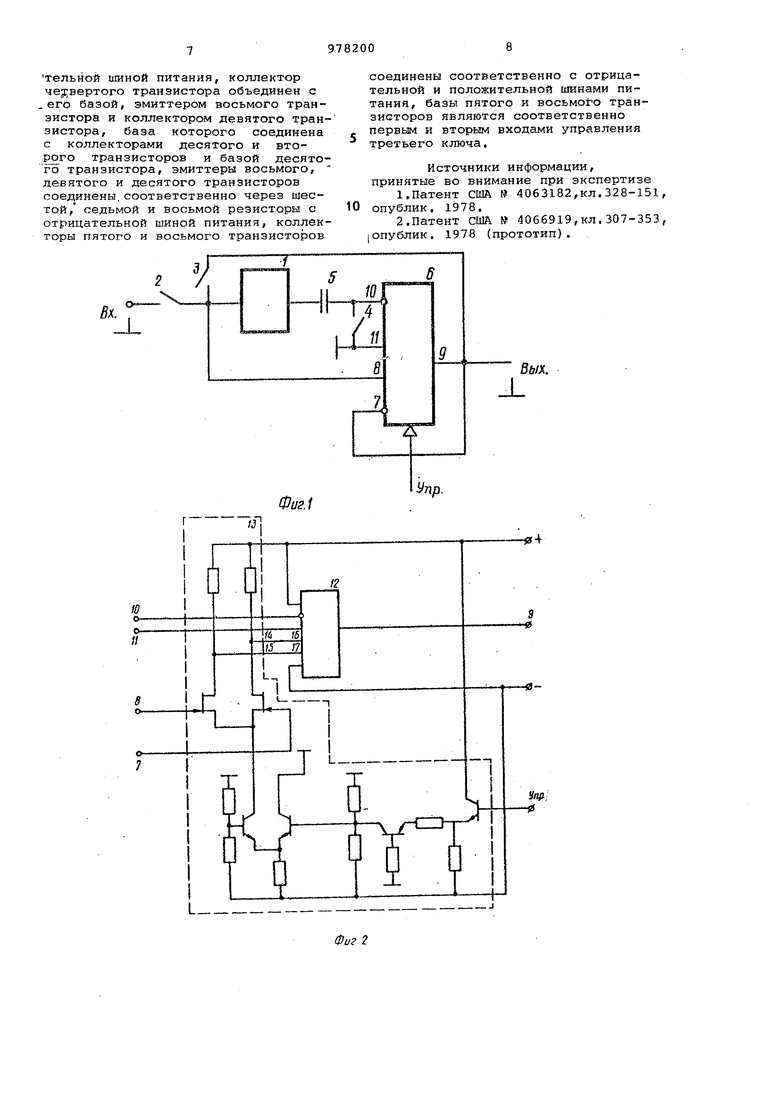

Переключаемый усилитель содержит операционный усилитель и управляемый дифференциальный каскад, инвертирую™ ГГкй и ь:еинвертирую ций входы которого являются сООТветственно первыгл инвертирующим и первьм неинвертирующим входами переключаемого yci-шителя первый и второй выходы управляемого дифференциального каскада соединены соответственно с первж. и вторым выходами входного каскада операционного усилителя, инвертирующ.ий вход, неинвертир тащий вход и выход которого являются соответственно вторыгл инвертиру1оир-1м входом, вторым неинвертируюш.им входом и выходом переключаемого усилителя,

Третий ключ содержит десять транзисторов и восемь резисторов,, первые выводы первого и второго резисторов объединены и являются входом третьего ключа, вторые выводы первого и второго резисторов соединены соответственно с эмиттерами первого и второго транзисторов, базы которых соединены соответственно с базами третьего и четвертого транзисторов, эмиттеры которых соединены с шиной нулевого потенциала, коллектор треть его транзистора объединен с его базой, эмиттером пятого транзистора и коллектором шестого транзистора, база которого соединена с коллекторами седьмого и первого транзисторов и базой седьмого транзистора, эмиттеры пятого, шестого и седьмого

транзисторов соединены соответственно через третий, четвертый и пятый резисторы с положительной шиной питания, коллектор четвертого транзистора объединен с его базой, эмитS тером восьмого транзистора и коллектором девятого транзистора, база которого соединена с коллекторами десятого и второго транзисторов и базой десятого транзистора, эмитте10 , ры восьмого, девятого и десятого

транзисторов соединены соответственно через шестой, седьмой и восьмой резисторы с отрицательной шиной питания, коллекторы пятого и восьмого

15 транзисторов соединена соответственно с отрицательной и положительной шинами питания, базе пятого и восьмого транзисторов являются соответственно первым и вторы.1 входами

Q управления третьего ключа,

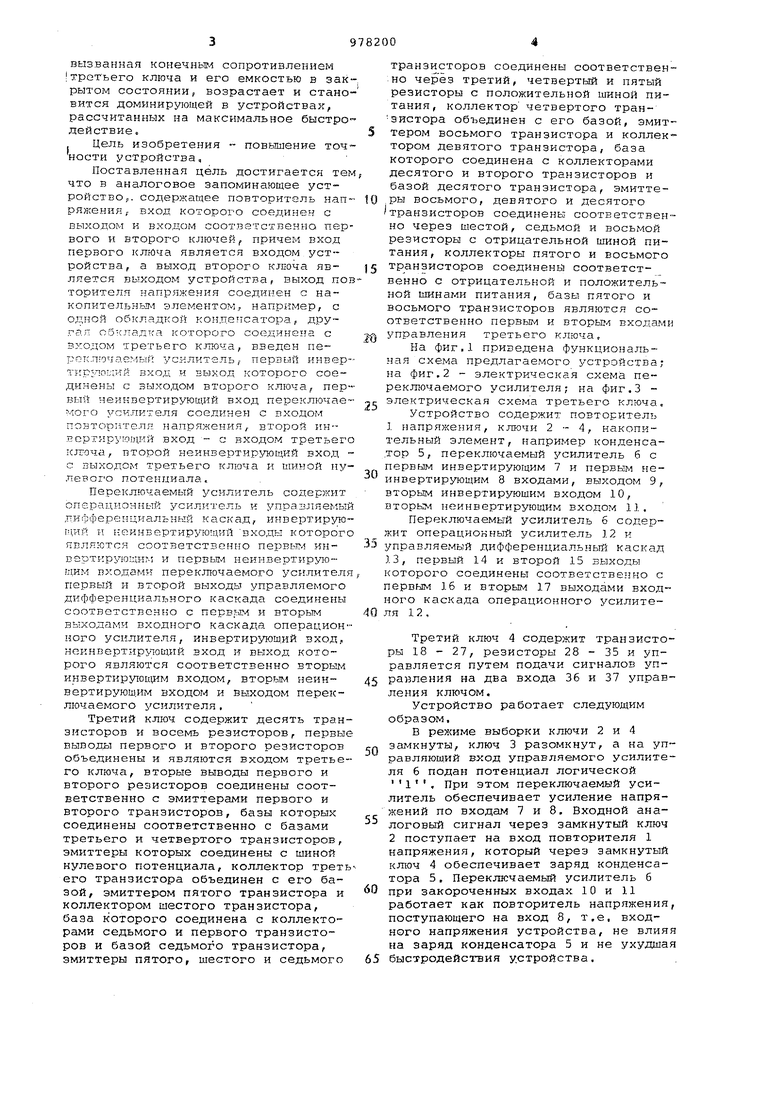

На фиг,1 приведена функциональная схема предлагаемого устройства; на фиг,2 - электрическая схема переключаемого усилителя; на фиг.3 тг электрическая схема третьего ключа.

Устройство содержит повторитель 1 напряжения, ключи 2-4, накопительный элемент, например конденсатор 5, переключаемый усилитель б с первым инвертирующим 7 и первым неинвертирующим 8 входами, выходом 9, вторым инвертирующим входом 10, вторым неинвертирующим входом 11,

Переключаемый усилитель б содержит операционный усилитель 12 и

35 управляемый дифференциальный каскад

13, первый 14 и второй 15 выходы которого соединены соответственно с первым 16 и вторым 17 выходами входного каскада операционного усилителя 12,

Третий ключ 4 содержит транзисторы 18 - 27, резисторы 28 - 35 и управляется путем подачи сигналов управления на два входа 36 и 37 управления ключом.

Устройство работает следующим образом,

В режиме выборки ключи 2 и 4 замкнуты, ключ 3 разомкнут, а на управляющий вход управляемого усилителя 6 подан потенциал логической 1 . При этом переключаемый усилитель обеспечивает усиление напряжений по входам 7 и 8, Входной аналоговый сигнал через замкнутый ключ 2 поступает на вход повторителя 1 напряжения, который через замкнутый ключ 4 обеспечивает заряд конденсатора 5. Переключаемый усилитель 6

60 при закороченных входах 10 и 11

работает как повторитель напряжения, поступающего на вход 8, т.е. входного напряжения устройства, не влияя на заряд конденсатора 5 и не ухудшая

65 быстродействия устройства.

Для уменьшения времени заряда конденсатора 5 до величины входного напряжения в качестве повторителя 1 напряжения может быть использован эмиттерный повторитель, а третий ключ 4 может быть выполнен по схеме представленной на фиг.З. В этом случае в режиме вьэборки на первый вход 36 управления ключа подается потенциал +1,5В, а на второй вход 37 управления -1,5В, Тогда в зависимости от полярности тока заряда, этот ток протекает либо через верхнюю половину схемы ключа (фиг.З), т.е. через резистор 28 и транзисторы 19, 18, 22 и 23 к шине нулевого потенциала, либо через нижнюю половину схемы, Характерной особенность предлагаемой схемы ключа является т что при идентичных транзисторах 19, и 18, 22, напряжение на эмиттере ;транзистора 19 (при протекании тока через верхнюю половину схемы) близ;ко к нулю, а следовательно, сопротивление открытого ключа равно сопротивлению резистора 28 и 29, которое можно уменьшить до единиц ом. Это на порядок меньше, чем у обычны ключей на полевых транзисторах.

При переходе в режим хранения на управляющий вход 36 ключа подается -1,5В, на вход 37 +1,5В, при это ключ 4 закрывается. На управляющий вход переключаемого усилителя б подается потенциал логического О, при котором управляемый дифференциальный каскад 13 отключается и переключаемый усилитель б обеспечивает усиление напряжений только по входам 10 и 11. Ключ 2 в режиме хранения закрыт, а ключ 3 открыт. При этом на выходе устройства остаеся напряжение,равное входному напряжению в момент перехода устройства от режима выборки в режим хранения .

На точность предлагаемого устройства не влияет напряжение смещения нуля повторителя 1 напряжения и отличие его коэффициента передачи от единицы, поскольку влияние этих факторов ослаблено в К раз, где К коэффициент усиления операционного усилителя 12.

Хотя напряжение смещения нуля переключаемого усилителя б в предлагаемом устройстве не компенсируется при малой емкости конденсатора 5 точность предлагаемого устройства оказывается выше точности прототипа а при выполнении третьего ключа 4 по схеме, показанной на фиг.З, увеличивается по сравнению с прототипом и быстродействие.

Формула изобретения

напряжения, вход которого соединен с выходом и входом соответственно первого и второго ключей, причем вх,од первого ключа -является входом устройства, а выход второго ключа является выходом устройства, выход повторителя напряжения соединен с накопительным элементом, например одной обкладкой конденсатора, другая обкладка которого соединена с входом третьего ключа, отличающееся тем, что, с целью увеличения точности устройства, в него введен переключаемый усилитель,первый инвертирующий вход и выход ко5торого соединены с выходом второго ключа, первый неинвертирующий вход переключаемого усилителя соединен с входом повторителя напряжения, второй инвертирующий вход - с входом третьего ключа, второй неинвертируто0щий вход - с выходом третьего ключа и шиной нулевого потенциала.

5 выходами входного каскалп операционного усилителя, инвертирующий вход, неинвертирующий вход и выход которого являются соответственно вторым инвертирующим входом, вторым неин0вертирующим входом и выходом переключаемого усилителя.

3,УстройствЬ по п. 1, о т л ичаюш. ееся тем, что, с целью увеличения быстродействия устройства , третий ключ содержит десять

5 транзисторов и восемь резисторов, первые выводы первого и второго резисторов объединены и являются входом третьего ключа, вторые выводы первого и второго резисторов соеди0нены соответственно с эмиттерами первого и второго транзисторов, базы которых соединены соответственно с базами третьего и четвертого транзисторов, эмиттеры которых сое5динены, с шиной нулевого потенциала, коллектор третьего транзистора объединен с его базой, эмиттером пятого транзистора и коллектором шестого транзистора, база которого соедине0на с коллекторами седьмого и первого транзисторов и базой седьмого транзистора, эмиттеры пятого, шестого

и седьмого транзисторов соединены соответственно через третий, чет5вертый и пятый резисторы с положительной шиной питания, коллектор четвертого транзистора объединен с .его базой, эмиттером восьмого транзистора и коллектором девятого транзистора, база которого соединена с коллекторами десятого и втоР ого транзисторов и базой десятого транзистора, эмиттеры восьмого, девятого и десятого транзисторов соед инены. соответственно через шестой, седьмой и восьмой резисторы с отрицательной шиной питания, коллекторы пятого и восьмого транзисторов

Х.

™L

Фиг.

соединены соответственно с отрицательной и положительной шинами питания, базы пятого и восьмого транзисторов являются соответственно первым и вторым входами управления третьего ключа.

Источники информации, принятые во внимание при экспертизе

2,Патент США № 4066919,кл,307-353, |опублик, 1978 (прототип).

Упр.

dO 28

Авторы

Даты

1982-11-30—Публикация

1981-01-30—Подача