Изобретение относится к вычислн- елл.-ной технике и может быть испольовано при решении задач гармоничесого анализа;, где необходимо произвоить отработку сигнала в реальном асштабе времени.

Целью изобретения является новыше- ние быстродействия процессора.

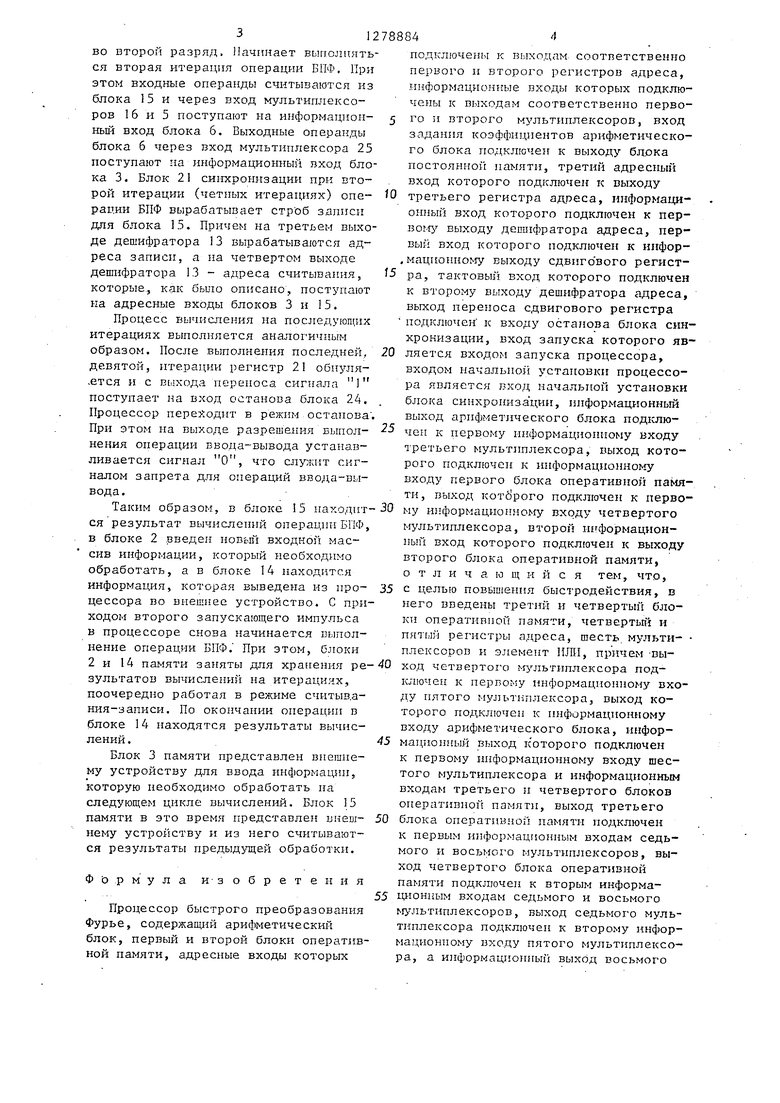

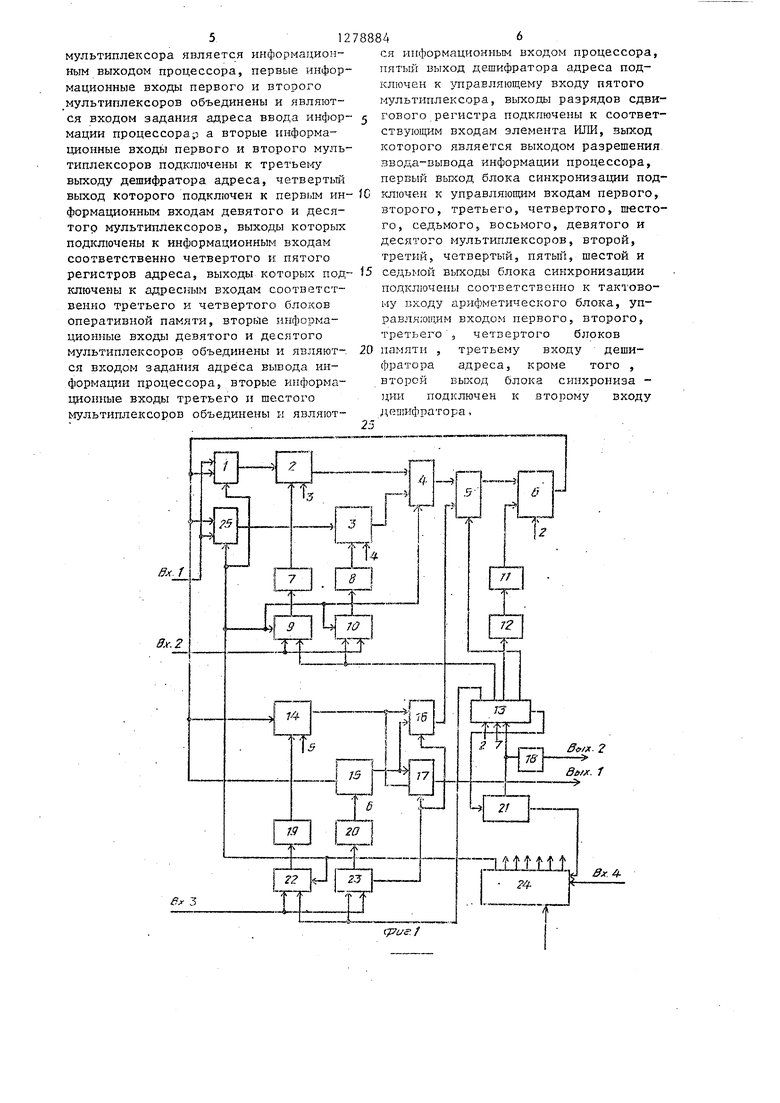

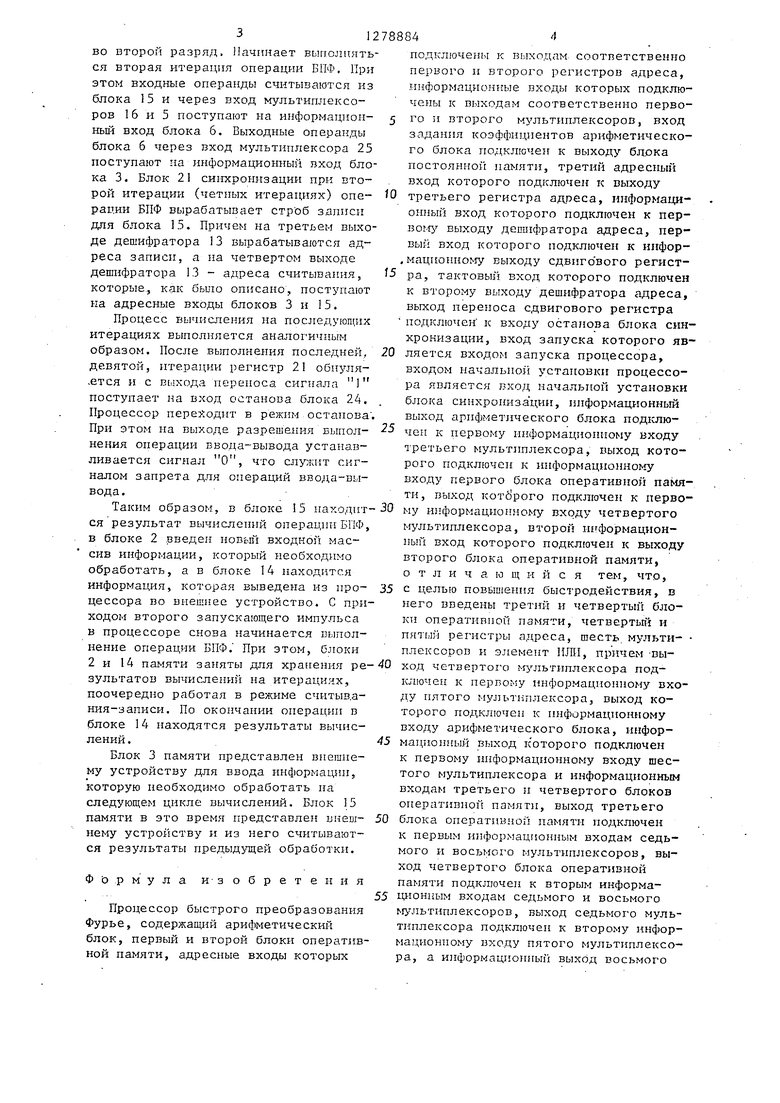

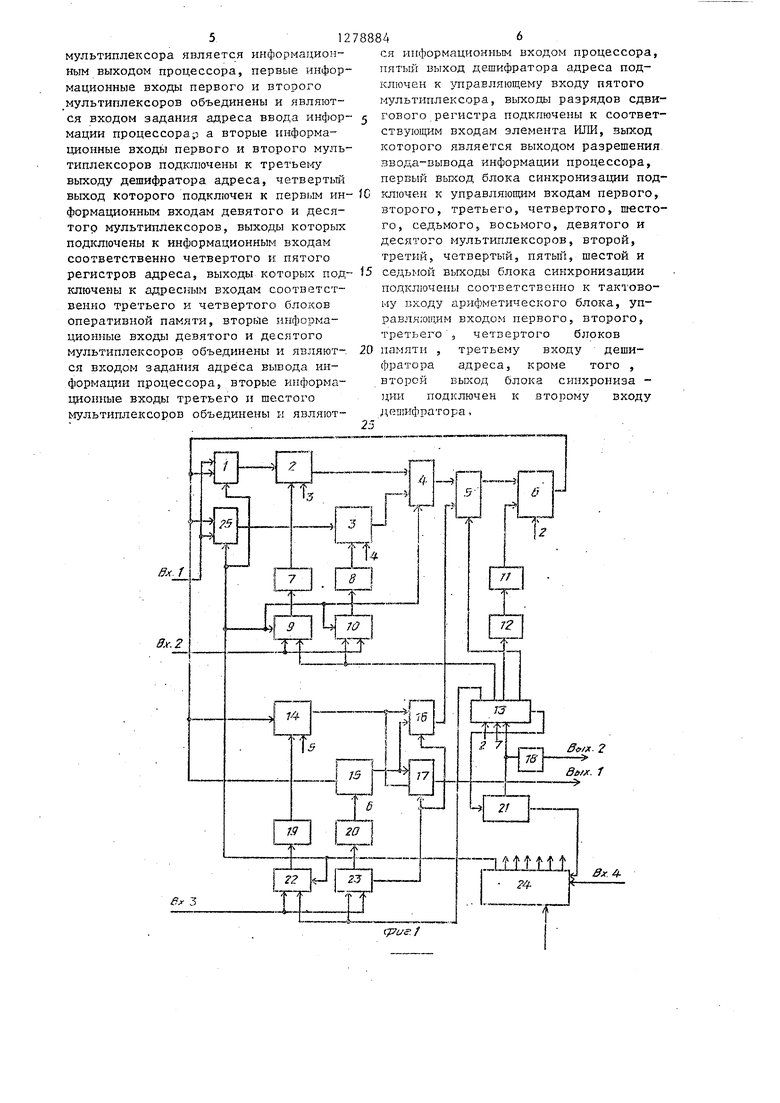

На фиг., представлена функциональная скема процессора; н.а фиг-, 2 - временная дмаграм-ia работы процессора дл51К 512 точек,

Процессор БПФ содержит ьгультиплек- сор 15 блоки 2 и 3 оперативной nat-iH- ти, кул1/ иплексоры 4 и 5, арифетичес- кий блок 6, регистры 7 и 8 адреса -мультиплексоры 9 и 0, блок- 1 нос- тояь ной памяти, регистр 12 адреса, блок 3 дешифратора адреса, блоки 14 и 15 оперативной памяти, мультиплексоры 1G и Г/, э-темеит 18, регистры 19 и 20 адреса, (итерацион- ньш) сдвигоБый реги.стр 21, мультиплексоры 22 и 23, блок 24 с-ЕП1хрониза- цни и мультиплексор 25,

PaccMOTpiiM работу процессора на примере обработки массива д/1иной N 512 течек,

В исходном состоянии все регистры .обкуленЫэ на первом выходе блока 24 устапавлипается уровень 1, при этом в мультиплексорах 1,4,9,10,16, 17,.22,23 и 25 будут открыты для про- хо/кдения информации первые вход;--. На пятом выходе де1ш-:фратора 13 установится уровень 1 и при это. в мультиплексоре 5 б удет открыт первый вход. На выходе разрешения операций ввода-вьшода установится уровень 0, что является сигнаггом запрета вьтол- иения этих оиераци.й для внешних устройств.

С приходом залуекающего импульса на вход .запуска блока 24, блок 24 синхронизации начинает вырабатывать такто.иые сигн-алы для всех устройств, При этом в первый разряд регистра 21 .сдвига устанавливается 1 и па выходе, разрешения выполнения операции ввода-вывода устанавливается сигнал что разрешает внешним устройст V

вам выполнетнге операций в.вода-вывода. Массив чисел, которы1 ): необходимо обработать, поступает на вход процессора и далее через вход г-гультинлексора 1 на вход блока 2. На адресный вход , блока 2 чер-23 вход мультиплексора 9 и регистр 7 ноступ,ают адреса, кото

5

0

5

0

5

0

5

0

5

рые вырабатывает внешнее устройство синхронно с входной информацией и подает на нервый адресньш вход процессора. Одновременно с вводом информации в процессоре выполняется операция обработки информации (операция БПФ). При этом дешифратор 13 вырабатывает на третьем выходе адреса операндов, по которым производится считглвание информации из блока 3. Через вход мультиплексора 10 адреса поступают на регистр 8 и далее - на адресный вход блока 3, Информация с выхода блока 3 через входы мульти- п.пексоров 4 и 5 поступает на инфор- мационн)Ш вход блока 6. На первом выходе дешифратора 13 формируются адреса весовых коэффициентов, которые занисывагатся в регистр 12.

С выхода блока 11 считываются весовые )ициенты, которые синхронно с входными операндами поступают . на вход зада1н я коэффициентов блока 5. В блоке б выполняются базовые операции алгоритмов БПФ. Результаты вы- ч.ислений с выхода блока 6 поступают на входь блоков 14 и 15. При выполнении первой итерации БПФ (нечетных итера;.иях) блок синхронизации выра- батывает строб записи для блока 15.

На четвертом выходе дешифратора 13 вырабатываются адреса, по которым производится запись результатов базовой операции в блок 15, Они поступают на адресный вход блока 15 через вход мультиплексора 22 и регистр 30. Одновременно с онерациями ввода информации и обработки в процессоре выполняется операция вывода информации, которая была обработана на предыдущем цикле вычислений. При этом внешнее устройство выставляет на второй адресный вход процессора адреса, по которым необходимо считать информа- трш. Через вход мультиплексора 22 адреса поступают на регистр 19- и далее на адресный вход блока 14. Из блока 14 считывается информация, ко-. торая через вход мультиплексора 17 поступает на информационны выход нроцессора и далее во внешнее устройство. После выполнения первой итерации на выходе дешифратора 3 устанавливается уровень О и нри этом в мультиплексоре 5 открывается второй вход. На втором выходе дешифратора 13 фop шpyeтcя сигнал, по которому происходит сдвиг 1 в регистре 21

во второй разряд. Начинает выполняться вторая итерация операции БПФ. При этом входные операнды считываются из блока 15 и через вход мультиплексоров 16 и 5 поступают па информациоп- ньш вход блока 6. Выходпые операнды блока б через вход мультиплексора 25 поступают на информационный вход блока 3. Блок 21 синхронизации при второй итерации (четных итерациях) операции БПФ вырабатывает стр об записи для блока 15. Причем на третьем выходе дешифратора 13 вырабатываются адреса записи, а на четвертом выходе дешифратора 13 - адреса считывания, которые,, как было описано, поступают на адресные входы блоков 3 и 15.

Процесс вычисления на последующих итерациях выполняется аналогичным образом. После выполнения последней, девятой, итерации регистр 21 обнуля- .ется и с выхода перепоса сигнала 1 поступает на вход останова блока 24. Процессор перез одпт в режим останова При этом на выходе разрешения выполнения онерации ввода-вывода устанавливается сигнал О, что слу;кпт сигналом занрета для операций ввода-вывода.

Таким образом, в блоке 15 находится результат вычислений операции БПФ, в блоке 2 введен новьй входной массив информации, который необходимо обработать, а в блоке 14 находится информация, которая выведена из процессора по внешнее устройство. С приходом второго запускающего импульса в процессоре снова начинается выполнение операции БПФ. При этом, блоки 2 и 14 памяти заняты для храпения результатов вычислений на итерациях, поочередно работая в режиме считыв.а- ния-записи. По окончании онерацрн: в блоке 14 находятся результаты вычислений .

Блок 3 памяти представлен внешнему устройству для ввода информации, которую необходимо обработать на следующем цикле вычислений. Блок 15 памяти в это время представлен внев;- нену устройству и из него считываются результаты предыдущей обработки.

Формула И з обретения

Процессор быстрого преобразования Фурье, содержащий арифметический блок, первый и второй блоки оперативной памяти, адресные входы которых

подключены к выходам соответственно первого и второго регистров адреса, информационные входы которых подключены к выходам соответственно перво- 5 го и второго мультиплексоров, вход задания коэффициентов арифметического блока подключен к выходу блока постоянной памяти, третий адресный вход которого подключен к выходу

третьего регистра адреса, информационный вход которого подключен к пер- во1-г выходу дешифратора адреса, первый вход которого подключен к иифор- .мациопному выходу сдвигового регист5 ра, тактовый вход которого подключен к второму выходу дешифратора адреса, выход переноса сдвигового регистра подключен к входу останова блока синхронизации, вход запуска которого яв0 ляется входом запуска процессора, входом начальпой устаповки процессора является вход начальной установки блока синхронизации, информационный выход арифметического блока подклю-5 чен к первому информационному входу третьего мультиплексора, выход которого подключен к информационному входу первого блока оперативной памяти , выход которого подключен к перво0 му информационному входу четвертого мультиплексора, второй информационный вход которого подключен к выходу второго блока оперативной памяти, отличающийся тем, что,

5 с целью повып1еппя быстродействия, в него введены третий и четвертый блоки оперативной памяти, четвертьш и пятый регистры адреса, шесть, мульти- плексоров и элемепт 1ШП, причем -вы0 ход четвертох о $ льтиплексора подключен к первому информационному входу пятого мультиплексора, выход которого подключен к информационному входу арифметического блока, инфор5 мационнЕ,ш выход к оторого подключен к первому информационному входу шестого мультиплексора и информационным входам третьего и четвертого блоков оперативной памятп, выход третьего

0 блока оперативной памятн подключен к первым информационным входам седьмого и восьмог о мультиплексоров, выход четвертого блока оперативной памяти подключен к вторым информа5 ционным входам седьмого и восьмого м льтиплексоров, выход седьмого мультиплексора подключеп к второму информационному входу пятого мультиплексора, а информациоппы выход восьмого

мультиплексора является информационным выходом процессора, первые информационные входы первого и второго мультиплексоров объединены и являются входом задания адреса ввода информации процессорар а вторые информационные входь первого и второго мультиплексоров подключены к третьему выходу дешифратора адреса, четвертый выход которого подключен к первым информационным входам девятого и деся- тогр мультиплексоров, выходы которых подключены к информационным входам соответственно четвертого и пятого регистров адреса, выходы которых подключены к адресным входам соответственно третьего и четвертого блоков оперативной памяти, вторйе информационные входы девятого и десятого мультиплексоров объединены и являются входом задания адреса вывода информации процессора, вторые информационные входы третьего и шестого мультиплексоров объединены н являются информационным входом процессора, пятый выход дешифратора адреса подключен к управляющеку входу пятого мультиплексора, выходы разрядов сдвигового регистра подключены к соответствующим входам элемента ИЛИ, выход которого является выходом разрешения, ввода-вывода информации процессора, первый выход блока синхронизации подключен к управляющим входам первого, второго, третьего, четвертого, шестого, седьмого, восьмого, девятого и десятого мультиплексоров, второй, третий, четвертый, пятый, шестой и

седьмой выходы блока синхронизации подключены соответственно к тактовому входу арифметического блока, управляющим входом первого, второго, третьего , четвертого блоков

памяти , третьему входу дешифратора адреса, кроме того , второй выход блока синхрониза - ции подключен к второму входу деп1ифратора,

вх.1

вх.2

Итерации

Редактор В.Иванова

Составитель А.Баранов Техред А.Кравчук

Заказ 6841/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий I13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ввод ()

Итерации

Ф(г.2

Корректор О.Луговая

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрого преобразования Фурье | 1983 |

|

SU1119027A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1277135A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1336029A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1987 |

|

SU1444814A1 |

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1983 |

|

SU1133597A1 |

Изобретение относится к вычислительной технике и может быть использовано при решении задач гармоничес- кого анализа, где необходимо производить обработку сигналов в реальном . масштабе времени. Цель изобретения - повышение быстродействия процессора. Поставленная цель достигается тем, что он содержит четыре блока оперативной , блок постоянной памя- ;ти, арифметический блок, десять мультиплексоров, пять регистров адреса, дешифратор адр.еса, элемент ИЛИ, сдвиговый регистр, блок синхронизации и соответствующие связи между узлами процессора. 2 ил. СЛ е g 00 00 00 u

| Устройство для реализации быстрого преобразования фурье | 1975 |

|

SU590750A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Процессор быстрого преобразования Фурье | 1983 |

|

SU1119027A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1984-12-23—Подача