10

11315999

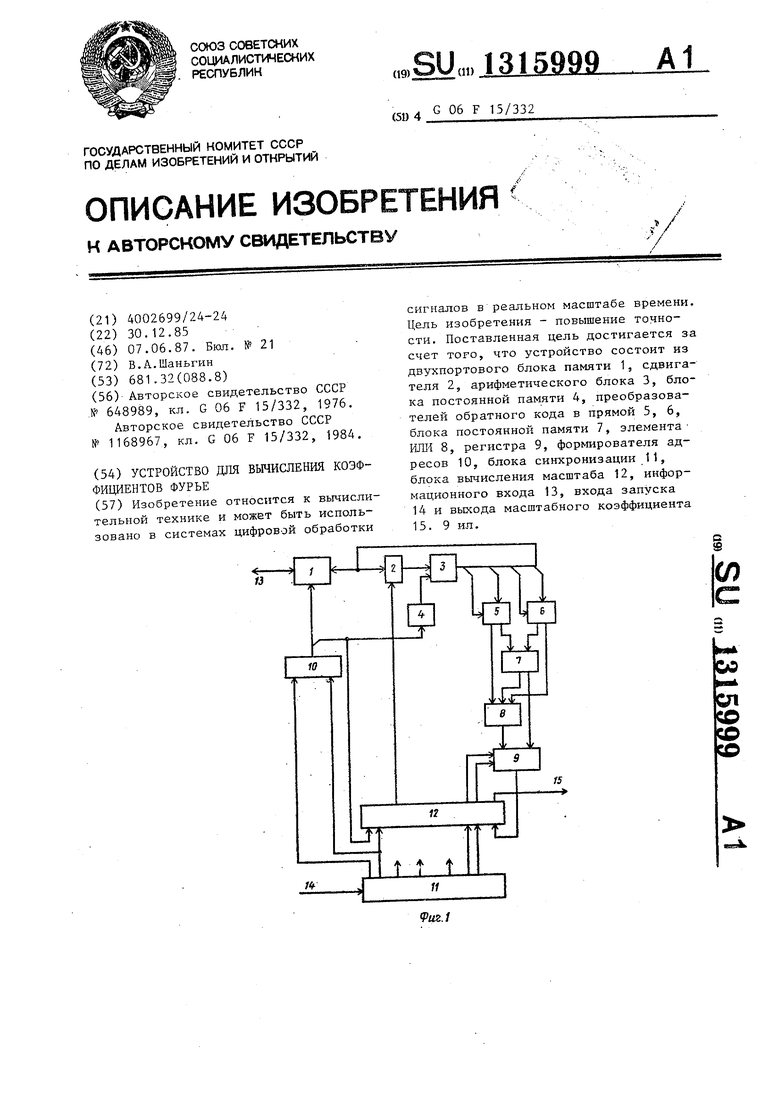

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов в реальном масштабе времени.

Целью изобретения является повышение точности вычислений;

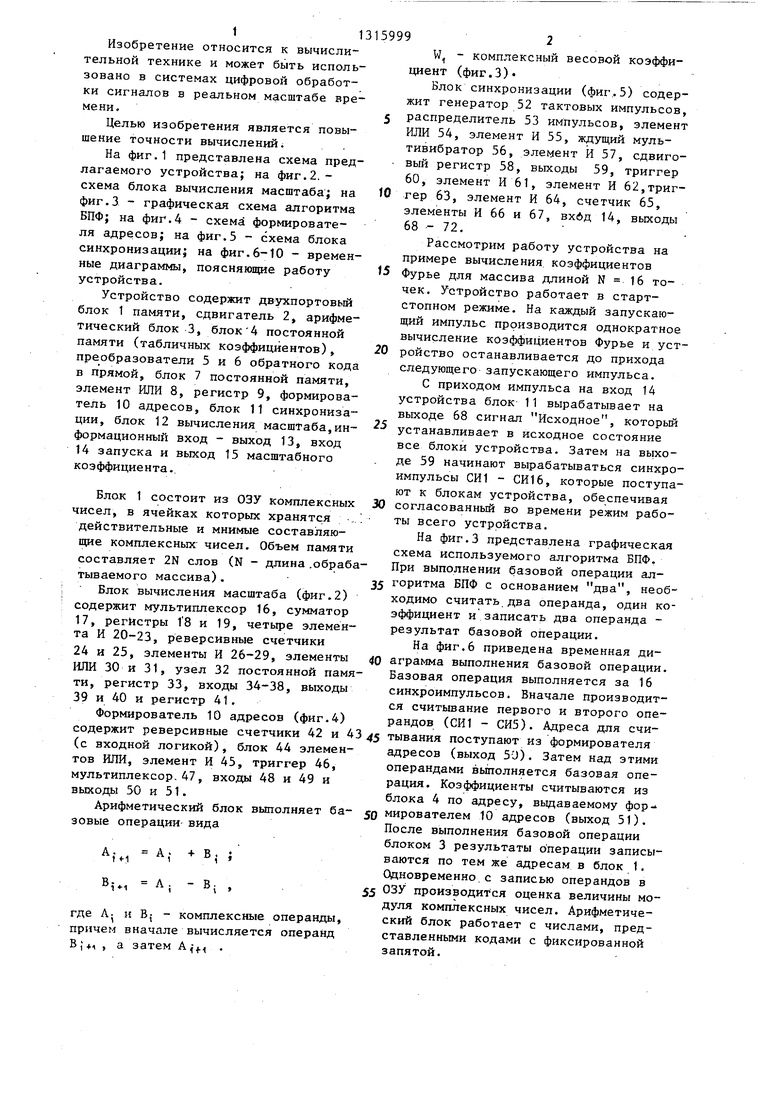

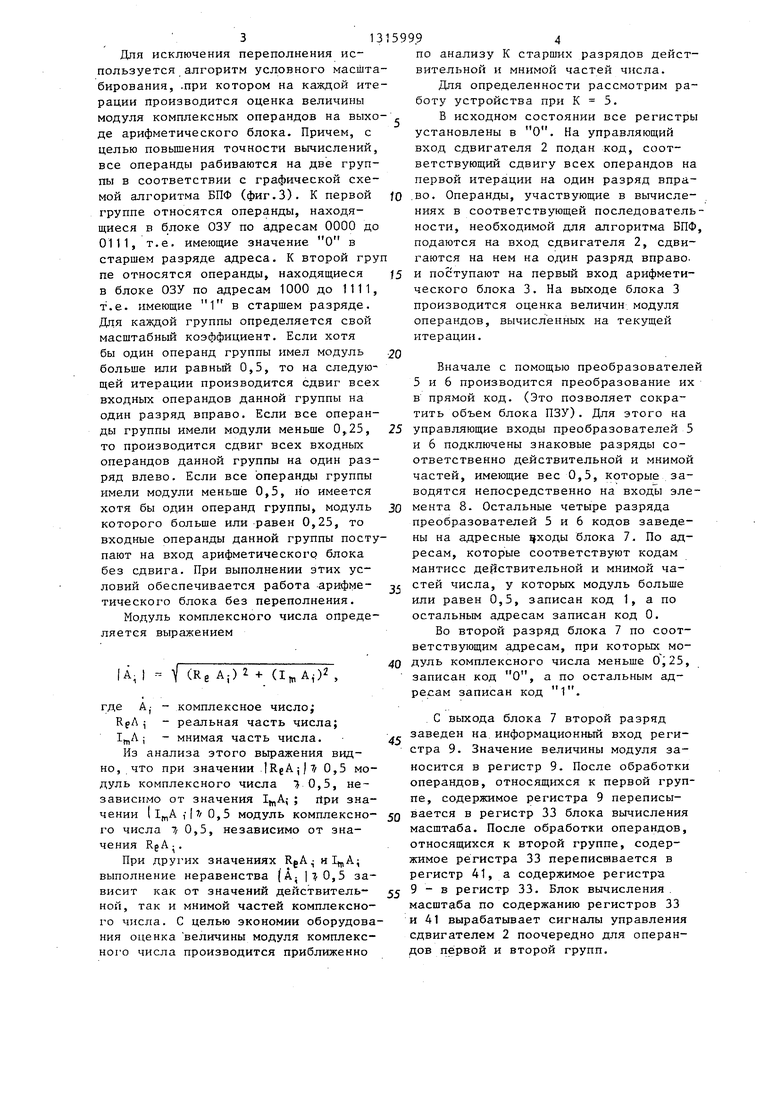

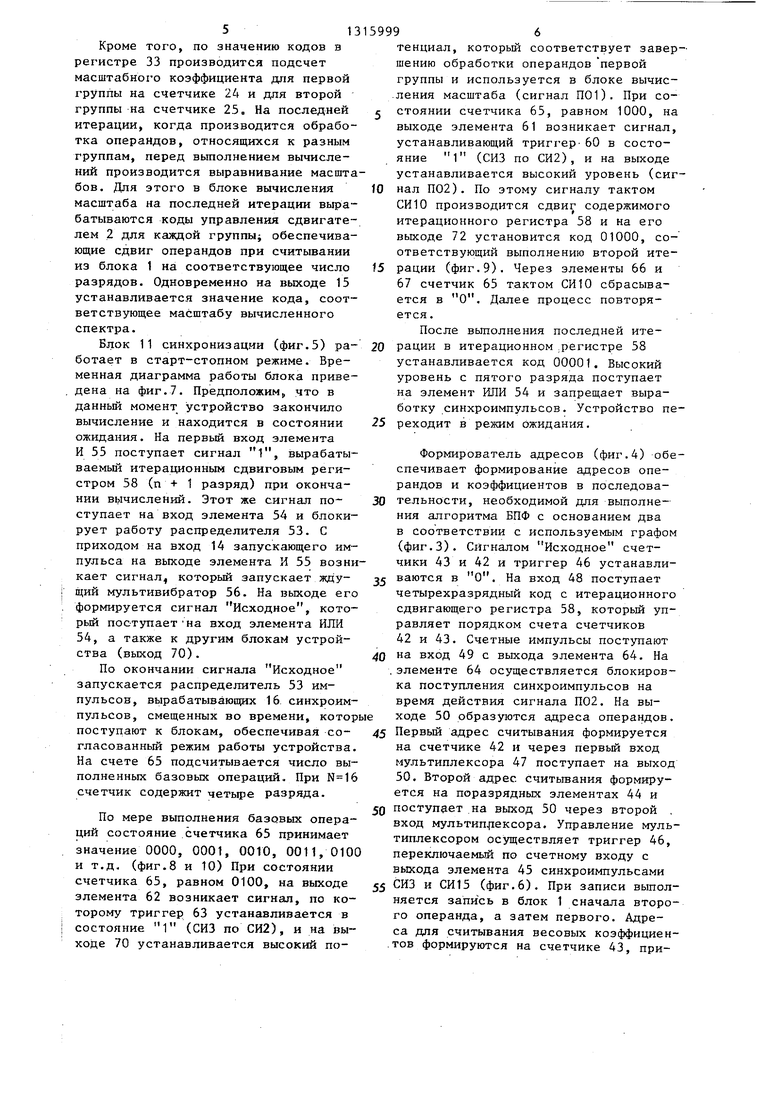

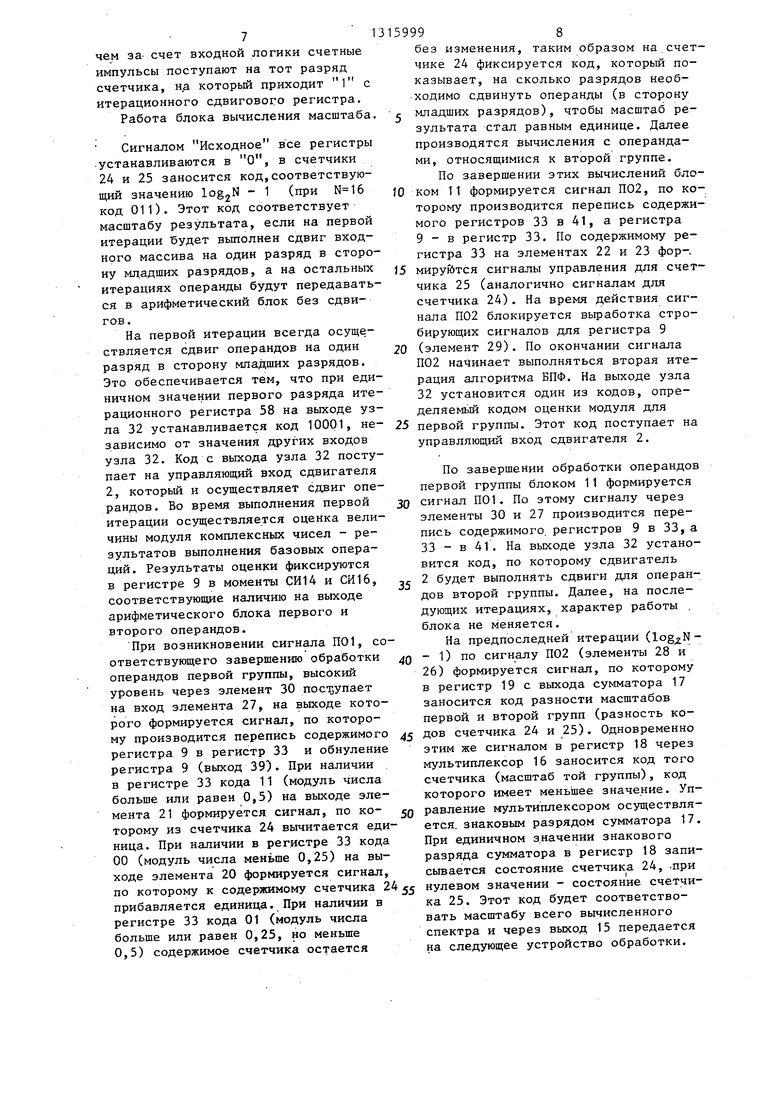

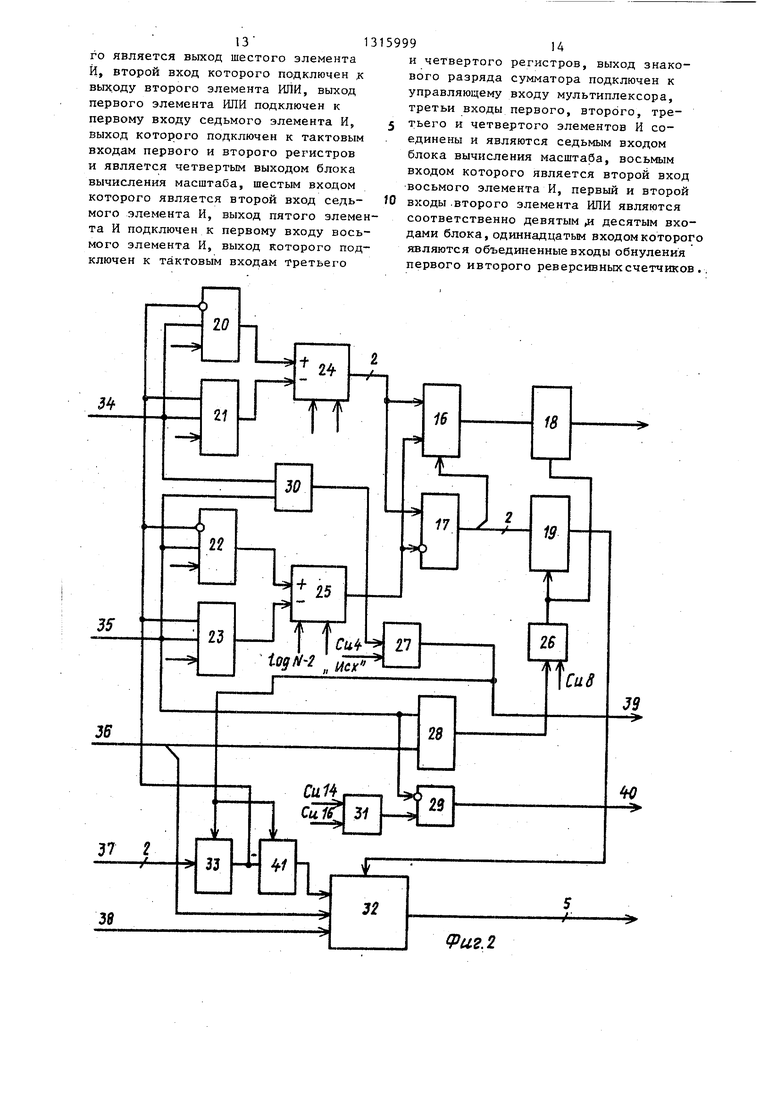

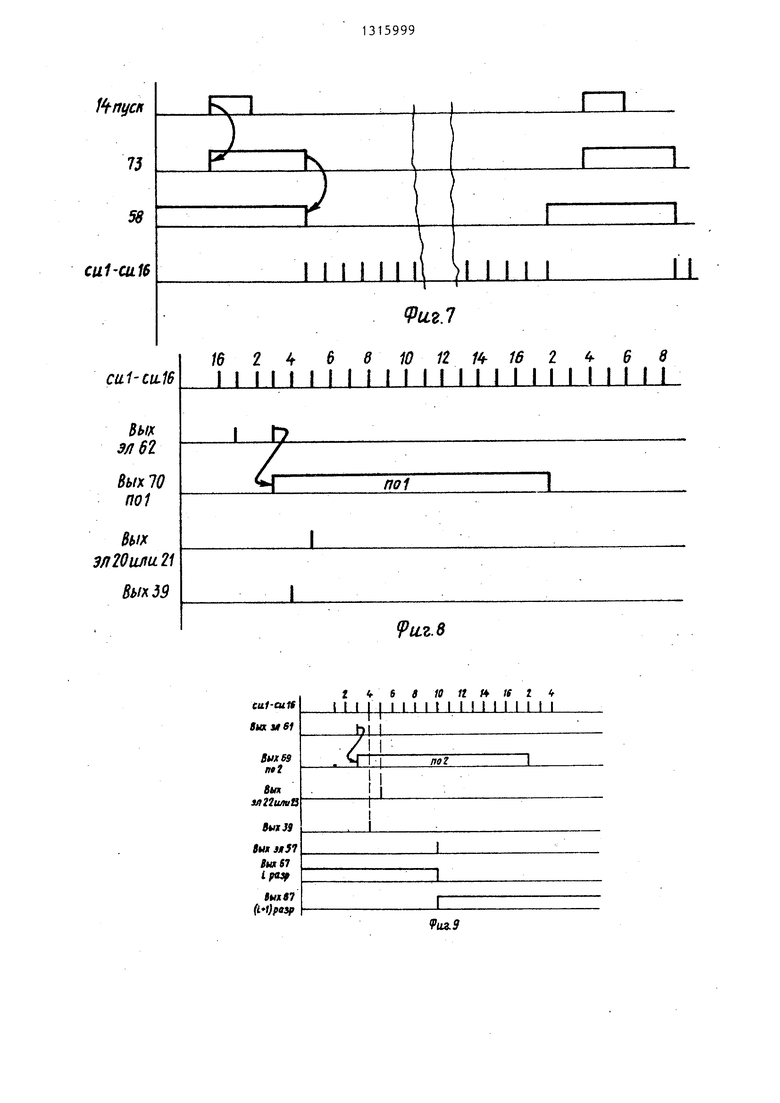

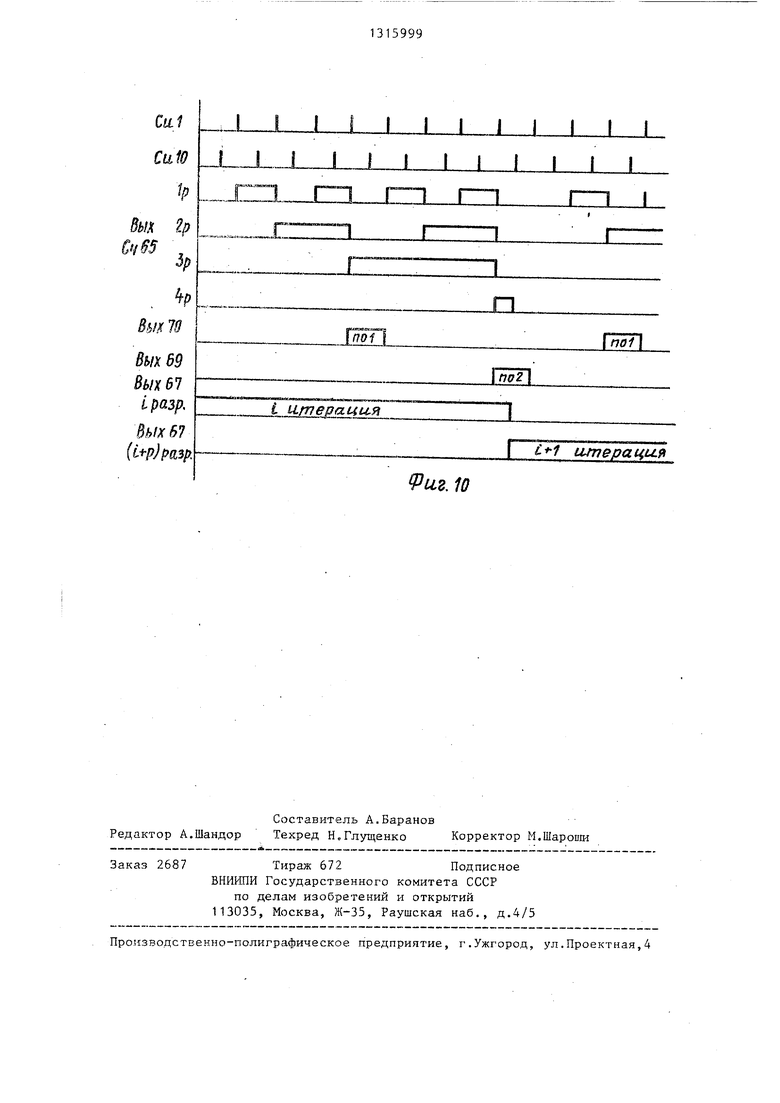

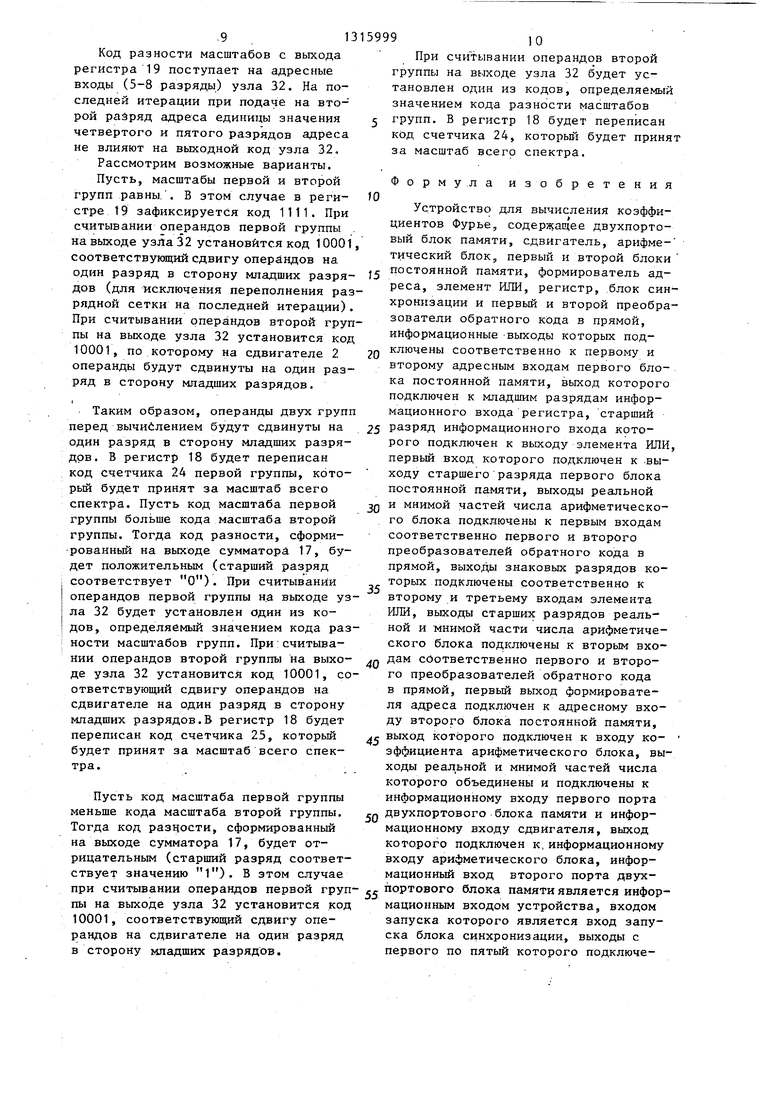

На фиг.1 представлена схема предлагаемого устройства; на фиг.2.- схема блока вычисления масштаба; на фиг.З - графическая схема алгоритма БПФ; на фиг,4 - схема формирователя адресов; на фиг,5 - схема блока синхронизацииJ на фиг.6-10 - временные диаграммы, поясняющие работу устройства.

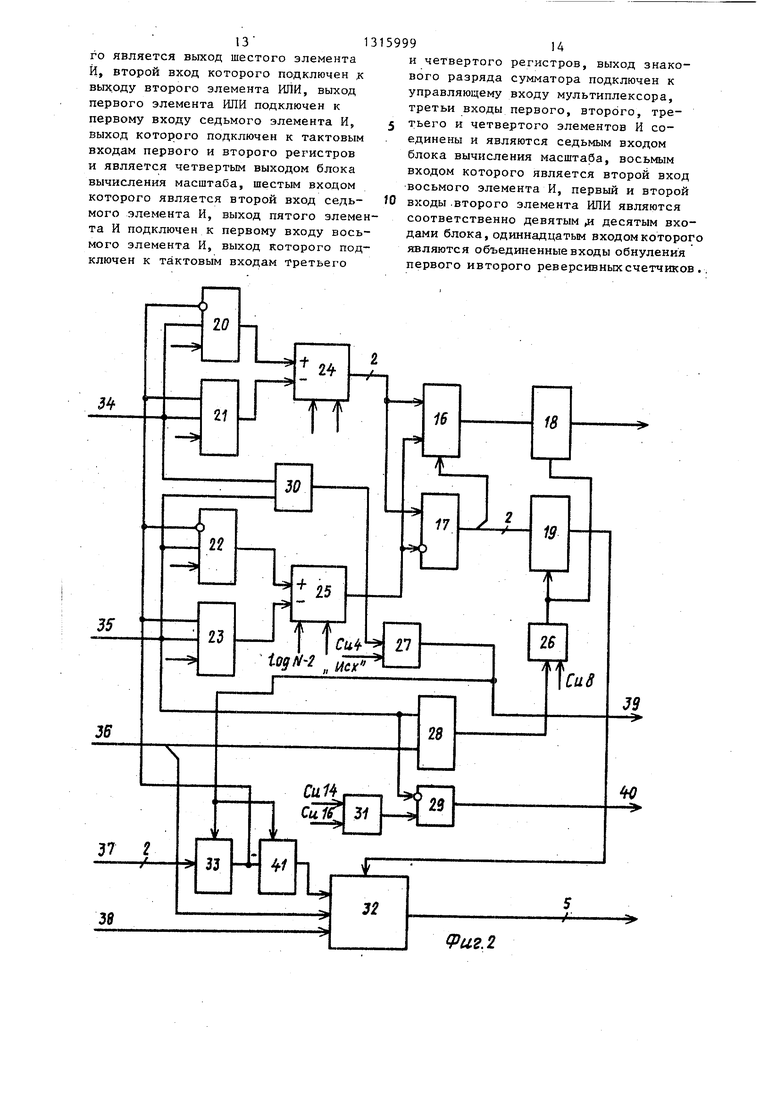

Устройство содержит двухпортовый блок 1 памяти, сдвигатель 2, арифметический блок 3, блок 4 постоянной памяти (табличных коэффициентов), преобразователи 5 и 6 обратного кода в прямой, блок 7 постоянной памяти, элемент ИЛИ 8, регистр 9, формирователь 10 адресов, блок 11 синхронизации, блок 12 вычисления масштаба,информационный вход - выход 13, вход 14 запуска и выход 15 масштабного коэффициента..

W. - комплексный весовой коэффиf5

циент (фиг.З)

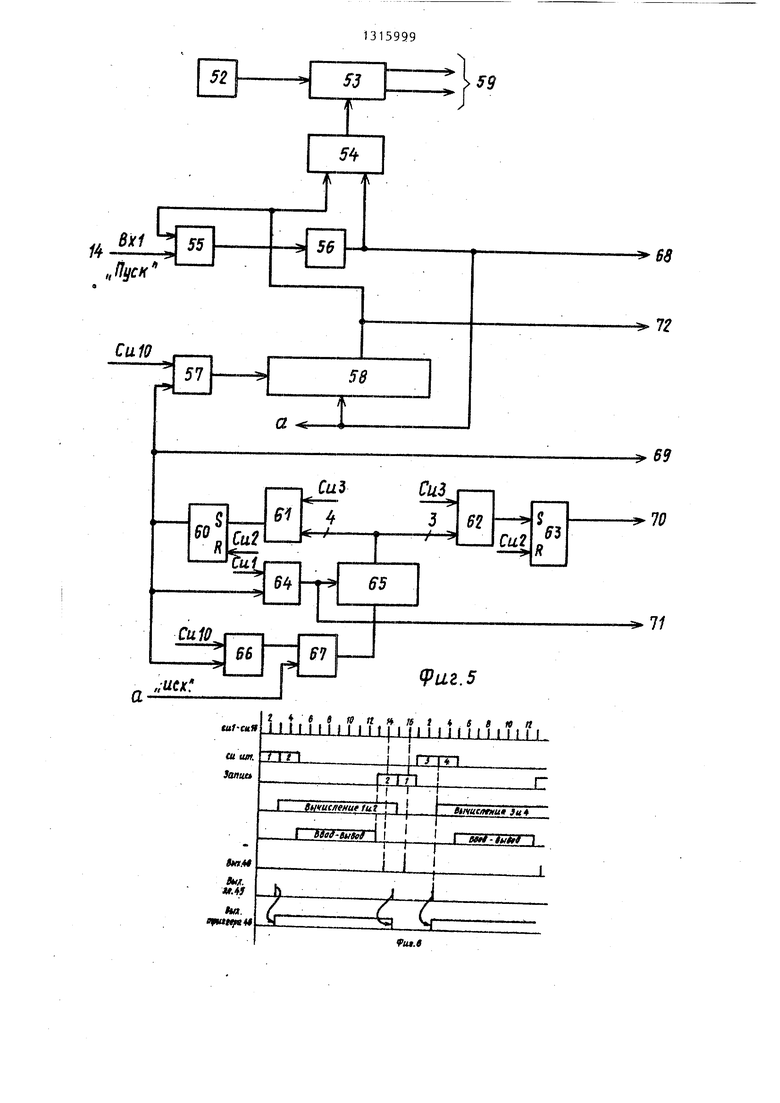

Блок синхронизации (фиг.5) содержит генератор 52 тактовых импульсов, распределитель 53 импульсов, элемент ИЛИ 54, элемент И 55, ждущий мультивибратор 56, элемент И 57, сдвиговый регистр 58, выходы 59, триггер 60, элемент И 61, элемент И 62,триггер 63, элемент И 64, счетчик 65, элементы И 66 и 67, вхбд 14, вькоды 68-72,

Рассмотрим работу устройства на примере вычисления коэффициентов Фурье для массива длиной N 16 точек. Устройство работает в старт- стопном режиме. На каждый запускающий импульс производится однократное вычисление коэффициентов Фурье и устройство останавливается до прихода следующего запускающего импульса.

С приходом импульса на вход 14 устройства блок 11 вырабатывает на выходе 68 сигнал Исходное, которьй устанавливает в исходное состояние все блоки устройства. Затем на выходе 59 начинают вырабатываться синхроимпульсы СИ1 - СИ16, которые поступают к блокам устройства, обеспечивая Блок 1 состоит из ОЗУ комплексных 30 согласованный во времени режим рабо20

25

чисел, в ячейках которых хранятся . действительные и мнимые составляющие комплексных чисел. Объем памяти составляет 2N слов (N - длина .обрабатываемого массива).

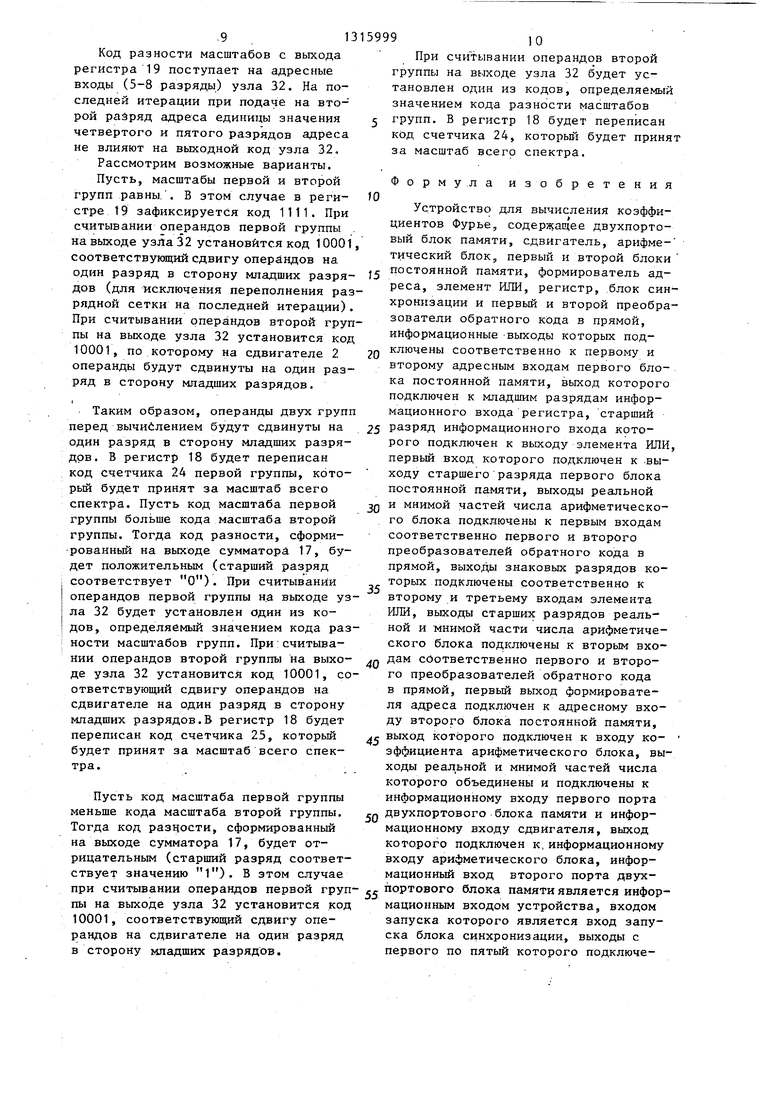

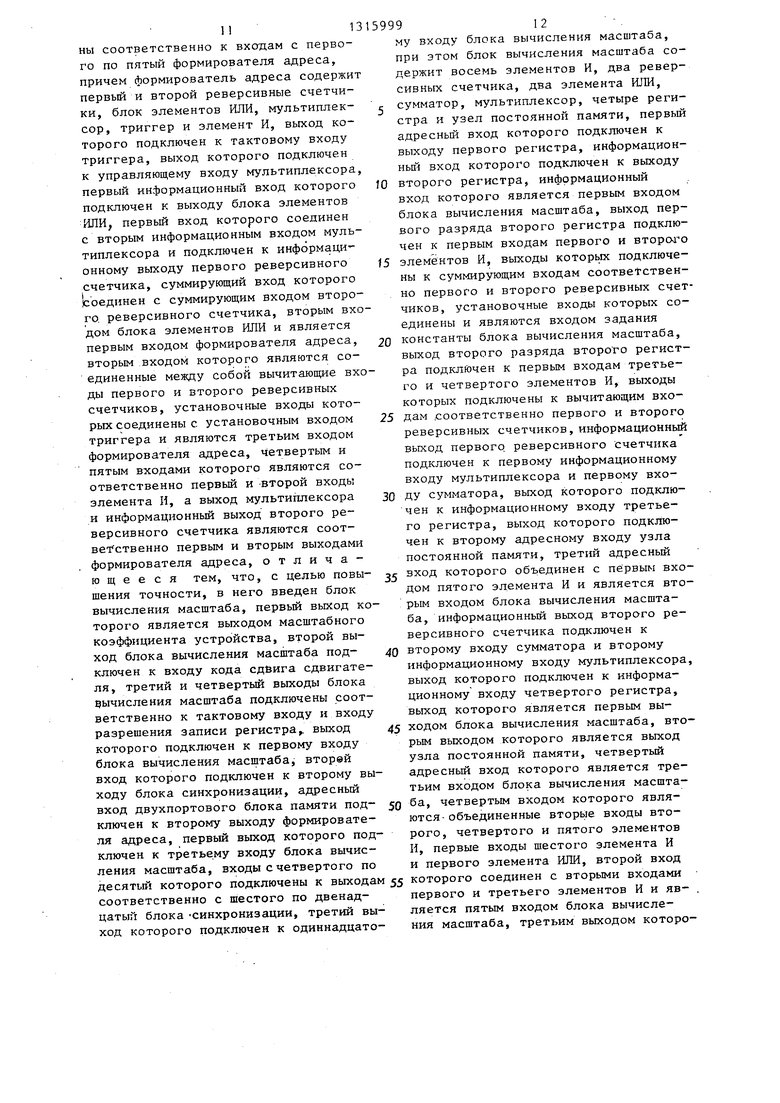

Блок вычисления масштаба (фиг.2) содержит мультиплексор 16, сумматор 17, регистры 18 и 19, четьфе элемента И 20-23, реверсивные счетчики 24 и 25, элементы И 26-29, элементы ИЛИ 30 и 31, узел 32 постоянной памяти, регистр 33, входы 34-38, выходы 39 и 40 и регистр 41,

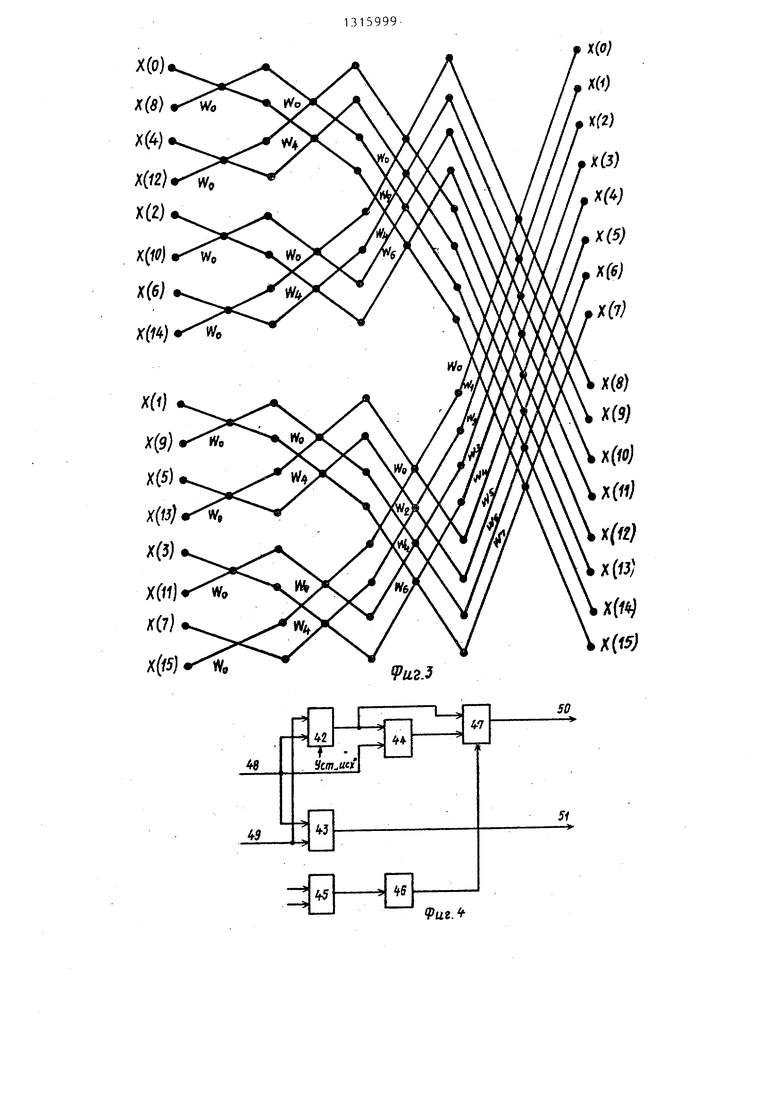

Формирователь 10 адресов (фиг,4)

ты всего устройства.

На фиг,3 представлена графическая схема используемого алгоритма БПФ, При выполнении базовой операции ал35 горитма БПФ с основанием два, необходимо считать.два операнда, один коэффициент и записать два операнда - результат базовой операции.

На фиг,6 приведена временная ди40 аграмма выполнения базовой операции. Базовая операция выполняется за 16 синхроимпульсов. Вначале производится считывание первого и второго операндов (СИ1 - СИ5), Адреса для счизовые операции вида

содержит реверсивные счетчики 42 и тывания поступают из формирователя (с входной логикой), блок 44 элемен- адресов (выход 50), Затем над этими тов ИЛИ, элемент И 45, триггер 46, операндами выполняется базовая one- мультиплексор, 47, входы 48 и 49 и рация. Коэффициенты считываются из выходы 50 и 51.блока 4 по адресу, вьщаваемому форАрифметический блок выполняет ба- 50 мирователем 10 адресов (выход 51),

После выполнения базовой операции блоком 3 результаты операции записываются по тем же адресам в блок 1, Одновременно.с записью операндов в 55 ОЗУ производится оценка величины модуля комплексных чисел. Арифметический блок работает с числами, представленными кодами с фиксированной запятой.

,-и

А;

4В.;

В,,, А, - В; ,

где А- и В; - комплексные операнды, причем вначале вычисляется операнд В ;4. , а затем А, ,

W. - комплексный весовой коэффиты всего устройства.

На фиг,3 представлена графическая схема используемого алгоритма БПФ, При выполнении базовой операции ал35 горитма БПФ с основанием два, необходимо считать.два операнда, один коэффициент и записать два операнда - результат базовой операции.

На фиг,6 приведена временная ди40 аграмма выполнения базовой операции. Базовая операция выполняется за 16 синхроимпульсов. Вначале производится считывание первого и второго операндов (СИ1 - СИ5), Адреса для счи

Для исключения переполнения используется алгоритм условного масштабирования, .при котором на каждой итерации производится оценка величины модуля комплексных операндов на выхо де арифметического блока. Причем, с целью повьшения точности вычислений, все операнды рабиваются на две группы в соответствии с графической схемой алгоритма БПФ (фиг.З). К первой группе относятся операнды, находящиеся в блоке ОЗУ по адресам 0000 до 0111, т.е. имеющие значение О в старшем разряде адреса. К второй гру пе относятся операнды, находящиеся в блоке ОЗУ по адресам 1000 до 1111, т.е. имеющие 1 в старщем разряде. Для каждой группы определяется свой масщтабный коэффициент. Если хотя бы один операнд группы имел модуль больше или равньй 0,5, то на следующей итерации производится сдвиг всех входных операндов данной группы на один разряд вправо. Если все операнды группы имели модули меньше О ,.25, то производится сдвиг всех входных операндов данной группы на один разряд влево. Если все операнды группы имели модули меньше 0,5, но имеется хотя бы один операнд группы, модуль которого больше или равен 0,25, то входные операнды данной группы поступают на вход арифметического блока без сдвига. При выполнении этих условий обеспечивается работа арифметического блока без переполнения.

Модуль комплексного числа определяется выражением

|А, I -- (Re А;): + ()2,

где А,- - комплексное число;

RpA I - реальная часть числа;

j - мнимая часть числа.

Из анализа зтого выражения видно, что при значении iRgA;)/ 0,5 модуль комплексного числа 0,5, независимо от значения ; йри значении 1 17/ 0,5 модуль комплексного числа 7, 0,5, независимо от значения RgA .

При других значениях RgA выполнение неравенства (А. ,5 зависит как от значений действительной, так и мнимой частей комплексного числа. С целью экономии оборудования оценка величины модуля комплексного числа производится приближенно

по анализу К старших разрядов действительной и мнимой частей числа.

Для определенности рассмотрим работу устройства при К 5.

В исходном состоянии все регистры установлены в О. На управляющий вход сдвигателя 2 подан код, соответствующий сдвигу всех операндов на первой итерации на один разряд вправо. Операнды, участвующие в вычислениях в соответствующей последовательности, необходимой для алгоритма БПФ, подаются на вход сдвигателя 2, сдвигаются на нем на один разряд вправо. и поступают на первый вход арифметического блока 3. На выходе блока 3 производится оценка величин модуля операндов, вычисленных на текущей итерации.

Вначале с помощью преобразователей 5 и 6 производится преобразование их в прямой код. (Это позволяет сократить объем блока ПЗУ). Для этого на

управляющие входы преобразователей 5 и 6 подключены знаковые разряды соответственно действительной и мнимой частей, имеющие вес 0,5, которые заводятся непосредственно на вход ы элемента 8. Остальные четыре разряда преобразователей 5 и 6 кодов заведены на адресные цходы блока 7. По адресам, которые соответствуют кодам мантисс действительной и мнимой частей числа, у которых модуль больше или равен 0,5, записан код 1, а по остальным адресам записан код 0.

Во второй разряд блока 7 по соответствующим адресам, при которых модуль комплексного числа меньше 0,25, О, а по остальным адII л II

записан код , ресам записан код

Г

С выхода блока 7 второй разряд заведен на информационный вход регистра 9. Значение величины модуля заносится в регистр 9. После обработки операндов, относящихся к первой группе, содержимое регистра 9 переписывается в регистр 33 блока вычисления масштаба. После обработки операндов, относящихся к второй группе, содержимое регистра 33 переписшвается в регистр 41, а содержимое регистра 9 - в регистр 33. Блок вычисления . масштаба по содержанию регистров 33 и 41 вырабатывает сигналы управления сдвигателем 2 поочередно для операндов первой и второй групп.

Кроме того, по значению кодов в регистре 33 производится подсчет масштабного коэффициента для первой группы на счетчике 24 и для второй группы на счетчике 25. На последней итерации, когда производится обработка операндов, относящихся к разным группам, перед вьтолнением вычислений производится выравнивание масштабов. Для этого в блоке вычисления масштаба на последней итерации вырабатываются коды управления сдвигате- лем 2 для каждой группы; обеспечивающие сдвиг операндов при считывании из блока 1 на соответствующее число разрядов. Одновременно на выходе 15 устанавливается значение кода, соответствующее масштабу вычисленного спектра.

Блок 11 синхронизации (фиг.5) ра- 20 рации в итерационном .регистре 58

ботает в старт-стопном режиме. Временная диаграмма работы блока приведена на фиг. 7. Предположим,, что в данный момент устройство закончило вычисление и находится в состоянии ожидания. На первый вход элемента И 55 поступает сигнал 1, вырабатываемый итерационным сдвиговым регистром 58 (п + 1 разряд) при окончании вычислений. Этот же сигнал поступает на вход элемента 54 и блокирует работу распределителя 53. С приходом на вход 14 запускающего импульса на выходе элемента И 55 возникает сигнал, который запускает жду- щий мультивибратор 56. На выходе его формируется сигнал Исходное, который поступаетна вход элемента ИЛИ 54, а также к другим блокам устройства (выход 70).

По окончании сигнала Исходное запускается распределитель 53 импульсов, вырабатывающих 16 синхроимпульсов, смещенных во времени, которые поступают к блокам, обеспечивая согласованный режим работы устройства. На счете 65 подсчитывается число выполненных базовых операций. При счетчик содержит четьфе разряда.

По мере выполнения базовых операций состояние счетчика 65 принимает значение 0000, 0001, 0010, 0011,0100 и т.д. (фиг.8 и 10) При состоянии счетчика 65, равном 0100, на выходе элемента 62 возникает сигнал, по которому Триггер 63 устанавливается в состояние 1 (СИЗ по СИ2), и на выходе 70 устанавливается высокий потенциал, который соответствует завер-- шению обработки операндов первой группы и используется в блоке вычис- -ления масштаба (сигнал П01). При состоянии счетчика 65, равном 1000, на выходе элемента 61 возникает сигнал, устанавливаюп;ий триггер- 60 в состояние 1 (СИЗ по СИ2), и на выходе устанавливается высокий уровень (сигнал П02). По этому сигналу тактом СИЮ производится сдвиг содержимого итерационного регистра 58 и на его выходе 72 установится код 01000, соответствующий выполнению второй итерации (фиг.9). Через элементы 66 и 67 счетчик 65 тактом СИЮ сбрасывается в О. Далее процесс повторяется.

После выполнения последней итеустанавливается код 00001. Высокий уровень с пятого разряда поступает на элемент ИЛИ 54 и запрещает выработку синхроимпульсов. Устройство пе- реходит в режим ожидания.

Формирователь адресов (фиг.4) обеспечивает формирование адресов операндов и коэ4)фициентов в последовательности, необходимой для выполнения алгоритма БПФ с основанием два в соответствии с используемым графом (фиг.З). Сигналом Исходное счетчики 43 и 42 и триггер 46 устанавливаются в О. На вход 48 поступает четырехразрядный код с итерационного сдвигающего регистра 58, который управляет порядком счета счетчиков 42 и 43. Счетные импульсы поступают

на вход 49 с выхода элемента 64. На элементе 64 осуществляется блокировка поступления синхроимпульсов на время действия сигнала П02. На выходе 50 образуются адреса операндов.

Первый адрес считывания формируется на счетчике 42 и через первый вход мультиплексора 47 поступает на выход 50. Второй адрес считывания формируется на поразрядных элементах 44 и

поступает на выход 50 через второй , вход мультиплексора. Управление мультиплексором осуществляет триггер 46, переключаемый по счетному входу с выхода элемента 45 синхроимпульсами

СИЗ и СИ15 (фиг.6). При записи выполняется запиЪь в блок 1 сначала второго операнда, а затем первого. Адреса для считывания весовых коэффициен- тов формируются на счетчике 43, причем за- счет входной логики счетные импульсы поступают на тот разряд счетчика, на которьй приходит 1 с итерационного сдвигового регистра.

Работа блока вычисления масштаба

Сигналом Исходное все регистры .устанавливаются в О, в счетчики 24 и 25 заносится код,соответствующий значению - 1 (при код 011). Этот код соответствует масштабу результата, если на первой итерации будет вьшолнен сдвиг входного массива на один разряд в сторону мл.адших разрядов, а на остальных итерациях операнды будут передаваться в арифметический блок без сдвигов.

На первой итерации всегда осуществляется сдвиг операндов на один разряд в сторону младших разрядов. Это обеспечивается тем, что при единичном значении первого разряда итерационного регистра 58 на выходе узла 32 устанавливается код 10001, не- зависимо от значения других входов узла 32. Код с выхода узла 32 поступает на управляющий вход сдвигателя 2, который и осуществляет сдвиг операндов. Во время выполнения первой итерации осуществляется оценка величины модуля комплексных чисел - результатов выполнения базовьпс операций. Результаты оценки фиксируются в регистре 9 в моменты СИ14 и СИ16, соответствующие наличию на выходе арифметического блока первого и второго операндов.

При возникновении сигнала П01, соответствующего завершению обработки операндов первой группы, высокий уровень через элемент 30 пост упает на вход элемента 27, на выходе которого формируется сигнал, по которому производится перепись содержимого регистра 9 в регистр 33 и обнуление регистра 9 (выход 39). При наличии в регистре 33 кода 11 (модуль числа больше или равен 0,5) на выходе элемента 21 формируется сигнал, по ко- торому из счетчика 24 вычитается единица. При наличии в регистре 33 кода 00 (модуль числа меньше 0,25) на выходе элемента 20 формируется сигнал, по которому к содержимому счетчика 2 прибавляется единица. При наличии в регистре 33 кода 01 (модуль числа больше или равен 0,25, но меньше 0,5) содержимое счетчика остается

без изменения, таким образом на,счечике 24 фиксируется код, который показывает, на сколько разрядов необходимо сдвинуть операнды (в сторону младших разрядов), чтобы масштаб результата стал равным единице. Далее производятся вычисления с операндами, относящимися к второй группе.

По завершении этих вычислений блоком 11 формируется сигнал П02, по которому производится перепись содержимого регистров 33 в 41, а регистра 9 - в регистр 33. По содержимому регистра 33 на элементах 22 и 23 фор-, мируйтся сигналы управления для счетчика 25 (аналогично сигналам для счетчика 24). На время действия сигнала П02 блокируется вьфаботка стро- бирующих сигналов для регистра 9 (элемент 29). По окончании сигнала П02 начинает выполняться вторая итерация алгоритма БПФ, На вькоде узла

32установится один из кодов, определяемый кодом оценки модуля для первой группы. Этот код поступает на управляющий вход сдвигателя 2.

По завершении обработки операндов первой группы блоком 11 формируется сигнал П01. По этому сигналу через элементы 30 и 27 производится перепись содержимого, регистров 9 в 33,а

33- в 41, На выходе узла 32 установится код, по которому сдвигатель

2 будет выполнять сдвиги для операндов второй группы. Далее, на последующих итерациях, характер работы . блока не меняется.

На предпоследней итерации ( - - 1) по сигналу П02 (элементы 28 и 26) формируется сигнал, по которому в регистр 19 с выхода сумматора 17 заносится код разности масштабов первой и второй групп (разность кодов счетчика 24 и 25). Одновременно этим же сигналом в регистр 18 через мультиплексор 16 заносится код того счетчика (масштаб той группы), код которого имеет меньшее значение. Управление мультиплексором осуществляется, знаковым разрядом сумматора 17. При единичном з.начении знакового разряда сумматора в регистр 18 записывается состояние счетчика 24, -при нулевом значении - состояние счетчика 25. Этот код будет соответствовать масштабу всего вычисленного спектра и через выход 15 передается на следующее устройство обработки.

.913

Код разности масштабов с выхода регистра 19 поступает на адресные входы (5-8 разряды) узла 32. На последней итерации при подаче на вто- рой разряд адреса единицы значения четвертого и пятого разрядов адреса не влияют на выходной код узла 32. Рассмотрим возможные варианты. Пусть, масштабы первой и второй групп равны.. В этом случае в регистре 19 зафиксируется код 1111. При считывании операндов первой группы . на выходе узЛа 32 установится код 10001 соответствующий сдвигу операндов на один разряд в сторону младших разрядов (для Исключения переполнения разрядной сетки на последней итерации). При считывании операндов второй группы на выходе узла 32 установится код 10001, по которому на сдвигателе 2 операнды будут сдвинуты на один разряд в сторону младших разрядов.

Таким образом, операнды двух групп перед вычислением будут сдвинуты на один разряд в сторону младших разрядов. В регистр 18 будет переписан код счетчика 24 первой группы, который будет принят за масштаб всего спектра. Пусть код масштаба первой группы больше кода масштаба второй группы. Тогда код разности, сформированный на выходе сумматора 17, будет положительным (старший соответствует О). При считывании операндов первой группы н.а выходе узла 32 будет установлен один из кодов, определяемый значением кода разности масштабов групп. При:считывании операндов второй группы на выходе узла 32 установится код 10001, соответствующий сдвигу операндов на сдвигателе на один разряд в сторону младших разрядов.В регистр 18 будет переписан код счетчика 25, который будет принят за масштаб всего спектра.

Пусть код масштаба первой группы меньше кода масштаба второй группы. Тогда код разности, сформированный на выходе сумматора 17, будет отрицательным (старший разряд соответствует значению 1). В этом случае при считывании операндов первой группы на выходе узла 32 установится код 10001, соответствующий сдвигу операндов на сдвигателе на один разряд в сторону младших разрядов.

599910

При счи тывании операндов второй группы на выходе узла 32 будет установлен один из кодов, определяемый значением кода разности масштабов 5 групп. В регистр 18 будет переписан код счетчика 24, которьп будет принят за масштаб всего спектра.

Формула изобретения

Устройство для вычисления коэффициентов Фурье, содержащее двухпортовый блок памяти, сдвигатель, арифме- тический блок., первый и второй блоки

постоянной памяти, формирователь адреса, злемент ИЛИ, регистр, блок синхронизации и первый и второй преобразователи обратного кода в прямой, информационные -выходы которых подключены соответственно к первому и второму адресным входам первого блока постоянной памяти, выход которого подключен к младшим разрядам информационного входа регистра, старший

разряд информационного входа которого подключен к выходу элемента ИЛИ, первый вход которого подключен к .выходу старшего разряда первого блока постоянной памяти, выходы реальной

и мнимой частей числа арифметического блока подключены к первым входам соответственно первого и второго преобразователей обратного кода в прямой, выходы знаковых разрядов которых подключены соответственно к второму и третьему входам элемента ИЛИ, выходы старших разрядов реаль ной и мнимой части числа арифметического блока подключены к вторым входам соответственно первого и второго преобразователей обратного кода в прямой, первый выход формирователя адреса подключен к адресному входу второго блока постоянной памяти,

выход которого подключен к входу ко- зффициента арифметического блока, выходы и мнимой частей числа которого обьединены и подключены к информационному входу первого порта

двухпортового блока памяти и информационному входу сдвигателя, выход которого подключен к, информационному входу арифметического блока, информационный вход второго порта двухпортового блока памяти является информационным входом устройства, входом запуска которого является вход запуска блока синхронизации, выходы с первого по пятый которого подключе1113

ны соответственно к входам с первого по пятый формирователя адреса, причем формирователь адреса содержит первый и второй реверсивные счетчики, блок элементов ИЛИ, мультиплексор, триггер и элемент И, выход которого подключен к тактовому входу триггера, выход которого подключен к управляющему входу мультиплексора, первый информационный вход которого подключен к выходу блока элементов ИЛИ, первьй вход которого соединен с вторым информационным входом мультиплексора и подключен к информаци - онному выходу первого реверсивного счетчика, суммирующий вход которого соединен с суммирующим входом второго, реверсивного счетчика, вторым входом блока элементов ИЛИ и является первым входом формирователя адреса, вторым входом которого являются соединенные между собой вычитающие входы первого и второго реверсивных счетчиков, установочные входы которых соединены с установочным входом триггера и являются третьим входом формирователя адреса, четвертым и пятым входами которого являются соответственно первый и второй входы элемента И, а выход мультиплексора и информационный выход второго реверсивного счетчика являются соот- вет ственно первым и вторым выходами формирователя адреса, отличающееся тем, что, с целью повышения точности, в него введен блок вычисления масштаба, первый выход которого является выходом масштабного коэффициента устройства, второй выход блока вычисления масштаба подключен к входу кода сдбига сдвигате- ля, третий и четвертый выходы блока вычисления масштаба подключены соответственно к тактовому входу и входу разрешения записи регистра выход которого подключен к первому входу блока вычисления масштаба, вторей вход которого подключен к второму выходу блока синхронизации, адресный вход двухпортового блока памяти подключен к второму выходу формирователя адреса, первый выход которого подключен к третьему входу блока вычисления масштаба, входы с четвертого по десятый которого подключены к выходам соответственно с шестого по двенадцатый блока -синхронизации, третий выход которого подключен к одиннадцато599912

му входу блока вычисления масштаба, при этом блок вычисления масштаба содержит восемь элементов И, два реверсивных счетчика, два элемента ШШ, с сумматор, мультиплексор, четыре регистра и узел постоянной памяти, первый адресный вход которого подключен к выходу первого регистра, информацион- ньш вход которого подключен к выходу

10 второго регистра, информационный

вход которого является первым входом блока вычисления масштаба, выход первого разряда второго регистра подключен к первым входам первого и вторш-о

15 элементов И, выходы которых подключены к суммирующим входам соответственно первого и второго реверсивных счетчиков, установочные входы которых соединены и являются входом задания

0 константы блока вычисления масштаба, выход второго разряда второго регистра подключен к первым входам третьего и четвертого элементов И, выходы которых подключены к вычитающим вхо5 дам .соответственно первого и второго реверсивных счетчиков, информационный выход первого, реверсивного счетчика подключен к первому информационному входу мультиплексора и первому вхо0 ДУ сумматора, выход которого подключен к информационному входу третьего регистра, выход которого подключен к второму адресному входу узла постоянной памяти, третий адресный

5 вход которого объединен с первым входом пятого элемента И и является вторым входом блока вычисления масштаба, информационный выход второго реверсивного счетчика подключен к

0 второму входу сумматора и второму информационному входу мультиплексора, выход которого подключен к информационному входу четвертого регистра, выход которого является первым вы5 ходом блока вычисления масштаба, вторым выходом которого является выход узла постоянной памяти, четвертый адресный вход которого является третьим входом блока вычисления масшта0 ба, четвертым входом которого являются- объединенные вторые входы второго, четвертого и пятого элементов И, первые входы шестого элемента И и первого элемента ИЛИ, второй вход

5 которого соединен с вторыми входами первого и третьего элементов И и яв- , ляется пятым входом блока вычисления масштаба, третьим выходом которо13-13

го является выход шестого элемента И, второй вход которого подключен д выходу второго элемента ИЛИ, выход первого элемента ИЛИ подключен к первому входу седьмого элемента И, выход которого подключен к тактовым входам первого и второго регистров и является четвертым выходом блока вычисления масштаба, шестым входом которого является второй вход седьмого элемента И, выход пятого элемента И подключен к первому входу восьмого элемента И, выход которого подключен к тактовым входам третьего

91А

и четвертого регистров, выход знакового разряда сумматора подключен к управляющему входу мультиплексора, третьи входы первого, второго, третьего и четвертого элементов И соединены и являются седьмым входом блока вычисления масштаба, восьмым входом которого является второй вход восьмого элемента и, первый и второй

входы .второго элемента ИЛИ являются соответственно девятым i десятым входами блока, одиннадцатым входом которого являются объединенные входы обнуления первого ивторого реверсивныхсчетчиков,.

Vu..

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1277135A1 |

| Устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1336029A1 |

| Устройство для вычисления коэффициентов Фурье | 1984 |

|

SU1168967A1 |

| Процессор быстрого преобразования Фурье | 1983 |

|

SU1119027A1 |

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1983 |

|

SU1133597A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов в реальном масштабе времени. Цель изобретения - повышение точности. Поставленная цель достигается за счет того, что устройство состоит из двухпортового блока памяти 1, сдвига- теля 2, арифметического блока 3, блока постоянной памяти 4, преобразователей обратного кода в прямой 5, 6, блока постоянной памяти 7, элемента- ИЛИ 8, регистра 9, формирователя адресов 10, блока синхронизации 11, блока вычисления масштаба 12, информационного входа 13, входа запуска 14 и выхода масштабного коэффициента 15. 9 ил. (Л ы tnA СП со

48

42 I ycCT.w/l

3

5f

9ut.

г 4-6 в to п te t V I И I I I I I I М И I I I I I I I

:й

no г

no г

Pia.9

| Устройство для вычисления коэффициентов фурье | 1977 |

|

SU648989A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления коэффициентов Фурье | 1984 |

|

SU1168967A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-12-30—Подача