fO

12822872

Изобретение относится к области электротехники и может быть использовано в тиристорных регуляторах переменного напряжения, работающих на нелинейную нагрузку в виде инфракрас- 5 .ных кварцевых нагревателей.

Цель изобретения - повышение надежности тиристорного регулятора в работе на нелинейную нагрузку.

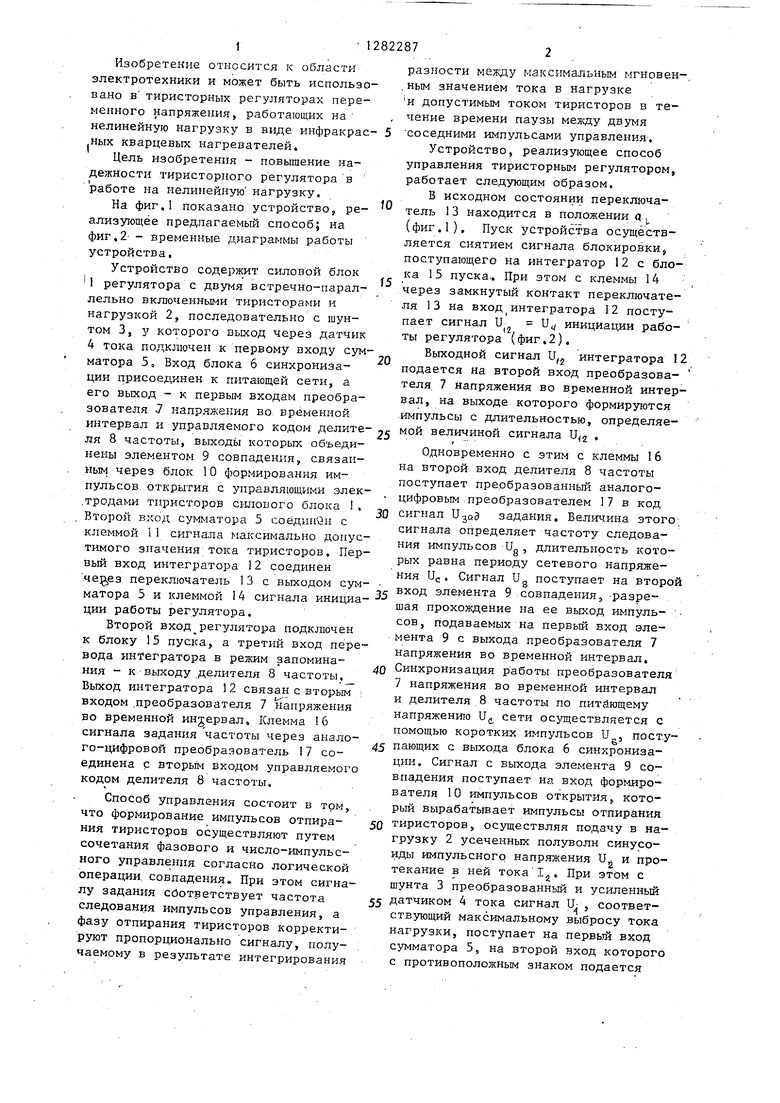

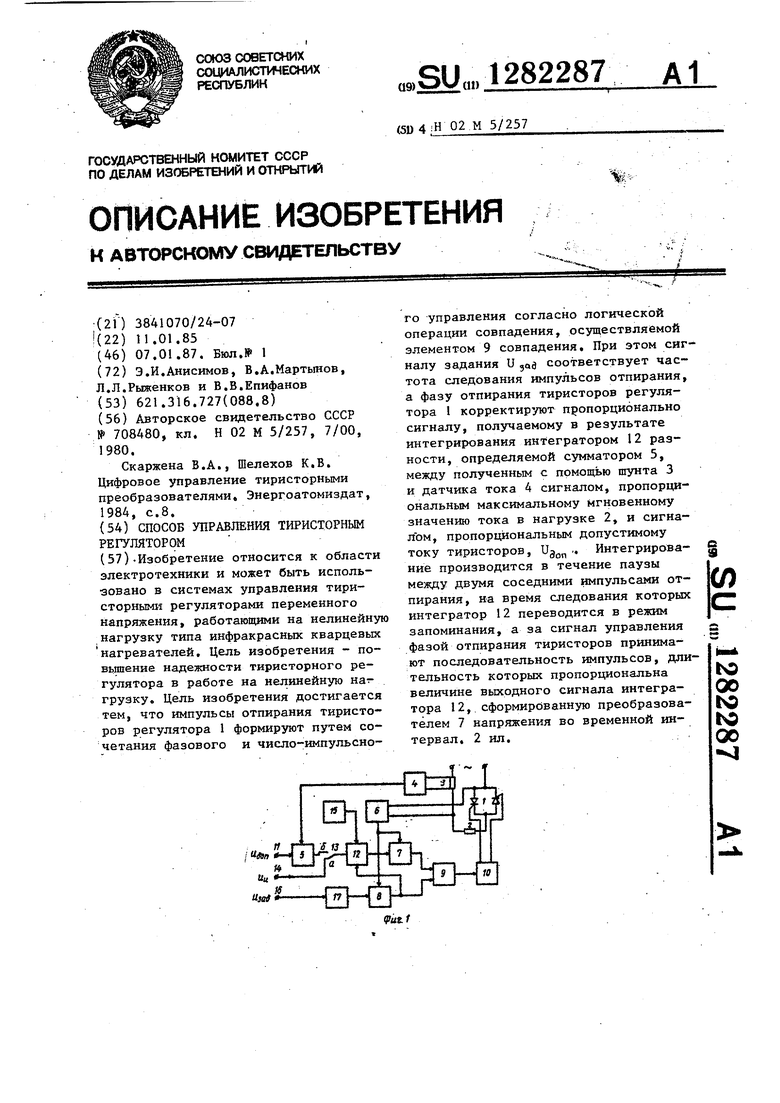

На фиг.1 показано устройство, реализующее предлагаемый способ; на фиг,2- - временные диаграммы работы устройства.

Устройство содержит силовой блок I регулятора с двумя встречно-параллельно включенными тиристорами и нагрузкой 2, последовательно с шунтом 3, у которого выход через датчик 4 тока подключен к первому входу сумматора 5, Вход блока 6 синхронизации присоединен к питающей сети, а его выход - к первым входам преобразователя 7 напряжения во, временной интервал и управляемого кодом делите-2 мой величиной сигнала

f5

20

разности между максимальн HbiM значением тока в нагр и допустимым током тирист чение времени паузы между соседними импульсами упра

Устройство, реализующе управления тиристорным ре работает следующим образо

В исходном состоянии п тель 13 находится в полож (фиг.1). Пуск устройства ляется снятием сигнала бл поступающего на интеграто ка 15 пуска.. При этом с к через замкнутый контакт п ля 13 на вход интегратора пает сигнал и 1 иниц ты регулятора (фиг,2).

Выходной сигнал ин подается на второй вход п теля. 7 напряжения во врем вал, на выходе которого ф .импульсы с длительностью,

ля 8 частоты, выходы которых объединены элементом 9 совпадения, связанным через блок 10 формирования импульсов открытия с управляющими элек- .тродами тиристоров силового блока I . Второй вход сумматора 5 соединен с клеммой 11 сигнала максимально допустимого значения тока тиристоров. Первый вход интегратора 2 соединен переключатель 13с выходом cyivi- матора 5 и клеммой 14 сигнала инициа ции работы регулятора.

Второй вход регулятора подключен к блоку 15 пуска, а третий вход перевода интегратора в режим запоминания - к-выходу .делителя 8 частоты, Выход интегратора 12 связан с вторым ; входом .преобразователя 7 напряжения во временной интервал. Клемма 16 сигнала задания частоты через аналого-цифровой преобразователь 17 соединена с вторым входом управляемого кодом делителя 8 частоты.

Способ управления состоит в том, что формирование импульсов отпирания тиристоров осуществляют путем сочетания фазового и число-импульсного управления согласно логической операции совпадения. При этом сигналу задания сйответствует частота следования импульсов управления, а фазу отпирания тиристоров корректи- РЗТот пропорционально сигналу, получаемому в результате интегрирования

Одновременно с этим с на второй вход делителя 8 поступает пре.образованный цифровым.преобразователем 30 сигнал задания. Вел сигнала определяет частот ния импульсов Ug, длитель рых равна периоду сетевог ния Uc , Сигнал и„ поступа

-. .о

j вход элемента 9 совпадени шая прохождение на ее вых

мента 9 с выхода преобраз напряжения во временной и

40 Синхронизация работы прео 7 напряжения во временной и делителя.8 частоты по п напряженито U сети осущес помощью коротких импульсо

45 пающих с выхода блока 6 с ции. Сигнал с выхода элем впадения поступает на вхо вателя 10 импульсов откры рый вырабатьгоает импульсы

50 тиристоров, осуществляя п грузку 2 усеченных полуво иды импульсного напряжени текание в ней Тока Ij. Пр шунта 3 преобразованный и датчиком 4 тока сигнал U ствующий максимальному вы нагрузки, поступает на пе сумматора 5, на второй вх с противоположным знаком

55

мой величиной сигнала

разности между максимальным мгновен-, HbiM значением тока в нагрузке и допустимым током тиристоров в течение времени паузы между двумя соседними импульсами управления.

Устройство, реализующее способ управления тиристорным регулятором, работает следующим образом,

В исходном состоянии переключатель 13 находится в положении а j (фиг.1). Пуск устройства осуществляется снятием сигнала блокировки, поступающего на интегратор 12 с блока 15 пуска.. При этом с клеммы 14 через замкнутый контакт переключателя 13 на вход интегратора 12 поступает сигнал и 1 инициации работы регулятора (фиг,2).

Выходной сигнал интегратора 12 подается на второй вход преобразователя. 7 напряжения во временной интервал, на выходе которого формируются .импульсы с длительностью, определяе

Одновременно с этим с клеммы 16 на второй вход делителя 8 частоты поступает пре.образованный аналого- цифровым.преобразователем 17 в код 30 сигнал задания. Величина этого сигнала определяет частоту следования импульсов Ug, длительность которых равна периоду сетевого напряжения Uc , Сигнал и„ поступает на второ:

.о

j вход элемента 9 совпадения, -разрешая прохождение на ее выход импульента 9 с выхода преобразователя 7 напряжения во временной интервал,

Синхронизация работы преобразователя 7 напряжения во временной интервал и делителя.8 частоты по питйющему напряженито U сети осуществляется с помощью коротких импульсов и J пост.упающих с выхода блока 6 синхронизации. Сигнал с выхода элемента 9 совпадения поступает на вход формироателя 10 импульсов открытия, который вырабатьгоает импульсы отпирания

тиристоров, осуществляя подачу в нагрузку 2 усеченных полуволн синусоиды импульсного напряжения U и протекание в ней Тока Ij. При этом с шунта 3 преобразованный и усиленный датчиком 4 тока сигнал U , соответствующий максимальному выбросу тока нагрузки, поступает на первый вход сумматора 5, на второй вход которого с противоположным знаком подается

сигнал Ug 5 соответствующий допустимому значению тока тиристоров 1 На выходе сумматора 5 получается сигнал и,- разности U - .

В момент времени t после начала протекания тока 1 в нагрузке 2 осуществляют подключение переключателем 13 первого входа интегратора. 12 к выходу сумматора 5.

В .положении В переключателя 13 на первый вход интегратора 12 поступает сигнал - Uyj который интегрируется в течение времени

tg-tj,

Выходной сигнал U , интегра13

тора с помощью преобразователя 7 напряжения во временной интервал преобразуют во временной интервал, соответствующий фазе отпирания тиристоров , и подают на перный вход элемен- та 9 совпадения. По приходу на в то- рой вход элемента 9 совпадения разре шающего сигнала U „ с выхода делителя 8 частоты на выходе элемента 9 совпадения появляется сигнал Ug в виде парных импульсов для управления встречно-параллельно включенными тиристорами, фаза которых соответствует сигналу на выходе интегратора, а частота их следования соот- ветствует сигналу U д задания. При этом в нагрузку будут пропускаться пары импульсов Ui положительной и отрицательной полярности. Далее процесс управления протекает аналогичны образом. Чтобы, исключить ошибочную работу интегратора на время t - t и Ь.л - Ь протекания переходного процесса изменения тока в нагрузке 2 его переводят в режим запоминания. Коррекцию фазы импульсов Ug с постепенным з еньшением задержки углов отпирания тиристоров производят до тех nopj пока сопротивление нагрев.а- телей Нагрузки 2 не перестанет меняться с ростом температуры. При этом с выхода интегратора 12 через элемент 9 совпадения на блок 10 на- чнет поступать максимальный сигнал, при котором фаза отпирания тиристо- ров имеет минимальное значение, близкое к нулю, В дальнейщем формирование импульсов отпирания тиристоров осуществляется путем число-им

О

0 0

пульсного управления, не подвергая искажению полуволны синусоиды напряжения, пропускаемые в нагрузку,

л

Таким образом, при комбинированном способе управления одновременно осуществляется регулирование частоты и коррекция фазы открытия тиристоров, кроме того, он позволяет избежать чрезмерных бросков тока на начальных участках вольт-амперной характеристики кварцевого нагревателя, сопротивление которого существенно зависит от температуры. Так как частота пропускаемых в нагрузку импульсов тока меньше частоты сети, в паузах между ними.сетевое напряжение не имеет искажений, кроме того, . автоматический переход на число- импульсное управление исключает отказы регулятора от сбоев в блоке синхронизации.

5

20 -30

25 Формула изо.бретения

Способ управления тиристсэрным регулятором, заключающийся в том, что импульсы отпирания тиристоров формируют.с частотой, меньщей частоты сети и пропорциональной сигналу управления частотой, отличающийся тем, что, с целью повышения надежности регулятора в работе на нелинейную нагрузку,корректиРУют фазу импульсов отпирания, для чего измеряют мгновенное максимальное значение выброса тока нагрузки, определяют разность между допустимым значением тока тиристоров и мгновенным максимальным значением выброса тока нагрузки каждого предыдущего включения, интегрируют эту разность в паузе между двумя соседними включениями, конечный резуль тат интегрирования на каждом интервале запоминают на время отпирания тиристоров и на следующем интервале интегрирование начинают с запом-. ненного значения, причем за- сигнал

управления фазой принимают последовательность импульсов, длительность которых пропорциональна величине результата интегрирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для компенсации реактивной мощности нагрузки и симметрирования трехфазной сети | 1985 |

|

SU1261044A1 |

| Тиристорный электропривод постоянного тока | 1978 |

|

SU771836A1 |

| Способ стабилизации активной мощности тиристорного регулятора и устройство для его осуществления | 1982 |

|

SU1073874A1 |

| Устройство для компенсации реактивной мощности | 1986 |

|

SU1347118A1 |

| Устройство для управления моментом синхронного двигателя | 1988 |

|

SU1527700A1 |

| Электропривод переменного тока | 1987 |

|

SU1529392A1 |

| Устройство для импульсно-фазового управления трехфазным тиристорным регулятором напряжения | 1987 |

|

SU1598081A1 |

| Способ управления трехфазным тиристорным регулятором мощности | 2023 |

|

RU2828285C1 |

| Система управления тиристорным электроприводом | 1976 |

|

SU938260A1 |

| Способ стабилизации среднего значения тока активной нагрузки однофазного однотактного тиристорного выпрямителя с интегратором | 1986 |

|

SU1385124A1 |

-Изобретение относится к области электротехники и может быть использовано в системах управления тиристорными регуляторами переменного напряжения, работающими на нелинейную нагрузку типа инфракрасных кварцевых нагревателей. Цель изобретения - по- вьппение надежности тиристорного регулятора в работе на нелинейную ка-г грузку. Цель изобретения достигается тем, что импульсы отпирания тиристоров регулятора 1 формируют путем сочетания фазового и число-импульсного управления согласно логической операции совпадения, осуществляемой элементом 9 совпадения. При этом сигналу задания U д соответствует частота следования импульсов отпирания, а фазу отпирания тиристоров регулятора 1 корректируют пропорционально сигналу, получаемому в результате интегрирования интегратором 12 разности, определяемой сумматором 5, между полученным с помощью шунта 3 и датчика тока 4 сигналом, пропорциональным максимальному мгновенному значению тока в нагрузке 2, и сигналом, пропорциональным допустимому току тиристоров, Ug .. Интегрирование производится в течение паузы между двумя соседними импульсами отпирания, на время следования которых интегратор 12 переводится в режим запоминания, а за сигнал управления фазой отпирания тиристоров принимают последовательность импульсов, длительность которых пропорциональна величине вькодного сигнала интегратора 12, сформированную преобразователем 7 напряжения во временной интервал. 2 ил. (Л го 00 ю ts9 00

| Способ цифрового управления тиристорным преобразователем | 1976 |

|

SU708480A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Скаржена В.А., Шелехов К.В | |||

| Цифровое управление тиристорными преобразователями, Энергоатомиздат, 1984, с.8. | |||

Авторы

Даты

1987-01-07—Публикация

1985-01-11—Подача