(St) СИСТЕМА УПРАВЛЕНИЯ ТИРИСТОРНЫМ ЭЛЕКТРОПРИВОДОМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для управления трехфазным тиристорным регулятором напряжения | 1989 |

|

SU1697228A1 |

| Фазовый дискриминатор | 1989 |

|

SU1688380A1 |

| Преобразователь код-угол | 1976 |

|

SU693416A1 |

| МОДУЛЬ СИНХРОНИЗАЦИИ | 2006 |

|

RU2304788C1 |

| Цифровой частотно-фазовый дискриминатор | 1987 |

|

SU1494204A2 |

| Преобразователь переменного напряжения в постоянное | 1985 |

|

SU1325640A1 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2002 |

|

RU2231912C2 |

| Устройство для измерения временных интервалов | 1984 |

|

SU1221637A1 |

| Устройство контроля системы импульсного регулирования тяговых электродвигателей транспортного средства | 1985 |

|

SU1355509A1 |

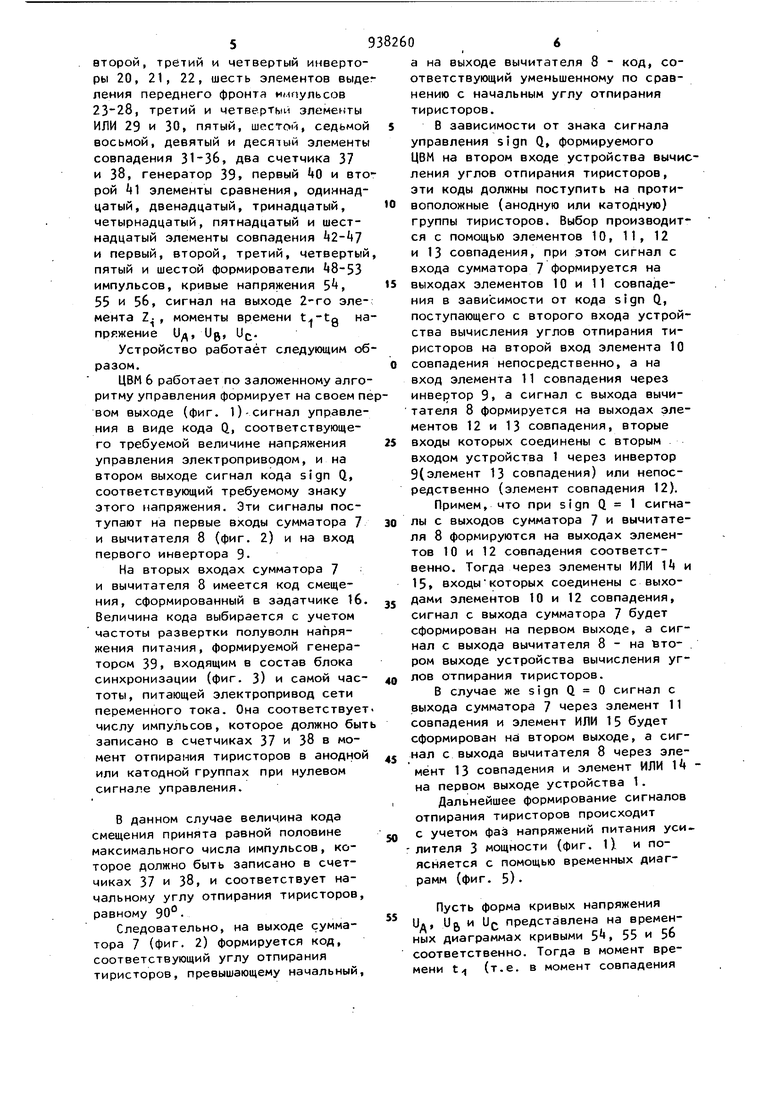

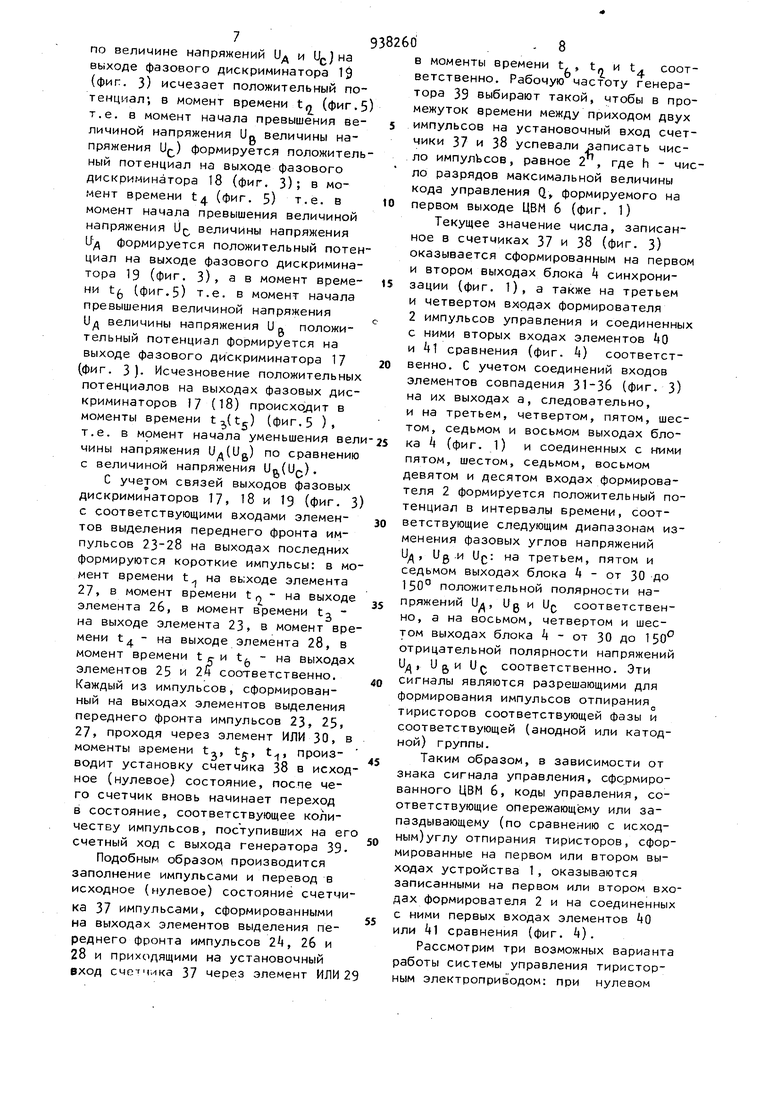

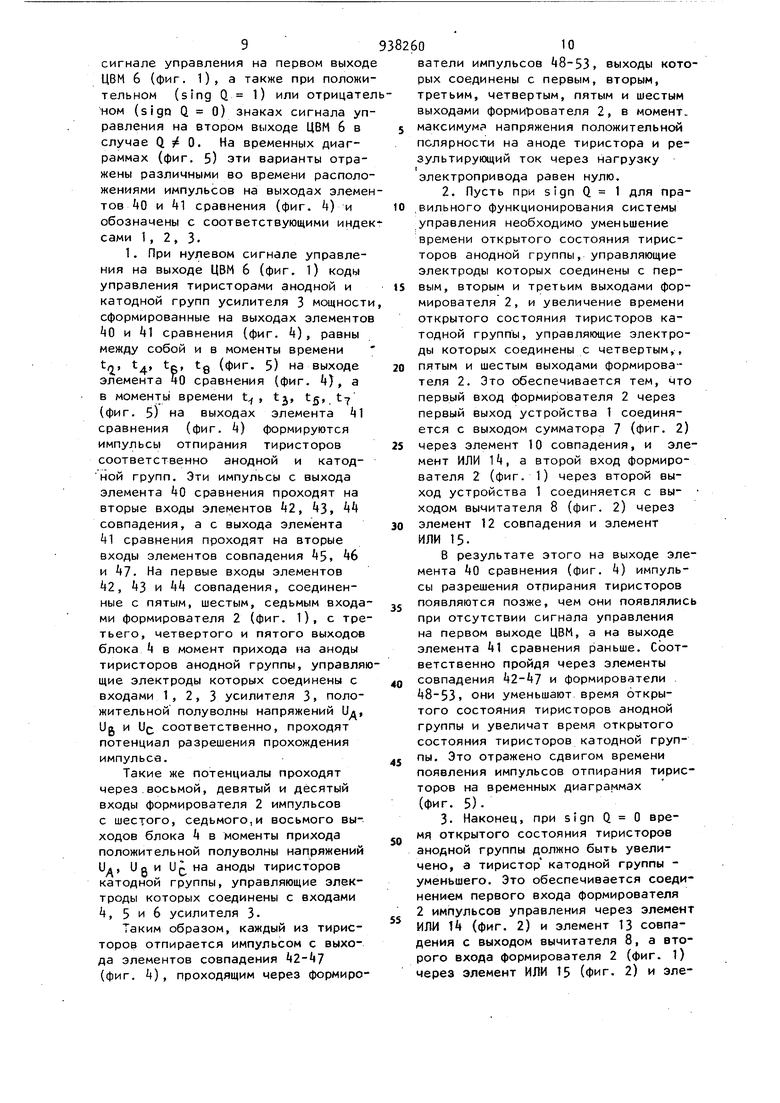

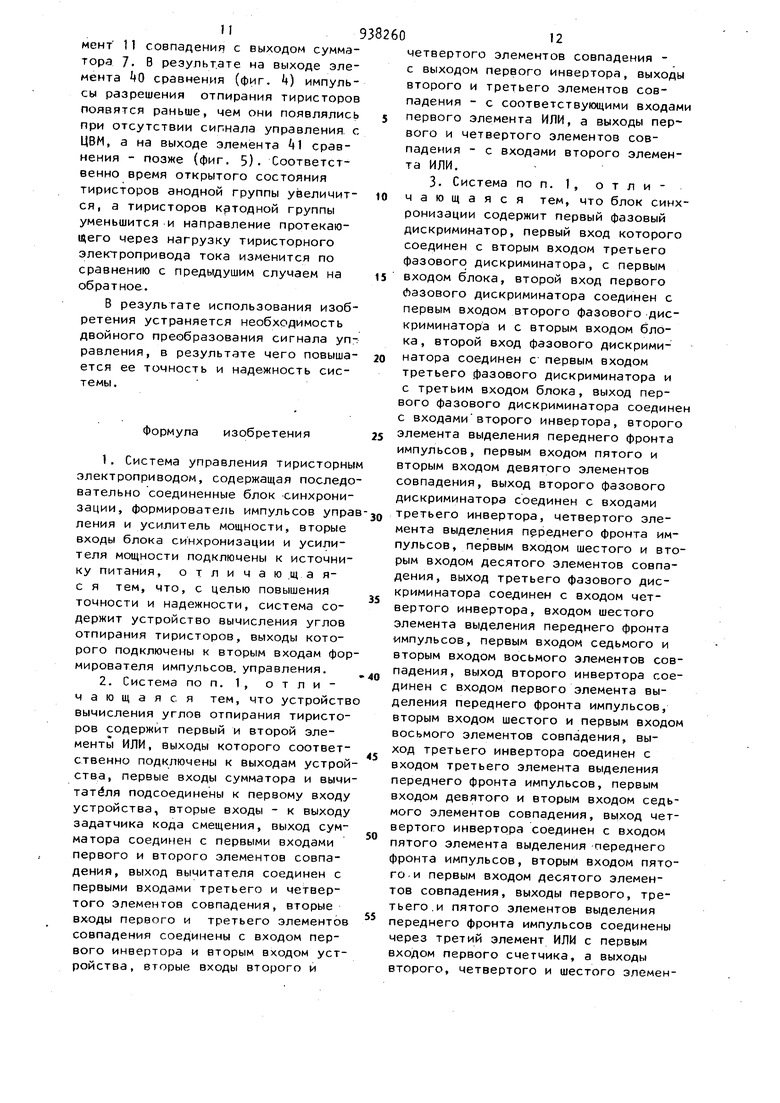

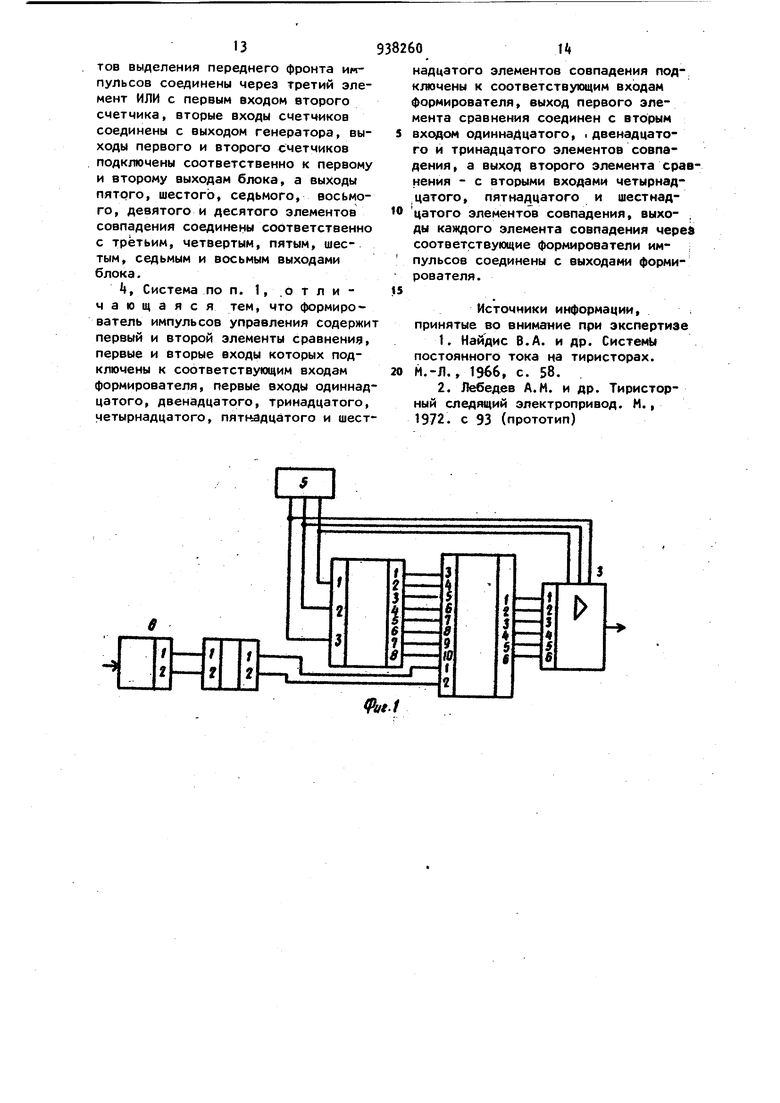

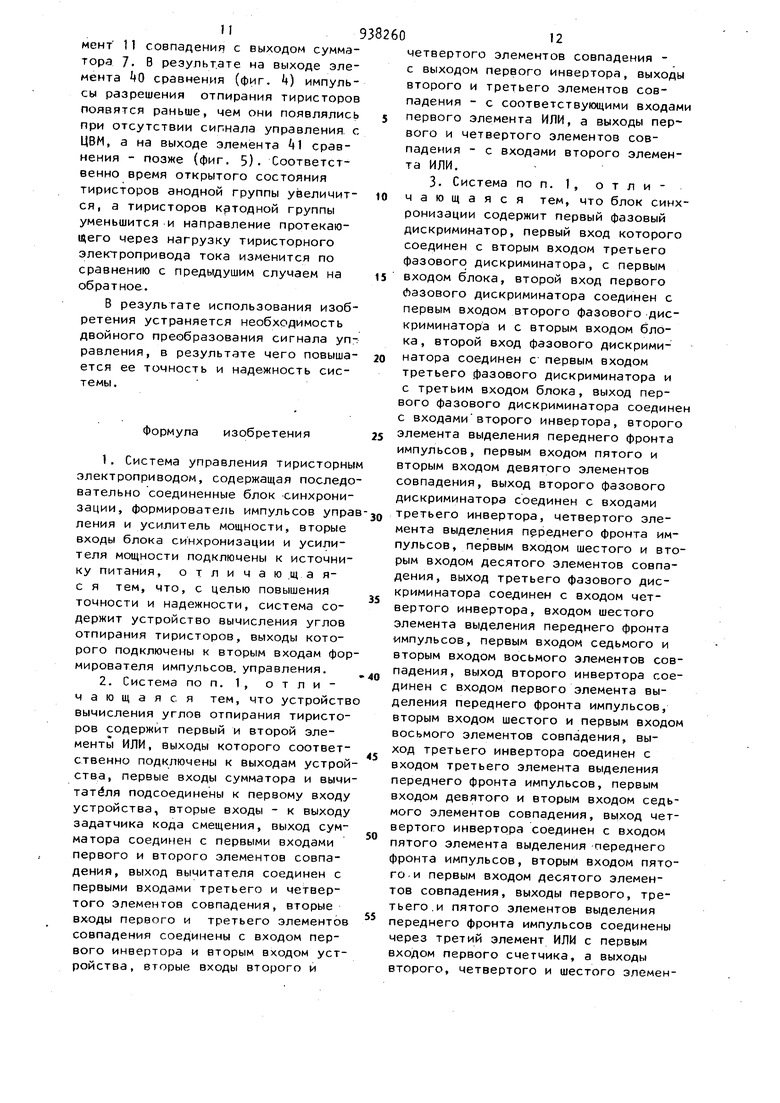

Изобретение относится к автоматическому управлению и регулированию и предназначено для управления тиристорными электроприводам с помощью средств вычислительной техники. Известна система управления тиристорным электроприводом, содержа щая блок синхронизации, формироват импульсов управления и усилитель мощности, а также источник питания Недостатком указанной системы является ее невысокая точность. Наиболее близкой по технической сущности к предлагаемой является система управления тиристорным элек троприводом, содержащая последовате.пьно соединенные блок синхронизации, формироватепь импульсов управления и усилитель мацности, входы блока синхронизации и вторые входы усилитепя мощности подключены к исгомнику питания Г2. Недостатком системы являются, малая точность и пониженная надежность. Цель изобретения - повышение точности и надежности устройства. Поставленная цель достигается тем, что система содержит устройство вычисления углов отпирания .тиристора, выходы которого подключены к вторым входам формирователя импульсов управления. Кроме того, устройство вычисления углов отпирания тиристоров содержит первый и второй элементы ИЛИ, выходы которых соответственно подключены к выходам устройства, первые выходы сумматора и вычитателя подсоединены к первому входу устройства, вторые входы - к выходу задатчика кода смещения, выход сумматора соединен с первыми входами первого и второго элементов совпадения, выход вычитателя соединен с первыми входами третьего и четвертого элементов совпадения, вторые входы первого и тре 39 тьего элементов совпадения соединены с входом первого инвертора и вторым входом устройства, вторые входы вто рого и четвертого элементов совпадения соединены с выходом первого инвертора, выходы второго и третьего элементов совпадения соединены с соответствующими входами первого элемента ИЛИ, а выходы первого и четвертого элементов совпадения с входами второго элемента ИЛИ. При этом блок синхронизации содержит первый фазовый дискриминатор, первый вход которого соединен с вторым входом третьего фазового дискриминатора и с первым входом блока, второй вход первого фазового дискриминатора соединен с первым входом второго фазового дискриминатора и с вторым входом блока, второй вход второго фазового дискриминатора соединен с первым входом третьего фазового дискриминатора и третьим входом блока, выходпервого фазового дискриминатора соединен с входами второго инвертора, второго элемента выделения переднего фронта импульсов, первым входом пятого и вторым вхбдом девятого элементов совпадения, выход второго фазового дискриминатора соединен с входами третьего инвентора, четвертого элемента выделения переднего фронта импульсов, первым входом шестого и вторым входом десятого элементов совпадения, выход третьего фазового дискриминатора соединен с входом четвертого инвентора, входом шестого элемента выделения переднего фро та импульсов, первым .входом седьмого и вторым входом восьмого элементов совпадения, выход второго инвен тора соединен с входом первого элемента выделения переднего фронта им пульсов , вторым входом шестого и первым входом восьмого элементов совпадения, выход третьего инвентора сбединен с входом третьего элеме та выделения Переднего фронта импул сов, первым входом девятого и вторы входом седьмого элементов совпадения, выход четвертого инвентора сое динен с входом пятого элемента, выде ления переднего фронта импульсов, вторым входом пятого и первым вхо. дом десятого элементов совпадения, выходы первого, третьего и пятого элементов совпадения переднего фрон та импульсов соединены через третий элемент ИЛИ с первым входом первого счетчика, а выходы второго, четвертого и шестого элементов выделения переднего фронта импульсов соединены через третий элемент ИЛИ с первым входом второго счетчика, вторые входы счетчика соединены с выходом генератора, выходы первого и второго счетчиков подключены соответственно к первому и второму выходам блока, а выходы пятого, шестого, седьмого и восьмого, девятого и десятого элементов совпадения соединены соответственно с третьим, четвертым, пятым, шестым, седьмым и восьмым выходами блока. Кроме того, формирователь импульсов управления содержит первый и второй элементы сравнения, первые и вторые входы которых подключены к соответствующим входам формирователя, первые входы одиннадцатого, двенадцатого, тринадцатого, четырнадцатого, пятнадцатого и шестнадцатого элементов совпадения подклю чены к соответствующим входам формирователя, выход первого элемента сравнения соединен с вторыми входами одиннадцатого, двенадцатого и тринадцатого элементов совпадения, а выход второго элемента сравнения соединен с вторыми входами четырнадцатого, пятнадцатого и шестнадцатого элементов совпадения, выходы каждого элемента совпадения через соответствующие формирователи импульсов соединены с выходами формирователя. На фиг. 1 представлена функциональная схема системы управления тиристорным электроприводом; на фиг. 2 - схема устройства вычисления углов отрицания тиристоров; на фиг. 3 - схема блока синхронизации; на фиг. - схема формирователя импульсов управления; на фиг. 5 переменные диаграммы работы системы. Схема содержит устройство 1 вычисления углов отпирания тиристоров формирователь 2 импульсов управления,, усилитель 3 мощности, блок синхронизации, источник 5 питания, ЦВМ 6, сумматор 7 вычитатель 8, первый инвертор 9 первый, второй, третий и четвертый элементы совпадения 10, 11, 12 и 13, первый и второй элементы ИЛИ Ц и 15, задатчик 16 кода смещения, первый, второй и третий дискриминаторы 17, 18 и 19, второй, третий и четвертый инверто ры 20, 21, 22, шесть элементов выд ления переднего фронта импульсов , третий и четвертый элементы ИЛИ 29 и 30, пятый, шестой, седьмой восьмой, девятый и десятый элементы совпадения 31-36, два счетчика 37 и 38, генератор 39, первый kQ и вто рой 41 элементы сравнения, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый и шестнадцатый элементы совпадения и первый, второй, третий, четвертый пятый и шестой формирователи 8-53 импульсов, кривые напряжения S, 55 и 5б, сигнал на выходе 2-го элемента Z , моменты времени на пряжение Уд, Ug, Uj.. Устройство работает следующим об разом. ЦВМ 6 работает по заложенному алго ритму управления формирует на своем п вом выходе (фиг. 1)-сигнал управления в виде кода Q,, соответствующего требуемой величине напряжения управления электроприводом, и на втором выходе сигнал кода sign Q, соответствующий требуемому знаку этого напряжения. Эти сигналы поступают на первые входы сумматора 7 и вычитателя 8 (фиг. 2) и на вход первого инвертора ЭНа вторых входах сумматора 7 и вычитателя 8 имеется код смещения, сформированный в задатчике 16. Величина кода выбирается с учетом частоты развертки полуволн напряжения питания, формируемой генератором 39, входящим в состав блока синхронизации (фиг. 3) и самой частоты, питающей электропривод сети переменного тока. Она соответствует числу импульсов, которое должно быт записано в счетчиках 37 и 38 в момент отпирания тиристоров в анодной или катодной группах при нулевом сигнале управления. В данном случае величина кода смещения принята равной половине максимального числа импульсов, которое должно быть записано в счетчиках 37 и 38, и соответствует начальному углу отпирания тиристоров, равному 90. Следовательно, на выходе сумматора 7 (фиг. 2) формируется код, соответствующий углу отпирания тиристоров, превышающему начальный. а на выходе вычитателя 8 - код, соответствующий уменьшенному по сравнению с начальным углу отпирания тиристоров. В зависимости от знака сигнала управления sign Q, формируемого ЦВМ на втором входе устройства вычисления углов отпирания тиристоров, эти коды должны поступить на противоположные (анодную или катодную) группы тиристоров. Выбор производится с помощью элементов 10, 11, 12 и 13 совпадения, при этом сигнал с входа сумматора 7 формируется на выходах элементов 10 и 11 совпадения в зависимости от кода sign Q, поступающего с второго входа устройства вычисления углов отпирания тиристоров на второй вход элемента 10 совпадения непосредственно, а на вход элемента 11 совпадения через инвертор 9, а сигнал с выхода вычитателя 8 формируется на выходах элементов 12 и 13 совпадения, вторые входы которых соединены с вторым входом устройства 1 через инвертор 9(элемент 13 совпадения) или непосредственно (элемент совпадения 12). Примем, что при sign Q 1 сигналы с выходов сумматора 7 и вычитателя 8 формируются на выходах элементов 10 и 12 совпадения соответственно. Тогда через элементы ИЛИ I и 15, входыкоторых соединены с выходами элементов 10 и 12 совпадения, сигнал с выхода сумматора 7 будет сформирован на первом выходе, а сигнал с выхода вычитателя 8 - на Ьтором выходе устройства вычисления yi- лов отпирания тиристоров. В случае же sign Q О сигнал с выхода сумматора 7 через элемент 11 совпадения и элемент ИЛИ 15 будет сформирован на втором выходе, а си1- нал с выхода вычитателя 8 через элемент 13 совпадения и элемент ИЛИ 14 на первом выходе устройства 1. Дальнейшее формирование сигналов отпирания тиристоров происходит с учетом фаз напряжений питания усилителя 3 мощности (фиг. Ц и поясняется с помощью временных диаграмм (фиг. 5). Пусть форма кривых напряжения UA, Ug И UQ представлена на временных диаграммах кривыми 5, 55 и 5б соответственно. Тогда в момент времени tx (т.е. в момент совпадения no величине напряжений Уд и U(.J на выходе фазового дискриминатора 1 (фиг. 3) исчезает положительный потенциал; в момент времени 1л (фиг.5 т.е. в момент начала превышения величиной напряжения Un величины напряжения ) формируется положитель ный потенциал на выходе фазового дискриминатора 18 (фиг. 3); в момент времени t. (фиг. 5) т.е. в момент начала превышения величиной напряжения U величины напряжения Uft формируется положительный потен циал на выходе фазового дискриминатора 19 (фиг. 3), а в момент времени t (фиг.5) т.е. в момент начала превышения величиной напряжения Уд величины напряжения Ug положительный потенциал формируется на выходе фазового дискриминатора 17 (фиг. 3)- Исчезновение положительных потенциалов на выходах фазовых дискриминаторов 17 (18) происходит в моменты времени t,(tc) (фиг.5 ) т.е. в момент начала уменьшения вел чины напряжения ид(и) по сравнению с величиной напряжения Un(Uc;). С учетом связей выходов фазовых дискриминаторов 17, 18 и 19 (фиг. 3 с соответствующими входами элементов выделения переднего фронта импульсов 2.3-28 на выходах последних формируются короткие импульсы: в мо мент времени на выходе элемента 27, в момент времени t - на выходе элемента 26, в момент времени LT tна выходе элемента 23, в момент вре мени t - на выходе элемента 28, в и t с и t момент времени t «;- и t, - на выходах элементов 25 и ZH соответственно. и 2ч СОО1 Каждый из импульсов, сформированный на выходах элементов выделения переднего фронта импульсов 23, 25, 27, проходя через элемент ИЛИ 30, моменты времени t,, tt, t.,, производит установку счетчика 38 в исход ное (нулевое) состояние, после чего счетчик вновь начинает переход в состояние, соответствующее количеству импульсов, поступивших на е счетный ход с выхода генератора 39 Подобным образом производится заполнение импульсами и перевод в исходное (нулевое) состояние счетч ка 37 импульсами, сформированными на выходах элементов выделения переднего фронта импульсов 2, 26 и 28 и приходящими на установочный вход сче-гчика 37 через элемент ИЛИ . 8 в моменты времени t, , t и t соответственно. Рабочую частоту генератора 39 выбирают такой, чтобы в промежуток времени между приходом двух импульсов на установочный вход счетчики 37 и 38 успевали записать число импулЬсов, равное 2 , где h - число разрядов максимальной величины кода управления Q формируемого на первом выходе ЦВМ 6 (фиг. 1) Текущее значение числа, записанное в счетчиках 37 и 38 (фиг. 3) оказывается сформированным на первом и втором выходах блока k синхронизации (фиг. 1), а также на третьем и четвертом входах формирователя 2 импульсов управления и соединенных с ними вторых входах элементов 0 и 41 сравнения (фиг. k} соответственно. С учетом соединений входов элементов совпадения (фиг. 3) на их выходах а, следовательно, и на третьем, четвертом, пятом, шестом, седьмом и восьмом выходах блока 4 (фиг. 1) и соединенных с ними пятом, шестом, седьмом, восьмом девятом и десятом входах формирователя 2 формируется положительный потенциал в интервалы времени, соответствующие следующим диапазонам изменения фазовых углов напряжений ид, Ug .и Up: на третьем, пятом и седьмом выходах блока 4 - от 30 до 150° положительной полярности напряжений ил, Ug и UQ соответственно, а на восьмом, четвертом и шестом выходах блока 4 - от 30 до отрицательной полярности напряжений соответственно. Эти УС сигналы являются разрешающими для формирования импульсов отпирания тиристоров соответствующей фазы и соответствующей (анодной или катодной) группы. Таким образом, в зависимости от знака сигнала управления, сформированного ЦВМ 6, коды управления, соответствующие опережающему или запаздывающему (по сравнению с исходным)углу отпирания тиристоров, сформированные на первом или втором выходах устройства 1, оказываются записанными на первом или втором входах формирователя 2 и на соединенных с ними первых входах элементов Q или 41 сравнения (фиг. 4). Рассмотрим три возможных варианта работы системы управления тиристорным электроприводом: при нулевом сигнале управления на первом выход ЦВМ 6 (фиг. 1), а также при полож тельном (sing Q 1) или отрицат ном (sign Q 0) знаках сигнала уп равления на втором выходе ЦВМ 6 в случае Q / 0. На временных диаграммах (фиг, 5) эти варианты отражены различными во времени располо жениями импульсов на выходах элеме и k сравнения (фиг. 4) и обозначены с соответствующими инде сами 1, 2, 3. 1, При нулевом сигнале управления на выходе ЦВМ 6 (фиг. 1) коды управления тиристорами анодной и катодной групп усилителя 3 мощност сформированные на выходах элементо kO и kl сравнения (фиг. k), равны между собой и в моменты времени l 4 6 8 (фиг. 5) на выходе элемента 40 сравнения (фиг. 4), а в моменть времени Ц, tj, tg, (фиг. 5) на выходах элемента k сравнения (фиг. А) формируются импульсы отпирания тиристоров соответственно анодной и катодной групп. Эти импульсы с выхода элемента tO сравнения проходят на вторые входы элементов Ц2, k3, совпадения, а с выхода элемента 41 сравнения проходят на вторые входы элементов совпадения 45, 46 и 47. На первые входы элементов 42, 43 и 44 совпадения, соединенные с пятым, шестым, седьмым входа ми формирователя 2 (фиг. 1), с тре тьего, четвертого и пятого выходов блока 4 в момент прихода на аноды тиристоров анодной группы, управля щие электроды которых соединены с входами 1, 2, 3 усилителя 3, положительной полуволны напряжений Цд, Ug и и соответственно, проходят потенциал разрешения прохождения импульса. Такие же потенциалы проходят через.восьмой, девятый и десятый входы формирователя 2 импульсов с шестого, седьмого,и восьмого выходов блока 4 в моменты прихода положительной полуволны напряжений UA, UQ и UQ на аноды тиристоров катодной группы, управляющие электроды которых соединены с входами 4, 5 и 6 усилителя 3. Таким образом, каждый из тиристоров отпирается импульсом с выхода элементов совпадения 42-47 (фиг. 4), проходящим через формиро ватели импульсов 48-53, выходы которых соединены с первым, вторым, третьим, четвертым, пятым и шестым выходами формирователя 2, в момент, максимума напряжения положительной полярности на аноде тиристора и результирующий ток через нагрузку электропривода равен нулю. 2.Пусть при sign Q 1 для пра,аильного функционирования системы управления необходимо уменьшение времени открытого состояния тиристоров анодной группы, управляющие электроды которых соединены с первым, вторым и третьим выходами формирователя 2, и увеличение времени открытого состояния тиристоров катодной группы, управляющие электроды которых соединены с четвертым,, пятым и шестым выходами формирователя 2. Это обеспечивается тем, что первый вход формирователя 2 через первый выход устройства 1 соединяется с выходом сумматора 7 (фиг. 2) через элемент 10 совпадения, и элемент ИЛИ 14, а второй вход формирователя 2 (фиг. 1) через второй выход устройства 1 соединяется с вы- ходом вычитателя 8 (фиг. 2) через элемент 12 совпадения и элемент ИЛИ 15В результате этого на выходе элемента 40 сравнения (фиг. 4) импульсы разрешения отпирания тиристоров появляются позже, чем они появлялись при отсутствии сигнала управления на первом выходе ЦВМ, а на выходе элемента 41 сравнения раньше. Соответственно пройдя через элементы совпадения 42-47 и формирователи 48-53, они уменьшают время открытого состояния тиристоров анодной группы и увеличат время открытого состояния тиристоров катодной группы. Это отражено сдвигом времени появления импульсов отпирания тиристоров на временных диаграммах (фиг. 5). 3.Наконец, при sign Q О время открытого состояния тиристоров анодной группы должно быть увеличено, а тиристор катодной группы уменьшего. Это обеспечивается соединением первого входа формирователя 2 импульсов управления через элемент ИЛИ 14 (фиг. 2) и элемент 13 совпадения с выходом вычитателя 8, а второго входа формирователя 2 (фиг. 1) через элемент ИЛИ 15 (фиг. 2) и элеПмент 11 совпадения с выходом сумматора 7. В результате на выходе элемента сравнения (фиг. 4) импульсы разрешения отпирания тиристоров появятся раньше, чем они появлялись при отсутствии сигнала управления, с ЦВМ, а на выходе элемента Ц сравнения - позже (фиг. 5). Соответственно время открытого состояния тиристоров анодной группы увеличится, а тиристоров катодной группы уменьшится и направление протекающего через нагрузку тиристорного электропривода тока изменится по сравнению с предыдущим случаем на обратное. В результате использования изобретения устраняется необходимость двойного преобразования сигнала управления, в результате чего повышается ее точность и надежность системы. Формула изобретения 1 . Система управления тиристорны электроприводом, содержащая последо вательно соединенные блок синхронизации, формирователь импульсов упра ления и усилитель мощности, вторые входы блока синхронизации и усилителя мощности подключены к источнику питания, о т л и ч а ю .щ а яс я тем, что, с целью повышения точности и надежности, система содержит устройство вычисления углов отпирания тиристоров, выходы которого подключены к вторым входам фор мирователя импульсов, управления. 2. Система по п. 1, отличающаяся тем, что устройств вычисления углов отпирания тиристоров содержит первый и второй элементы ИЛИ, выходы которого соответственно подключены к выходам устрой ства, первые входы сумматора и выми татёля подсоединены к первому входу устройства, вторые входы - к выходу задатчика кода смещения, выход сумматора соединен с первыми входами первого и второго элементов совпадения, выход вычитателя соединен с первыми входами третьего и четвертого элементов совпадения, вторые входы первого и третьего элементов совпадения соединены с входом первого инвертора и вторым входом устройства, вторые входы второго и четвертого элементов совпадения с выходом первого инвертора, выходы второго и третьего элементов совпадения - с соответствующими входами первого элемента ИЛИ, а выходы первого и четвертого элементов совпадения - с входами второго элемента ИЛИ. 3. Система по п. 1, отличающаяся тем, что блок синхронизации содержит первый фазовый дискриминатор, первый вход которого соединен с вторым входом третьего фазового дискриминатора, с первым входом блока, второй вход первого базового дискриминатора соединен с первым входом второго фазового дискриминатора и с вторым входом блока , второй вход фазового дискриминатора соединен с первым входом третьего фазового дискриминатора и с третьим входом блока, выход первого фазового дискриминатора соединен с входамивторого инвертора, второго элемента выделения переднего фронта импульсов, первым входом пятого и вторым входом девятого элементов совпадения, выход второго фазового дискриминатора соединен с входами третьего инвертора, четвертого элемента выделения переднего фронта импульсов, первым входом шестого и вторым входом десятого элементов совпадения, выход третьего фазового дискриминатора соединен с входом четвертого инвертора, входом шестого элемента выделения переднего фронта импульсов, первым входом седьмого и вторым входом восьмого элементов совпадения, выход второго инвертора соединен с входом первого элемента выделения переднего фронта импульсов, вторым входом шестого и первым входом восьмого элементов совпадения, выход третьего инвертора соединен с входом третьего элемента выделения переднего фронта импульсов, первым входом девятого и вторым входом седьмого элементов совпадения, выход четвертого инвертора соединен с входом пятого элемента выделения переднего фронта импульсов, вторым входом пятого- и первым входом десятого элементов совпадения, выходы первого, третьего, и пятого элементов выделения переднего фронта импульсов соединены через третий элемент ИЛИ с первым входом первого счетчика, а выходы второго, четвертого и шестого элементов выделения переднего фронта иипульсов соединены через третий элемент ИЛИ с первым входом второго счетчика, вторые входы счетчиков соединены с выходом генератора, выходы первого и второго счетчиков подключены соответственно к первому и второму выходам блока, а выходы пятого, шестого, седьмого, восьмого, девятого и десятого элементов совладения соединены соответственно с третьим, четвертым, пятым, шестым, седьмым и восьмым выходами блока.

4, Система по п. 1, .о т л и чающаяся тем, что формирователь импульсов управления содержит первый и второй элементы сравнения, первые и вторые входы которых подключены к соответствующим входам формирователя, первые входы одиннадцатого, двенадцатого, тринадцатого, четырнадцатого, пятнадцатого и шестf f

1

2

надцатого элементов совпадения подключены к соответствующим входам формирователя, выход первого элемента сравнения соединен с вторым

входом одиннадцатого, двенадцатого и тринадцатого элементов совпадения, а выход второго элемента сравнения - с вторыми входами четырнадцатого, пятнадцатого и шестнадцатого элементов совпадения, выхо- , ды каждого элемента совпадения черед соответствующие формирователи им- ;

пульсов соединены с выходами формирователя.

Источники информации, принятые во внимание при экспертизе

t, Найдис В.А. и др. Системы постоянного тока на тиристорах. М.-Л., 1966, с. 58.

8

Ю

/

H

/

12

/3

f 2

/

tfi

г j ii

5 6

7

8 9

W

8

4J

9

50

5i

S

52

4ff

S3

7

fpt/i.ff

Авторы

Даты

1982-06-23—Публикация

1976-06-01—Подача