Изобретение относится к автоматике и вычислительной технике и может быть использовано в АСУТП для сбора информации от аналоговых датчиков.

Целью изобретения является повышение надежности устройства за счет исключения сбоев при одновременном срабатывании входных каналов.

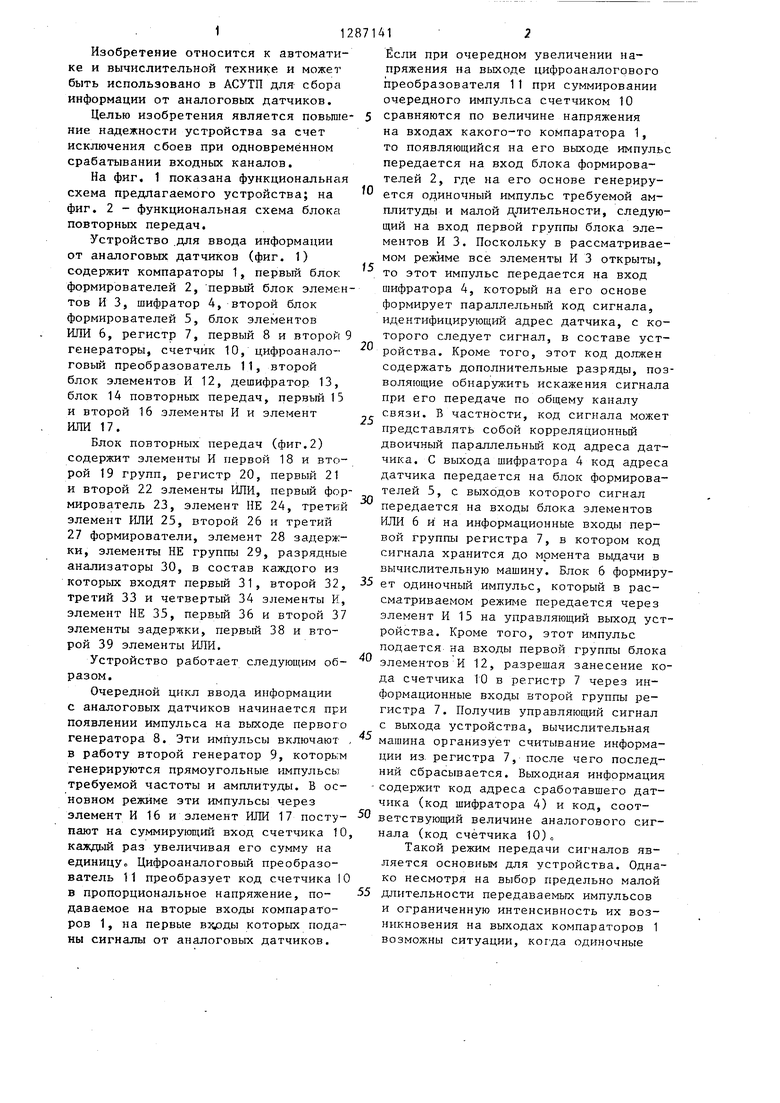

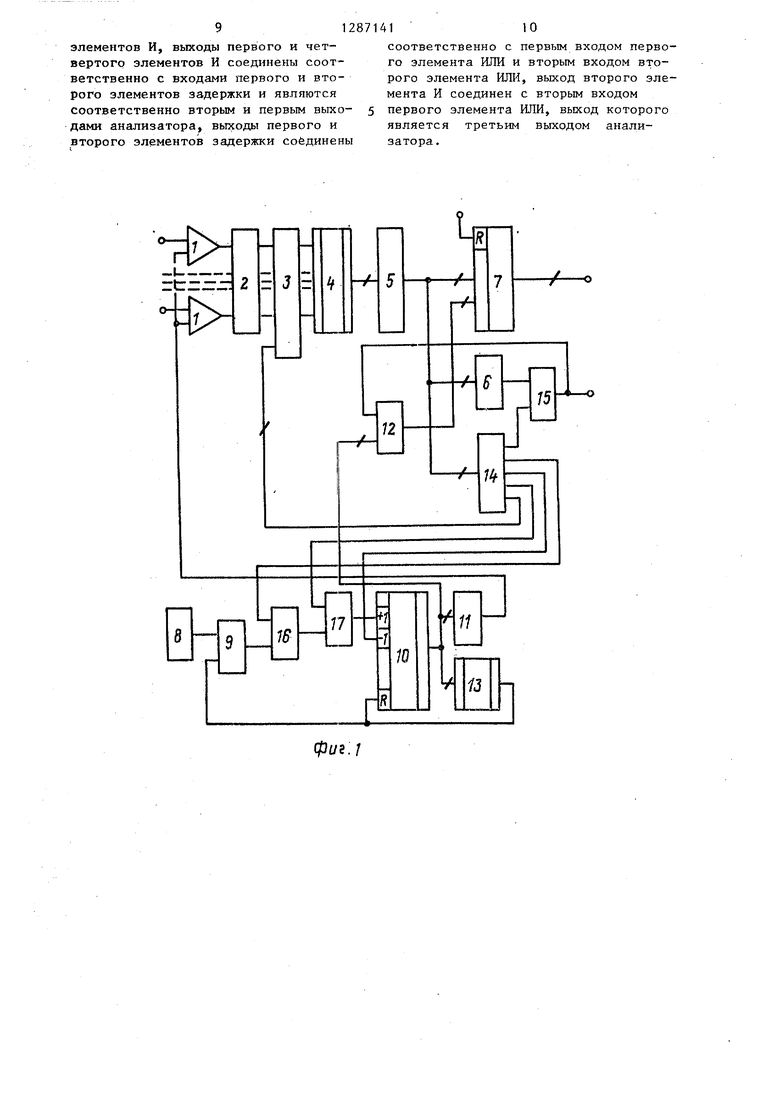

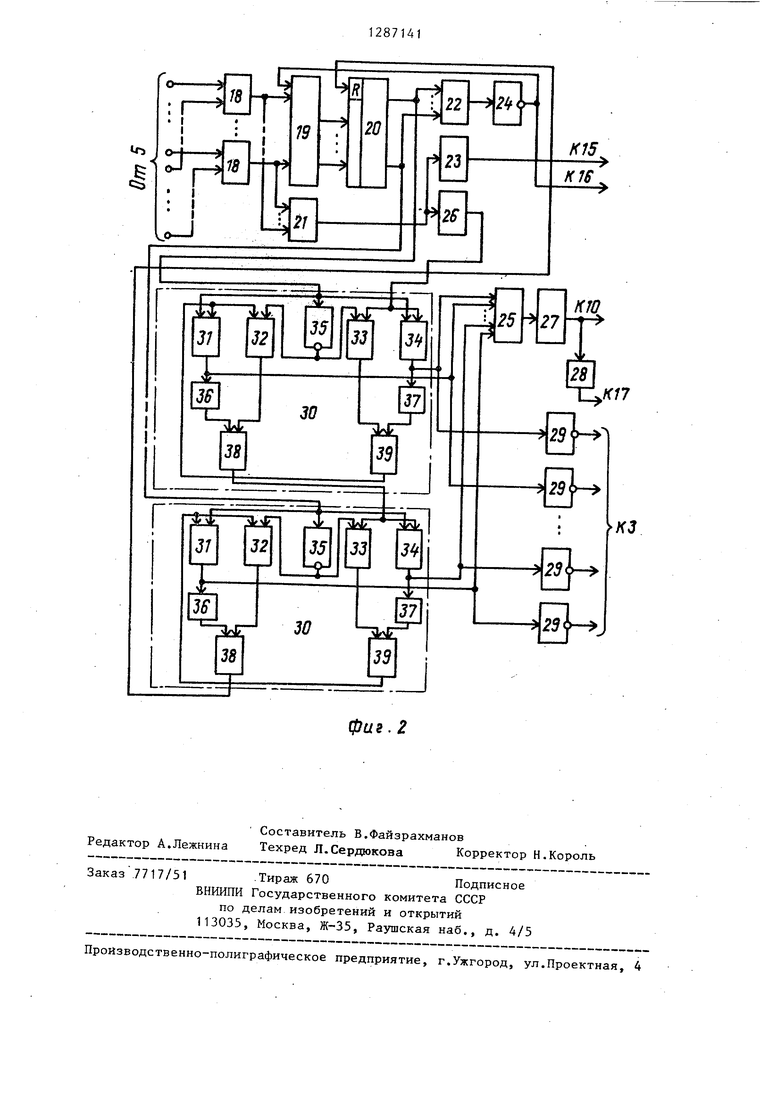

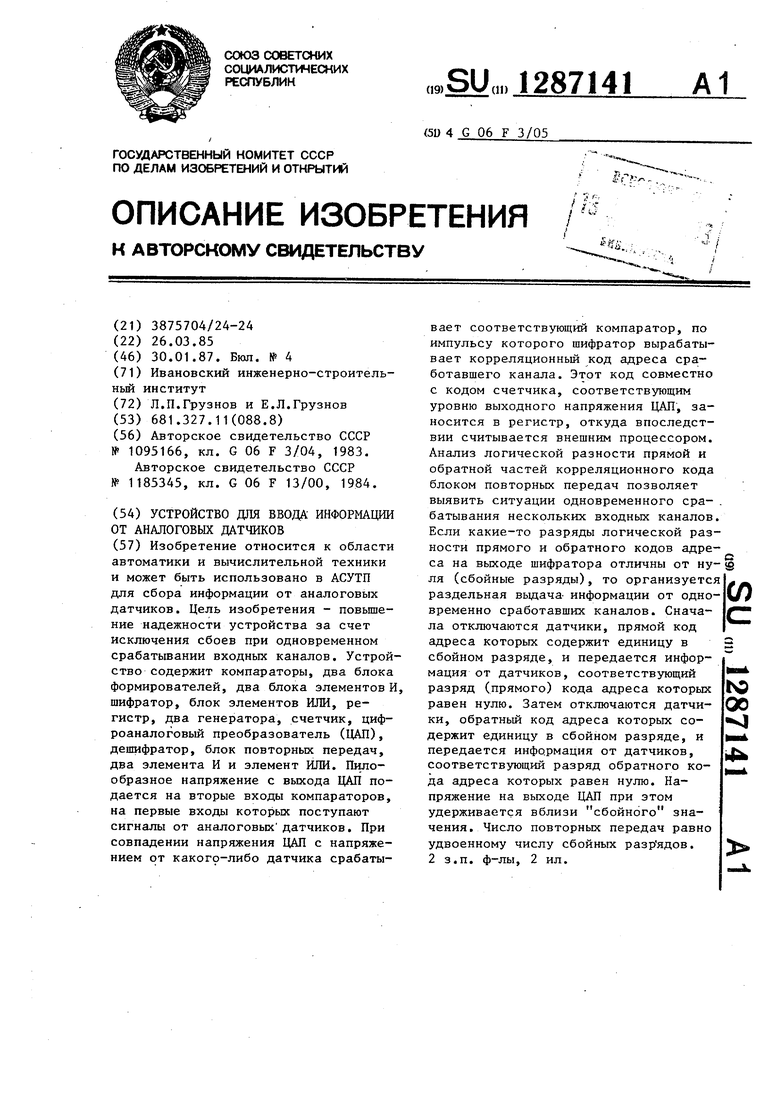

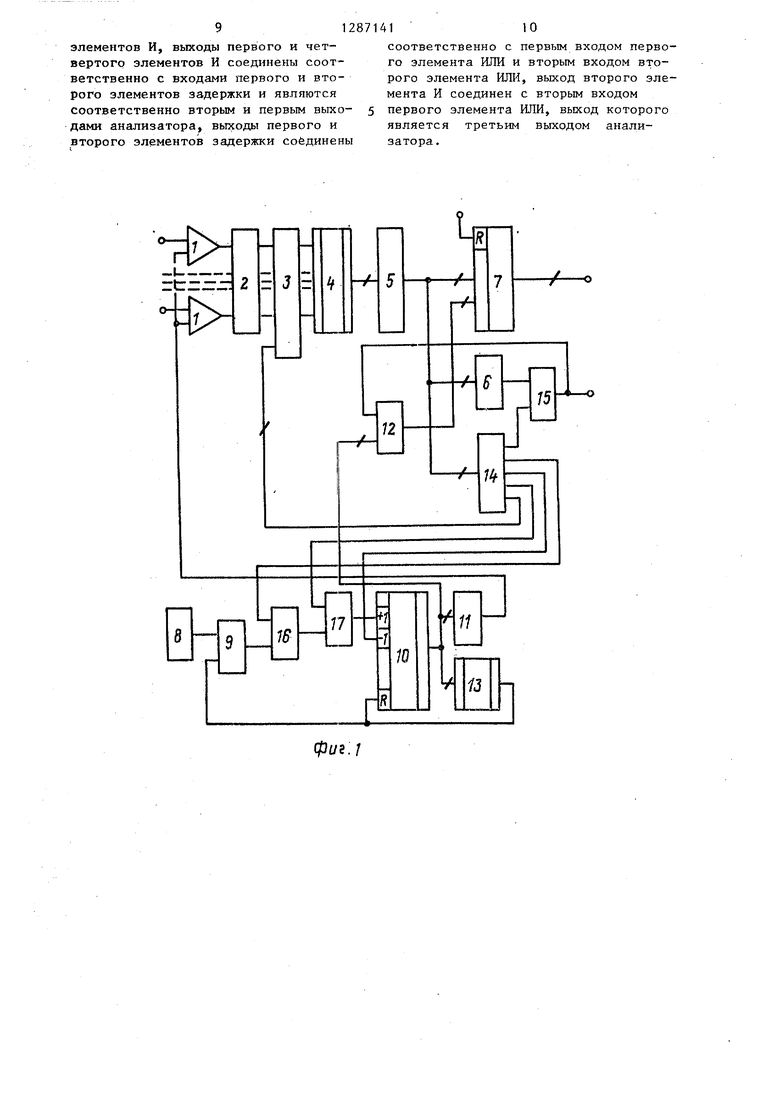

На фиг. 1 показана функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока повторных передач.

Устройство .для ввода информации от аналоговых датчиков (фиг. 1) содержит компараторы 1, первый блок формирователей 2, первый блок элеме:н- тов И 3, шифратор 4, второй блок формирователей 5, блок элементов ИЛИ 6, регистр 7, первый 8 и второй 9 генераторы, счетчик 10, цифроанало- говый преобразователь 11, второй блок элементов И 12, дешифратор 13, блок 14 повторных передач, первый 15 и второй 16 элементы И и элемент ИЛИ 17.

Блок повторных передач (фиг.2) содержит элементы И первой 18 и второй 19 групп, регистр 20, первый 21 и второй 22 элементы ИЛИ, первый формирователь 23, элемент НЕ 24, третий элемент ИЛИ 25, второй 26 и третий 27 формирователи, элемент 28 задержки, элементы НЕ группы 29, разрядные анализаторы 30, в состав каждого из которых входят первый 31, второй 32, третий 33 и четвертый 34 элементы И, элемент НЕ 35, первьй 36 и второй 37 элементы задержки, первый 38 и второй 39 элементы ИЛИ.

Устройство работает следующим образом.

Очередной цикл ввода информации с аналоговых датчиков начинается при появлении импульса на выходе первого генератора 8. Эти импульсы включают , в работу второй генератор 9, которым генерируются прямоугольные импульсы требуемой частоты и амплитуды. В основном режиме эти импульсы через

fO

15

20

25

Если при очередном увеличении напряжения на выходе цифроаналогового преобразователя 11 при суммировании очередного импульса счетчиком 10 сравняются по величине напряжения на входах какого-то компаратора 1, то появляющийся на его выходе импульс передается на вход блока формирователей 2, где на его основе генерируется одиночный импульс требуемой амплитуды и малой длительности, следующий на вход первой группы блока элементов И 3. Поскольку в рассматриваемом режиме все элементы И 3 открыты, то этот импульс передается на вход щифратора 4, который на его основе формирует параллельньш код сигнала, идентифицирующий адрес датчика, с которого следует сигнал, в составе устройства. Кроме того, этот код должен содержать дополнительные разряды, поз воляющие обнаружить искажения сигнала при его передаче по общему каналу связи. В частности, код сигнала может представлять собой корреляционньш двоичный параллельный код адреса датчика. С выхода шифратора 4 код адреса датчика передается на блок формирователей 5, с выходов которого сигнал передается на входы блока элементов ИЛИ 6 и на информационные входы первой группы регистра 7, в котором код сигнала хранится до момента вьщачи в вычислительную машину. Блок б формиру 35 ет одиночный импульс, который в рассматриваемом режиме передается через элемент И 15 на управляющий выход уст ройства. Кроме того, этот импульс подается на входы первой группы блока элементов И 12, разрешая занесение ко да счетчика ТО в регистр 7 через информационные входы второй группы регистра 7. Получив управляющий сигнал с выхода устройства, вычислительная машина организует считывание информации из, регистра 7, после чего последний сбрасывается. Выходная информация содержит код адреса сработавшего датчика (код шифратора 4) и код, соот30

40

45

элемент И 16 и элемент ИЛИ 17 посту- ветствующий величине аналогового сиг- пают на суммирующий вход счетчика 10, нала (код счётчика 10)„

каждый раз увеличивая его сумму на единицу. Цифроаналоговый преобразователь 11 преобразует код счетчика 10 в пропорциональное напряжение, подаваемое на вторые входы компараторов 1, на первые вхрды которых поданы сигналы от аналоговых датчиков.

5

0

5

Если при очередном увеличении напряжения на выходе цифроаналогового преобразователя 11 при суммировании очередного импульса счетчиком 10 сравняются по величине напряжения на входах какого-то компаратора 1, то появляющийся на его выходе импульс передается на вход блока формирователей 2, где на его основе генерируется одиночный импульс требуемой амплитуды и малой длительности, следующий на вход первой группы блока элементов И 3. Поскольку в рассматриваемом режиме все элементы И 3 открыты, то этот импульс передается на вход щифратора 4, который на его основе формирует параллельньш код сигнала, идентифицирующий адрес датчика, с которого следует сигнал, в составе устройства. Кроме того, этот код должен содержать дополнительные разряды, позволяющие обнаружить искажения сигнала при его передаче по общему каналу связи. В частности, код сигнала может представлять собой корреляционньш двоичный параллельный код адреса датчика. С выхода шифратора 4 код адреса датчика передается на блок формирователей 5, с выходов которого сигнал передается на входы блока элементов ИЛИ 6 и на информационные входы первой группы регистра 7, в котором код сигнала хранится до момента вьщачи в вычислительную машину. Блок б формиру- 5 ет одиночный импульс, который в рассматриваемом режиме передается через элемент И 15 на управляющий выход устройства. Кроме того, этот импульс подается на входы первой группы блока элементов И 12, разрешая занесение кода счетчика ТО в регистр 7 через информационные входы второй группы регистра 7. Получив управляющий сигнал с выхода устройства, вычислительная машина организует считывание информации из, регистра 7, после чего последний сбрасывается. Выходная информация содержит код адреса сработавшего датчика (код шифратора 4) и код, соот0

0

5

ветствующий величине аналогового сиг- нала (код счётчика 10)„

Такой режим передачи сигналов является основным для устройства. Однако несмотря на выбор предельно малой длительности передаваемых импульсов и ограниченную интенсивность их возникновения на выходах компараторов 1 возможны ситуации, ког да одиночные

импульсы подаются одновременно на несколько входов шифратора 4. При этом.им формируется код сигнала, в общем случае не совпадающий с кодом ни одного из подлежащих передаче сигналов.

В устройстве искажения такого рода устраняются следующим образом, С выходов блока формирователей 5 код сигнала подается на блок 14 повторных передач. Если результаты анализа разрядных импульсов кода показывают, что сигнал передается неискаженным, то состояние выходов блока 14 повторных передач соответст вует описанному режиму передачи сигналов. Если обнаружится, что переда- вае1.1ый сигнал является следствием наложения нескольких сигналов, то блок 14 повторных передач запрещает его выдачу в вычислительную машину, закрывая элемент И 15, и организует поочередную передачу налагающихся сигналов. При этом закрывается элемент И 16, отключая выход генератора 9 от суммирующего входа счетчика 10, С третьего и четвертого выходов блока 14 поочередно на вычитающий и суммирующий входы счетчика 10 подаются одиночные импульсы, В соответствии с этим и напряжение на выходе цифроаналогового преобразователя 11 то уменьшается, то увеличивается на заданную ступеньку, совершая колебания около того значения, при котором одновременно выдали импульсы несколько компараторов 1. Кроме того, блок 14 повторных передач изменяет потенциалы группы выходов, чтобы поочередно запретить прохождение через блок элементов И 3 части сигналов от компараторов 1, которые по результатам анализа участвовали в образовании искаженного сигнала. Передаваемые при повторной передаче достоверные сигналы следуют в вычис- лительну о машину. Повторная передача организуется по всем кодам, которые могут участвовать в наложении. Коды искаженных при повторной передаче сигналов в вычислительную машину также не передаются. Передача сигналов корреляционным кодом устраняет необходимость очистки первого регистра 7 перед повторной записью.

По окончании повторной передачи, блок 14 выдает разрешающие потенциалы на входы второй группы блока элементов И 3 и на элементы И 15 и 16,

10

-571414

Появление импульсов на третьем и четвертом выходах блока 14 прекращается. Импульсы генератора 9 снова поступают на суммирующий вход счетчика 10,

По мере нарастания суммы в счетчике 10 она достигает максимального значения, при котором появляется управляющее напряжение на выходе дешифратора 13, Этим напряжением кращается работа второго генератора 9 и сбрасывается в нуль содержимое счетчика 10, Закончен очередной цикл передачи, а элементы устройства подготовлены к работе в следующем цикле.

0

5

-5

0

5

0

5

0

5

Работа блока 14 повторных передач заключается в следующем. Если при поступлении кода очередного сигнала на входы блока 14 окажется, что на оба входа какого-то элемента И 18 поданы рабочие импульсы (а это возможно только при искажении сигнала, в частности, из-за наложения нескольких сигналов), то на выходе этого элемента появляется импульс, свидетельствующий об искажении передаваемого сигнала. Каждый такой импульс передается на соответствующий вход элемента ИЛИ 21, а также проходит через соответствующий . открытый в рассматриваемом режиме элемент И 19 на один из информационных входов регистра 20, который запоминает по каким разрядам обнаружены искажения. Появляющийся на выходе элемента ИЛИ 2-1 импульс поступает в формирователи 23 и 25, Формирователь 23 увеличивает его длительность для того, чтобы она бьша достаточна для подавления импульса на управляющем выходе устройства, и вы- дает его на первый выход блока. Элемент ИЛИ 22 вырабатывает сигнал, которьй инвертируется первым элементом НЕ 24 и подается на второй выход блока и на первые входы элементов И 19, запирая их на время повторных передач, в результате сохраняется содержимое регистра 20 при передаче . через устройство искаженных сигналов при некоторых повторных передачах. Формирователь 26 формирует И14пульс, управляющий процессом повторных передач. Длительность этого импульса определяет длительность промежутка времени повторной передачи по каждому отключаемому разряду искаженного кода. Управляющий импульс поступает на второй вход первого разрядного

анализатора 30 (вторые входы элементов И 33 и 34). Если в первом разряде регистра 20 не зафиксировано искажения, то на первый вход первого анализатора 30 поступает уровень логического нуля. В результате элементы И 32 и 33 оказываются открытыми, а элементы И 31 и 34 - закрытыми. Управляющий импульс формирователя 26 проходит через элементы И 33, ИЛИ 39, И 32, ИЛИ 38 на третий выход блока 30, не вызывая повторной передачи по первому разряду, и поступает на второй

111001.Наличие искажения в передаваемом сигнале будет обнаружено в блоке 14 повторньк передач по налич рабочих импульсов в младшем разряде прямого и обратного кодов. Следовавход следующего анализатора 30, кото- рьй работает аналогично. Если на пер- 15 тельно, во второй регистр 20 будет вый вход анализатора 30 поступает записан код 001. Повторная передача уровень логической единицы (соответ- ствующргй разряд искажен), То. элементы И 32 и 33 закрыты, а элементы И 31 и 34 открыты. В результате упоав- ляющий импульс через элемент И 34

20

сигналов будет .осу1дествляться тольк два раза. В первый раз будут отключены выходы компараторов 1, коды ад реса которых содержат единицы в мла шем разряде прямого кода, а во второй раз - имеющие единицы в младшем разряде обратного кода. При первой повторной передаче будет передан до 25 стоверный сигнал шестого датчика, а при.второй - седьмого.

поступает на первый выход разрядного анализатора 30 и через элемент НЕ 29 вращает на выход блока 14 сигнал (нулевой уровень) на отключение датчиков, имеющих единицу в соответствутаПредлагаемая конструкция блока 14 повторных передач практически полиостью устраняет искажения сигналов

щем разряде прямого кода адреса. Одновременно через элемент ШШ 25 за. пускается формирователь 27 и на третьем и четвертом выходах блока 14 появ- 30 из-за их наложения. Им полностью ляются импульсы, управляющие измеке- устраняются наиболее вероятные нало- нием состояния счетчика 10, Задержан- жения любых двух сигналов и большин- ный элементом 37 управляющий импульс ство многократных наложений. Остаю- через элемент ИЛИ 39 и элемент И 31 . щиеся ситуации, в частности неразли- поступает н.а второй выход разрядного 35 чимая для предлагаемой конструкции анализатора 30, вызывая (через эле:- блока 14 повторных передач ситуация мент НЕ 29) отключение датчиков, передачи сигналов одновременно со имеющих единицу в соответствующем раз- всех семи датчиков, маловероятны. ряде обратного кода адреса, и выра- Изобретение обеспечивает повышение .ботку импульсов на третьем и. четвер- 40 надежности устройства за счет умень- том выходах блока 14. Затем через элемент 36 задержки и элемент ИЛИ 38 управляющий импульс поступает на второй вход следующего анализатора 30,

шения вероятности сбоев при одновременном срабатывании нескольких входных каналов. Обнаружение сбойных ситуаций производится на основе аналикоторый работает аналогично. Импульс 45 за корреляционного кода адреса сработавшего канала (датчика) блоком повторных передач.

с третьего выхода последнего разрядного анализатора 30 сбрасывает регистр 20, завершая режим повторной передачи.

Рассмотрим пример передачи кор- 50 реляционным кодом сигналов при трехразрядных адресах датчиков, т.е. для устройства, контролирующего состояние лишь самих датчиков. Предполояшм,

что одновременно на входы шифратора 455 регистр, блок элементов ИЛИ, два ге- подаются импульсы с шестого и седьмо- нератора, счетчик, цифроаналоговый .го датчиков. каждый из них преобразователь и дешифратор, выход поступал на вход шифратора 4 отдель- которого соединен с входом сброса

Формул.а изобретения

1. Устройство для ввода информаци от аналоговых датчиков, содержащее компараторы, два блока формирователей, два блока элементов И, шифратор

но, то корреляционные коды передаваемых сигналов имели бы вид соответственно для сигнала шестого датчика 110001 и для сигнала седьмого датчика

111000.Каждой единице кода соответствует рабочий импульс в соответствующей разрядной линии. Следовательно, при наложении сигналов рабочие импульсы будут соответствовать коду

111001.Наличие искажения в передаваемом сигнале будет обнаружено в блоке 14 повторньк передач по наличию рабочих импульсов в младшем разряде прямого и обратного кодов. Следовательно, во второй регистр 20 будет записан код 001. Повторная передача

15 тельно, во второй регистр 20 будет записан код 001. Повторная передача

0

сигналов будет .осу1дествляться только два раза. В первый раз будут отключены выходы компараторов 1, коды адреса которых содержат единицы в младшем разряде прямого кода, а во второй раз - имеющие единицы в младшем разряде обратного кода. При первой повторной передаче будет передан до- 5 стоверный сигнал шестого датчика, а при.второй - седьмого.

Предлагаемая конструкция блока 14 повторных передач практически полиостью устраняет искажения сигналов

30 из-за их наложения. Им полностью устраняются наиболее вероятные нало- жения любых двух сигналов и большин- ство многократных наложений. Остаю- щиеся ситуации, в частности неразли- 35 чимая для предлагаемой конструкции блока 14 повторных передач ситуация передачи сигналов одновременно со всех семи датчиков, маловероятны. Изобретение обеспечивает повышение 0 надежности устройства за счет умень-

из-за их наложения. Им полностью устраняются наиболее вероятные нало- жения любых двух сигналов и большин- ство многократных наложений. Остаю- щиеся ситуации, в частности неразли- чимая для предлагаемой конструкции блока 14 повторных передач ситуация передачи сигналов одновременно со всех семи датчиков, маловероятны. Изобретение обеспечивает повышени надежности устройства за счет умень-

шения вероятности сбоев при одновременном срабатывании нескольких входных каналов. Обнаружение сбойных ситуаций производится на основе аналиботавшего канала (датчика) блоком повторных передач.

регистр, блок элементов ИЛИ, два ге- нератора, счетчик, цифроаналоговый преобразователь и дешифратор, выход которого соединен с входом сброса

Формул.а изобретения

1. Устройство для ввода информации от аналоговых датчиков, содержащее компараторы, два блока формирователей, два блока элементов И, шифратор.

712

счетчика и вторым входом второго генратора, к первому входу которого подключен выход первого генератора, выкоцы счетчика соединены с входами дешифратора, входами второй группы второго блока элементов И и входами цифроаналогового преобразователя, выход которого соединен с вторыми входами компараторов, выходы которых соединены с входами первого блока формирователей, выходы которого соеднены с входами первой группы первого блока элементов И, выходы которого соединены с входами шифратора, выходы которого соединены с входами вто- рого блока формирователей, выходы которого соединены с входами блока элементов ИЛИ и информационными входами первой группы регистра, выходы которого являются информационными вы ходами устройства, выходы второго блока элементов И соединены с информ ционньхми входами второй группы регистра, вход сброса которого является управляющим входом устройства, пер- вые входы компараторов являются информационными входами устройства, отличающееся тем, что, с целью повышения надежности устройства за счет исключения сбоев при од новременном срабатывании каналов, устройство содержит блок повторных передач, два элемента И и элемент ИЛ выход которого соединен с суммирующи входом счетчика, выход второго гене- ратора соединен с вторым входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ, входы блока повторных передач объединены с входами блока элемен- тов ИЛИ, выход которого соединен с первым входом первого элемента И, выход которого соединен с входами первой группы второго блока элементов И и является управляющим выходом устройства, первый, второй, третий и четвертый выходы блока повторных передач соединены соответственно с вторым входом первого элемента И, первым входом второго элемента И, вычитающим входом счетчика и первым входом элемента ИЛИ, выходы группы блока повторных передач соединены с входами второй группы первого блока элементов И.

2. Устройство по п. 1, о т л и- чающееся тем, что бло,к повторных передач содержит элементы И первой и второй групп, регистр, эле-

10 150 5 0 0 5 Q

5

418

мент НЕ, три формирователя, три элемента ИЛИ, элемент задержки, элементы НЕ группы и разрядные анализато- ры, входы элементов И первой группы являются входами блока, выходы элементов И первой группы соединены с входами первого элемента ИЛИ и вторыми входами элементов И второй группы, выходы которых соединены с информационными входами регистра, выходы которого соединены с первыми входами соответствующих разрядньк анализаторов и входами второго элемента ИЛИ, выход которого соединен с входом элемента НЕ, выход которого соединен с первыми входами элементов И второй группы и является вторым выходом блока, выход первого элемента ИЛИ соединен с входами первого и второго формирователей, выход первого формирователя является первым выходом блока, выход второго формирователя соединен с вторым входом первого разрядного анализатора, к вторым входам последующих разрядных анализаторов подключены третьи выходы предыдущих, третий вьрсод последнего разрядного анализатора соединен с входом сброса регистра, первьй и второй выходы каждого ра-зрядного анализатора сое- динены с входами соответствующих элементов НЕ группы и соответствующими входами третьего элемента ИЛИ, выход которого соединен с входом третьего формирователя, выход которого соединен с входом элемента задержки и является третьим выходом блока, выход элемента задержки является четвертым выходом блока, выходы элементов НЕ группы являются выходами группы блока.

3. Устройство по ПП.1 и 2, отличающееся тем, что разрядный анализатор содержит четыре элемента И, элемент НЕ, два элемента задержки и два элемента ИЛИ, второй вход первого элемента И объединен с первым входом четвертого элемента И, входом элемента НЕ и является первым входом анализатора, вторые входы третьего и четвертого элементов И объединены и являются в торым входом анализатора, выход элемента НЕ соединен с вторым входом второго элемента И и с первым входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с первыми входами первого и второго

элементов И, выходы первого и четвертого элементов И соединены соответственно с входами первого и второго элементов задержки и являются соответственно вторым и первым выходами анализатора, выходы первого и второго элементов задержки соединены

фуе./

соответственно с первым входом первого элемента ИЛИ и вторым входом второго элемента ИЛИ, выход второго элемента И соединен с вторым входом первого элемента ИЛИ, выход которого является третьим выходом анализатора.

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ ПАРАМЕТРА, В ЧАСТНОСТИ ТЕМПЕРАТУРЫ, НЕОДНОРОДНОЙ СРЕДЫ | 1995 |

|

RU2115098C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2037964C1 |

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1983 |

|

SU1095166A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1978 |

|

SU765798A1 |

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1981 |

|

SU972497A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ ПАРАМЕТРА, В ЧАСТНОСТИ ТЕМПЕРАТУРЫ, НЕОДНОРОДНОЙ СРЕДЫ | 1995 |

|

RU2107900C1 |

| Устройство для контроля параметров | 1990 |

|

SU1795501A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ ПАРАМЕТРА, В ЧАСТНОСТИ ТЕМПЕРАТУРЫ, НЕОДНОРОДНОЙ ФАЗЫ | 1995 |

|

RU2107269C1 |

| Устройство для ввода информации | 1983 |

|

SU1128244A1 |

| Многоканальное устройство для ввода данных в цифровую вычислительную машину | 1980 |

|

SU898411A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в АСУТЛ для сбора информации от аналоговых датчиков. Цель изобретения - повышение надежности устройства за счет исключения сбоев при одновременном срабатывании входных каналов. Устройство содержит компараторы, два блока формирователей, два блока элементов И, шифратор, блок элементов ИЛИ, регистр, два генератора, счетчик, циф- роаналоговый преобразователь (ЦАЛ), дешифратор, блок повторных передач, два элемента И и элемент ИЛИ. Пилообразное напряжение с выхода ДАЛ подается на вторые входы компараторов, на первые входы которых поступают сигналы от аналоговых датчиков. При совпадении напряжения ЦАЛ с напряжением от какого-либо датчика срабатывает соответствующий компаратор, по импульсу которого шифратор вырабатывает корреляционный код адреса сработавшего канала. Этот код совместно с кодом счетчика, соответствующим уровню выходного напряжения ЦАЛ, заносится в регистр, откуда впоследствии считывается внешним процессором. Анализ логической разности прямой и обратной частей корреляционного кода блоком повторных передач позволяет выявить ситуации одновременного ера- . батывания нескольких входных каналов. Если какие-то разряды логической разности прямого и обратного кодов адреса на выходе шифратора отличны от нуля (сбойные разряды), то организуется раздельная выдача информации от одновременно сработавших каналов. Сначала отключаются датчики, прямой код адреса которых содержит единицу в сбойном разряде, и передается информация от датчиков, соответствующий разряд (прямого) кода адреса которых равен нулю. Затем отключаются датчики, обратный код адреса которых содержит единицу в сбойном разряде, и передается информация от датчиков, соответствующий разряд обратного кода адреса которых равен нулю. Напряжение на выходе ЦАП при этом , удерживается вблизи сбойного значения. Число повторных передач равно удвоенному числу сбойных разр ядов. 2 з.п. ф-лы, 2 ил. i (Л 1C 00 ч|

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1983 |

|

SU1095166A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1185345, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-03-26—Подача