Изобретение относится к технике электросвязи и может быть использовано в системах передачи дискретной информации.

Целью изобретения является повышение защищенности передаваемой информации за счет рандомизированной смены частот генераторов импульсов времени в процессе передачи.

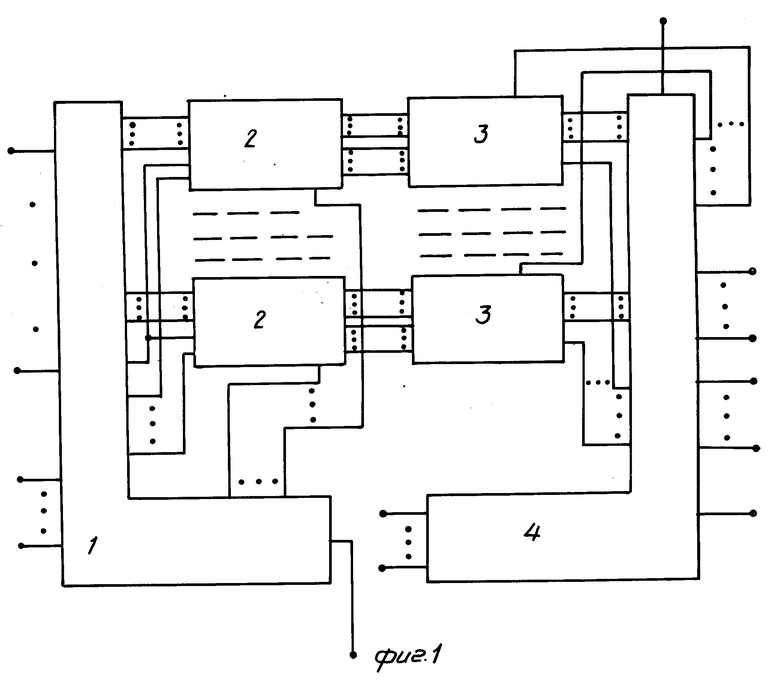

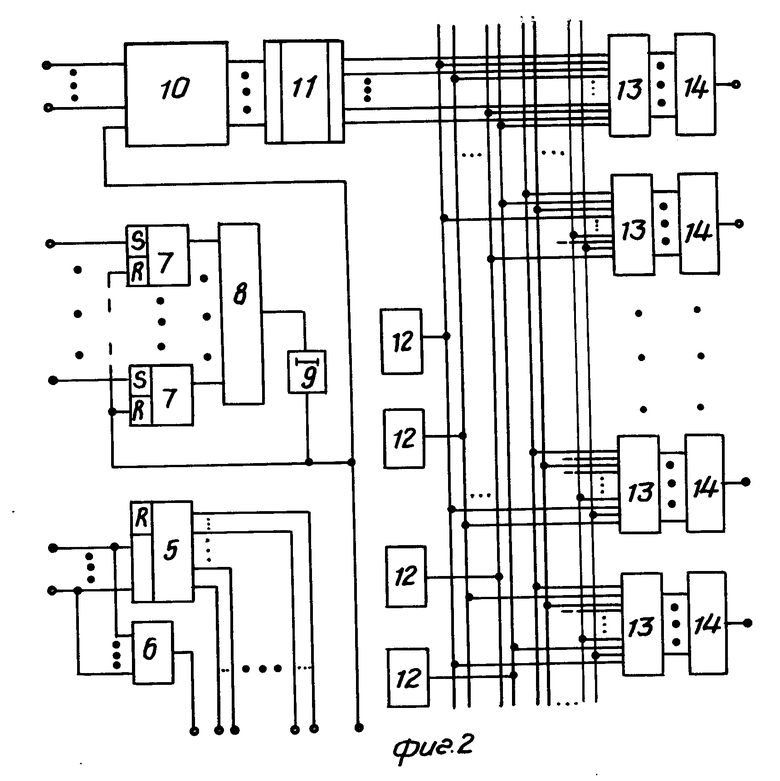

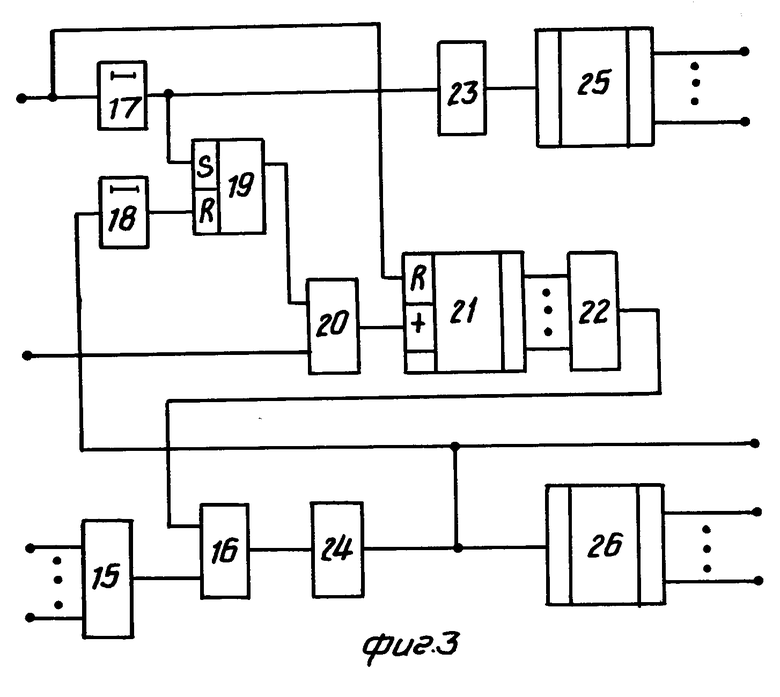

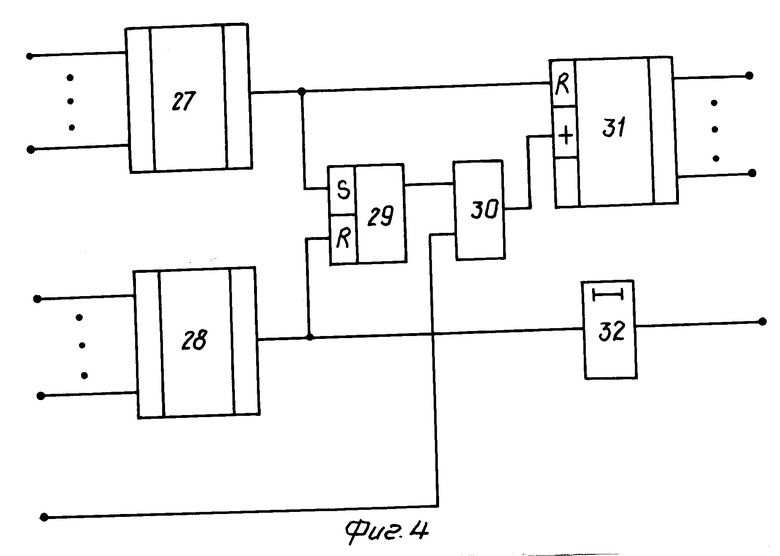

На фиг.1 представлена структурная схема устройства; на фиг.2-5 соответственно структурные схемы блока управления передачей, кодера, декодера и блока управления приемом.

В состав устройства для передачи и приема инфоpмации (фиг.1) входят блок 1 управления передачей, n кодеров 2, m декодеров 3, блок 4 управления приемом.

Блок 1 управления передачей содержит (фиг.2) регистр 5, элемент ИЛИ 6, группу RS-триггеров 7, элемент И 8, элемент задержки 9, вычислительный блок 10, дешифратор 11, p генераторов 12 импульсов времени, n гpупп по n-двухвходовых элементов И 13, n элементов ИЛИ 14.

В состав кодера 2 (фиг.3) входят: первый цифроаналоговый преобразователь 15, компаратор 16, первый и второй элементы задержки 17, 18, RS-триггер 19, элемент И 20, счетчик 21, второй цифроаналоговый преобразователь 22, первый и второй формирователи 23, 24, первый и второй шифраторы 25, 26.

Декодер 3 (фиг.4) содержит первый и второй дешифраторы 27, 28, RS-триггер 29, элемент И 30, счетчик 31, элемент задержки 32.

В состав блока 4 управления приемом (фиг.5) входят группа 33 элементов И считывания, группа RS-триггеров 34, элемент И 35, элемент задержки 36, вычислительный блок 37, дешифратор 38, генераторы 39 импульсов времени, n групп по n двухвходовых элементов И 40, группу из n элементов ИЛИ 41.

Устройство работает следующим образом (фиг.1).

Перед каждой очередной передачей информации в блоки 1 и 4 через дополнительные группы входов устройства (или с клавиатуры вычислительного блока 10 и вычислительного блока 37) вводятся одинаковые числа, неизвестные лицам, не имеющим разрешения на прием передаваемой информации. Этими числами определяются все последующие числа в последовательности генерируемых вычислительными блоками по одинаковым программам формирования псевдослучайных чисел. Этими числами определяются частоты прямоугольных импульсов, выдаваемых с дополнительной группой управляющих выходов блока 1 на дополнительные управляющие входы каждого из кодеров 2 группы и с дополнительной группы управляющих выходов блока 4 на дополнительные управляющие входы каждого из декодеров 3 группы.

Поскольку смена частот осуществляется синхронно по каждой паре кодер 2-декодер 3, то это приводит к изменению псевдослучайным образом масштабов кодовременного в кодерах 2 и временно-кодового в декодерах 3 преобразовании в процессе передачи частичных кодов общего сообщения, что практически полностью исключает несанкционированный прием передаваемой информации.

Передача кода, в частности параллельного двоичного, зашифрованного сообщения осуществляется группами по M разрядов. Каждая очередная группа из М разрядов (частичный код передаваемого сообщения) разбивается на подгруппы из М разрядов, причем k-я подгруппа частичного кода передается с помощью k-ых кодера 2 и декодера 3 группы. Очередной частичный код записывается в блок 1, в котором хранится отведенное на его передачу время. Значение этого кода определяет потенциалы группы информационных выходов блока 1 и потенциалы подключенных к этим выходам группы информационных входов кодеров 2 группы.

Кроме того, блоком 1 в момент приема каждого очередного частичного кода формируется одиночный импульс. С управляющего выхода блока 1 этот импульс поступает на управляющий вход кодеров 2 группы, являясь командой, по которой каждый из кодеров начинает кодовременное преобразование относящегося к нему частичного кода.

В процессе преобразования кодерами 2 используются прямоугольные импульсы, подаваемые с дополнительной группы управляющих выходов блока 1 на дополнительный управляющий вход каждого кодера 2 группы. В процессе преобразования кодер 2 первоначально формирует первый кодовый сигнал, идентифицирующий начало преобразования, а в определяемый в процессе преобразования момент времени второй кодовый сигнал, соответствующий окончанию преобразования. Эти сигналы с первой и второй групп выходов кодера 2 подаются по собственным каналам связи на первую и вторую группы информационных входов декодеров 3.

Кроме того, в момент окончания кодовременного преобразования импульс с управляющего выхода кодера 2 подается на соответствующий вход управляющей группы входов блока 1. После того, как аналогичные импульсы поступят со всех кодеров 2 группы, блок 1 выдает на выход управления передачей импульс, являющийся командой на ввод и в блок 1 очередного частичного кода общего подлежащего передаче сообщения.

В том случае, если на первую и вторую группы информационных входов декодеров 3 поступают требуемые кодовые сигналы, то этим декодером осуществляется обратное временно-кодовое преобразование соответствующей группы разрядов передаваемого частичного кода.

При этом на дополнительный управляющий вход декодера 3 должны подаваться прямоугольные импульсы, частота которых в любой момент времени должна равняться частоте аналогичных импульсов, подаваемых в кодер 2, с которым работает рассматриваемый декодер 3. Эти импульсы на дополнительные управляющие входы каждого из декодеров 3 подаются с дополнительной группой управляющих выходов блока 4.

В результате временно-кодового преобразования на группе информационных выходов декодера 3 окажутся сформированными группа разрядов частичного кода, передаваемая через данный декодер 3, а на группах выходов всех декодеров 3 группы переданный частичный код общего сообщения в виде комбинации разрешающих и запрещающих потенциалов. Эти потенциалы через блок 4 выдаются на первый канальный выход устройства.

Кроме того, при поступлении импульса на управляющий вход блока, импульсный кодовый сигнал, соответствующий принятому частичному коду, выдается на второй канальный выход устройства. В момент окончания формирования обусловленной группы разрядов частичного кода принимаемого сообщения декодером 3, на его управляющем выходе появляется импульс, поступающий на соответствующую группу управляющих входов блока 4.

Как только аналогичные импульсы поступят на всех декодеров 3 группы, блок 4 формирует и выдает на выход управления приемом импульс, разрешающий считывание очередного импульсного кодового сигнала по второму канальному выходу устройства. В это же время в вычислительный блок 10 и вычислительный блок 37 поступают командные импульсы на генерацию очередных псевдослучайных чисел.

Блок 1 управления передачей (фиг.2) работает следующим образом.

Код исходного псевдослучайного числа через i дополнительную информационную группу входов блока 1 вводится в вычислительный блок 10 (или вводится в него с клавиатуры). При этом на выходе этого вычислительного блока появляется определенная комбинация потенциалов, которая передается на входы дешифратора 11, определяя тот его выход, на котором в заданном режиме будет присутствовать разрешающий потенциал. Выходы дешифратора 11 соединены с соответствующими первыми входами каждой из n групп из n двухвходовых элементов И 13. Поэтому при разрешающем потенциале на любом из выходов дешифратора 11 импульсы генераторов 12 импульсов времени, подаваемые на вторые входы каждой из n групп из n двухвходовых элементов И 13, проходят на выход одного из двухвходовых элементов И 13 и далее через соответствующий элемент ИЛИ 14 группы на группу дополнительных управляющих выходов блока 1 управления подач передачей. При каждом изменении положения разрешающего потенциала на выходах дешифратора 11 по новому распределяются частоты импульсов времени на выходах элементов ИЛИ 14 и на группе дополнительных управляющих выходов элемента блока 1.

Очередной записываемый в блок 1 частичный код сообщения, например, в виде парафазного импульсного двоичного кода, подается на входы регистра 5 и элемента ИЛИ 6. Регистр 5 запоминает поступивший код, а его выходные потенциалы через группу информационных выходов блока 1 передаются на информационную группу входов кодеров 2 группы. Элемент ИЛИ 6 на основе разрядных импульсов поступившего сигнала формирует одиночный импульс и выдает его на управляющий выход блока 1 в качестве команды на начало кодовременного преобразования в кодерах 2.

Импульсы с управляющих выходов кодеров 2 через группу управляющих входов блока 1 поступают на S-входы RS-триггеров 7 группы и переводят их в единичное состояние. Как только это произойдет по всем триггерам группы, что свидетельствует об окончании передачи кода частичного сообщения по всем кодерам 2 группы, на всех входах элементов И 8 будут присутствовать разрешающие потенциалы, а следовательно, разрешающий потенциал появится и на выходе этого элемента.

Задержанный на промежуток времени, определяемый параметрами элемента задержки 9 вызванный этим потенциалом перепад напряжения подается на R-входы всех RS-триггеров 7 группы, обнуляя их. Разрешающие потенциалы снимаются со всех входов элемента И 8, и на его выходе появляется запрещающий потенциал. Сформированный на выходе элемента И 8 одиночный импульс передается на управляющий вход вычислительного блока 10 как команда на генерацию очередного псевдослучайного числа. Кроме того, этот импульс выдается на выход управления передачей блока 1, как сигнал на ввод в блок 1 очередного частичного кода передаваемого сообщения.

Работа кодера 2 (фиг.3) заключается в следующем. Первый цифроаналоговый преобразователь 15, на входы которого подводятся потенциалы, характеризующие подлежащий передаче частичный код (группу его разрядов для отдельного кодера 2), формирует на выходе напряжение, пропорциональное подводимому коду, и выдает его на первый вход компаратора 16.

Импульс с управляющего входа кодера 2 передается на обнуляющий вход счетчика 21 и обращает в нуль его содержимое. Одновременно он поступает на вход первого элемента задержки 17, которым задерживается на время переходных процессов в счетчике 21. После этого он передается на S-вход RS-триггера 19 и переводит его в единичное состояние. Кроме того, этот импульс следует на вход первого формирователя 23, которым формируется одиночный импульс требуемой формы. Этот импульс поступает на вход первого шифратора 25, который на его основе формирует кодовый сигнал, выдаваемый на первую группу информационных выходов кодера 2 и идентифицирующий начало формируемого при передаче промежутка времени.

Код этого сигнала содержит адрес кодера в группе и номера группы информационных выходов кодера 2. Разрешающим потенциалом, возникающим на выходе перешедшего в единичное состояние RS-триггера 19, открывается по первому входу элемент И 20. Прямоугольные импульсы с дополнительного управляющего кодера 2, проходя через элемент И 20, поступают на счетный вход счетчика 21 и суммируются им. Напряжение на выходе второго цифроаналогового преобразователя 22, управляемого по входам выходными потенциалами счетчика 22, пропорционально значению кода счетчика 21, т.е. количеству импульсов, поступивших на счетный вход счетчика за время кодовременного преобразования. Поэтому оно становится равным выходному напряжению первого цифроаналогового преобразователя 15, тогда, когда код счетчика 21 станет равным коду разрядов частичного кода передаваемого сообщения, передача которого осуществляется через рассматриваемый кодер 2.

Контроль наступления равенства осуществляется компаратором 16, который сравнивает выходные напряжения первого и второго цифроаналоговых преобразователей 15 и 22. В момент равенства этих напряжений на выходе компаратора 16 появляется разрешающий потенциал, под воздействием которого второй формирователь 24 генерирует одиночный импульс требуемой формы. Этот импульс передается на второй шифратор 26, которым формируется импульсный кодовый сигнал, идентифицирующий окончание кодовременного преобразования, выдаваемый на вторую группу информационных выходов кодера 2. Кроме того, импульс с выхода второго формирователя выдается на управляющий выход кодера 2, как сигнал в блок 1, и на вход второго элемента задержки 18. Через промежуток времени, достаточный для окончания переходных процессов, связанных с выдачей сигналов из кодера 2, импульсом с выхода второго элемента задержки 18 на R-вход RS-триггера 19, этот триггер переводится в нулевое состояние. Запрещающим потенциалом с выхода триггера 19 элемент И 20 запирается по первому входу. Поступление импульсов на счетный вход счетчика 21 прекращается. Цикл передачи кодером 2 заканчивается.

В процессе передачи сообщения в декодере 3 (фиг.4) происходят следующие процессы. При каждом поступлении на первую и вторую группы информационных входов декодера 3 требуемых кодовых импульсных сигналов на выходах или первого дешифратора 27 или второго дешифратора 28 формируются одиночные импульсы. При приеме очередной группы разрядов передаваемого частичного кода сначала поступает импульсный кодовый сигнал на первую информационную группу входов декодера 3. Если код сигнала соответствует обусловленному, то первый дешифратор 27 формирует одиночный импульс, которым обнуляется счетчик 31 и в единичное состояние переводится RS-триггер 29. Разрешающим потенциалом с его выхода открывается по первому входу элемент И 30, и прямоугольные импульсы требуемой частоты с дополнительного управляющего входа декодера 3 проходят через него на счетный вход счетчика 31 и суммируются им.

При появлении импульсного заданного кодового сигнала на второй информационной группе входов декодера 3 импульсом с выхода второго дешифратора 28 обнуляется RS-триггер 29. Появляющимся запрещающим потенциалом с его выхода запирается по первому входу элемент И 30. Импульсы на счетный вход счетчика 31 в этом цикле передачи более не проходят. Потенциалы на выходах счетчика 31, отображающие группу разрядов принятого частичного кода общего сообщения, выдаются на группу информационных выходов декодера 3. Импульс с выхода второго дешифратора 28 одновременно подается на вход элемента задержки 32, в котором задерживается на время переходных процессов в счетчике 31. После этого он выдается на управляющий выход декодера 3 как сигнал об окончании очередного цикла приема сигнала декодером 3.

Работа блока 4 управления приемом (фиг.5) заключается в следующем.

Выходные потенциалы группы информационных выходов каждого из декодеров 3 через группу информационных входов блока 4 выдаются непосредственно на первую группу информационных выходов блока, представляющих собою одновременно первый канальный выход устройства. Кроме того, они передаются на группу входов элемента И считывания 33. При подаче управляющего импульса на вход управления приемом блока 4 он передается на вход считывания группы элементов И считывания 33, и с ее группы выходов в виде импульсного кодового сигнала выдается на вторую группу информационных выходов блока 4, представляющую собой второй канальный выход устройства. Импульсы, поступающие с управляющих выходов декодеров 3 группы, через соответствующие входы группы управляющих входов блока 4 передаются на S-входы RS-триггеров 34 группы, переводя их в единичное состояние.

Как только в единичное состояние будут переведены все триггеры группы, т.е. закончится прием очередного частичного кода, на всех выходах триггеров, а следовательно, на всех входах элемента И 35 появятся разрешающие потенциалы. На выходе элемента И 35 также сформируется разрешающий потенциал, который передается на вход второго элемента задержки 36. Через промежуток времени, определяемый параметрами этого элемента, он выдается на R-входы всех RS-триггеров 34 группы и обнуляет их. На выходах этих триггеров и элемента И 35 появляются запрещающие потенциалы, а на выходе элемента задержки 36 формируется прямоугольный импульс заданной длительности.

Этот импульс выдается на выход управления приемом блока 4, как команда на считывание поступившего частичного кода, и на управляющий вход вычислительного блока 37, инициируя выдачу очередного в последовательности псевдослучайного числа (как и в блоке 1 исходное псевдослучайное число вводится в вычислительный блок 37 через дополнительную группу информационных входов устройства и блока 4 или через клавиатуру вычислительного блока 37 при ее наличии).

После формирования очередного псевдослучайного числа на выходе вычислительного блока 37 появляется новая комбинация потенциалов, которая передается на входы дешифратора 38, определяя его выход, на котором в возникшем режиме будет присутствовать разрешающий потенциал. Выходы дешифратора 38 соединены с соответствующими первыми входами каждой из n групп из n двухвходовых элементов И 40. Поэтому при разрешающем потенциале на любом из выходов дешифратора 38 импульсы генераторов 39 импульсов времени, подаваемые на вторые входы каждого из n двухвходового элемента И 40 каждой из n групп таких элементов, проходит на выход одного из двухвходовых элементов И 40 в группе и далее на соответствующий вход собственного для группы элементов И 40 одного элемента ИЛИ 41 из группы в n элементов. Выходы элементов ИЛИ 41 группы соединены с соответствующими выходами группы дополнительных управляющих выходов блока 4. При каждом изменении положения разрешающего потенциала на выходах дешифратора 38 по новому распределяются частоты импульсов времени на выходах группы элементов ИЛИ 41 и на группе дополнительных управляющих выходов блока 4.

Нормальная работа устройства будет иметь место только в том случае, если на дополнительные управляющие входы работающих совместно пар кодер 2-декодер 3 подаются прямоугольные импульсы одинаковой частоты: только в этом случае будет правильно осуществляться преобразование кода во временной промежуток и временного промежутка в группы разрядов частичного кода передаваемого сообщения по каждой паре кодер 2-декодер 3. Это достигается, во-первых, идентичностью схем подачи импульсов на дополнительные управляющие входы кодеров 2 и декодеров 3, во-вторых, равенством частот генераторов в блоках управления передачей и приемом (попарно) и, в-третьих, идентичностью программ формирования псевдослучайных чисел и исходных чисел, на основе которых формируются последовательности.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ ПАРАМЕТРА, В ЧАСТНОСТИ ТЕМПЕРАТУРЫ, НЕОДНОРОДНОЙ СРЕДЫ | 1995 |

|

RU2107900C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ ПАРАМЕТРА, В ЧАСТНОСТИ ТЕМПЕРАТУРЫ, НЕОДНОРОДНОЙ ФАЗЫ | 1995 |

|

RU2107269C1 |

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1983 |

|

SU1095166A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1096634A2 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1287141A1 |

| Устройство для ввода информации | 1983 |

|

SU1128244A1 |

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ ПАРАМЕТРА, В ЧАСТНОСТИ ТЕМПЕРАТУРЫ, НЕОДНОРОДНОЙ СРЕДЫ | 1995 |

|

RU2115098C1 |

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1981 |

|

SU972497A1 |

| Измеритель вязкости жидкости | 1986 |

|

SU1318846A1 |

| Устройство для контроля параметров | 1990 |

|

SU1795501A1 |

Использование: в технике электосвязи, в системах передачи дискретной информации. Цель - повышение защищенности передаваемой информации от несанкционированного приема за счет рандолизированной смены частот генераторов импульсов времени в процессе передачи. В состав устройства для передачи и приема информации входят блок управления передачей, n кодеров, m декодеров, блок управления приемом. Блок управления передачей содержит регистр, элемент ИЛИ, группу RS-триггеров, элемент И, элемент задержки, вычислительный блок, дешифратор, p генераторов, m двухвходовых элементов и группу n элементов ИЛИ. В состав кодера входят первый цифроаналоговый преобразователь (ЦАП), компаратор, первый элемент задержки, второй элемент задержки, RS-триггер, элемент И, счетчик, второй ЦАП, первый формирователь, второй формирователь, первый и второй шифраторы. Декодер содержит первый и второй дешифраторы и, RS-триггер, элемент И, счетчик, элемент задержки. В состав блока управления приемом входят шесть элементов И, группа RS-триггеров, элемент И, элемент задержки, вычислительный блок, шифратор, p генераторов, m элементов И, m элементов ИЛИ. Сущность - повышает защищенность передаваемой устройством ниформации от несанкционированного чтения. 5 ил.

УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ, содержащее на передающей стороне последовательно соединенные блок управления передачей и n кодеров, а на приемной стороне последовательно соединенные m декодеров и блок управления приемом, причем k информационных входов блока управления передачей являются информационным входом устройства, при этом группы информационных входов и управляющие входы каждого из n кодеров соединены с соответствующей группой информационных выходов блока управления передачей и подключены к управляющему его выходу соответственно, управляющий выход каждого кодера подключен к соответствующему управляющему входу блока управления передачей, информационные выходы n кодеров соединены с информационными входами m декодеров (n= m), управляющий выход каждого декодера соединен с соответствующим управляющим входом блока управления приемом, группы информационных выходов декодеров соединены с соответствующими информационными группами входов блока управления и приемом, а q-й и g-й информационные выходы и выход управления приемом блока управления приемом и выход управления передачей блока управления передачей образуют соответственно первый и второй канальные выходы и выходы управления приемом и передачей устройства, отличающееся тем, что, с целью повышения защищенности передаваемой информации за счет рандомизированной смены частот генераторов импульсов времени в процессе передачи на передающей и приемной сторонах, i информационных входов блока управления передачей и J информационных входов блока управления приемом образуют дополнительные информационные входы устройства, дополнительный управляющий вход каждого кодера подключен к соответствующему дополнительному выходу блока управления передачей, дополнительный вход каждого декодера подключен к соответствующему дополнительному выходу блока управления приемом, блок управления передачей содержит регистр, элемент ИЛИ, группу RS-триггеров, элемент И, элемент задержки, вычислительный блок, дешифратор, группу генераторов импульсов времени, n групп из n двухвходовых элементов И и группу элементов ИЛИ, причем каждый из k входов регистра и элемента ИЛИ соединены между собой и с k входами информационной группы входов блока управления передачей, а выход элемента ИЛИ является управляющим входом блока управления передачей, группа выходов регистра соединена с соответствующими выходами информационных групп выходов блока управления передачей, вход элемента задержки соединен с выходом элемента И, а его выход подключен к соединенным между собой R-входам всех RS-триггеров и управляющим входом вычислительного блока, а также с выходом управления передачей блока управления передачей, выходы RS-триггеров группы соединены с соответствующими входами элемента И, их S-входы подключены к управляющим входам блока управления передачей, информационные входы вычислительного блока являются i-ми информационными входами блока управления передачей, а его выходы подключены к входам дешифратора, первые входы каждого из n двухвходовых элементов И каждой из n групп таких элементов соединены с соответствующими выходами дешифратора, а их вторые входы подключены к выходам соответствующих генератором импульсов времени, выходы каждого двухвходового элемента И в группе подключены к соответствующим входам элементов ИЛИ группы из n элементов, выходы которых образуют группу дополнительных выходов блока управления передачей, каждый кодер содержит первый и второй цифроаналоговый преобразователи, первый и второй элементы задержки, компаратор, RS-триггер, элемент И, счетчик, первый и второй формирователи и первый и второй шифраторы, причем группы входов первого и второго цифроаналоговых преобразователей соединены с информационными входами кодера и выходами счетчика, их выходы подключены к первому и второму входам компаратора соответственно, вход первого элемента задержки соединен с управляющим входом кодера и обнуляющим входом счетчика, а его выход подключен к S-входу RS-триггера и входу первого формирователя, R-вход RS-триггера соединен с выходом второго элемента задержки, а его выход подключен к первому входу элемента И, второй вход которого соединен с дополнительным управляющим входом кодера, а выход подключен к счетному входу счетчика, выход первого формирователя соединен с входом первого шифратора, вход второго формирователя подключен к выходу компаратора, а его выход соединен с входом второго элемента задержки, входом второго шифратора и управляющим выходом кодера, выходы первого и второго шифраторов образуют группу информационных выходов кодера, каждый декодер содержит первый и второй дешифраторы, RS-триггер, элемент И, счетчик и элемент задержки, группы входов первого и второго дешифраторов образуют информационную группу входов декодера, а их выходы подключены соответственно к S-входу RS-триггера и обнуляющему входу счетчика и к R-входу RS-триггера и входу элемента задержки, выход которого является управляющим выходом декодера, первый вход элемента И соединен с выходом RS-триггера, его второй вход является дополнительным управляющим входом декодера, а выход подключен к счетному входу счетчика, выходы которого являются информационной группой выходов декодера, блок управления приемом содержит элемент И, элемент задержки, группу RS-триггеров, группу элементов И считывания, вычислительный блок, дешифратор, n групп из n двухвходовых элементов И, группу генераторов импульсов времени и группу элементов ИЛИ, причем группа информационных входов блока управления приемом соединена с первой группой информационных входов блока управления приемом и входами считывания группы элементов и считывания, выходы которой образуют вторую группы информационных выходов блока управления приемом, а управляющий вход группы элементов И считывания является управляющим входом блока управления приемом, вход элемента задержки соединен с выходом элемента И, а его выход подключен к соединенным между собой R-входам группы RS-триггеров, управляющим входом вычислительного блока и выходом управления приемом блока управления приемом, S-входы группы RS-триггеров соединены с группой управляющих входов блока управления приемом, а их выходы с соответствующими входами элемента И, j информационных входов вычислительного блока являются j информационными входами блока управления приемом, а его выходы подключены к входам дешифратора, первые входы каждого из n двухвходовых элементов И каждой из n групп таких элементов соединены с соответствующими выходами дешифратора, а их вторые входы подключены к выходам соответствующих генераторов импульсов времени, выходы каждого двухвходового элемента И в группе подключены к соответствующим входам элементов ИЛИ группы из n элементов, выходы которых образуют группу дополнительных выходов блока управления приемом.

| РУЧНЫЕ НОЖНИЦЫ ДЛЯ РЕЗКИ МЕТАЛЛА | 2008 |

|

RU2384394C2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-06-19—Публикация

1991-06-17—Подача