Изобретение относится к устройствам измерения среднего значения поля параметра, а именно к устройствам измерения среднего значения температуры участков среды с неоднородным температурным полем, и предназначено для использования в системах контроля окружающей среды и технологических процессов.

Известно устройство для измерения среднего значения температуры участков среды с неоднородным температурным полем [1], содержащее распределенный термопреобразователь, выполненный в виде жгута из n проводных термопреобразователей, первые выводы которых соединены с первыми выводами n генераторов тока, вторые выводы которых соединены соответственно с первыми выводами n резисторов, коммутаторов, выход которого соединен с регистром, а входы подключены к выходам (n-1) развязывающих усилителей, первые входы которых соединены соответственно с вторыми выводами резисторов за исключением последнего резистора, второй вывод которого соединен с входом (n-1)-го развязывающего усилителя и вторым выводом n-го проводного термопреобразователя.

В устройство [1] введены (n-1) дополнительных резисторов, каждый из которых включен между вторыми выводами соответствующих проводных термопреобразователей и резисторов, причем вторые выходы развязывающих усилителей за исключением последнего усилителя соединены соответственно с вторыми выводами проводных преобразователей за исключением первого и последнего, при этом каждый проводной термопреобразователь состоит из прямого и возвратного проводов, а длина каждого К-го проводного термопреобразователя больше длины (К-1)-го проводного термопреобразователя на величину L, равную длине участка усреднения.

При исследовании статических характеристик, в том числе при измерении среднего значения неоднородного поля параметра точность их результатов в существенной мере зависит от числа точек, в которых измеряются значения исследуемого параметра. Это число зависит как от геометрического объема подлежащего исследованию поля, так и дискретностью по расстояниям между точками по координатным осям, в которых должен измеряться параметр. Очень часто желательно число датчиков, которые требуется ввести в измерительную схему, может исчисляться сотнями. Но именно в этих условиях затруднительно применение известного устройства [1] из-за сложности выбора входящих в него элементов и особенно их настройки.

В устройство введены группа компараторов, группа формирователей, группа элементов памяти, первая и вторая группы элементов И, группа элементов задержки, первый и второй генераторы, задатчик, первый и второй элементы И, элемент ИЛИ, элемент памяти, счетчик, цифро-аналоговый преобразователь, группа усилителей считывания, блок контроля, вычислительный блок и индикатор, группа входов которого соединена с группой выходов вычислительного блока, первый и второй входы и выходы i-го компаратора в группе соединен с выходом i-го датчика, выходом цифро-аналогового преобразователя и входом i-го формирователя соответственно, первый и второй и первый и второй выходы i-го элемента памяти соединены с выходом i-го формирователя, выходом i-го элемента задержки, с первым входом i-го элемента И первой группы и с первым входом i-го элемента И второй группы и i-ым входом первого элемента И соответственно, вторяе входы i-ых элементов И первой и второй группы, за исключением первых, соединены между собою и подключены к выходу i-1-го элемента И второй группы, вторые входы первых элементов И первой и второй группы соединены между собою и подключены к выходу первого генератора, i-ый вход элемента ИЛИ соединен с выходом i-го элемента И первой группы и входом i-го элемента задержки, а его выход подключен к входу группы усилителей считывания и первому входу вычислительного блока, первый вход элемента питания памяти соединен с выходом задатчика и обнуляющим входом счетчика, его второй вход подключен к выходу блока контроля и второму входу вычислительного блока, а выход соединен с первым входом второго элемента И, второй и третий входы которого подключены к выходам первого элемента И и второго генератора соответственно, счетный вход счетчика соединен с выходом второго элемента И, а группа его выходов подключена к группам входов цифро-аналогового преобразователя, группы усилителей считывания и блока контроля, группа выходов группы усилителей считывания соединена с группой входов вычислительного блока.

Наличие в предлагаемом устройстве группы новых элементов и новых связей как между ними, так и с элементом, ранее существовавшем в устройстве-прототипе, позволяет утверждать, что заявляемого техническое решение соответствует критерию "новизна" изобретения. Поскольку признаки, отличающие заявляемое техническое решение от прототипа не выявлены и в других технических решениях данной области техники и в смежных областях, то, следовательно, они обеспечивают заявляемому техническому решению соответствие критерию "существенные отличия".

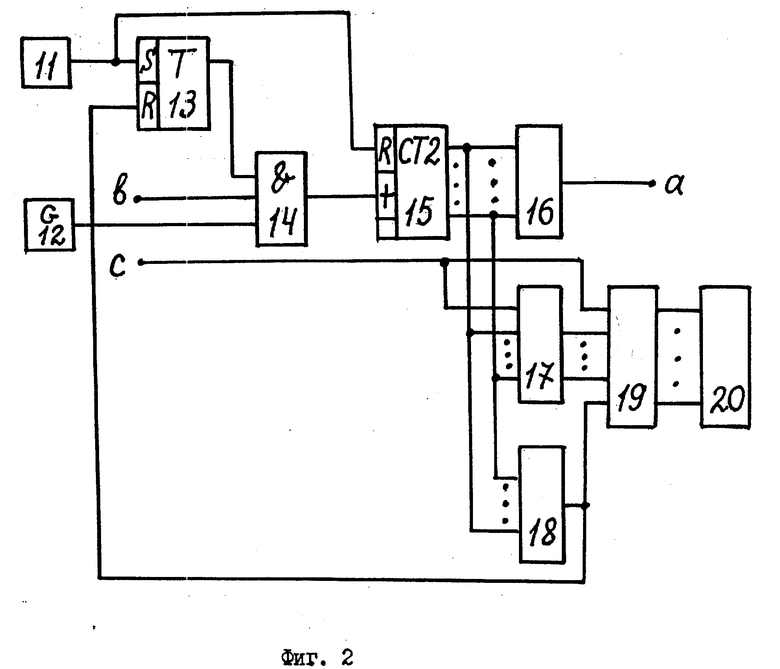

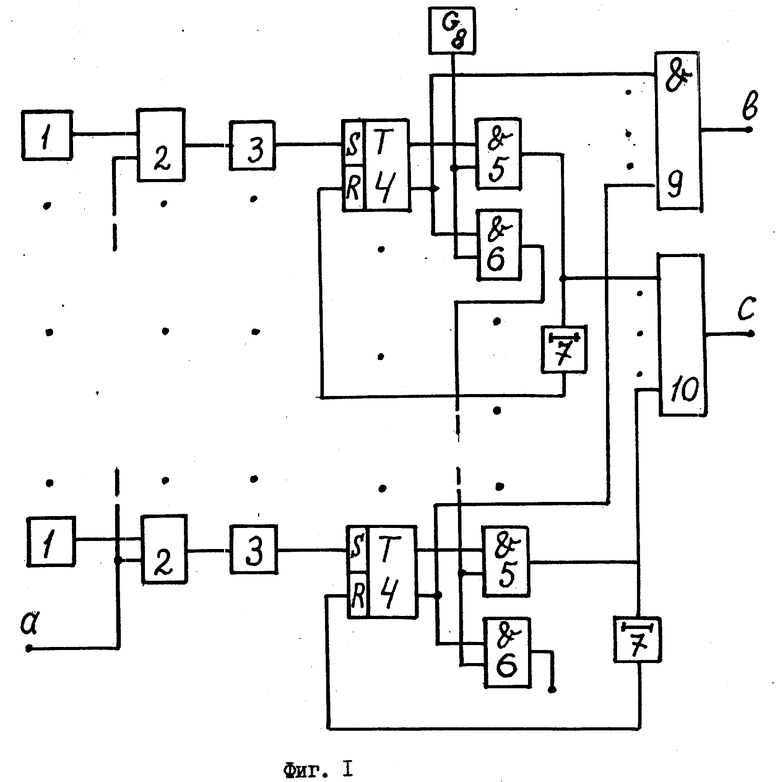

Сущность изобретения поясняется фиг. 1 и фиг. 2, на которых представлены структурные схемы соответственно передающей и приемной частей устройства.

В состав передающей стороны устройства (фиг. 1): группа датчиков 1, преобразующих текучее значение контролируемого параметра, в частности, в пропорциональное напряжение; группа компараторов 2, определяющих моменты времени равенства выходного напряжения, соединенного с компаратором 2 датчика 1, и формируемого изменяющегося напряжения; группа формирователей 3, выдающих импульс малой длительности в момент времени равенства напряжений на входах соответствующих компараторов 2; группа элементов памяти 4, хранящихся сигнал о появлении импульса на выходе соответствующего формирователя 3 до элементов И 5, выдающих очередной сигнал в свободный общий канал связи; вторая группа элементов И 6. передающих импульс считывания в последующую цепь, если связанный с соответствующим элементом И 6 второй группы элемент памяти 4 не содержит подлежащего передаче сигнала; группа элементов задержки 7, задерживающих поступивший на их вход импульс считывания на время выдачи в общий канал связи сигнала связанного с ним элемента памяти 4; первый генератор 8, генерирующий импульсы считывания обусловленной частоты и формы: первый элемент И 9, выдающий на собственный выход разрешающий потенциал, если все элементы памяти 4 группы не хранят подлежащих передаче сигналов; элемент ИЛИ 10, объединяющий выходы всех элементов И 5 первой группы и выдающий очередные подлежащие передачи сигналы в общий канал связи.

На приемной стороне устройства содержит (фиг. 2) задатчик 11 времени начала очередного измерения среднего значения параметра; второй генератор 12, генерирующий импульсы обусловленной частоты и формы; элемент памяти 13, управляющий режимом работы второго элемента И 14; второй элемент И 14, имеющий три входа и пропускающий импульсы второго генератора 12 на собственный выход при наличии разрешающего потенциала на первых двух входах; счетчик 15, увеличивающий на единицу собственный код при поступлении каждого очередного импульса на счетный вход; цифро-аналоговый преобразователь 16, формирующий на выходе аналоговое напряжение, величина которого пропорциональна коду, хранящемуся в счетчике 15; группу усилителей считывания 17, обеспечивающую формирование импульсного кодового сигнала, характеризующего текущее значение кода счетчика 15; блок контроля 18, выдающий командный импульс на прекращение нарастания напряжения на выходе цифро-аналогового преобразователя 16; вычислительный блок 19, суммирующий значения кодов сигналов, поступающих на его группу входов, рассчитывающий измеренное среднее значение параметра в исследуемом поле и управляющий режимом работы индикатора 20; индикатор 20, высвечивающий (выдающий) результат очередного измерения среднего значения параметра в исследуемом поле.

Устройство работает следующим образом (фиг. 1 и 2).

В исходном состоянии перед очередным измерением устройство оказывается или после переходного процесса, связанного с его включением, или после очередного замера среднего значения параметра. При этом в обнуленном состоянии оказывается элемент памяти 13, а в счетчике 15 и в вычислительном блоке 19 хранятся результаты предшествующего измерения. Запрещающим потенциалом с выхода элемента памяти 13 заперт по первому входу второй элемент И 14, на третий вход которого при включенном устройстве постоянно поступают импульсы напряжения с выхода второго генератора 12. Выходные потенциалы счетчика 15 управляют режимом работы цифро-аналогового преобразователя 16, на выходе которого формируется напряжение, пропорциональное коду счетчика 15. Кроме того, выходные потенциалы счетчика 15 подаются на группы входов группы усилителей считывания 17, которые в рассматриваемом режиме сигналов на собственную группу выходов не выдают, и блока контроля 18, на выходе которого формируется разрешающий потенциал. Этим потенциалом удерживается в обнуленном состоянии элемент памяти 13. Индикатор 20 высвечивает значение кода, хранящегося в вычислительном блоке 19. На выходах датчиков 1 группы формируются напряжения, величины которых в частности, пропорциональна текущим значениям контролируемого параметра в соответствующих точках исследуемого поля.

Очередное измерение начинается в момент времени, определяемый настройкой или программой работы задатчика 11, когда на выходе этого задатчика появляется импульс напряжения, являющийся командой на начало выполнения очередного замера. Этот импульс поступает на первый вход элемента памяти 13 и переводит его в единичное состояние. При этом на выходе элемента памяти 13 появляется разрешающий потенциал, которым открывается по первому входу второй элемент И 14. Импульсы с выхода второго генератора 12 начинают проходить через второй элемент И 14 на счетный вход счетчика 15. Импульс с выхода задатчика 11 передается и на обнуляющий вход счетчика, подготавливая его к накоплению очередной суммы.

В процессе очередного цикла измерения счетчик 15 увеличивает на единицу хранящийся в нем код при поступлении на его счетный вход каждого очередного импульса с выхода второго генератора 12. При этом на перепад Δ U возрастает и выходное напряжение цифро-аналогового преобразователя 16, которое в любой текущий момент времени остается пропорциональным хранящемуся в счетчике 15 коду.

Выходные напряжения цифро-аналогового преобразователя 16 подается на вторые входы компараторов 2 группы, на первые входы которых подведены выходные напряжения соответствующих датчиков 1 группы (точки "a" на фиг. 1 и 2 являются общей точкой линии связи, соединяющей выход цифро-аналогового преобразователя 16 вторыми входами компараторов 2 группы).

По мере нарастания напряжения на выходе цифро-аналогового преобразователя 16 в какие-то моменты времени оно становится равным выходному напряжению на выходе какого-либо из датчиков 1 группы. Это приводит к срабатыванию компаратора 2 группы, к первому входу которого подведено выходное напряжение соответствующего датчика 1. На выходе компаратора 2 появляется перепад напряжения, который поступает на вход формирователя 3 группы.

При поступлении перепада напряжения формирователь 3 на его основе формирует импульс напряжения обусловленной формы. Этот импульс следует далее на первый вход соответствующего элемента памяти 4 группы. Этот элемент переходит в единичное состояние, в котором на его первом выходе формируется разрешающий потенциал, а на втором выходе - запрещающий. Запрещающий потенциал второго выхода элемента памяти 4 передается на первый вход соответствующего элемента И 6 второй группы и соответствующий вход первого элемента И 9 и запирает их. Размещающим потенциалом первого выхода элемента памяти 4 открывается по первому входу элемент И 5 первой группы, подключенный к первому выходу этого элемента памяти.

При наличии запрещающего потенциала хотя бы на одном из входов первого элемента И 9 (т.е. тогда, когда хотя бы один из элементов памяти 4 находится в единичном состоянии) на его выходе также формируется запрещающий потенциал, передающийся по каналу связи выхода первого элемента И 9 с вторым второго элемента И 14 (эту линию связи на чертежах фиг. 1 и 2 объединяет точка "b"). Этим потенциалом запирается по второму входу второй элемент И 14. таким образом в те промежутки времени, когда хотя бы в одном из элементов памяти 4 имеется подлежащий передаче сигнал, импульсы второго генератора 12 на счетный вход счетчика 15 не поступают. Этим приостанавливается нарастание выходного напряжения цифро-аналогового преобразователя 16.

Передача сигналов, хранящихся в элементах памяти 4, обеспечивается импульсами с выхода первого генератора 8. Они поступают на вход цепочки из последовательности элементов И 5 и 6 первой и второй групп. Если пара этих элементов управляется элементом памяти 4, находящимся в нулевом состоянии, то импульс вторых входов соответствующих элементов И первой и второй групп через открытый по первому входу элемент И второй группы поступает на вторые входы следующих элементов И 5 и 6 первой и второй групп.

Такое следование очередного импульса с выхода первого генератора 8 продолжается до тех пор, пока он достигается элементов И 5 и 6 первой и второй групп, которые управляются элементом памяти 4, находящимся в единичном состоянии. В этом случае импульс напряжения не может пройти на выход элемента И 6 второй группы, поскольку этот элемент заперт по первому входу запрещающим потенциалом с второго выхода находящегося в единичном состоянии элемента памяти 4.

В рассматриваемом режиме открыт по первому входу связанный с тем же элементом памяти 4 элемент И 5 первой группы. Импульс с напряжения проходит через элемент и передается на соответствующий вход элемента ИЛИ 10. Пройдя через этот элемент на его выход, он следует далее по линии связи (общая точка этой линии на фиг. 1 и 2 обозначена буквой "C") на вход группы усилителя считывания 17 и на первый вход вычислительного блока 19. Кроме того, импульс с выхода элемента И 5 первой группы следует на вход элемента задержки 7, в котором находится до тех пор, пока на выход элемента ИЛИ 10 в линию связи "C" будет выдан импульс напряжения обусловленной длительности. После этого импульс напряжения с выхода элемента задержки 7 следует на второй вход элемента памяти 4 и переводит его в нулевое состояние. Восстанавливаются запрещающий и разрешающий потенциалы, соответственно, на его первом и втором выходах. Запирается по первому входу подключенный к первому выходу элемента памяти 4 элемента И 5 первой группы. Открывается по первому входу элемент И 6 второй группы, соединенный с вторым выходом элемента памяти 4. На входе первого элемента И 9, подключенного к второму выходу элемента памяти 4, восстанавливается разрешающий потенциал, что является сигналом о том, что сигнал с элемента памяти 4 передан.

Если во время появления очередного напряжения на выходе первого генератора 8 все элементы памяти 4 окажутся в нулевом состоянии (подлежащие передаче сигналы отсутствуют), то этот импульс проходит через цепочку последовательно включенных элементов И 6 второй группы и затухает неиспользованным на выходе последнего в цепочке элемента И 6 второй группы.

Импульс напряжения, поступившей по линии связи на вход группы усилителей считывания 17, является командой на перезапись кода счетчика 15 в память вычислительного блока 19. Группа выходов счетчика 15 подает на группу входов группы усилителей считывания 17 потенциальный код этого счетчика 15. Поэтому импульс напряжения, подаваемый на вход группы усилителей считывания 17, обеспечивает формирование импульсного кодового сигнала, идентифицирующего текущего код счетчика 15, который передается на группу входов вычислительного блока 19. По команде импульса на первом входе вычислительного блока 10 этот блок суммирует значение поступающего кода с накапливаемой суммой значений кодов счетчика 15 в моменты поступления сигналов о равенстве значений напряжения на том или ином датчике 1 группы.

Поскольку разрешающий потенциал на выходе элемента памяти 13 сохраняется в течение всего очередного цикла измерения, а следовательно, в течение всего цикла измерения второй элемент И 14 остается открытым по первому входу, режим его работы в цикле измерения определяется напряжением на его втором входе. В моменты времени, когда все элементы памяти 4 группы находятся в нулевом состоянии, т. е. не содержат подлежащих передаче сигналов, на все входы первого элемента И 9 подаются разрешающие потенциалы со вторых входов элементов памяти 4 группы. Формируемый при этом разрешающий потенциал с выхода первого элемента И 9 подводится к второму входу второго элемента И 14, который оказывается открытым по обоим управляющим входам. Поэтому импульсы напряжения с выхода второго генератора 12 проходят через второй элемент И 14 на счетный вход счетчика 15 с перерывами на время передачи сигналов с элементов памяти 4 группы.

Этот процесс продолжается до тех пор, пока будут переданы сигналы со всех датчиков 1 группы и в вычислительном блоке 19 окажется накопленной сумма значений напряжений на выходах всех датчиков 1 группы, оцененных в моменты их равенства с напряжением на выходе цифро-аналогового преобразователя 16. При дальнейшем увеличении кода счетчика 15 наступит момент времени, когда напряжение на выходе цифро-аналогового преобразователя 16 станет заведомо больше любого возможного напряжения на выходах датчиков 1 группы. При достижении кодом счетчика 15 обусловленного значения сработает блок контроля 18, возникающий разрешающий потенциал на выходе которого передается на второй вход вычислительного блока 19 и на второй вход элемента памяти 13. Элемент памяти 13 переходит в нулевое состояние, запирая формируемым на собственном выходе запрещающим потенциалом по первому входу второй элемент И 14. Поступление импульсов второго генератора 12 на счетный вход счетчика 15 прекращается.

Подаваемый на второй вход вычислительного блока 19 импульс напряжения является командой на завершение очередного цикла измерения среднего значения параметра в контролируемом его поле. Для этого осуществляется деление накопительной в вычислительном блоке 19 суммы измеренных напряжений на число датчиков 1 в группе. Частое отделение в виде параллельного потенциального кода через группу выходов вычислительного блока 19 передается на группу входов индикатора 20. Результат замера высвечивается этим индикатором.

Очевидна простота реализации предлагаемого устройства, поскольку все входящие в его элементы серийно выпускаются промышленностью. Элементы памяти 4 и 13 устройства могут быть выполнены, в частности, в виде триггеров, конструкция которых определяется выбранной элементной базой. Блок контроля 18 может представлять собой, например, дешифратор. Вычислительный блок 19 может быть выбран в виде микро - ЭВМ. Если число датчиков 1 в группе кратно 2, то проводимые при измерении вычисления существенно упрощаются, что позволяет вычислительный блок 19 выполнить в виде регистра, способного выполнять процедуры суммирования подаваемых последовательно на его входы потенциальных кодов и сдвиг содержимого разрядов кода на заданное число разрядов. Полный переход при решении задачи измерения среднего значения от программного управления средств на аппаратные средства существенно повышает надежность работы устройства.

Таким образом, предлагаемым техническим решением полностью реализуется задача измерения среднего значения параметра, в частности температуры неоднородной среды, причем в широкой области применений с существенным упрощением технических средств и повышением надежности их работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ ПАРАМЕТРА, В ЧАСТНОСТИ ТЕМПЕРАТУРЫ, НЕОДНОРОДНОЙ ФАЗЫ | 1995 |

|

RU2107269C1 |

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ ПАРАМЕТРА, В ЧАСТНОСТИ ТЕМПЕРАТУРЫ, НЕОДНОРОДНОЙ СРЕДЫ | 1995 |

|

RU2115098C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2037964C1 |

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1983 |

|

SU1095166A1 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1287141A1 |

| Устройство для обнаружения аварийных ситуаций | 1982 |

|

SU1105865A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1096634A2 |

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1981 |

|

SU972497A1 |

| Измеритель вязкости жидкости | 1986 |

|

SU1318846A1 |

| ИЗМЕРИТЕЛЬ УРОВНЯ ЖИДКОСТИ И УРОВНЯ ПЕНЫ НАД ЕЕ ПОВЕРХНОСТЬЮ | 1993 |

|

RU2054632C1 |

Использование: в системах контроля окружающей среды и технологических процессов. Сущность изобретения: устройство содержит группу датчиков, преобразующих текущее значение температуры в напряжение, группу компараторов, группу формирователей, группу элементов памяти, две группы элементов И, группу элементов задержки, два генератора, задатчик времени начала очередного цикла измерения, два элемента И, элемент ИЛИ, элемент памяти, счетчик, цифроаналоговый преобразователь, группу усилителей считывания, блок контроля, вычислительный блок и индикатор. Результат измерения, высвечиваемый индикатором, представляет собой частное от деления накопленной в вычислительном блоке суммы измеренных напряжений на число датчиков в группе. 2 ил.

Устройство для измерения среднего значения параметра, в частности температуры, неоднородной среды, содержащее группу датчиков, отличающееся тем, что в него введены группа компараторов, группа формирователей, группа элементов памяти, первая и вторая группы элементов И, группа элементов задержки, первый и второй генераторы, задатчик, первый и второй элементы И, элемент ИЛИ, элемент памяти, счетчик, цифроаналоговый преобразователь, группа усилителей считывания, блок контроля, вычислительный блок и индикатор, группа входов которого соединена с группой выходов вычислительного блока, первый и второй входы и выход i-го компаратора в группе соединены с выходом i-го датчика, выходом цифроаналогового преобразователя и входом i-го формирователя соответственно, первый и второй входы и первый и второй выходы i-го элемента памяти группы соединены с выходом i-го формирователя, выходом i-го элемента задержки, с первым входом i-го элемента И первой группы, первым входом i-го элемента И второй группы и i-м входом первого элемента И, соответственно, вторые входы i-х элементов И первой и второй группы, за исключением первых, соединены между собой и подключены к выходу (i-1)-го элемента И второй группы, вторые входы первых элементов И первой и второй групп соединены между собой и подключены к выходу первого генератора, i-ый вход элемента ИЛИ соединен с выходом i-го элемента И первой группы и входом i-го элемента задержки, а его выход подключен к входу группы усилителей считывания и первому входу вычислительного блока, первый и второй входы и выход элемента памяти соединены с выходом задатчика и обнуляющим входом счетчика, его второй вход подключен к выходу блока контроля и второму входу вычислительного блока, а выход соединен с первым входом второго элемента И, второй и третий входы которого подключены к выходам первого элемента И и второго генератора соответственно, счетный вход счетчика соединен с выходом второго элемента И, а группа его выходов подключена к группам входов цифроаналогового преобразователя, группы усилителей считывания и блока контроля, группа выходов группы усилителей считывания соединена с группой входов вычислительного блока.

| SU, авторское свидетельство, 1352246, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1998-03-27—Публикация

1995-11-08—Подача