Изобретение относится к электротехнике и электронике и может быть использовано для снижения энергопотребления устройствами, периодически находящимися в режимах Работа и Ожидание.

Цель изобретения - повышение надежности, снижение пртребляемой мощности и расширение функциональных возможностей.

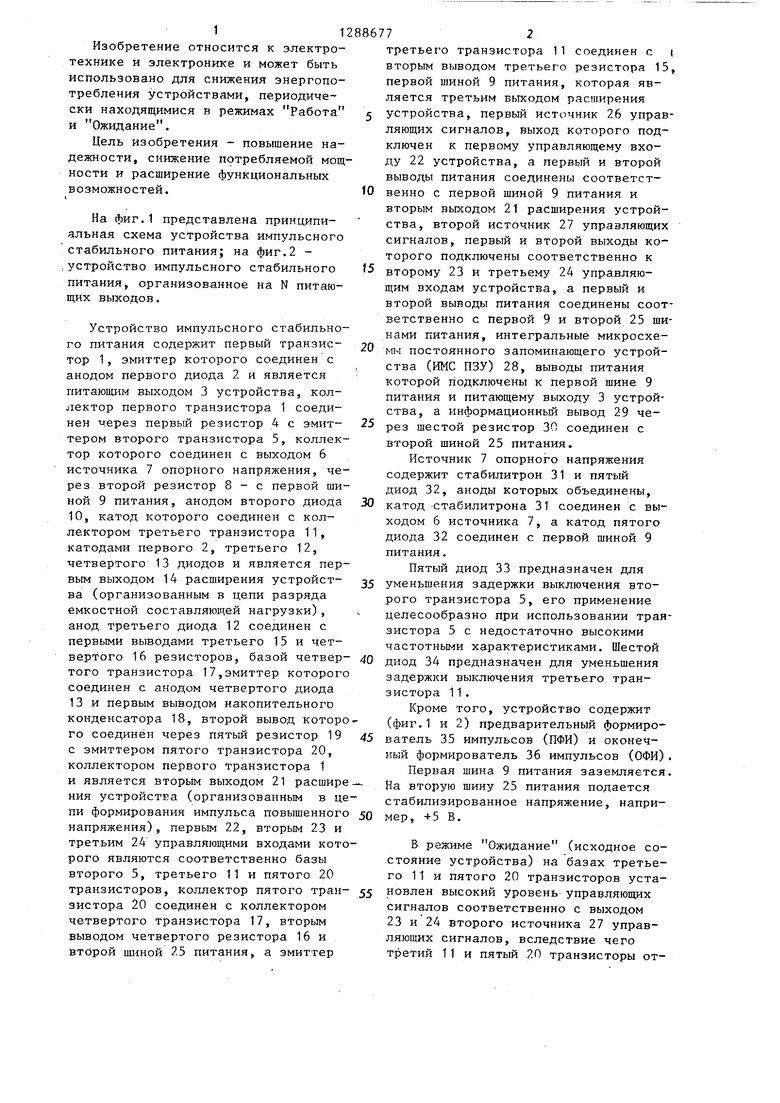

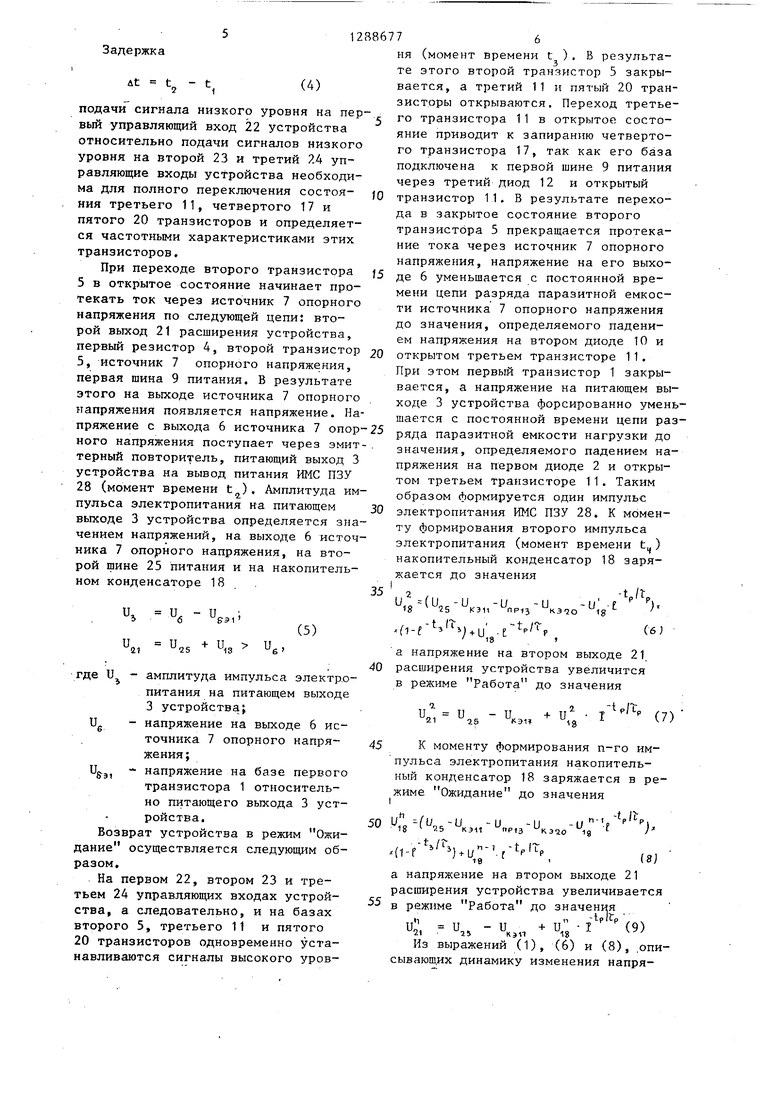

На фиг.1 представлена принципиальная схема устройства импульсного стабильного питания; на фиг.2 - ,устройство импульсного стабильного питания, организованное на N питающих выходов.

Устройство импульсного стабильного питания содержит первый транзистор 1, эмиттер которого соединен с анодом первого диода 2 и является питающим выходом 3 устройства, коллектор первого транзистора 1 соединен через первый резистор 4 с эмиттером второго транзистора 5, коллектор которого соединен с выходом 6 источника 7 опорного напряжения, через второй резистор 8 - с первой шиной 9 питания, анодом второго диода 10, катод которого соединен с коллектором третьего транзистора 11, катодами первого 2, третьего 12, четвертого 13 диодов и является первым выходом 14 расширения устройства (организованным в цепи разряда емкостной составляющей нагрузки), анод третьего диода 12 соединен с первыми выводами третьего 15 и четвертого 16 резисторов, базой четвертого транзистора 17,эмиттер которого соединен с анодом четвертого диода 13 и первым выводом накопительного конденсатора 18, второй вывод которо го соединён через пятый резистор 19 с эмиттером пятого транзистора 20, коллектором первого транзистора 1 и является вторым выходом 21 расшире ния устройства (организованным в цепи формирования импульса повышенного напряжения), первым 22, вторым 23 и третьим 24 управляющими входами которого являются соответственно базы второго 5, третьего 11 и пятого 20 транзисторов, коллектор пятого транзистора 20 соединен с коллектором четвертого транзистора 17, вторым выводом четвертого резистора 16 и второй шиной 25 питания, а эмиттер

третьего транзистора 11 соединен с ( вторым выводом третьего резистора 15, первой шиной 9 питания, которая является третьим выходом расширения

5 устройства, первый источник 26 управляющих сигналов, выход которого подключен к первому управляющему входу 22 устройства, а первый и второй выводы питания соединены соответст0 венно с первой шиной 9 питания и

вторым выходом 21 расширения устройства, второй источник 27 управляющих сигналов, первый и второй выходы которого подключены соответственно к

второму 23 и третьему 24 управляющим входам устройства, а первый и второй выводы питания соединены соответственно с первой 9 и второй 25 шинами питания, интегральные микросхе0 п,1 постоянного запоминающего устройства (ИМС ПЗУ) 28, выводы питания которой подключены к первой шине 9 питания и питающему выходу 3 устройства, а информационный вывод 29 че5 рез шестой резистор 30 соединен с второй шиной 25 питания.

Источник 7 опорного напряжения содержит стабилитрон 31 и пятый диод 32, аноды которых объединены,

0 катод -стабилитрона 31 соединен с выходом 6 источника 7, а катод пятого диода 32 соединен с первой шиной 9 питания.

Пятый диод 33 предназначен для

5 уменьшения задержки выключения второго транзистора 5, его применение целесообразно при использовании транзистора 5 с недостаточно высокими частотными характеристиками. Шестой

0 диод 34 предназначен для уменьшения задержки выключения третьего транзистора 11 .

Кроме того, устройство содержит (фиг.1 и 2) предварительный формиро5 ватель 35 импульсов (ПФИ) и оконечный формирователь 36 импульсов (ОФИ), Первая шина 9 питания заземляется. На вторую шину 25 питания подается стабилизированное напряжение, напри0 мер, +5 В.

В режиме Ожидание (исходное состояние устройства) на базах третьего 1 1 и пятого 20 транзисторов уста- 5 новлен высокий уровень управляющих сигналов соответственно с выходом 23 и 24 второго источника 27 управ- ляюш,их сигналов, вследствие чего третий 11 и пятый 20 транзисторы открыты. Четвертый транзистор 17 закрыт низким уровнем сигнала на его базе, которая подключена к первой шине 9 питания через третий диод 12 и открытый третий транзистор 11. Открытое состояние третьего 11 и пятого 20 транзисторов обеспечивает заряд накопительного конденсатора 18 по следующей цепи: первая шина 9 питания, третий транзистор 11, четвертый диод 13, накопительный конденсатор 18, пятый резистор 19, пятый транзистор 20, вторая шина 25 питания. Накопительный конденсатор 18 заряжается до значения

и,й-(и„-и,„ги„.,,оП -« 1)

напряжение на второй шине 25 питания; напряжение на эмиттере пятого транзистора 20 относительно второй шины 25 питания; - время, в течение которого осуществляется заряд накопительного конденсатора 18; - постоянная времени цепи заряда накопительного конденсатора 18.

том напряжение на втором 1 расширения устройства

и

25

- икэ,о- и,,

(2)

где - падение напряжения на

пятом резисторе 19. Кроме того, открытое состояние третьего транзистора 11 обеспечивает разряд емкостной составляющей нагрузки и паразитной емкости источника 7 опорного напряжения, которые осуществляются следующим образом. Питающий вькод 3 устройства подключен к первой шине 9 питания через первый диод 2, первый выход 1А расширения устройства и третий транзистор 11. В результате этого паразитная емкость нагрузки разряжается до напряжения, не превышающего падение напряжения на первом диоде 2 открытом транзисторе 11, при котором обеспечивается полное отключение 55 ляющем входе 22 устройства, а следовнутренних узлов ИМС ПЗУ 28.

Выход 6 источника 7 опорного напряжения подключен к первой шине 9 питания через второй диод 10, первый выход 14 расширения устройства и открытый транзистор 11. В результате этого паразитная емкость источника 7 опорного напряжения разря:ха- 5 ется до напряжения, не превышающего падение напряжения на первом диоде 2 и открытом транзисторе 11, при котором обеспечивается надежное запирание первого транзистора 1.

Второй транзистор 5 в режиме Ожидание также закрыт высоким уровнем сигнала на его базе, установленным с выхода 22 первого источника 26 управляющих сигналов.

5 В .режиме Работа на втором 23 и третьем 24 управляющих входах устройства, а следовательно, и на базах третьего 11 и пятого 20 транзисторов устанавливаются сигналы низкого

0 уровня (момент времени Ц ). В результате этого третий 11 и пятый 20 транзисторы закрываются. Четвертый транзистор 17 открывается сигналом высокого уровня на его базе, подключен5 ной через четвертый резистор 16 к второй шине 25 питания и отключенной от первой шины 9 питания при закрытом транзисторе 11. При этом заряженный (в режиме Ожидание) на0 копительный конденсатор 18 через открытый четвертый транзистор 17 подключается к второй шине 25, т.е. последовательно и согласно источнику питания, подключенного к шинам 9 и

5 25 питания. Напряжение на втором

выходе 21 расширения устройства увеличивается до значения

ai

U,s-4ov

+ и

-(г

19

(3)

5

0

где tp - время, в течение которого осуществляется разряд накопительного конденсатора 18;

Тр - постоянные времени цепи разряда накопительного конденсатора 18.

Кроме того, при закрытом состоянии третьего транзистора 11 питающий выход 3 устройства и выход 6 источника 7 опорного напряжения отклют чены от первой шины 9 питания. В момент времени t на первом управвательно, и на базе второго транзистора 5 устанавливается сигнал низкого уровня, под действием которого второй транзистор 5 открывается.

Задержка

At t - t,

(4)

подачи сигнала низкого уровня на первый управляющий вход 22 устройства относительно подачи сигналов низкого уровня на второй 23 и третий 24 управляющие входы устройства необходима для полного переключения состояния третьего 11, четвертого 17 и пятого 20 транзисторов и определяется частотными характеристиками этих транзисторов.

При переходе второго транзистора 5 в открытое состояние начинает протекать ток через источник 7 опорного напряжения по следующей цепи: второй выход 21 расширения устройства, первый резистор 4, второй транзистор 5, источник 7 опорного напряжения, первая шина 9 питания. В результате этого на выходе источника 7 опорного напряжения появляется напряжение. Напряжение с выхода 6 источника 7 опорного напряжения поступает через эмит- терный повторитель, питающий выход 3 устройства на вывод питания ИМС ПЗУ 28 (момент времени t). Амплитуда импульса электропитания на питающем выходе 3 устройства определяется значением напряжений, на выходе 6 источника 7 опорного напряжения, на второй шине 25 питания и на накопительном конденсаторе 18 .

и, и, - и

&Э1

(5)

о, + и,,

21

где и - амплитуда импульса электропитания на питающем выходе 3 устройства; и. - напряжение на выходе 6 исD

точника 7 опорного напряжения;

Ug-j, - напряжение на базе первого транзистора 1 относительно питающего выхода 3 устройства.

Возврат устройства в режим Ожидание осуществляется следующим образом.

На первом 22, втором 23 и третьем 24 управляющих входах устройства, а следовательно, и на базах второго 5, третьего 11 и пятого 20 транзисторов одновременно устанавливаются сигналы высокого уровня (момент времени t ). В результате этого второй транзистор 5 закрывается, а третий 11 и пятый 20 транзисторы открываются. Переход третье го транзистора 11 в открытое состояние приводит к запиранию четвертого транзистора 17, так как его база подключена к первой шине 9 питания через третий диод 12 и открытый O транзистор 11. В результате перехода в закрытое состояние второго транзистора 5 прекращается протекание тока через источник 7 опорного напряжения, напряжение на его выхо- 5 де 6 уменьшается с постоянной времени цепи разряда паразитной емкости источника 7 опорного напряжения до значения, определяемого падением напряжения на втором диоде 10 и 0 открытом третьем транзисторе 11.

При этом первый транзистор 1 закрывается, а напряжение на питающем выходе 3 устройства форсированно уменьшается с постоянной времени цепи раз ряда паразитной емкости нагрузки до значения, определяемого падением напряжения на первом диоде 2 и открытом третьем транзисторе 11. Таким образом формируется один импульс 30 электропитания ШС ПЗУ 28. К моменту формирования второго импульса электропитания (момент времени t) накопительный конденсатор 18 заряжается до значения

и.(и,,-и..-и„,-и..,. ).

18 15 КЭ1, ПР13 КЭ70 ig ,-tJT,. .. „-tp/r

(1-f

a напряжение на втором выходе 21 40 расширения устройства увеличится в режиме Работа до значения

Сб;

Uaa - UK.. +

(7)

45 К моменту формирования п-го импульса электропитания накопительный конденсатор 18 заряжается в режиме Ожидание до значения

V-.5-U,,,,-Unp,3-U,3,.

(i-f )..

1 в1

-,-t,ll

) (8)

а напряжение на втором выходе 21 расширения устройства увеличивается 5-5 в режиме Работа до значения ,11 .. .. .. ,-tpitp

U.5 - и,,„ ц, - I

(9)

Из выражений (1), (6) и (8), .опи- сываюш,их динамику изменения напряжения на накопительном конденсаторе 18 в режиме Ожидание, и выражений (3), (7), (9), описывающих динамику изменения напряжения на втором выходе 21 расширения устройства в режиме Работа, можно сделать слдующие выводы. Для обеспечения нормальной работы устройства с малым энергопотреблением на различных, в том числе и на максимальной частоте обращений к ИМС ПЗУ 28, необходимо.

чтобы t р быпо минимально и незави - симо от длительности цикла обращения имело постоянное значение. Минимальное значение определяется временем, необходимым для надежного считывания информации с ИМС ПЗУ 28. Минимальная, но достаточная для нормальной работы устройства (выработки импульса электропитания необходимой амплитуды на питающем выходе 3 устройства), амплитуда импульса по- вьш1енного напряжения на втором выходе 21 расширения устройства определяется отношением tp /t при максимальной частоте обращений, а номинал накопительного конденсатора 18 при этом определяет уровень пульсации напряжения на втором выходе 21 расширения устройства, а также время подготовки устройства к работе после подключения истбчника питания к первой 9 и второй 25 шинам питания .

При возможном коротком замыкании в режиме Работа в цепи питания нагрузки устройство работает следующи образом.

В случае замыкания питающего выхода 3 устройства и первой шины 9 питания накопительный конденсатор 18 разряжается по цепи: первая шина 25 питания, четвертый транзистор

17,накопительный конденсатор 18, второй выход 21 расширения устройства, первый транзистор 1, питающий выход 3 устройства и первая щина 9 питания. При этом ток короткого замыкания, определяемый током в цепи

разряда накопительного конденсатора

18,уменьшается в процессе его разряда и ограничивается по времени.

в результате устройство автоматически отключает дефектную нагрузку, что существенно снижает вероятность выхода из строя его ключевых элементов.

С помощью выходов 9, 14 и 21 расширения устройства число питающих

г

выходов 3 устройства может быть увеличено до необходимого числа N, если БЬфаботка импульсов электропитания на этих выходах должна быть разнесена во времени.

Устройство импульсного стабильного питания, организованное на N

O

0

5

питающих выходов 3 (фиг.2), по сравнению с устройством импульсного стабильного питания на один питающий выход 3 (фиг.1) дополнительно содержит N - 1 ОФИ 36, которые подключены параллельно к соответствующим выходам 9, 14 и 21 расширения устрой5 ства, N - 1 первых источников 26 управляющих сигналов, выходы которых подключены к первым управляющим входам 22 соответствующих N - 1 ОФИ 36, N - 1 ИМС ПЗУ 28, выводы питания которых подключены соответственно к выходам 3 N - 1 ОФИ, 36, а информационные выходы ИМС ПЗУ 28 объединены по схеме Проводное ИЛИ. Такая организация устройства предполагает считывание информации в каждом такте его работы только с одной из N ИМС ПЗУ, что обеспечивается выработкой импульса электропитания только на одном питающем вы0 ходе 3 соответствующего ОФИ 36.При этом остальные N - 1 ОФИ 36 остаются в режиме Ожидание под действием сигналов высокого уровня на их первых управляющих входах 22 и вли5 яния на работу устройства не оказывают, так как не потребляют энергию (первые 1 и вторые 5 транзисторы в режиме Ожидание закрыты). В остальном работа устройства им0 пульсного питания, организованного на питающих выходах 3, не отличается от описанной для устройства на один питающий выход 3.

Таким образом в предлагаемом уст-.

5 ройстве импульсного питания для формирования спада импульса электропитания обеспечены условия, аналогичные известному устройству. I

0 Предлагаемое устройство по срав- нзнию с известным имеет более высокую надежность, достигаемую уменьшением числа источников питания до одного и причем общего с электрони5 кой обрамления, а также уменьшением вероятности выхода из строя ключевых элементов устройства при возможном коротком замыкании в цепи пита- кия нагрузки за счет подключения ее

к источнику питания через накопительный конденсатор.

Потребление энергии в режиме Ожидание устройством, организованным на N питающих выходах, в N раз меньше, поскольку в режиме Ожидание ОФИ энергии не потребляют, а потребление энергии ПФИ примерно такое же как одним известным устройством, имеющим один питающий вьпсод,

Более широкие функциональные возможности достигаются уменьшением числа источников питания устройства до одного за счет формирования предварительного импульса электропитания повьппенного напряжения, а также за

счет возможности наращивания питающих выходов устройства до необходимого числа при минимальных дополнительных затратах оборудования и -без увеличения потребляемой устройством мощности.

Формула изобретения

1. Устройство импульсного стабильного питания функциональных блоков электронно-вычислительных машин, содержащее три транзистора, источник опорного напряжения, первый диод, два резистора и шину питания, причем первый вывод первого резистора соединен с эмиттером второго транзистора, первый вывод второго резистора соединен с базой первого транзистора, эмиттер которого соединен с анодом первого диода и является питающим выходом устройства, а второй, вывод второго резистора соединен с общей шиной, отличающее с я тем, что, с целью повышения надежности путем обеспечения защиты от перегрузки, по току и улучшения эксплуатационных характеристик путем уменьшения числа источников питания до одного, в него введены четвертый и пятый транзисторы,второй, третий и четвертый диоды,конденсатор, третий, четвертый и пятый резисторы, причем база первого транзистора соединена с выходом источника опорного напряжения, коллектором второго транзистора и анодом второго диода, катод которого соединен

с коллектором третьего транзистора, катодами первого, третьего и четвертого диодов и служит выводом для подключения к разрядной шине нагрузки, анод третьего диода соединен

с первыми выводами третьего и четвертого резисторов и базой четвертого транзистора, эмиттер которого соединен с анодом четвертого диода и первым выводом конденсатора, второй ;вывод которого соединен через пятый резистор с эмиттером пятого транзистора. Коллектором первого транзистора, вторым выводом первого резистора

и является шиной повьш1енного напряжения устройства, первым, вторым и третьим управляющими входами которого являются соответственно базы второго, третьего и пятого транзисторов, коллектор пятого транзистора соединен с коллектором четвертого транзистора, вторым выводом четвертого резистора и шиной питания, а эмиттер третьего транзистора соедийен с вторым выводом третьего резистора и общей шиной, причем первый и второй транзисторы, первый и второй диоды, первый и второй резисторы и источник опорного напряжения

образуют оконечный формирователь

импульсов, а третий, четвертый и пятый транзисторы, третий и четвертый диоды, третий, четвертый и пятый резисторы и конденсатор образуют

предварительный формирователь импульсов, при этом оконечный формирователь импульсов и предварительный формирователь импульсов объединены по шине повышенного напряжения,

общей шине и по выводу, служащему для подключения разрядной шины нагрузки,

2. Устройство по п,1, о т л и - чающееся тем, что, с целью расширения функциональных возможностей путем обеспечения работы на N нагрузок без увеличения потребляемой мощности и при минимальных аппаратурных затратах , в него введено N - 1 аналогичных оконечных формирователей импульсов, объединенных с предварительным формирователем импульсов аналогичным образом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления подключением электропитания | 1987 |

|

SU1427371A2 |

| Электронное устройство | 1986 |

|

SU1334305A2 |

| Формирователь импульсов | 1982 |

|

SU1086418A1 |

| Электронное устройство | 1987 |

|

SU1427518A2 |

| Устройство для управления подключением электропитания | 1985 |

|

SU1302283A1 |

| Зарядный преобразователь | 1987 |

|

SU1450085A1 |

| Устройство контроля технологического процесса сельскохозяйственного агрегата | 1991 |

|

SU1782393A1 |

| Стабилизирующий преобразователь напряжения с защитой | 1989 |

|

SU1682990A1 |

| ИСТОЧНИК ВТОРИЧНОГО ЭЛЕКТРОПИТАНИЯ | 1995 |

|

RU2074492C1 |

| Устройство емкостной гальванической развязки | 1986 |

|

SU1370767A1 |

Изобретение относится к электротехнике, в частности, к источникам электропитания электронно-вычислительных машин. Цель изобретения - повышение надежности, снижение потребляемой мощности и расширение функциональных возможностей. Устройство работает в двух режимах - Ожидание и Работа. Для нормальной работы устройства с малым энергопотреблением необходимо, чтобы время разряда накопительного конденсатора 18 tp бьшо минимально и независимо от длительности цикла обращения,было постоянным. При коротком замыкании в режиме Работа устройство автоматически, отключает дефектную нагрузку. Устройство может иметь один и N питающих выходов 3. При N выходах 3 устройство содержит N - 1 оконечных формирователей 36 импульсов . Считывание информации происходит только с одной из N интегральных микросхем постоянного запоминающего устройства. Это обеспечивается выработкой импульса электропитания только на одном выходе 3 соответст- ствующего оконечного формирователя 36 импульсов. Остальные N - 1 фор- мирователей 36 остаются в режиме Ожидание. 1 з.п. ф-лы, 2 ил. W ю 00 00 о: 1 фиг.1

| Иканфиев А.Б | |||

| и др | |||

| Канатное устройство для подъема и перемещения сыпучих и раздробленных тел | 1923 |

|

SU155A1 |

| Формирователь импульсов | 1982 |

|

SU1086418A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-02-07—Публикация

1985-04-26—Подача