Изобретение относится к электротехнике и может быть использовано н регулируемых системах вторичного электропитания.

Цель изобретения - расшигрение функциональных возможностей путем формирования дополнительных импульсов электропитания.

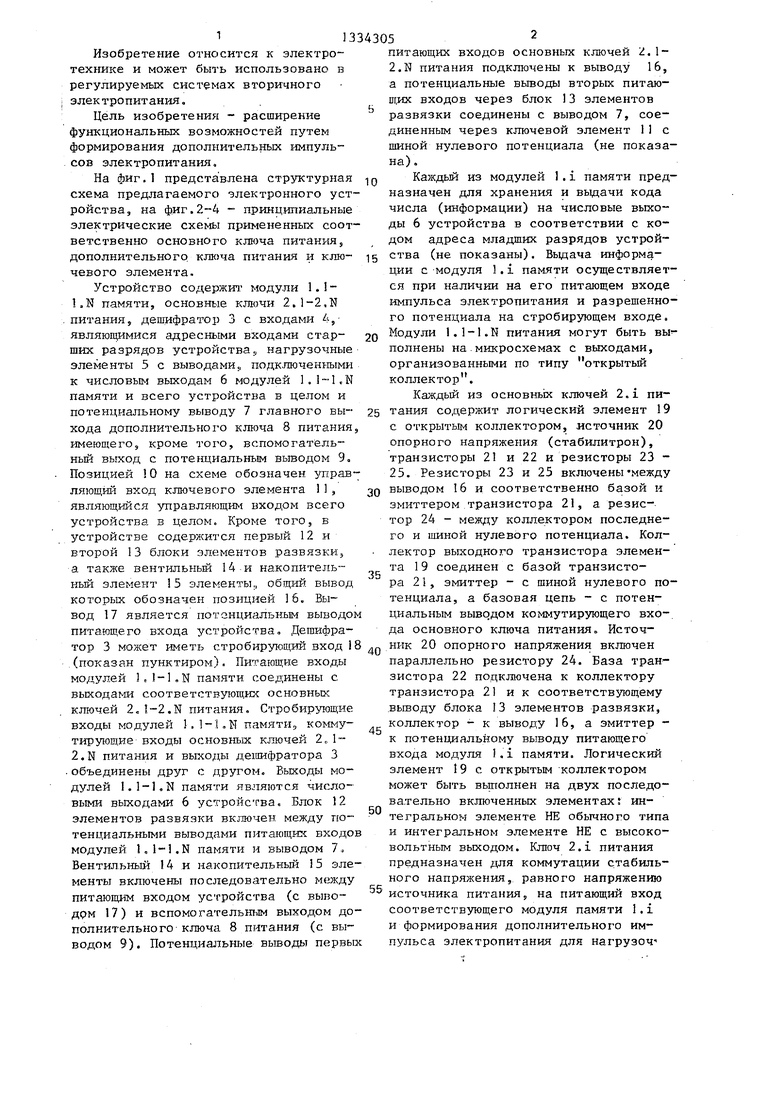

На фиг,1 представлена структурная схема предлагаемого электронного устройства, на фиг.2-4 - принципиальные электрические схемы примененных соответственно основного ключа питания, дополнительного, ключа питания и ключевого элемента.

Устройство содержит модули 1. - .N памяти, основные ключи 2,1-2.N питания, дешифратор 3 с входами i-,- являющимися адресными входами старших разрядов устройства., нагрузочные элементы 5 с выводами,, подк,гаоченными к числовым выходам 6 модулей 1.1-1.N памяти и всего устройства в целом и потенциальному выводу 7 главного выхода дополнительного ключа 8 питания имеющего, кроме того, вспомогательный с потенциальным вьтодом 9, Позицией 0 на схеме обозначен управляющий вход ключевого элемента 11, являющийся управляющим входом всего устройства в целом. Кроме того, в устройстве содержится первый 12 и второй 13 блоки элементов развязки, а. также вентильный 14 и накопительный элемент 15 элементы,, общий вывод которых обозначен позицией 16. Вывод 17 является потенциальным выводо питающего входа устройства о Дешифра

тор 3 может иметь стробирующий вход 18 „ ник 20 опорного напряжения включен

(показан пунктиром). Питающие входы модулей .N памяти соединены с выходами соответствующих основных ключей 2, 1-2.N питания. Стробирующие входы модулей 1,1-l.N памяти, коммутирующие входы основных ключей 2.1 2.N питания и выходы деишфратора 3 объединены друг с другом. Выходы модулей 1.1-,N памяти являются числовыми выходами 6 устройства. Блок 12 элементов развязки включен между потенциальными выводами питающих входов модулей 1,1-,N памяти и выводом 7., Вентильный 14 и накопительный 5 элементы включены последовательно м«укду питающим входом устройства (с дрм 17) и вспомогательшлм выходом дополнительного ключа 8 питания (с выводом 9). Потенциальные выводы первых

45

50

55

параллельно резистору 24. База тран зистора 22 подключена к коллектору транзистора 21 и к соответствующему выводу блока 13 элементов развязки, коллектор - к выводу 16, а эмиттер к потенциальному выводу питающего входа модуля 1,1 памяти. Логический элемент 19 с открытым коллектором может быть вьшолнен на двух последо вательно включенных элементах; интегральном элементе НЕ обычного тип и интегральном элементе НЕ с высоко вольтным выходом. Ключ 2.1 питания предназначен для коммутации стабиль ного напряжения, равного напряжению источника питания, на питающий вход соответствующего модуля памяти 1.1 и формирования дополнительного импульса электропитания для нагрузоч

Q

питающих входов основных ключей 2,- 2.N питания подключены к выводу 16, а потенциальные выводы вторых питающих входов через блок 3 элементов развязки соединены с выводом 7, соединенным через ключевой элемент 11 с шиной нулевого потенциала (не показана).

Каждьй из модулей 1.i памяти предназначен для хранения и выдачи кода числа (информации) на числовые выходы 6 устройства в соответствии с кодом адреса младших разрядов устрюй- 5 ства (не показаны). Выдача информации с -модуля .1 памяти осуществляется при наличии на его питающем входе импульса электропитания и разрешенного потенциала на стробирующем входе. Модули 1,1-l.N питания могут быть вы

0

5

0

5

полнены на микросхемах с выходами, организованными по типу открытый коллектор.

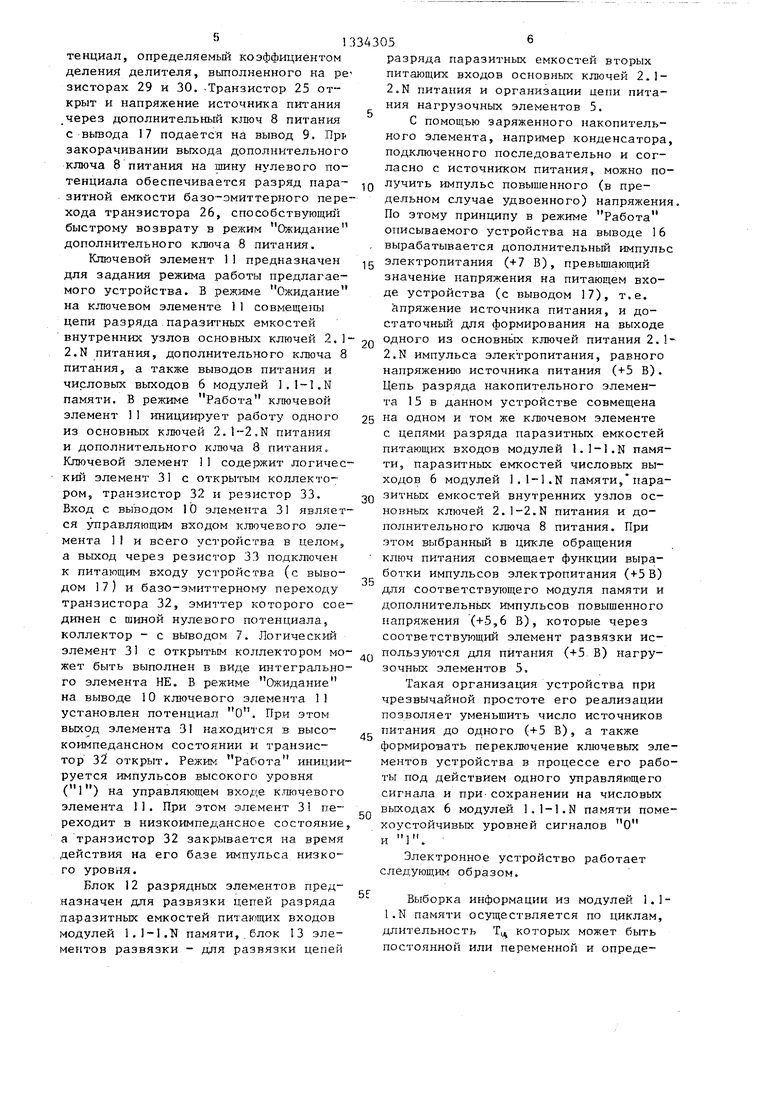

Каждый из ocHOBHbix ключей 2.1 питания содержит логический элемент 19 с открытым коллектором, источник 20 опорного напряжения (стабилитрон), транзисторы 21 и 22 и резисторы 23 - 25. Резисторы 23 и 25 включены-между выводом 16 и соответственно базой и эмиттером транзистора 21, а резистор 24 - между коллектором последнего и шиной нулевого потенциала. Коллектор выходного транзистора элемента 19 соединен с базой транзистора 21, эмиттер - с щиной нулевого потенциала, а базовая цепь - с потенциальным выводом коммутирующего вхо-. да основного ключа питания. Источник 20 опорного напряжения включен

параллельно резистору 24. База транзистора 22 подключена к коллектору транзистора 21 и к соответствующему выводу блока 13 элементов развязки, коллектор - к выводу 16, а эмиттер - к потенциальному выводу питающего входа модуля 1,1 памяти. Логический элемент 19 с открытым коллектором может быть вьшолнен на двух последовательно включенных элементах; интегральном элементе НЕ обычного типа и интегральном элементе НЕ с высоковольтным выходом. Ключ 2.1 питания предназначен для коммутации стабильного напряжения, равного напряжению источника питания, на питающий вход соответствующего модуля памяти 1.1 и формирования дополнительного импульса электропитания для нагрузоч

ньгх элементов блока 5. Выдача импульсов электропитания осуществляется под действием дополнительного импульса электропитания повьпиенного напряжения на первом питающем входе ключа 2.1 питания при наличии необходимого уровня сигнала на его коммутирующем входе. Ключ питания 2.i может функционировать в трех режимах: Ожидание, / Подготовка и Работа. В режиме Ожидание (исходное состояние) на выводе 16 установлен потенциал, приблизительно равный +4,3 В. Выход элемента 19 находится в высоко импедансном состоянии под действием сигнала высокого уровня (1) на его входе. Второй питающий вход ключа 2 питания закорочен на шину нулевого потенциала через последовательн соединенные соответствующий элемент развязки блока 13 и открытый ключевой элемент 11. В резз- льтате этого транзисторы 21 и 22 закрыты и ключ 2.1 питания практически не потребляет энергию. При появлении сигнала низкого уровня (О) на коммутирующем входе ключа 2.1 питания он переводится в режим подготовка. В этом режиме выход элемента 19 находится в низко- компедансном состоянии. При этом транзистор 21 открыт под действием потенциала низкого уровня на его ба 38. В режиме Подготовка .потреблени ключа 2.1 питания составляет несколько десятков миллиампер. Перевод ключа 2.1 питания в режим Работа осуществляется при одновременном отключении от ши-ны нулевого потенциала второго питающего входа (базы транзистора 22) и подаче на вывод 16 импульса электропитания амплитудой приблизительно +7 В. При этом ток базы транзистора 22 резко возрастает и транзистор 22 открывается. Ключ 2.1 питания выдает на выход мощный импульс электропитания, ограниченный по амплитуде до напряжения +5 В стабилитроном 20 и падением напряжения на переходе база - эмиттер транзистора 22, а на втором питающем входе появляется дополнительный импульс электропитания напряжением приблизительно +5,6 В. Из режима Работа ключ 2. питания может быть переведен в режим Подготовка при одновременном сняти активизирующих воздействий с вывода 16 и второго пита ющего входа или в режим Ожидание при снятии активи

0

5

зирующего воздействия с первого питающего входа. В любом из названньк вариантов транзистор 22-резко закрывается за счет закорачивания на шину нулевого потенциала паразитной емкости источника 20 опорного напряжения по цепи второго питающего входа ключа 2.1 питания.

Дешифратор 3 предназначен для преобразования кода адреса старших разрядов устройства в унитарный код-для задания реж1 Гма Подготовка одному из основных ключей 2.1-2.N питания.

Нагрузочные элементы 5 (резисторы) формируют на числовых выходах 6 устройства стандартный vpoBeHb сигма- лов 1.

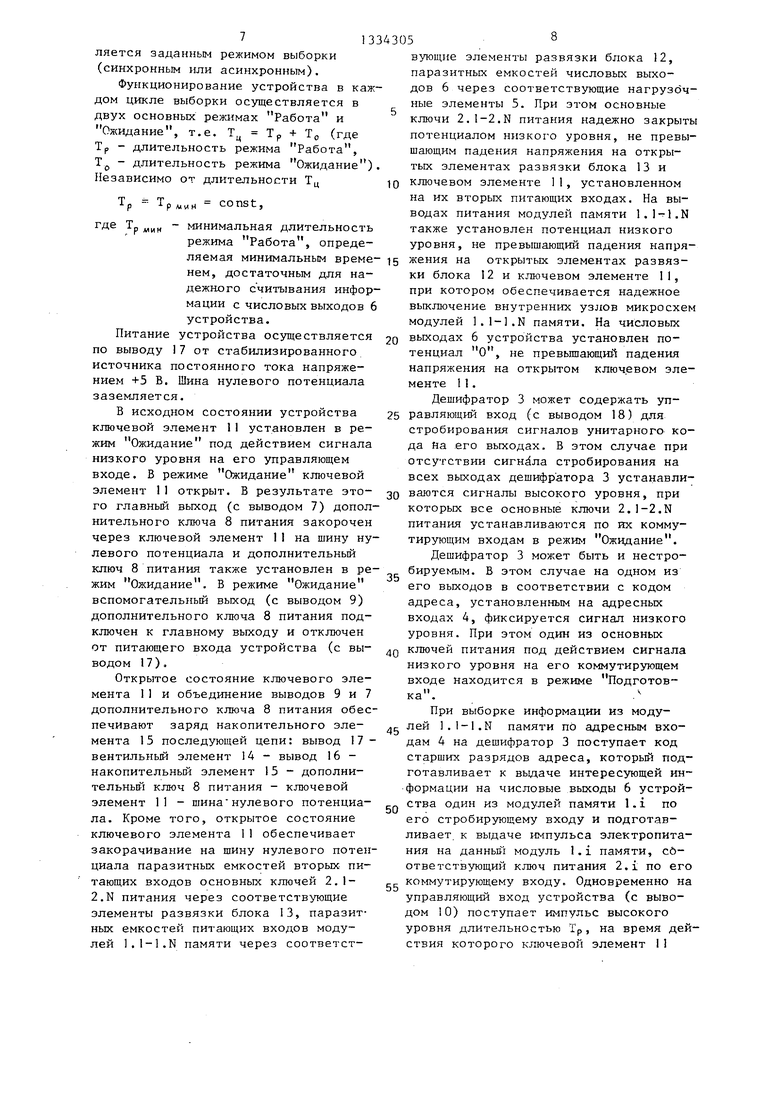

Дополнительный ключ 8 питания предназначен для коммутации тока разряда накопительного элемента 15 на вывод (шину питания) 16 основных ключей 2.1-2N питания и организации цепи заряда накопительного элемента 15. Цепь 5 заряда накопительного элемента 15 образуют вывод 17з вентильный элемент Г4, вывод 16, накопительный элемент 15, дополнительный ключ 8 питания, к1гочевой элемент 11, шина кулевого потенциала.

Дополнительньй ключ 8 питания содержит транзистор 26, диоды 27 и 28 и резисторы 29 и 30. Первые выводы резисторов 29 и 30 объединены и подключены к базе транзистора 25 и аноду диода 27. Второй вывод резистора 2i соединен с шиной нулевого потенциала. Коллектор транзистора 26 соединен со вторым выводом резистора 30 и с выводом 17. Потенциальный вывод 9 вспомогательного выхода дополнительного ключа 8 питания соединен с эмиттером транзистора 26 и анодом диода 28. Катод последнего подключен к катоду диода 27 и выводу 7. На вывод 17 подается напряжение +5 В от источника питания устройства. В режиме Ожидание главный выход дополнительного ключа 8 питания закорочен через от- крытьм ключевой элемент 11 на шину нулевого потенциала. В результате транзистор 26 закрыт При этом по цепи: вывод 9 - диод 28 - выьод 7 питания, протекает ток заряда накопительного элемента 15. В режиме Работа главный выход дополнительного ключа 8 питания отк. гючен от шины нулевого потенциале:, При этом на базе транзистора 26 ус- ановлен высокий по0

5

0

5

0

5

тенциал, определяемый коэффщиентом деления делителя, вьтолненного на ре зисторах 29 и 30. -Транзистор 25 открыт и напряжение источника питания через дополнительный ключ 8 питания с-вьгоода 17 подается на вывод 9. Прр закорачивании выхода дополнительного ключа 8 питания на :шину нулевого потенциала обеспечивается разряд паразитной емкости базо-эмиттерного перехода транзистора 26, способствующш быстрому возврату в режим Ожидание дополнительного ключа 8 питания.

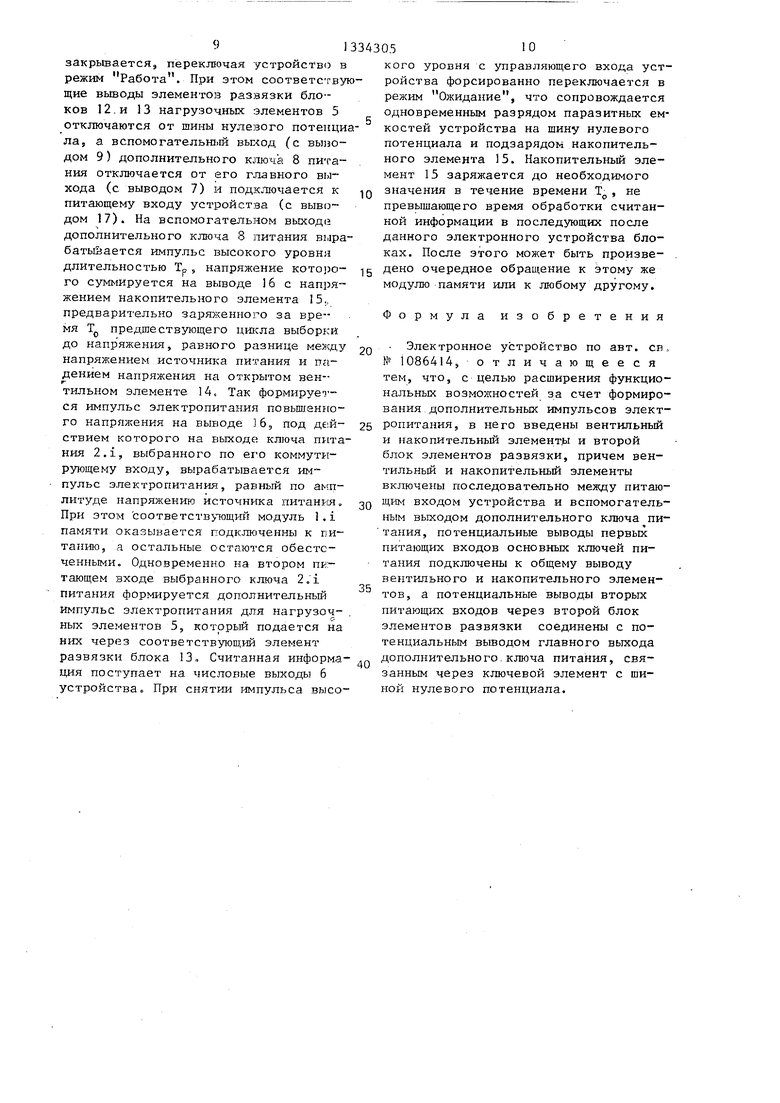

Ключевой элемент 1 предназначен для задания режима работы предлагаемого устройства. В режиме Ожидание на ключевом элементе 11 совмещены цепи разряда паразитных емкостей внутренних узлов основных ключей 2.1- 2.N питания, дополнительного ключа 8 питания, а также выводов питания и числовых выходов 6 модулей 1,1-l.N памяти. В режиме Работа ключевой элемент 11 иницищэует работу одного из основных ключей 2.1-2,N питания и дополнительного ключа 8 питания„ Ключевой элемент 11 содержит логический элемент 31 с открытым коллектором, транзистор 32 и резистор 33. Вход с выводом 10 элемента 31 является управляющим входом ключевого элемента 1I и всего устройства в целом, а выход через резистор 33 подключен к питающим входу устройства (с выводом 17) и базо-эмиттерному переходу транзистора 32, эмиттер которого соединен с шиной нулевого потенциала, коллектор - с выводом 7. Логический

элемент 31 с открытым коллектором мо- .,, пользуются для питания (+5, В) нагружет быть выполнен в виде интегрального элемента НЕ. В режиме Ожидание на выводе 10 ключевого элемента 1 установлен потенциал О. При этом выход элемента 3I находится в высо- коимпедансном состоянии и транзистор 32 открыт. Режим; Работа инициируется импульсов высокого уровня (1) на управляющем входе к.пючевого элемента 1i. При этом элемент 3 переходит в низкоимпедансное состояние, а транзистор 32 закрывается на время действия на его базе импульса низкого уровня.

Блок 12 разрядных элементов предназначен для развязки цепей разряда паразитных емкостей питающих входов модулей 1.1-I.N памяти,.блок 13 элементов развязки - для развязки цепей

45

50

5f

зочных элементов 5,

Такая организация устройства при чрезвычайной простоте его реализации позволяет уменьшить число источников питания до одного (+5 В), а также формировать переключение ключевых эл ментов устройства в процессе его раб ты под действием одного управляющего сигнала и при-сохранении на числовых выходах 6 модулей 1.1-1.N памяти пом хоустойчивых уровней сигналов О и 1.

Электронное устройство работает следующим образом.

Выборка информации из модулей 1.1 1.N памяти осуществляется по циклам, длительность Т, которых может быть постоянной или переменной и опреде

разряда паразитных емкостей вторых питающих входов основных ключей 2.1- 2.N питания и организации цепи питания нагрузочных элементов 5.

С помощью заряженного накопительного элемента, например конденсатора, подключенного последовательно и согласно с источником питания, можно получить импульс повышенного (в предельном случае удвоенного) напряжения. По этому принципу в режиме Работа описываемого устройства на выводе 16 , вырабатывается дополнительный импульс

g электропитания (+7 В), превьшшющий значение напряжения на питающем входе устройства (с выводом 17), т.е.

Спряжение источника питания, и достаточный для формирования на выходе одного из основньк ключей питания 2. 2.N импульса электропитания, равного напряжению источника питания (+5 В). Цепь разряда накопительного элемента 15 в данном устройстве совмещена

5 на одном и том же ключевом элементе с цепями разряда паразитных емкостей питающих входов модулей 1.1-1.N памяти, паразитных емкостей числовых выходов 6 модулей 1.1-1.N памяти/паразитных емкостей внутренних узлов основных ключей 2.1-2.N питания и дополнительного ключа 8 питания. При этом выбранный в цикле обращения ключ питания совмещает функции выработки импульсов электропитания (+5 В) для соответствующего модуля памяти и дополнительных импульсов повышенного напряжения (+5,6 В), которые через соответствующий элемент развязки ис0

0

5

5

0

f

зочных элементов 5,

Такая организация устройства при чрезвычайной простоте его реализации позволяет уменьшить число источников питания до одного (+5 В), а также формировать переключение ключевых элементов устройства в процессе его работы под действием одного управляющего сигнала и при-сохранении на числовых выходах 6 модулей 1.1-1.N памяти помехоустойчивых уровней сигналов О и 1.

Электронное устройство работает следующим образом.

Выборка информации из модулей 1.1- 1.N памяти осуществляется по циклам, длительность Т, которых может быть постоянной или переменной и определяется заданным режимом выборки (синхронным или асинхронным).

Функционирование устройства в каждом цикле вь1борки осуществляется в двух основных режимах Работа и Ожидание, т.е. Т Тр + Т,, (где Тр - длительность режима Работа, Тр - длительность режима Ожидание). Независимо от длительности Тц

т

р «и и

вующие элементы развязки блока 12, паразитных емкостей числовых выходов 6 через соответствующие нагрузочные элементы 5. При этом основные ключи 2.1-2.N питания надежно закрыты потенциалом низкого уровня, не превышающим падения напряжения на открытых элементах развязки блока 13 и 10 ключевом элементе 11, установленном на их вторых питающих входах. На выводах питания модулей памяти 1.1-rl.N также установлен потенциал низкого уровня, не превышающий падения напря- ляемая минимальным време- 15 жения на открытых элементах развяз const.

где Тр , - минимальная длительность режима Работа, опреденем, достаточным для надежного считывания информации с числовых выходов 6 устройства.

Питание устройства осуществляется по выводу 17 от стабилизированного источника постоянного тока напряжением +5 В, Шина нулевого потенциала заземляется.

В исходном состоянии устройства ключевой элемент 11 установлен в режим Ожидание под действием сигнала низкого уровня на его управляющем входе. В режиме Ожидание ключевой элемент 11 открыт, В результате этого главный выход (с выводом 7) дополнительного ключа 8 питания закорочен через ключевой элемент 11 на шину нулевого потенциала и дополнительный ключ 8 питания также установлен в режим Ожидание, В режиме Ожидание вспомогательный выход (с выводом 9) дополнительного ключа 8 питания подключен к главному выходу и отключен от питающего входа устройства (с выводом 17).

Открытое состояние ключевого элемента 11 и объединение выводов 9 и 7 дополнительного ключа 8 питания обеспечивают заряд накопительного элемента 15 последующей цепи: вывод 17- вентильный элемент 14 - вывод 16 - накопительньй элемент 15 - дополнительный ключ 8 питания - ключевой элемент 11 - шина нулевого потенциала. Кроме того, открытое состояние ключевого элемента 11 обеспечивает закорачивание на шину нулевого потенциала паразитных емкостей вторых питающих входов основных ключей 2,1- 2,N питания через соответствующие элементы развязки блока 13, паразитных емкостей питающих входов модулей 1,1-l.N памяти через соответст0

0

5

ки блока I2 и ключевом элементе I1, при котором обеспечивается надежное выключение внутренних узлов микросхем модулей 1.1-1.N памяти. На числовых выходах 6 устройства установлен потенциал О, не превьшающий падения напряжения на открытом ключевом элементе 11.

Дешифратор 3 может содержать уп- 5 равляющий вход (с выводом 18) для

стробирования сигналов унитарного кода На его выходах, В этом случае при отсутствии сигнала стробирования на всех выходах дешифратора 3 устанавливаются сигналы высокого уровня, при которых все основные ключи 2. 1-2.N питания устанавливаются по их коммутирующим входам в режим Ожидание.

Дешифратор 3 может быть и нестро- бируемым. В этом случае на одном из его выходов в соответствии с кодом адреса, установленным на адресных входах 4, фиксируется сигнал низкого уровня. При этом один из основных ключей питания под действием сигнала низкого уровня на его коммутирующем входе Находится в режиме Подготов- ка.

При выборке информации из моду- g лей 1,1-l.N памяти по адресным входам 4 на дешифратор 3 поступает код старших разрядов адреса, которьш подготавливает к выдаче интересующей информации на числовые выходы 6 устройства один из модулей памяти 1.i по его стробирующему входу и подготавливает к выдаче импульса электропитания на данньш модуль 1.i памяти, сб- ответствующий ключ питания 2.i по его коммутирующему входу. Одновременно на управляющий вход устройства (с выводом 10) поступает импульс высокого уровня длительностью Тр, на время действия которого ключевой элемент II

0

0

5

закрьшается, переключая устройство в режим Работа. При этом соответствущие выводы элементов развязки блоков 12.и 13 нагрузочных элементов 5 отключаются от шины нулевого потенцила, а вспомогательш1Ш выход (с выио- дом 9) дополнительного к;шоча 8 питания отключается от его главного выхода (с выводом 7) и подключается к питающему входу устройства (с выводом 17). На вспомогательном выход(г дополнительного ключа 8 питания вырабатывается импульс высокого уровня длительностью Тр , напряжение кото))о- го суммируется на выводе 16 с напряжением накопительного элемента 15., предварительно заряженного за время Т предшествующего цшсла выборки до напряжения, равного разнице между напряжением источника питания и падением напряжения на открытом вентильном элементе 14, Так формируеп - ся импульс электропитания повышенного напряжения на выводе 16, под де .й- ствием которого на выходе ключа питания 2.1, выбранного по его коммутирующему входу, вырабатывается импульс электропитания, равный по амплитуде, напряжению источника питан ся, При этом соответствующз-ЕЙ модуль l.i памяти оказывается подк.пюченны к питанию, а остальные остаются обесточенными. Одновременно на втором питающем входе выбра.нного ключа 2.1 питания формируется дополнительный импульс электропитания для нагрузоч- ных элементов 5, котррьй подается на них через соответствуюш;ий элемент развязки блока 13, Считанная информа ция поступает на числовые выходы 6 устройства. При снятии 1-1мпульса высо

g о 5 д „

5

кого уровня с управляющего входа устройства форсированно переключается в режим Ожидание, что сопровождается одновременным разрядом паразитных емкостей устройства на шину нулевого потенциала и подзарядок накопительного элемента 15. Накопительный элемент 15 заряжается до необходимого значения в течение времени Т, не превышающего время обработки считанной информации в последующих после данного электронного устройства блоках. После этого может быть произве- . дено очередное обращение к этому же модулю памяти или к любому другому.

Формула изобретения

Электронное устройство по авт. св. № 1086414, отличающееся тем, что, с целью расширения функциональных возможностей за счет формирования ,дополнительных импульсов электропитания, в него введены вентильный и накопительный элементы и второй блок элементов развязки, причем вен- тильньш и накопительный элементы включены последовательно между питающим входом устройства и вспомогательным выходом дополнительного ключа пи- тания, потенциальные выводы первых питающих входов основных ключей питания подключены к общему выводу вентильного и накопительного элементов, а потенциальные выводы вторых питающих входов через второй блок элементов развязки соединены с потенциальным выводом главного выхода дополнительного.ключа питания, связанным через ключевой элемент с шиной нулевого потенциала.

1334305 16

К73

Фиг. 2

11

33

ЗГ

Ю

Фае. 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Электронное устройство | 1987 |

|

SU1427518A2 |

| Устройство импульсного стабильного питания функциональных блоков электронно-вычислительных машин | 1985 |

|

SU1288677A1 |

| Устройство для управления подключением электропитания | 1987 |

|

SU1427371A2 |

| Электронное устройство (его варианты) | 1982 |

|

SU1086414A1 |

| ВЫСОКОВОЛЬТНЫЙ ИМПУЛЬСНЫЙ МОДУЛЯТОР СО СТАБИЛИЗАЦИЕЙ АМПЛИТУДЫ ИМПУЛЬСОВ И ЭЛЕКТРОННЫЙ КЛЮЧ ДЛЯ НЕГО (ВАРИАНТЫ) | 2006 |

|

RU2339158C2 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Устройство для управления подключением электропитания | 1985 |

|

SU1302283A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU943853A1 |

| Система электропитания | 2017 |

|

RU2665030C1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

Изобретение относится к электротехнике, в частности к источникам вторичного электропитания интегральных блоков памяти с выходом, органи- эованным по типу открытый коллектор. Цель изобретения - расширение функциональных возможностей за счет формирования дополнительных импульсов электропитания. Первый из дополни- г тельных импульсов формируется с помощью дополнительного ключа 8 питания при последовательном и согласном подключении источника питания и накопительного элемента 15, предварительно заряженного в предыдущем цикле выборки. Под действием этого импульса на выходе одного из основных ключей 2.1-2.N питания вырабатывается напряжение, равное напряжению источника . питания, а на его втором питающем входе - второй дополнительный импульс повышенного напряжения. Последний через соответствующий элемент развязки блока 13 используется для подключения электропитания к нагрузочным элементам 5, что определяет низкий уровень сигнала логического нуля на числовых выходах 6 устройства. Формирование в устройстве дополнительных импульсов электропитания позволяет сократить до одного число используемых источников питания. 4 ил. сл П 0 со 004; 00 о С71 N)

Составитель Л.Морозов Редактор Л.Пчолинская Техред М. Ходанич

Заказ 3975/53 Тираж 659Подписное

BKHIfflH Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор А.Тяско

| Электронное устройство (его варианты) | 1982 |

|

SU1086414A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-08-30—Публикация

1986-02-03—Подача