11

Изобретение относится к области контрольно-измерительной техники и может бйггь использовано при построении систем автоматизированного контроля многопараметрических объектов.

Цель изобретения - повышение быстродействия устройства.

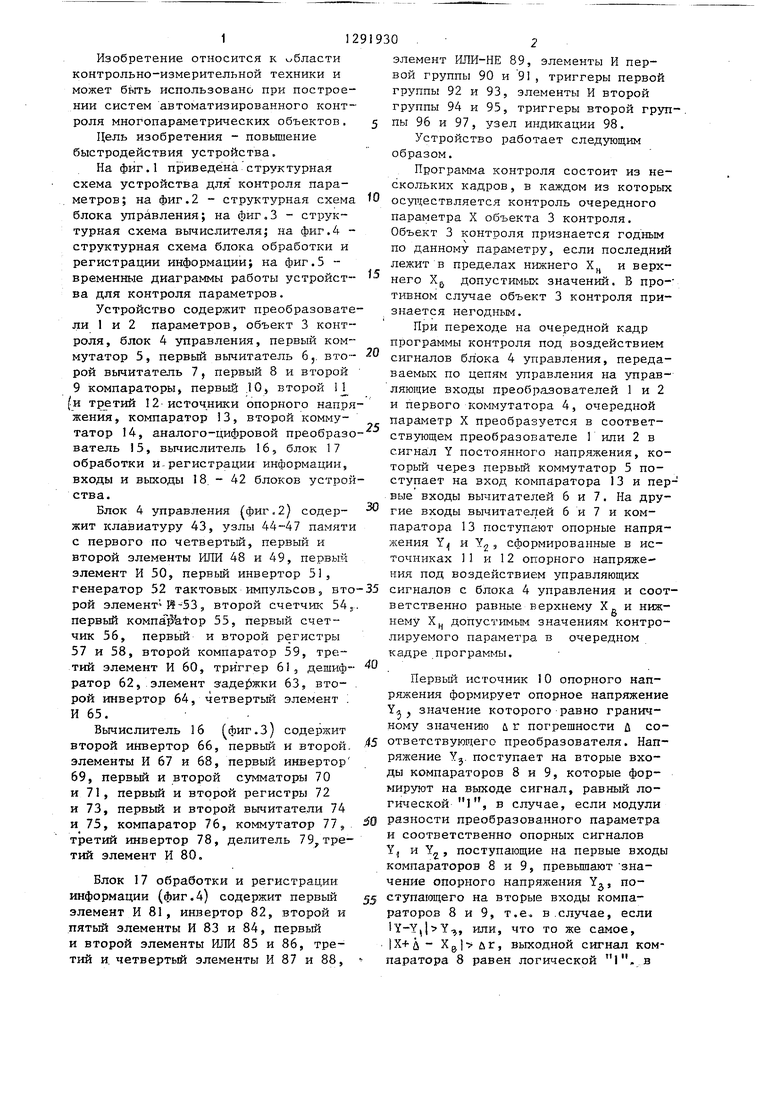

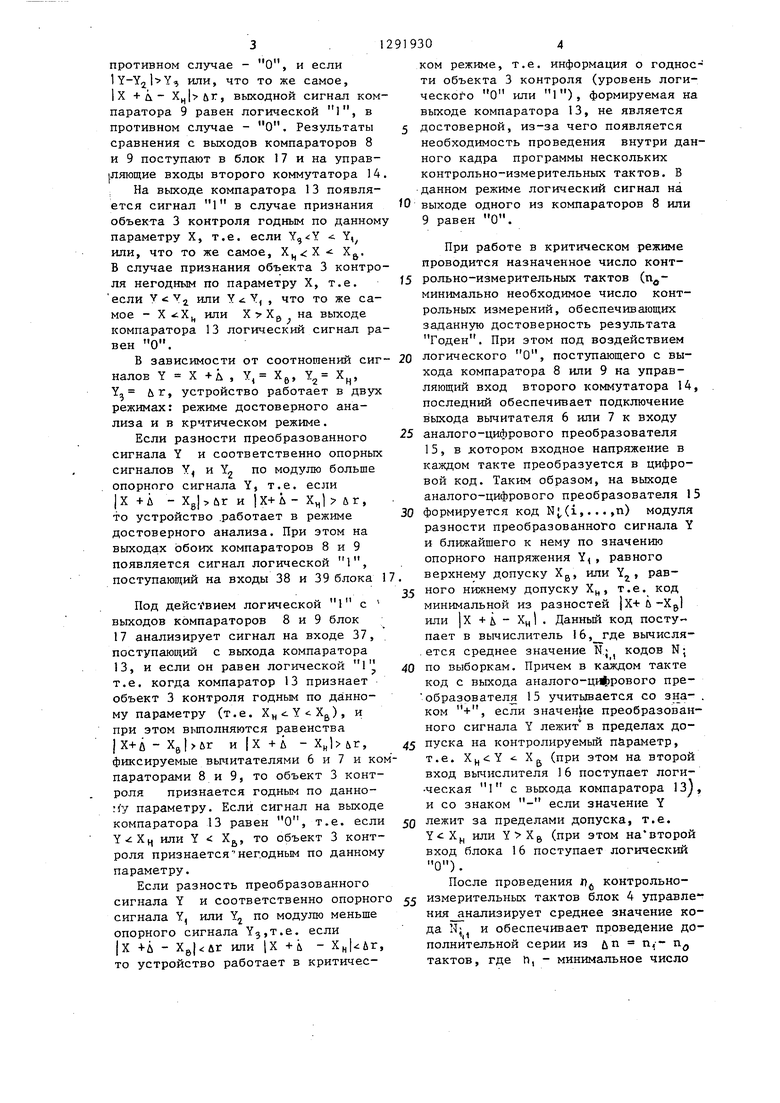

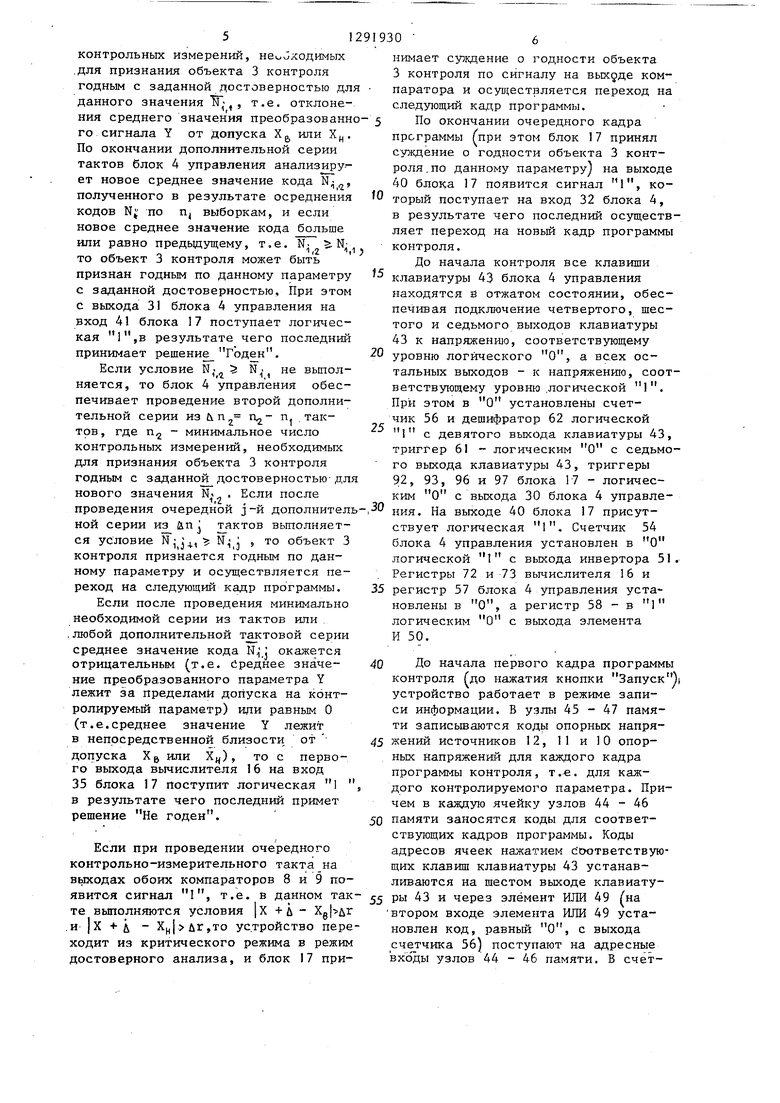

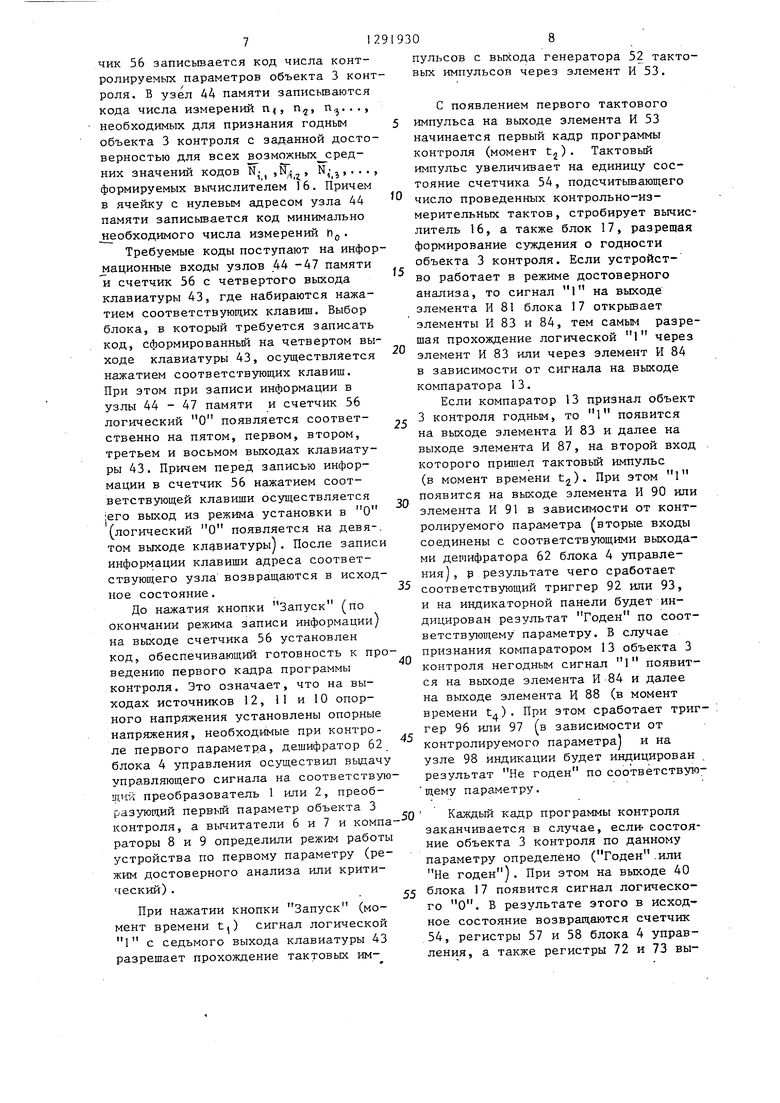

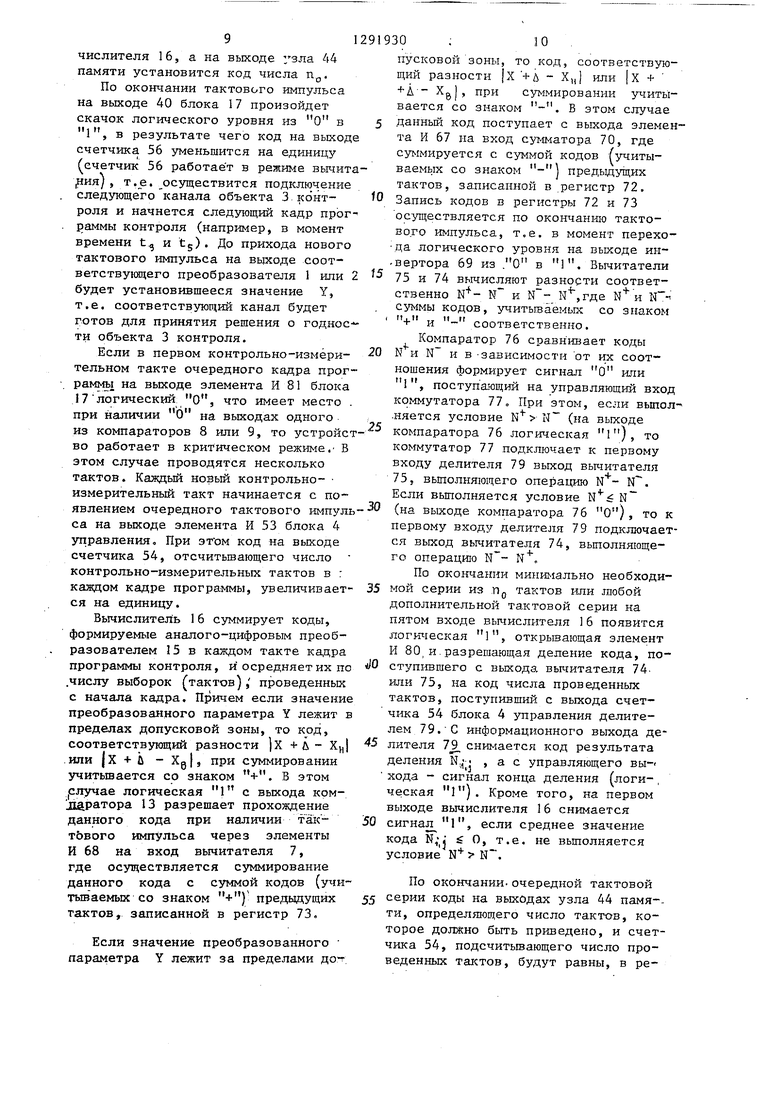

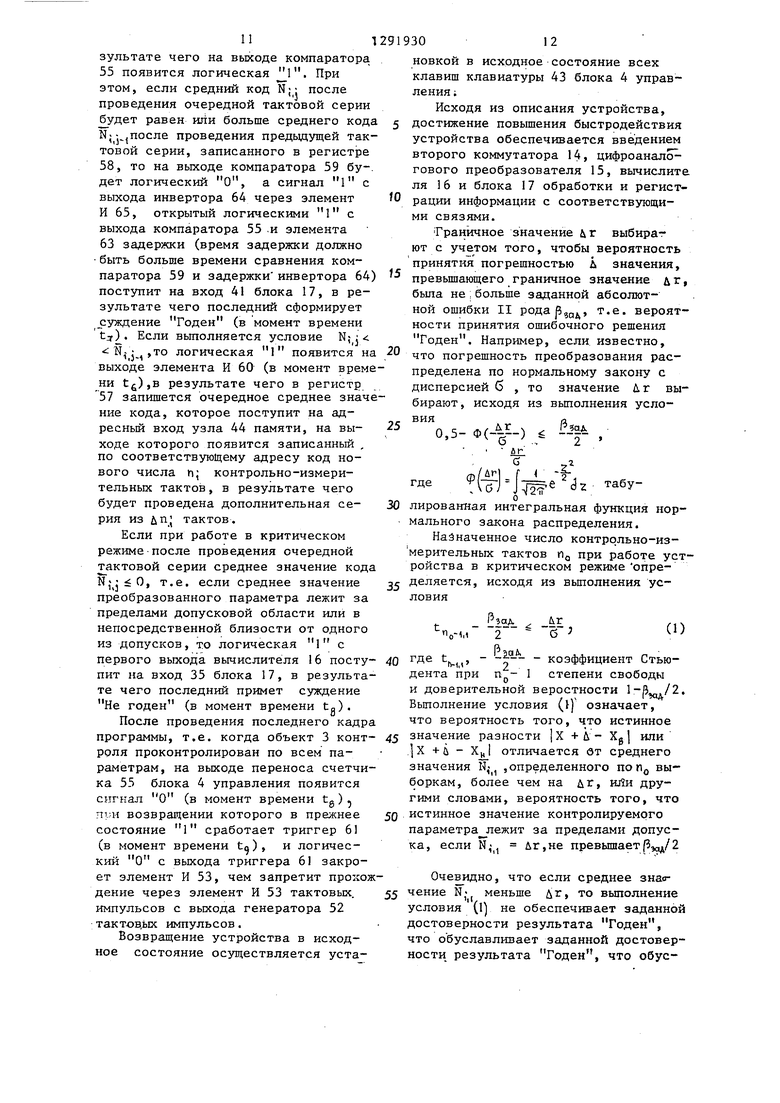

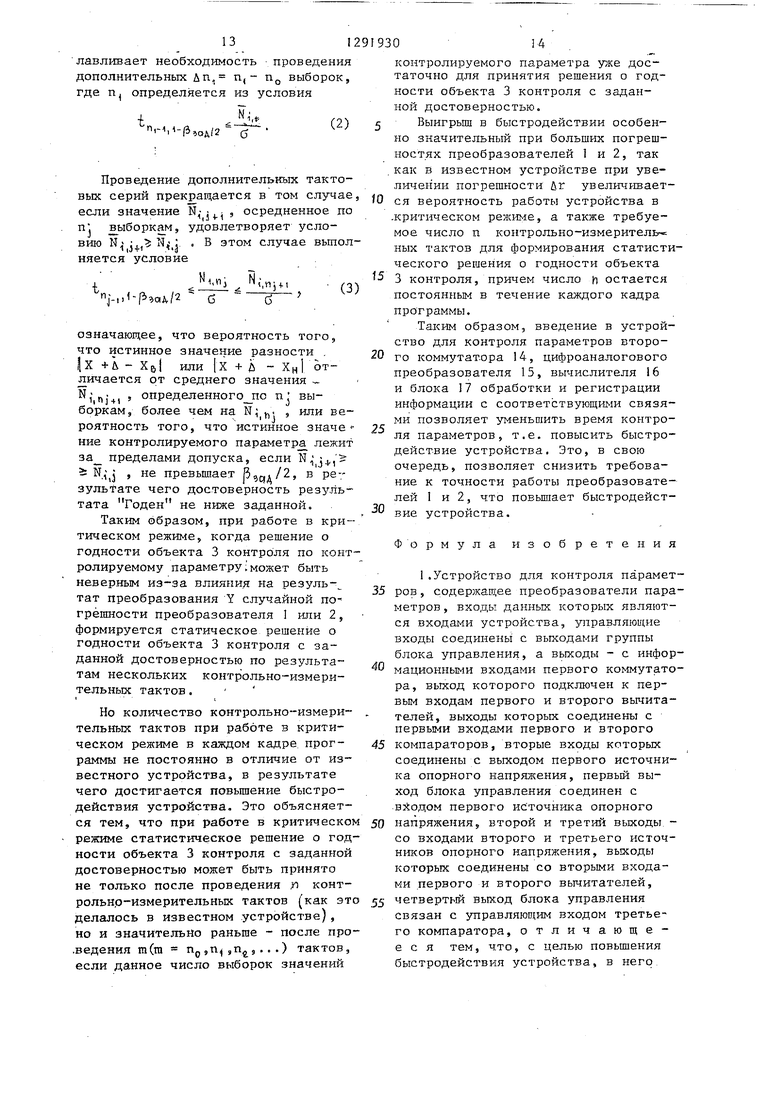

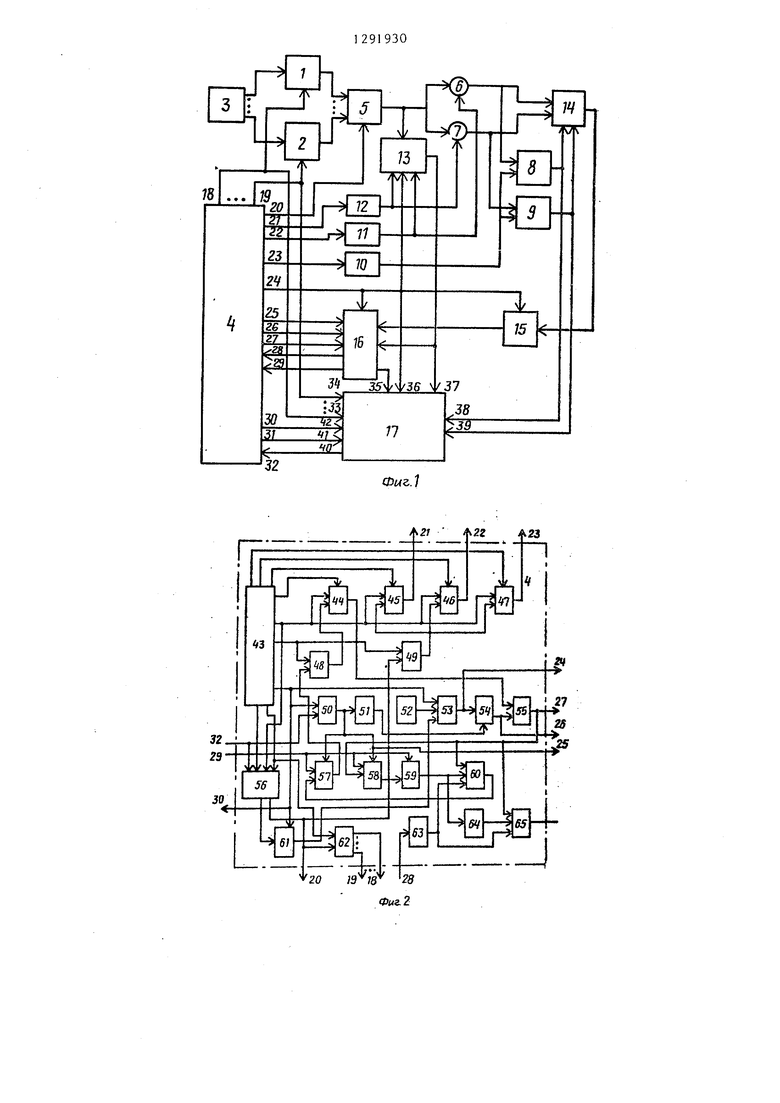

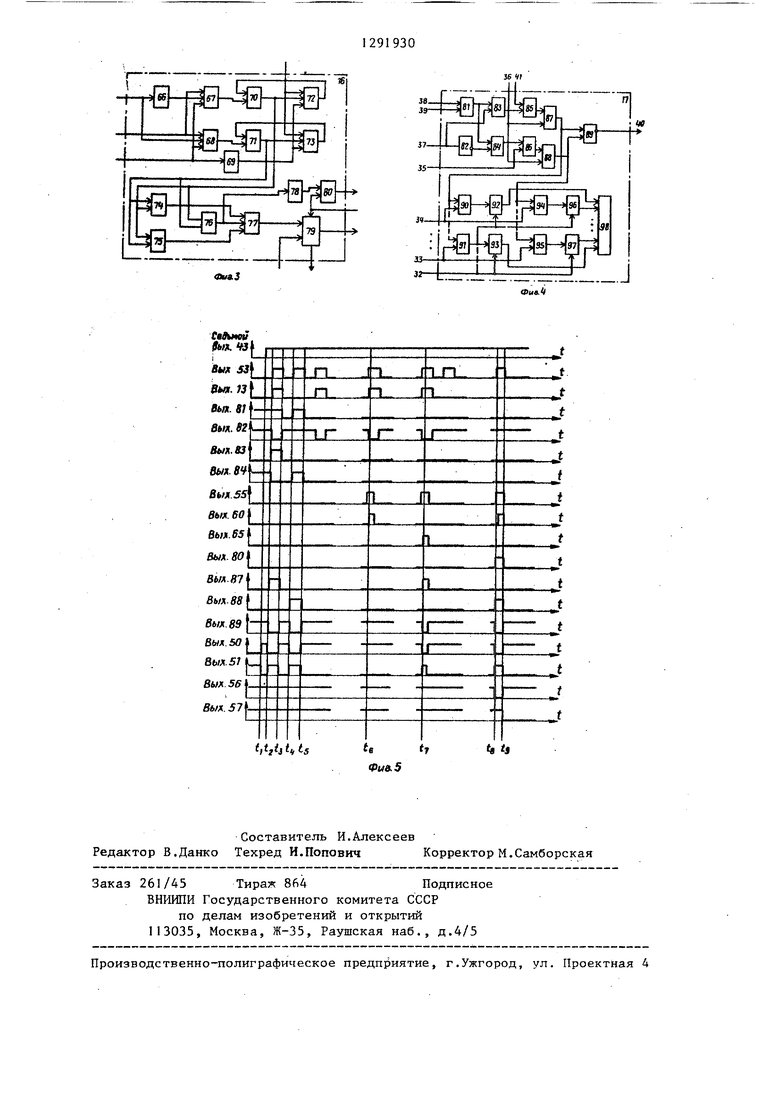

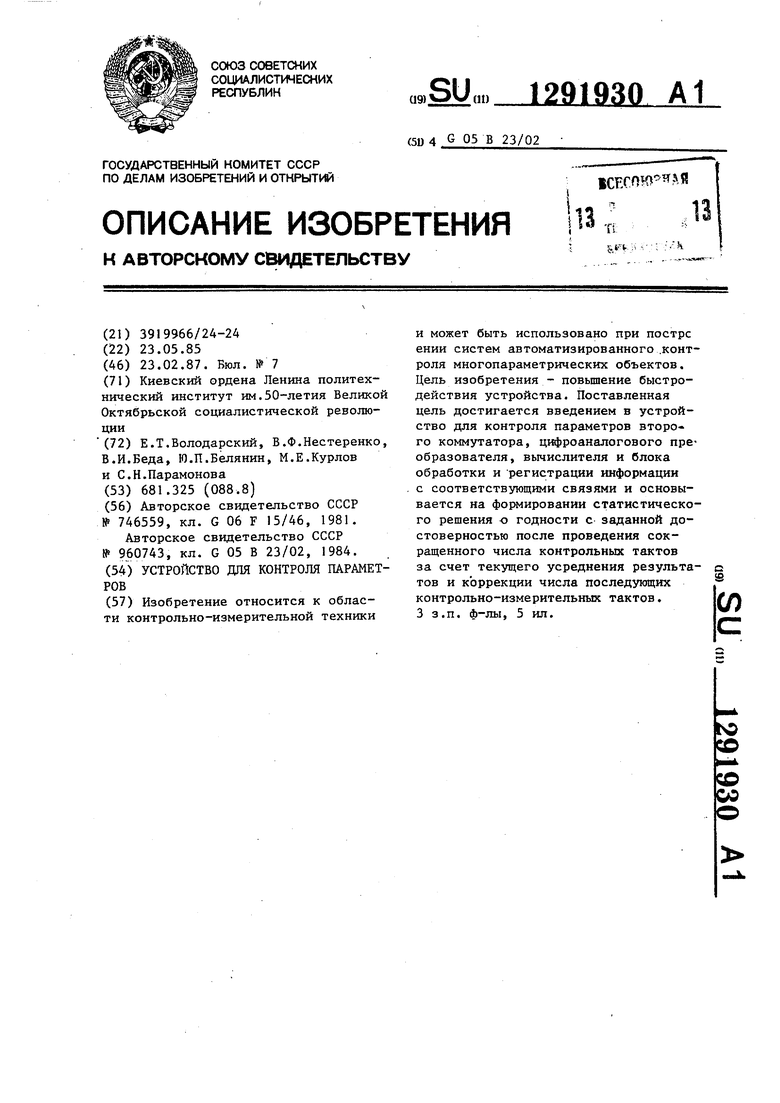

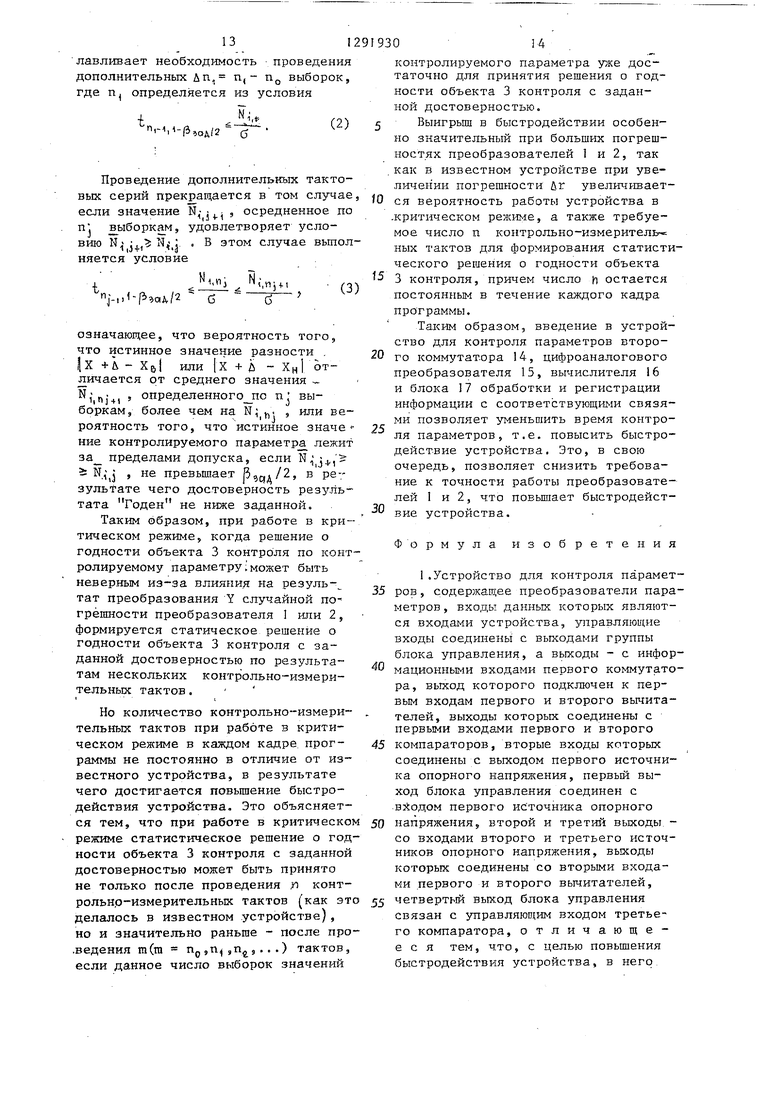

На фиг.1 приведена структурная схема устройства для контроля параметров; на фиг.2 - структурная схема блока управления; на фиг.З - структурная схема вычислителя; на фиг.4 - структурная схема блока обработки и регистрации информации; на фиг.5 - временные диаграммы работы устройства для контроля параметров.

Устройство содержит преобразователи 1 и 2 параметров, объект 3 контроля, блок 4 управления, первый коммутатор 5, первый вычитатель б j. вто-

рой вычитатель 7, первый 8 и второй 9 компараторы, первьй .10, второй 11 (и третий 12 источники опорного напряжения, компаратор 13, второй коммутатор 14, аналого-цифровой преобразователь 5, вычислитель 16, блок 17 обработки И-регистрации информации, входы и выходы 18. - 42 блоков устройства.

Блок 4 управления фиг,2) содер- жит клавиатуру 43, узлы 44-47 памяти с первого по четвертый, первый и второй элементы ИЛИ 48 и 49, первый элемент И 50, первый инвертор 51, генератор 52 тактовых импульсов, вто рой элемент И-53э второй счетчик 54 первьй KOMna atop 55, первый счетчик 56, первый и второй регистры 57 и 58, второй компаратор 59, третий элемент И 60, три ггер 61, дешифратор 62, элемент задержки 63, второй инвертор 64, четвертьй элемент ; И 65.

Вьиислитель 16 (фиг, 3) содержит второй инвертор 66, первый и второй. элементы И 67 и 68, первый инвертор 69, первый и второй сумматоры 70 и 71, первый и второй регистры 72 и 73, первый и второй вычитатели 74 и 75, компаратор 76, коммутатор 77, третий инвертор 78, делитель 79 третий элемент И 80,

Блок 17 обработки и регистрации информации (фиг.4) содержит первый элемент И 81, инвертор 82, второй и пятый элементы И 83 и 84, первый и второй элементы ИЖ 85 и 86, третий и. четвертый элементы И 87 и 88,

0

0

5

5 сигналов

элемент ИЛИ-НЕ 89, элементы И первой группы 90 и 91 , триггеры первой группы 92 и 93, элементы И второй группы 94 и 95, триггеры второй группы 96 и 97, узел индикации 98.

Устройство работает следующим образом.

Программа контроля состоит из нескольких кадров, в каждом из которых осутцествляется контроль очередного параметра X объекта 3 контроля. Объект 3 контроля признается годным по данному параметру, если последний лежит в пределах нижнего Х и верхнего Xj, допустимых значений. В про- тивном случае объект 3 контроля признается негодным.

При переходе на очередной кадр программы контроля под воздействием сигналов бл:ока 4 управления, передаваемых по цепям управления на управляющие входы преобразователей 1 и 2 и первого коммутатора 4, очередной параметр X преобразуется в соответствующем преобразователе 1 или 2 в сигна л Y постоянного напряжения, который через первый коммутатор 5 поступает на вход компаратора 13 и первые входы вычитателей 6 и 7. На другие входы вычитателей 6 и 7 и компаратора 13 поступают опорные напряжения Y и 2 ., сформированные в источниках 11 и 12 опорного напряжения под воздействием управляющих

с блока 4 управления и соотсигналов

ветственно равные верхнему X., и нижо

нему Х допустимым значениям контролируемого параметра, в очередном кадре программы.

сигналов

Первый источник 10 опорного напряжения формирует опорное напряжение Yi ,, значение которого равно граничному значению и г погрешности и соответствующего преобразователя. Напряжение Yj. поступает на вторые входы компараторов 8 и 9, которые формируют на выходе сигнал, равный логической I, в случае, если модули

разности преобразованного параметра и соответственно опорных сигналов YJ и Y, поступающие на первые входы компараторов 8 и 9, превьшают значение опорного напряжения Y, поступающего на вторые входы компараторов 8 и 9, т.е. в.случае, если , или, что то же самое, |Х+й в1 йг, выходной сигнал компаратора 8 равен логической 1, в

противном случае - О, и если lY-Yjl Y, или, что то же самое, 1 X + U - , выходной сигнал компаратора 9 равен логической 1, в противном случае - О. Результаты сравнения с выходов компараторов 8 и 9 поступают в блок 17 и на управ- |Ляющие входы второго коммутатора 14. ; На выходе компаратора 13 появляется сигнал 1 в случае признания объекта 3 контроля годным по данному параметру X, т.е. если Y,

или, что то же самое.

Х,Х

X.

6

в случае признания объекта 3 контроля негодным по параметру X, т.е. если или Y.iY, , что то же самое - X Х или X Хц на выходе компаратора 13 логический сигнал равен О.

В зависимости от соотношений сигналов Y X +U , Y, Xg, Y2 Х, Y лг, устройство работает в двух режимах: режиме достоверного анализа и в критическом режиме.

Если разности преобразованного сигнала Y и соответственно опорных сигналов Y и Yj по модулю больше опорного сигнала Y, т.е. если

|Х +U - и 1х+Л - йг, то устройство .работает в режиме достоверного анализа. При этом на выходах обоих компараторов 8 и 9 появляется сигнал логической 1, поступающий на входы 38 и 39 блока

Под действием логической 1 с выходов компараторов 8 и 9 блок 17 анализирует сигнал на входе 37, поступаюо;ий с выхода компаратора 13, и если он равен логической 1 т.е. когда компаратор 13 признает объект 3 контроля годным по данному параметру (т.е. ),

и

при этом выполняются равенства 1Х+й-Хц| йг и |Х +А , фиксируемые вычитателями 6 и 7 и ко параторами 8 и 9, то объект 3 контроля признается годным по данно- параметру. Если сигнал на выходе компаратора 13 равен О, т.е. если , или Y Xg,, то объект 3 контроля признается негодным по данному параметру.

Если разность преобразованного сигнала Y и соответственно опорног сигнала Y, или Y по модулю меньше опорного сигнала .e. если |Х -t-u - или х +6 - , то устройство работает в критичес

ком режиме, т.е. информация о годное- ти объекта 3 контроля (уровень логического О или 1), формируемая на выходе компаратора 13, не является достоверной, из-за чего появляется необходимость проведения внутри данного кадра программы нескольких контрольно-измерительных тактов. В данном режиме логический сигнал на выходе одного из компараторов 8 или 9 равен О.

При работе в критическом режиме проводится назначенное число контрольно-измерительных тактов ( минимально необходимое число контрольных измерений, обеспечива 01цих заданную достоверность результата Годен. При этом под воздействием

логического О, поступающего с выхода компаратора 8 или 9 на управляющий вход второго коммутатора 14, последний обеспечивает подключение выхода вычитателя 6 или 7 к входу

аналого-цифрового преобразователя 15, в котором входное напряжение в каждом такте преобразуется в цифровой код. Таким образом, на выходе аналого-цифрового преобразователя 15

формируется код N{(i,...,n) модуля разности преобразованного сигнала Y и ближайшего к нему по значению опорного напряжения Y,, равного верхнему допуску Хц, или Y,, равного нижнему допуску X,., т.е. код

минимальной из разностей 1х+Ь-X-l

40

м -

о 50

55

или

пает

, ется

|Х в

+ h ХцI . Данный код посту- вычислитель 6,где вычисля- среднее значение Nj кодов N; по выборкам. Причем в каждом такте код с выхода аналого-цифрового пре- образователя 15 учитьшается со зна- . ком +, если 3Ha4eHiie преобразованного сигнала Y лежит в пределах до- 45 пуска на контролируемый параметр, т.е. Х„ (при этом на второй вход вычислителя 16 поступает логи- ческая I с выхода компаратора 13у, и со знаком - если значение Y лежит за пределами допуска, т.е. или (при этом на второй вход блока 16 поступает логический О).

После проведения fl контрольно- измерительных тактов блок 4 управле ния анализирует среднее значение кода Н- и обеспечивает проведение дополнительной серии из 1,п п.-- Пд тактов, где h, - минимальное число

51

контрольных измерений, необходимых .для признания объекта 3 контроля годным с заданной достоверностью дл данного значения ,, т.е. отклонения среднего значен ия преобразованн го сигнала Y от допуска Х или Х. По окончании дополнительной серии тактов блок 4 управления анализиру-- ет новое среднее значение кода N, полученного в результате осреднения кодов N; по п выборкам, и если новое среднее значение кода больше или равно предьщущему,

т.е. N- 5.N1,2 |

ТО объект 3 контроля может быть признан годным по данному параметру с заданной достоверностью. При этом с выхода 31 блока 4 управления на вход 41 блока 17 поступает логическая 1,в результате чего последний принимает решение Годен.

Если условие N,- 5

не выполняется, то блок 4 управления обеспечивает проведение второй дополнительной серии из йП2 Д2 TT.J , тактов , где п - минимальное число контрольных измерений, необходимых для признания объекта 3 контроля годнь1м с заданной достоверностью для нового значения N. . Если после

До начала контроля все клавший клавиатуры 43 блока 4 управления находятся и отжатом состоянии, обес печивая подключение четвертого, шес того и седьмого выходов клавиатуры 43 к напряжению, соответствующему уровню логического О, а всех остальных выходов - к напряжению, соо ветствующему уровню .логической 1. При этом в О установлены счетчик 56 и дешифратор 62 логической 1 с девятого выхода клавиатуры 43 триггер 61 - логическим О с седьм го выхода клавиатуры 43, триггеры 92, 93, 96 и 97 блока 17 - логическим О с выхода 30 блока 4 управле

25

ствует логическая 1. Счетчик 54 блока 4 управления установлен в О логической 1 с выхода инвертора 5 Регистры 72 и 73 вычислителя 16 и 35 регистр 57 блока 4 управления установлены в логическим И 50.

О

а регистр 58 - в 1

О с выхода элемента

проведения очередной j-й дополнитель-|-30 „j На выходе 40 блока 17 присут- ной серии из йп j TviKTOB выполняется условие NJ j, 5 N.; j , то объект 3 контроля признается годным по данному параметру и осуществляется переход на следующий кадр программы.

Если после проведения минимально необходимой серии из тактов или .любой дополнительной тактовой серии среднее значение кода окажется отрицательным (т.е. Среднее значение преобразованного параметра Y лежит за пределами допуска на контролируемый параметр) иди равным О (т.е.среднее значение Y лежит в непосредственной близости от

допуска Kg или Xj), то с первого выхода вычислителя 16 на вход 35 блока 17 поступит логическая 1 в результате чего последний примет решение Не годен.

40

До начала первого кадра программ контроля Гдо нажатия кнопки Запуск устройство работает в режиме записи информации. В узлы 45 - 47 памяти записьшаются коды опорных напря- 45 жений источников 12, 11 и 10 опорных напряжений для каждого кадра программы контроля, т.е. для каждого контролируемого параметра. При чем в каждую ячейку узлов 44 - 46 памяти заносятся коды для соответствующих кадров программы. Коды адресов ячеек нажатием с сютветствую щих клавиш клавиатуры 43 устанавливаются на шестом выходе клавиату50

До начала первого кадра программ контроля Гдо нажатия кнопки Запуск устройство работает в режиме записи информации. В узлы 45 - 47 памя ти записьшаются коды опорных напря 45 жений источников 12, 11 и 10 опорных напряжений для каждого кадра программы контроля, т.е. для каждого контролируемого параметра. Пр чем в каждую ячейку узлов 44 - 46 памяти заносятся коды для соответствующих кадров программы. Коды адресов ячеек нажатием с сютветствую щих клавиш клавиатуры 43 устанавливаются на шестом выходе клавиату

Если при проведении очередного контрольно-измерительного такта на вькодах обоих компараторов 8 и 9 появится сигнал I, т.е. в данном так- 55 ры 43 и через элемент ИЛИ 49 (на те выполняются условия х +й - втором входе элемента РШИ 49 уста- .и |Х +i - Xj.ur,TO устройство пере- новлен код, равный О, с выхода

счетчика 56) поступают на адресные входы узлов 44 - 46 памяти. В счетходит из критического режима в режим достоверного анализа, и блок 17 при5

O

нимает су кдение о годности объекта 3 контроля по сигналу на выхдде компаратора и осуп;ествляется переход на следующий кадр программы.

По окончании очередного кадра программы при этом блок 17 принял суждение о годности объекта 3 контроля .по данному параметру) на выходе 40 блока 17 появится сигнал 1, который поступает на вход 32 блока 4, в результате чего последний осуществляет переход на новьй кадр программы контроля.

До начала контроля все клавший клавиатуры 43 блока 4 управления находятся и отжатом состоянии, обеспечивая подключение четвертого, шестого и седьмого выходов клавиатуры 43 к напряжению, соответствующему уровню логического О, а всех остальных выходов - к напряжению, соответствующему уровню .логической 1. При этом в О установлены счетчик 56 и дешифратор 62 логической 1 с девятого выхода клавиатуры 43, триггер 61 - логическим О с седьмого выхода клавиатуры 43, триггеры 92, 93, 96 и 97 блока 17 - логическим О с выхода 30 блока 4 управле0

5

0 „j На выходе 40 блока 17 присут-

ствует логическая 1. Счетчик 54 блока 4 управления установлен в О логической 1 с выхода инвертора 51. Регистры 72 и 73 вычислителя 16 и 35 регистр 57 блока 4 управления уста|-30 „j На выходе 40 блока 17 присут-

О

а регистр 58 - в 1

О с выхода элемента

40

До начала первого кадра программы контроля Гдо нажатия кнопки Запуск устройство работает в режиме записи информации. В узлы 45 - 47 памяти записьшаются коды опорных напря- 45 жений источников 12, 11 и 10 опорных напряжений для каждого кадра программы контроля, т.е. для каждого контролируемого параметра. Причем в каждую ячейку узлов 44 - 46 памяти заносятся коды для соответствующих кадров программы. Коды адресов ячеек нажатием с сютветствую- щих клавиш клавиатуры 43 устанавливаются на шестом выходе клавиату50

55 ры 43 и через элемент ИЛИ 49 (на втором входе элемента РШИ 49 уста- новлен код, равный О, с выхода

счетчика 56) поступают на адресные входы узлов 44 - 46 памяти. В счет71291930

чик 56 записьюается код числа контролируемых параметров объекта 3 контроля. В узел А4 памяти записьшаются

С появлением первого тактового 5 импульса на выходе элемента И 53

пульсов с выхода генератора 52 так вых импульсов через элемент И 53.

кода числа измерений п, п, п.

необходимых для признания годным объекта 3 контроля с заданной достоверностью для всех возможных средначинается первый кадр программы контроля (момент tj). Тактовый импульс увеличивает на единицу сос тояние счетчика 54, подсчитьшающег число проведенных контрольно-измерительных тактов, стробирует выч литель 16, а также блок 17, разрещ формирование суждения о годности объекта 3 контроля. Если устройство работает в режиме достоверного анализа, то сигнал 1 на выходе элемента И 81 блока 17 открывает элементы И 83 и 84, тем самым раз шая прохождение логической 1 чер элемент И 83 или через элемент И 8 в зависимости от сигнала на выходе компаратора 13.

N

1Л

них значений кодов N N, формируемых вычислителем 16. Причем в ячейку с нулевым адресом узла 44 памяти записьшается код минимально необходимого числа измерений п.

Требуемые коды поступают на инфор мационные входы узлов 44 -47 памяти и счетчик 56 с четвертого выхода клавиатуры 43, где набираются нажатием соответствующих клавиш. Выбор блока, в который требуется записать код, сформированный на четвертом выходе клавиатуры 43, осуществлйется нажатием соответствующих клавиш. При этом при записи информации в узлы 44 - 47 памяти и счетчик 56 логический О появляется соответственно на пятом, первом, втором, третьем и восьмом выходах клавиатуры 43. Причем перед записью информации в счетчик 56 нажатием соответствующей клавиши осуществляется

;его выход из режима установки в

О

(логический О появляется на девя-. том выходе кл }виатуры . После записи информации клавиши адреса соответствующего узла возвращаются в исходное состояние.

До нажатия кнопки Запуск (по окончании режима записи информации) на выходе счетчика 56 установлен код, обеспечивающий готовность к проведению первого кадра программы контроля. Это означает, что на выходах источников 12, 11 и 10 опорного напряжения установлены опорные напряжения, необходимые при контроле первого параметра, дешифратор 62 блока 4 управления осуществил выдачу управляющего сигнала на соответствую- щнй преобразователь 1 или 2, преобразующий первый параметр объекта 3 контроля, а вычитатели 6 и 7 и компа раторы 8 и 9 определили режим работы устройства по первому параметру (режим достоверного анализа или критический) .

При нажатии кнопки Запуск (момент времени t) сигнал логической 1 с седьмого выхода клавиатуры 43 разрешает прохождение тактовых импульсов с выхода генератора 52 тактовых импульсов через элемент И 53.

-

Ю

15

20

25

- начинается первый кадр программы контроля (момент tj). Тактовый импульс увеличивает на единицу состояние счетчика 54, подсчитьшающего число проведенных контрольно-измерительных тактов, стробирует вычислитель 16, а также блок 17, разрещая формирование суждения о годности объекта 3 контроля. Если устройство работает в режиме достоверного анализа, то сигнал 1 на выходе элемента И 81 блока 17 открывает элементы И 83 и 84, тем самым разрешая прохождение логической 1 через элемент И 83 или через элемент И 84 в зависимости от сигнала на выходе компаратора 13.

Если компаратор 13 признал объект 3 контроля годным, то 1 появится на выходе элемента И 83 и далее на выходе элемента И 87, на второй вход которого пршиел тактовьм импульс (в момент времени t). При этом 1 появится на выходе элемента И 90 или элемента И 91 в зависимости от контролируемого параметра (вторые входы соединены с соответствующими выходами дешифратора 62 блока 4 управления), р результате чего сработает

5 соответствующий триггер 92 или 93, и на индикаторной панели будет индицирован результат Годен по соответствующему параметру. В случае признания компаратором 13 объекта 3 контроля негодным сигнал 1 появится на выходе элемента И-84 и далее на выходе элемента И 88 (в момент времени t). При этом сработает триггер 96 или 97 (в зависимости от

45

30

40

50

55

контролируемого параметра и на узле 98 индикации будет индицирован , результат Не годен по соответствую- щему параметру.

Каждый кадр программы контроля заканчивается в случае, если- состояние объекта 3 контроля по данному параметру определено (Годен .или Не годен). При этом на выходе 40 блока 17 появится сигнал логического О. В результате этого в исходное состояние возвращаются счетчик 54, регистры 57 и 58 блока 4 управления, а также регистры 72 и 73 вы20

числителя 16, a на выходе узла 44 памяти установится код числа п.

По окончании тактового импульса на выходе 40 блока 17 произойдет скачок логического уровня из О в 5 1, в результате чего код на выходе счетчика 56 з меньшится на единицу (счетчик 56 работает в режиме вычита- рия), т.е. осуществится подключение следующего канала объекта 3 конт- fO роля и начнется следз тащий кадр программы контроля (например, в момент времени t и tg). До прихода нового тактового импульса на выходе соот- ветству(нцего преобразователя 1 или 2 5 будет установившееся значение Y, т.е. соответствующий канал будет готов для принятия решения о годнос - ти объекта 3 контроля.

Если в первом контрольно-измерительном такте очередного кадра программь1 на выходе элемента И 81 блока 17 логический О, что имеет место . при наличии О на выходах одного из компараторов 8 или 9, то устройство работает в критическом режиме. В этом случае проводятся несколько тактов. Каждый новый контрольно- измерительный такт начинается с появлением очередного тактового импуль са на выходе элемента И 53 блока 4 управления. При эГом код на выходе счетчика 54, отсчитьшающего число контрольно-измерительньпг тактов в г каждом кадре программы, увеличивает- 35 ся на единицу.

Вычислитель 16 суммирует коды, формируемые аналого-цифровым преобразователем 15 в каждом такте кадра программы контроля, и о ере дня е т их по .числу выборок (тактов) , проведенных с начала кадра. Причем если значение преобразованного параметра У лежит в пределах допусковой зоны, то код, соответствующий разности JX +Д- Хц| .или JX + Ь - Xgl, при суммировании учитьшается со знаком +. В этом рлучае логическая 1 с выхода ком- лдратора 13 разрешает прохождение

наличии такданного кода при тЬвого импульса через элементы И 68 на вход вычитаталя 7, где осуществляется суммирование данного кода с суммой кодов (учи- тьтаемых со знаком +) предыдущих тактов, записанной в регистр 73.

Если значение преобразованного параметра Y лежит за пределами до-г

-30

0

45

50

55

пусковой зоны, то код, соответствующий разности |Х +Д - X,,j или |Х -i- + g) при суммировании учитывается со знаком -. в этом случае данный код поступает с выхода элемента И 67 на вход сумматора 70, где суммируется с суммой кодов /учитываемых со знаком предьщущих тактов, записанной в регистр 72. Запись кодов в регистры 72 и 73 осу1цествляется по окончаншо тактового импульса, т.е. в момент перехо- да логического уровня на выходе ин- вертора 69 из .О в 1. Вычитатели 75 и 74 вычисляют разности соответственно N и Н ,где N и N суммы кодов, учитьшаемых со знаком

и

соответственно.

20

5

35

Компаратор 76 сравн ивает коды

WH N

и в -зависимости от trx соотношения формирует сигнал О или 1, поступающий на управляющий вход коммутатора 77. При этом, если выпол- .няется условие N (на выходе компаратора 76 логическая I), то коммутатор 77 подключает к первому входу делителя 79 выход вычитателя 75, вьшолняющего операцию N - N. Если вьшолняется условие N 30 (на выходе компаратора 76 О), то к первому входу делителя 79 подключается выход вычитателя 74, выполняющего операцию N .

По окончании минимально необходимой серии из Пд тактов или таобой

дополнительной тактовой серии на пятом входе вьгаислителя 16 появится логическая 1, открьшающая элемент И 80,и.разрешающая деление кода, ступившего с выхода вычитателя 74- или 75, на код числа проведенных тактов, поступивший с выхода счетчика 54 блока 4 управления делителем 7 9. С информационного выхода де45 лителя 7 снимается код результата деления N., , а с управляющего вы-- хода - сигнал конца деления (логи-, ческая 1). Кроме того, на первом выходе вычислителя 16 снимается

50 сигнал 1, если среднее значение кода N,, О, т.е. не вьшолняется условие N N.

По окончании-очередной тактовой серии коды на выходах узла 44 памя-- ти, определяющего число тактов, которое должно быть приведено, и счетчика 54, подсчитьшающего число проведенных TaicTOB, будут равны, в ре11Т29193012

новкой в исходное состояние всех клавиш клавиатуры 43 блока 4 управления ;

Исходя из описания устройства, удет равен или больше среднего кода 5 достижение повышения быстродействия ,после проведения предыдущей так- устройства обеспечивается введением

второго коммутатора 14, цифроанало- гового преобразователя 15, вычислите ля 16 и блока 17 обработки и регист- 0 рации информации с соответствующими связями.

Граничное значение &г выбираг ют с учетом того, чтобы вероятность принятия погрешностью д значения.

зультате чего на выходе компаратора 55 появится логическая 1. При этом, если средний код N;- после проведения очередной тактовой серии

товой серии, записанного в регистре 58, то на выходе компаратора 59 бу-. дет логический О, а сигнал 1 с

выхода инвертора 64 через элемент И 65, открытый логическими 1 с выхода компаратора 55 .и элемента 63 задержки (время задержки должно быть больше времени сравнения компаратора 59 и задержки инвертора 64) превьш1ающего граничное значение дг, поступит на вход 41 блока 17, в ре- была не;больше заданной абсолют20

зультате чего последний сформирует суждение Годен (в момент времени ). Если вьшолняется условие N;,j ,.-,TO логическая 1 появится на выходе элемента И 60 (в момент времени t),B результате чего в регистр 57 запишется очередное среднее значение кода, которое поступит на ад25

ной ошибки II рода|,дд, т.е. вероятности принятия ошибочного решения Годен. Например, если известно, что погрешность преобразования распределена по нормальному закону с дисперсией G , то значение Л г выбирают, исходя из выполнения условияд

Рбал

0,5- Ф()

дг G

.

2

где

Kf) I

Ф

-2

Tlfe (3z табуловия

(1)

ресный вход узла 44 памяти, на выходе которого появится записанный , по соответствующему адресу код нового числа п; контрольно-измерительных тактов, в результате чего будет проведена дополнительная се- 30 лированная интегральная функция нор- рия из unj тактов.мального закона распределения.

Если при работе в критическом Назначенное число контрольно-из- режиме после проведения очередной мерительных тактов Пд при работе уст- тактовой серии среднее значение кода ройства в критическом режиме опре- i О, т.е. если среднее значение 35 Я&ля&тс-я, исходя из выполнения ус- преобразованного параметра лежит за пределами допусковой области или в непосредственной близости от одного из допусков, то логическая 1 с

первого выхода вычислителя 16 посту- 40 Д Vi, f коэффициент Стью- пит на вход 35 блока 17, в результа- дента при 1 степени свободы те чего последний примет суждение и доверительной веростности 1-рздд/2. Не годен (в момент времени tg). Выполнение условия (if означает.

После проведения последнего кадра что вероятность того, истинное программы, т.е. когда объект 3 конт- 45 значение разности JX +Л- Xg или ррля проконтролирован по всем па- jX +й - Xj,l отличается вт среднего раметрам, на выходе переноса счетчи- значения N;, ,определенного по п вы- ка 55 блока 4 управления появится боркам, более чем на дг, кии дру- сигкал О (в момент времени tg), гими словами, вероятность того, что пин возвращении которого в прежнее 50 истинное значение контролируемого состояние 1 сработает триггер 6 параметра лежит за пределами допус- (в момент времени t), и логический О с выхода триггера 61 закроет элемент И 53, чем запретит прохож- Очевидно, что если среднее знао- дение через элемент И 53 тактовых. 55 чение N;

t - , %-м 2 б

PIIA.

Ь

ка, если N Лг,не превышаетр д/2

ii.

меньше дг, то выполнение условия (1 не обеспечивает заданной достоверности результата Годен, что обуславливает заданной достоверности результата Годен, что обусимпульсов с выхода генератора 52 тактодьЕс импульсов.

Возвращение устройства в исходное состояние осуществляется уста0

5

ной ошибки II рода|,дд, т.е. вероятности принятия ошибочного решения Годен. Например, если известно, что погрешность преобразования распределена по нормальному закону с дисперсией G , то значение Л г выбирают, исходя из выполнения условияд

Рбал

0,5- Ф()

дг G

.

2

где

Kf) I

Ф

-2

Tlfe (3z табу0 лированная интегральная функция нор- мального закона распределения.

ловия

Наз мерите ройств Я&ля&т

(1)

Назначенное число контрольно-из- ительных тактов Пд при работе уст- ства в критическом режиме опре- я&тс-я, исходя из выполнения ус-

Vi, f коэффициент Стью- та при 1 степени свободы оверительной веростности 1-рздд/2. олнение условия (if означает.

t - , %-м 2 б

PIIA.

Ь

что вероятность того, истинное значение разности JX +Л- Xg или jX +й - Xj,l отличается вт среднего значения N;, ,определенного по п вы- боркам, более чем на дг, кии дру- гими словами, вероятность того, что истинное значение контролируемого параметра лежит за пределами допус- Очевидно, что если среднее знао- чение N;

ка, если N Лг,не превышаетр д/2

что вероятность того, истинное значение разности JX +Л- Xg или jX +й - Xj,l отличается вт среднего значения N;, ,определенного по п вы- боркам, более чем на дг, кии дру- гими словами, вероятность того, что истинное значение контролируемого параметра лежит за пределами допус- Очевидно, что если среднее знао- чение N;

ii.

меньше дг, то выполнение условия (1 не обеспечивает заданно достоверности результата Годен, что обуславливает заданной достоверности результата Годен, что обус лавливает необходимость -проведения дополнительных Дп, п, - п выборок, где п определяется из условия

Ni,,

..

б

(2)

Проведение дополнительных тактовых серий прекращается в том случае, если значение N,- , осредненное по п . Шз1боркам, удовлетворяет условию ;, N ;. . В этом случае выполняется условие

t .

J-,H-fi,o.A/2 б S

(3)

означающее, что вероятность того, что истинное значение разности , |Х +& - Хе1 или Х + Ь - Хн1 отличается от среднего значения - ,nj+) определенного по п: выборкам, более чем на N;,,. , или вероятность того, что истинное значение контролируемого параметр а лежит за пределами допуска, если N,-:, г i N;j , не превышает (, в ре-.- зультате чего достоверность результата Годен не ниже заданной.

Таким образом, при работе в кри- тическом режиме5 когда решение о годности объекта 3 контроля по контролируемому параметру:может быть неверным из-за влияния на резуль- тат преобразования Y случайной по грешности преобразователя 1 или 2, формируется статическое решение о годности объекта 3 контроля с заданной достоверностью по результатам нескольких контрольно-измерительных тактов.

Но количество контрольно-измерительных тактов при работе в критическом режиме в каждом кадре программы не постоянно в отличие от известного устройства, в результате чего достигается повышение быстродействия устройства. Это объясняется тем, что при работе в критическо режиме статистическое решение о годности объекта 3 контроля с заданной достоверностью может быть принято не только после проведения я конт- рольнр-измерительных тактов (как эт делалось в известном устройстве), но и значительно раньше - после про .ведення т(га Пр,п,п,...) тактов, если данное число выборок значений

O

5

0

5

контролируемого параметра уже достаточно для принятия решения о годности объекта 3 контроля с заданной достоверностью.

Выигрьш в быстродействии особенно значительный при больших погрешностях преобразователей 1 и 2, так как в известном устройстве при уве- погрешности uf увеличршает- ся вероятность работы устройства в .критическом режиме, а также требуемое число п контрольно-измеритель ных тактов для формирования статистического решения о годности объекта 3 контроля, причем число h остается постоянным в течение каждого кадра программы.

Таким образом, введение в устройство для контроля параметров второго коммутатора 14, цифроаналогового преобразователя 15, вычислителя 16 и блока 7 обработки и регистрации информации с соответствующими связями позволяет уменьшить время контроля параметров, т.е. повысить быстродействие устройства. Это, в свою очередь, позволяет снизить требование к точности работы преобразователей I и 2, что повьшхает быстродействие устройства.

Формула изобретения

1.Устройство для контроля парамет- 5 ров, содержащее преобразователи параметров, входы данных которых являются входами устройства, управляющие входы соединены с выходами группы блока управления, а выходы - с информационными входами первого коммутатора, выход которого подключен к первым входам первого и второго вычита- телей, выходы которых соединены с первыми входами первого и второго компараторов, вторые входы которых соединены с выходом первого источника опорного напряжения, первый выход блока управления соединен с взводом первого источника опорного напряжения, второй и третий выходы. - со входами второго и третьего источников опорного напряжения, выходы которых соединены со вторыми входами первого и второго вьгчитателей, 5 четвертый вькод блока управления связан с управляющим входом третьего компаратора, отличающееся тем, что, с целью повьш1ения быстродействия устройства, в него.

0

0

5

0

15

введены второй коммутатор, аналого- цифровой преобразователь, вычислитель и блок обработки и регистрации информации, выход которого соединен с первым входом блока управления, выходы группы которого подключены к входам группы блока обработки и регистрации информации, четвертый выход - к первым входам вычислителя и блока обработки и регистрации информации и к управляющему входу аналого-цифрового преобразователя, первый выход вычислителя подключен ко второму входу блока обработки и регистрации информации выходы первого и второго компараторов соединены с соответствующими управляющими входами второго коммутатора и с третьим и четвертым входми обработки и регистрации информации соответственно, пятый и шестой выходы блока управления подключены к пятому и шестому входам блока обработки и регистрации информации соответственно, седьмой выход - к управляющему входу первого коммутатора, выход которого соединен с первым входом третьего компаратора, второй и третий входы которого соответственно соединены с выходами второго и третьего источников опорного напряжения, а выход подключен к седьмому входу блока обработки и регистрации информации и второму входу вьиислителя, второй и третий выходы которого соответственно соединены с вторым и третьим входами блока управления, выходы с восьмого по десятьш которого соединены соответственно с входами с третьего по пятый вычислителя, вьпсод аналого- цифрового преобразователя подключен к шестому входу вычислителя, вьпсоды первого и второго вычитателёй соединены с соответствующими информацонными входами второго коммутатора выход которого подключен к инфор- мационному входу аналого-цифрового преобразователя.

2. Устройство по п.1, о т л и- чающееся тем, что блок упрления содержит четыре узла памяти, два элемента ИЛИ, четыре элемента два инвертора, генератор тактовых импульсов, два счетчика, два компаратора, два регистра, триггер, дешратор, элемент задержки и клавиатуру, четыре выхода которой соответс

16

5

0

5

венно подк:..чены к входам управления узлов памяти с первого по четвертьм пятый ВЫХОД - к входам данных узлов памяти с первого по четвертый и к входу установки первого счетчика, шестой выход - к первым входам первого и второго элементов ИЛИ, выходы которых подключены к адресным входам первого узла памяти и к объединенным адресным входам узлов, памяти со второго по четвертый соответственно,. выход первого узла памяти соединен с первым входом первого компаратора, а выходы второго, третьего и четвертого узлов памяти являются третьим, вторым и первым выходами блока соответственно, седьмой выход клавиатуры подключен к первым входам первого и второго элементов И, к входу установки в О триггера и.является пятым выходом блока, восьмой выход - к входу сброса первого счетчика и к управляющему входу дешифратора, девятый выход - к стробирующему входу счетчика, счетный вход которого и второй вход первого элемента И являются первым входом блока, информационные входы первого и второго регистров и первый вход второго компаратора являются третьим входом блока, выход первого элемента И является восьмьм выходом блока, соединен с -установочными входами первого и.второт о регистров и через инвертор подключен к 5 входу сброса второго счетчика, выход генератора тактовых импульсов соединен со вторым, а выход триггера - с третьим входами второго элемента И, выход которого является четвертым выходом блока и подключен к счетному входу второго счетчика, выход которого является девятым выходом блока и соединен со вторым входом первого компаратора, выход которого является деся ым выходом i бЛока и соединен со стробирующим входом второго регистра и с первыми входами третьего и четвертого элементов И, вькоды первого и второго регистров соединены соответственно со вторым входом первого элемента ИЛИ и со вторым входом второго компаратора, выход которого подключен ко второму входу третьего элемента И и . через второй инвертор ко второму входу четвертого элемента И, выход которого является шестым выходом б лока, выход переполнения первого счетчика соединен с входом уста0

0

5

0

17 ;

новки в 1 триггера, кодовый выход счетчика является седьмым выходом блока, подключен ко второму входу второго элемента ИЛИ и к информационным входам дешифратора, выходы ;которого являются выходами группы блока, второй вход блока через элемент задержки подключён к третьим входам третьего и четвертого элементов И, выход третьего элемента И сое динен со стробирующим входом первого регистра.

3, Устройство по п.1, о т л и - чающееся тем, что вычислитель содержит три инвертора, три элемента И, два сумматора, два регистра, компаратор, коммутатор, делитель и два вычитателя, первые входы первого и второго элементов И и вход первого инвертора являются первым входом вычислителя, второй вход второго элемента И и вход второго инвертора являются вторым входом вычислителя, второй вход первого и третий вход второго элементов И являются шестым входом вьиислителя, выход второго инвертора подключен к третьему входу первого элемента И выход которого и выход второго элемента И соответственно соединены с первыми входами первого и второго сумматоров, выходы которых соответственно подключены к объединенным информационному входу первого регистра, первым входом первого и в торого вычитателей и первому входу компаратора, к объединенным вторым входам первого и второго вычитателей, второму входу компаратора и информационному входу второго регистра, выходы первого и второго регистров соединены со вторыми входами первого и второго сумматоров соответственно, вькоды первого и второго вычитателей и выход компаратора подключены к соответствующим входам коммутатора, выход которого соединен с одним информационньм входом делителя, другой информационный вход которого является четвертым входом вычислителя, выход компаратора через третий инвертор подключен к первому входу третьего элемента И,

91930 18

второй вход которого и управляющий вход делителя являются пятым входом вычислителя, выход третьего элемента И и выходы делителя являют- 5 ся с первого по третий выходами вычислителя соответственно, выход первого инвертора подключен к синхро- входам первого и второго регистров, входы установки в О которых яв- to ляются третьим входом вычислителя, 4. Устройство по п.1, о т л и - чающееся тем, что блок обработки и регистрации информации содержит пять элементов И, инвертор,

5 два элемента ИЛИ, элемент ИЛИ-НЕ, две группы элементов И, две группы триггеров и узел швдикации, входы первого элемента И являются четвертым и третьим входами блока соот20 ветственно, вход инвертора и первый вход второго элемента И являются седьмым входом блока, первые входы первого и второго элементов ИЛИ являются шестым и вторым входами

блока соответственно, первые входы третьего и четвертого элементов И являются первым входом блока, выход инвертора подключен к первому входу пятого элемента И, выход первого

У} элемента И соединен со вторыми входами второго и пятого элементов И, выходами подключенных соответственно ко вторым входам первого и второго элементов ИЛИ, выходы которых под35 ключены ко вторым входам третьего и четвертого элементов И соответственно, вькод третьего элемента И соединен с первым входом элемента ИЛИ-НЕ и с первыми входами элементов И пер40 вой группы, выход четвертого элемента И подключен ко второму входу элемента ИЛИ-НЕ и к первьм входам элементов И второй группы, вторые входы элементов И первого и второй групп

45 являются группой входов блока, выходы элементов И первой и второй групп подключены к установочным входам триггеров первой и второй групп соответственно, входы установки триг50 геров первой и второй групп являются пятым входом блока, а выходы подключены к соответствующим входам узла индикации, выход элемента ИЛИ-НЕ является выходом блока.

20

аив.3

36 41

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параметров | 1985 |

|

SU1254441A1 |

| Устройство для контроля | 1986 |

|

SU1390617A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2013 |

|

RU2517322C1 |

| Устройство для автоматизированного контроля параметров | 1988 |

|

SU1647520A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2012 |

|

RU2517316C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2012 |

|

RU2517317C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ДИФФЕРЕНЦИРУЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2535467C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2450343C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2451328C1 |

| Устройство для контроля параметров | 1980 |

|

SU960743A2 |

Изобретение относится к области контрольно-измерительной техники и может быть использовано при пострс ении систем автоматизированного .контроля многопараметрических объектов. Цель изобретения - повьпаение быстродействия устройства. Поставленная цель достигается введением в устройство для контроля параметров второго коммутатора, цифроаналогового преобразователя, вьмислителя и блока обработки и регистрации информации с соответствующими связями и основывается на формировании статистического решения о годности с заданной достоверностью после проведения сокращенного числа контрольных тактов за счет текущего усреднения результатов и коррекции числа последующих контрольно-измерительных тактов. 3 3.п. ф-лы, 5 ил. i СП

t,tjiit,ts

Составитель И.Алексеев Редактор В.Данко Техред И.Попович Корректор М.Самборская

Заказ 261/45 Тираж 864Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная 4

t,tj

Фи9.5

t ti

| Дискретная система автоматического контроля и измерения параметров | 1978 |

|

SU746559A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля параметров | 1980 |

|

SU960743A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-02-23—Публикация

1985-05-23—Подача