торому выходу блока 4 программирования, третий и четвертый выходы ко-, торого соединены с входами BTOpot-o и первого источников 11 и 12 опорного напряжения, выходы которых соединены с вторыми выходами первого и второго блоков 6 и 7 вычитания, вычислитель 13, выход которого соединен с входом счетчика 14, а управ- ляющий вход подключен к пятому выходу блока 4 программирования, а также дополнительно введенные оперативное запоминающее устройство 15, компаратор 16 кодов и блок 17 обработки и регистрации информации, первый выход которого соединен с входом блока 4 программирования, второй выход которого соединен с управляющим входом счетчика 14, первые входы подключены к первым выходам блока 4 программирования, второй и третий входы подключены к выходам соответственно первого и второго комI

Изобретение относится к контрольно-измерительной технике и может быть использовано при построении систем автоматизированного контроля многопараметрических объектов.

Цель изобретения - повьшение быстродействия уст зойства.

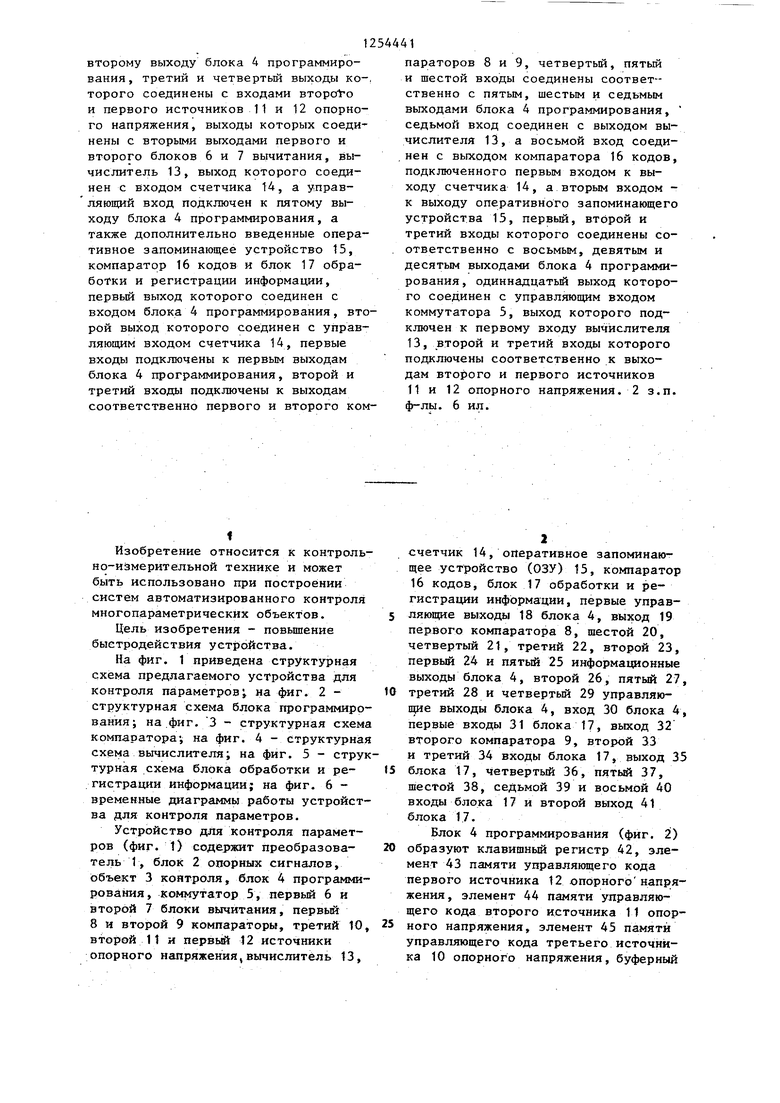

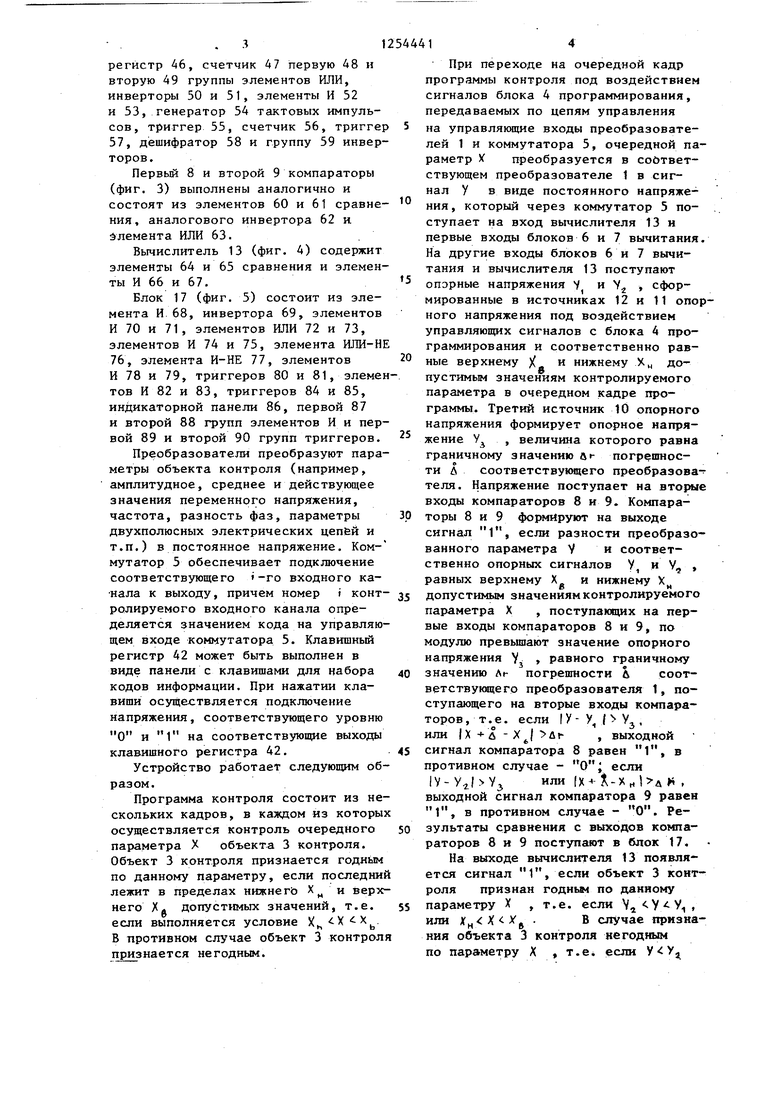

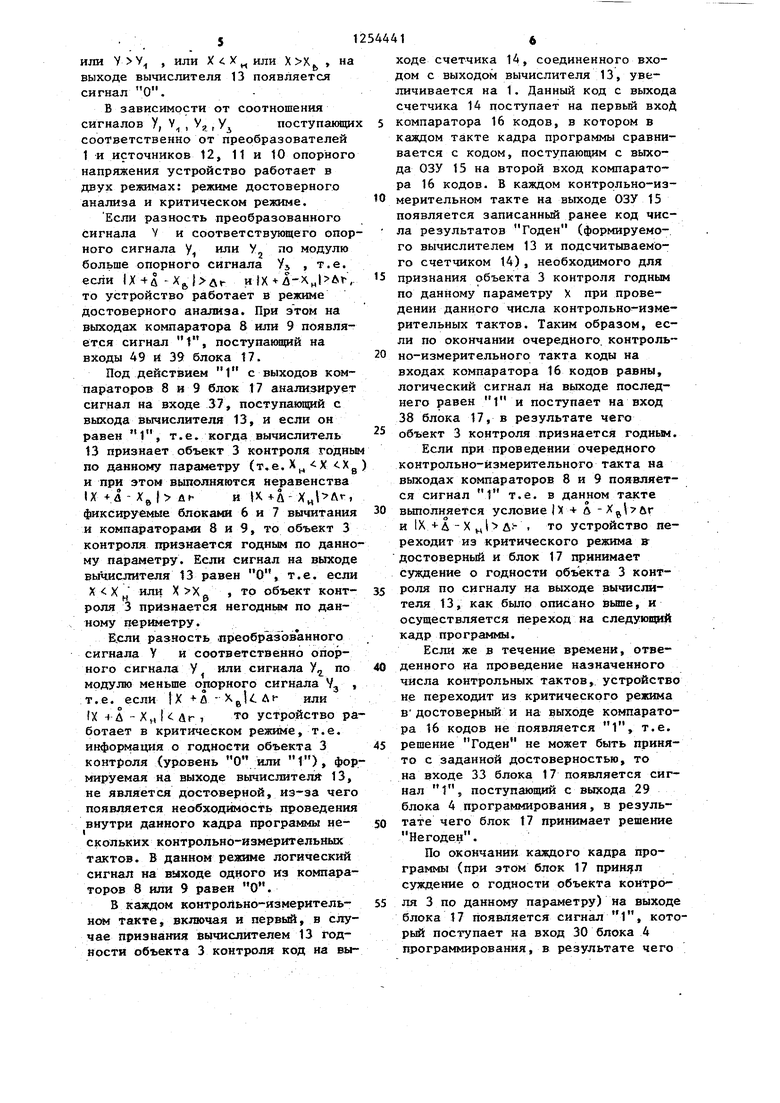

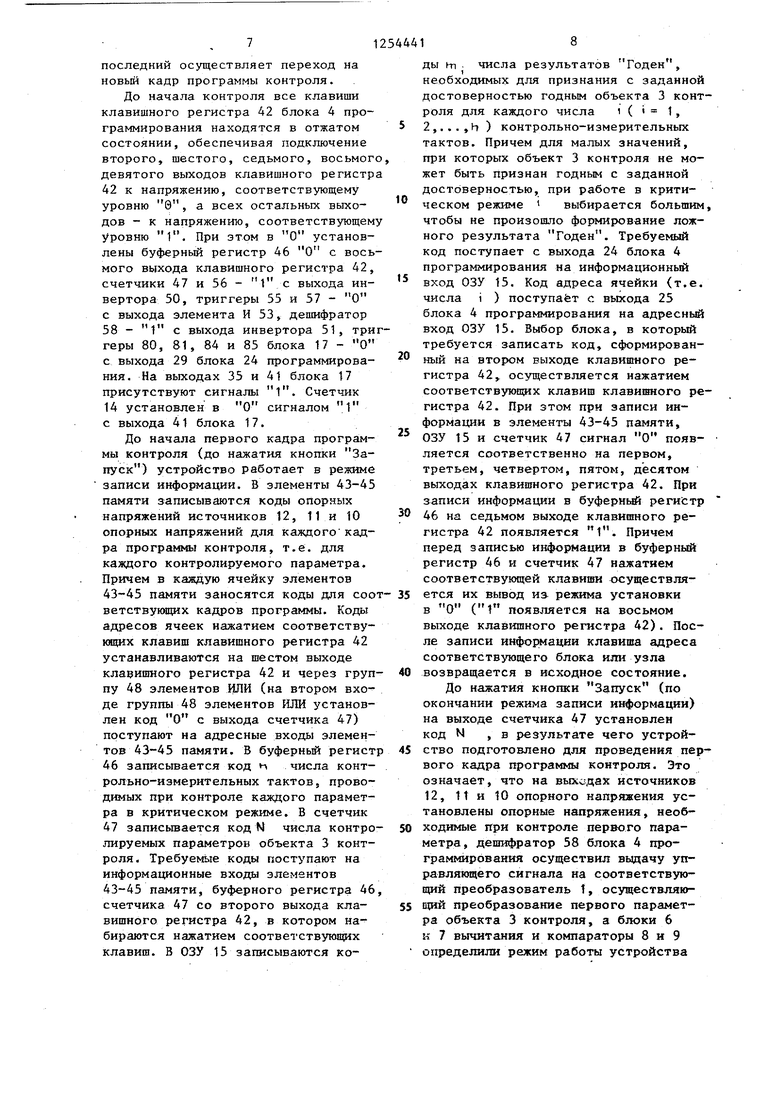

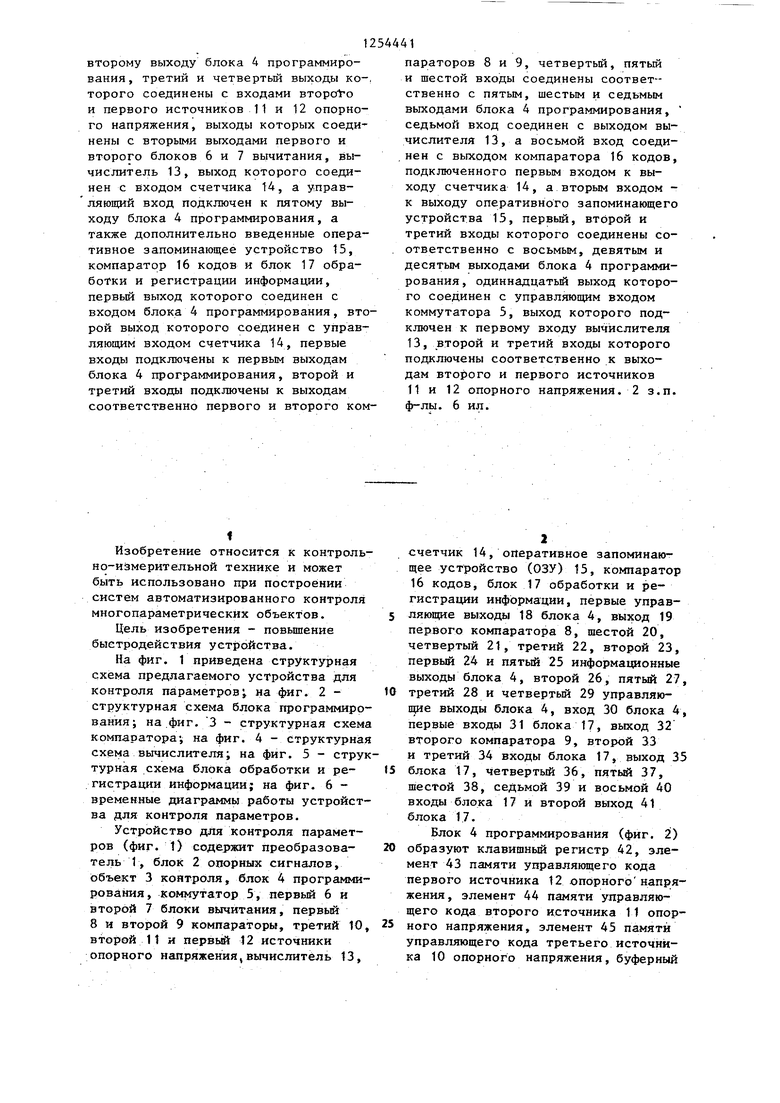

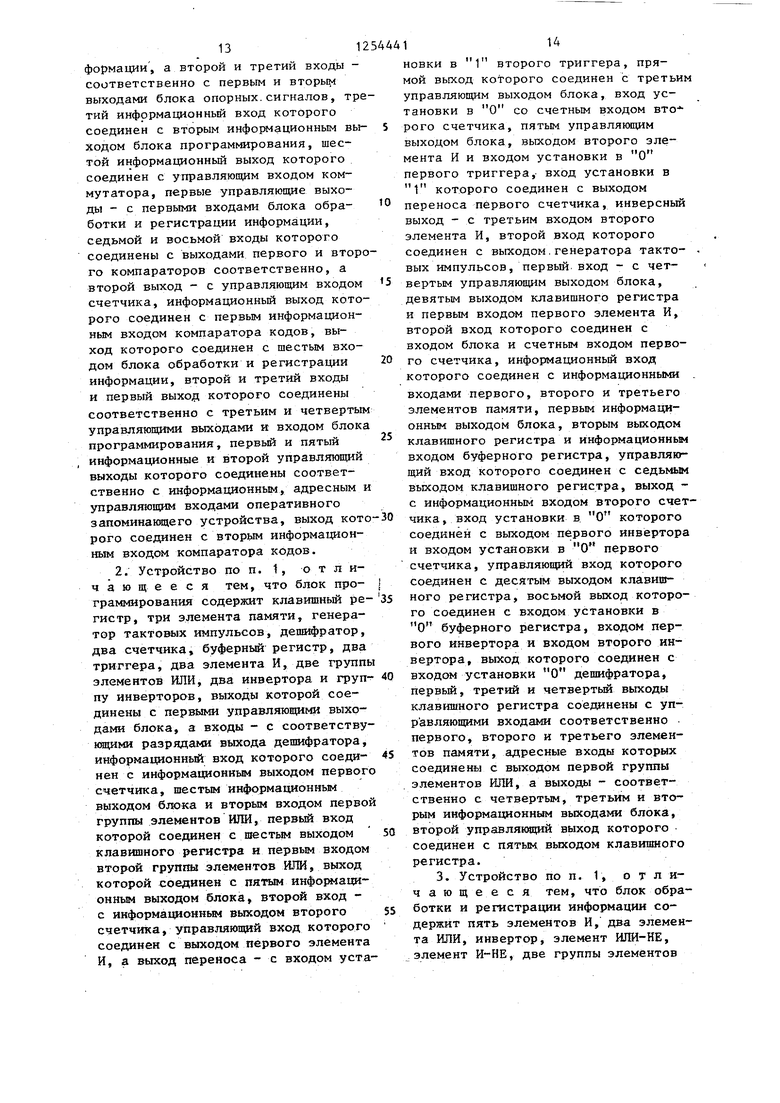

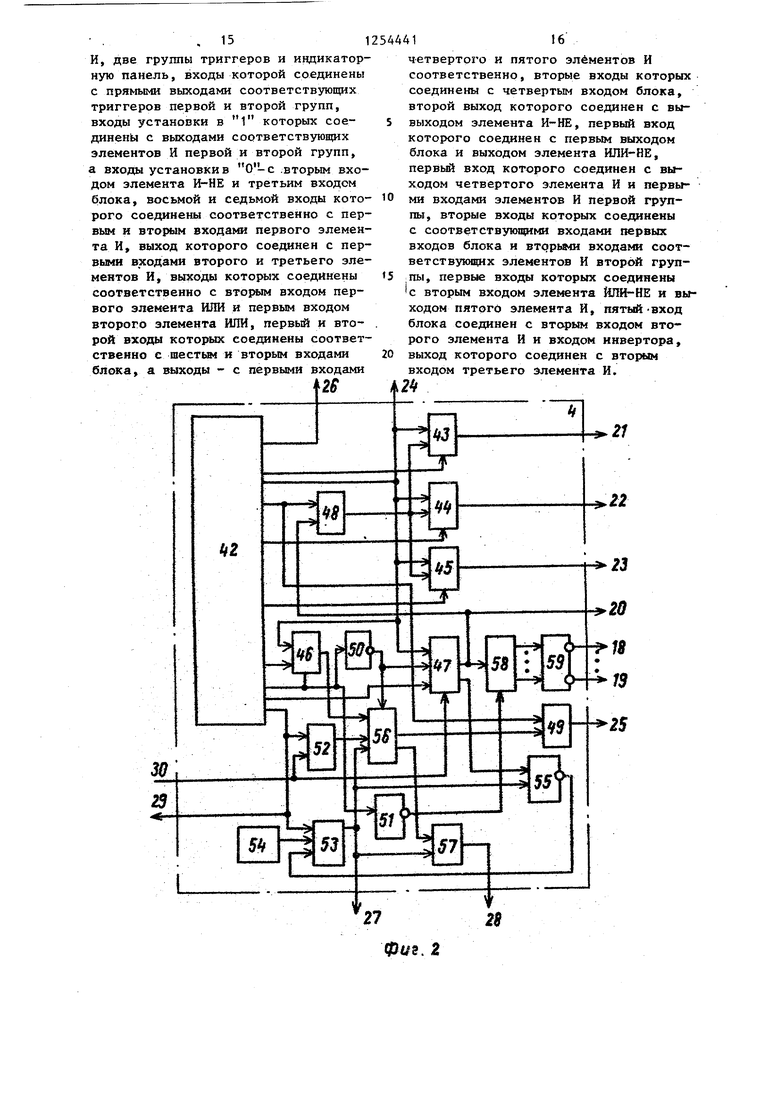

На фиг. 1 приведена структурная схема предлагаемого устройства для контроля параметров на фиг. 2 - структурная схема блока программирования; на.фиг. 3 - структурная схема компаратора , на фиг. 4 - структурная схема вычислителя; на фиг. 5 - структурная схема блока обработки и регистрации информации; на фиг. 6 - временные диаграммы работы устройства для контроля параметров.

Устройство для контроля параметров (фиг. 1) содержит преобразователь 1, блок 2 опорных сигналов, объект 3 контроля, блок 4 программирования, коммутатор 5, первый 6 и второй 7 блоки вычитания, первьй 8 и второй 9 компараторы, третий 10, второй 11 и первый 12 источники опорного напряжения,вычислитель 13,

параторов 8 и 9, четвертый, пятый и шестой входы соединены соответственно с пятым, шестым и седьмым выходами блока 4 программирования, седьмой вход соединен с выходом вычислителя 13, а восьмой вход соединен с выходом компаратора 16 кодов, подключенного первым входом к выходу счетчика 14, а вторым входом - к выходу оперативного запоминающего устройства 15, первый, второй и третий входы которого соединены со- ответственно с восьмым, девятым и десятым выходами блока 4 программирования, одиннадцатьй выход которого соединен с управляющим входом коммутатора 5, выход которого подключен к первому входу вычислителя 13, второй и третий входы которого подключены соответственно к выходам второго и первого источников 11 и 12 опорного напряжения. 2 з.п. ф-лы. 6 ил.

счетчик 14, оперативное запоминающее устройство (ОЗУ) 15, компаратор 16 кодов, блок 17 обработки и регистрации информации, первые управ- ляющие выходы 18 блока 4, выход 19 первого компаратора 8, шестой 20, четвертый 21, третий 22, второй 23, первый 24 и пятый 25 информационные выходы блока 4, второй 26, пятый 27,

третий 28 и четвертый 29 управляющие выходы блока 4, вход 30 блока 4, первые входы 31 блока 17, выход 32 второго компаратора 9, второй 33 и третий 34 входы блока 17, выход 35

блока 17, четвертый 36, пятый 37, шестой 38, седьмой 39 и восьмой 40 входы блока 17 и второй выход 41 блока 17.

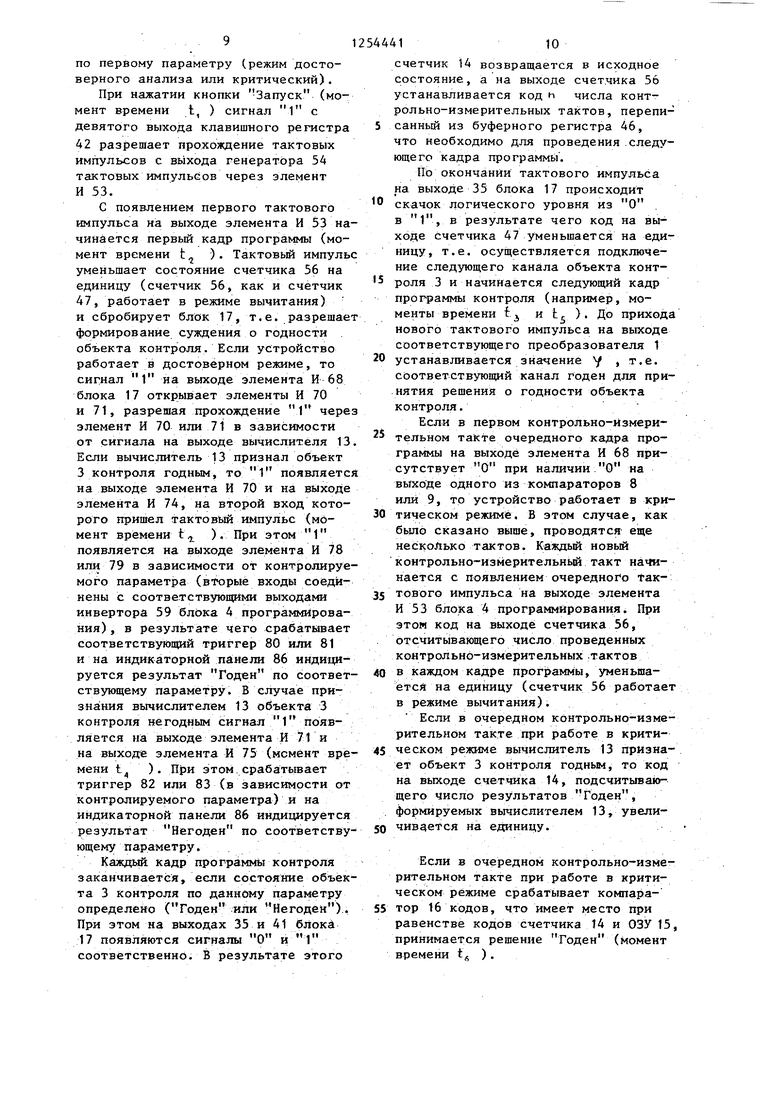

Блок 4 программирования (фиг. 2)

образуют клавишный регистр 42, элемент 43 памяти управляющего кода первого источника 12 опорнопэ напряжения , элемент 44 памяти управляющего кода второго источника 11 опорного напряжения, элемент 45 памяти управляющего кода третьего источника 10 опорного напряжения, буферный

регистр 46, счетчик 47 первую 48 и вторую 49 группы элементов ИЛИ, инверторы 50 и 51, элементы И 52 и 53, генератор 54 тактовых импульсов, триггер 55, счетчик 56, триггер 57, дешифратор 58 и группу 59 инверторов.

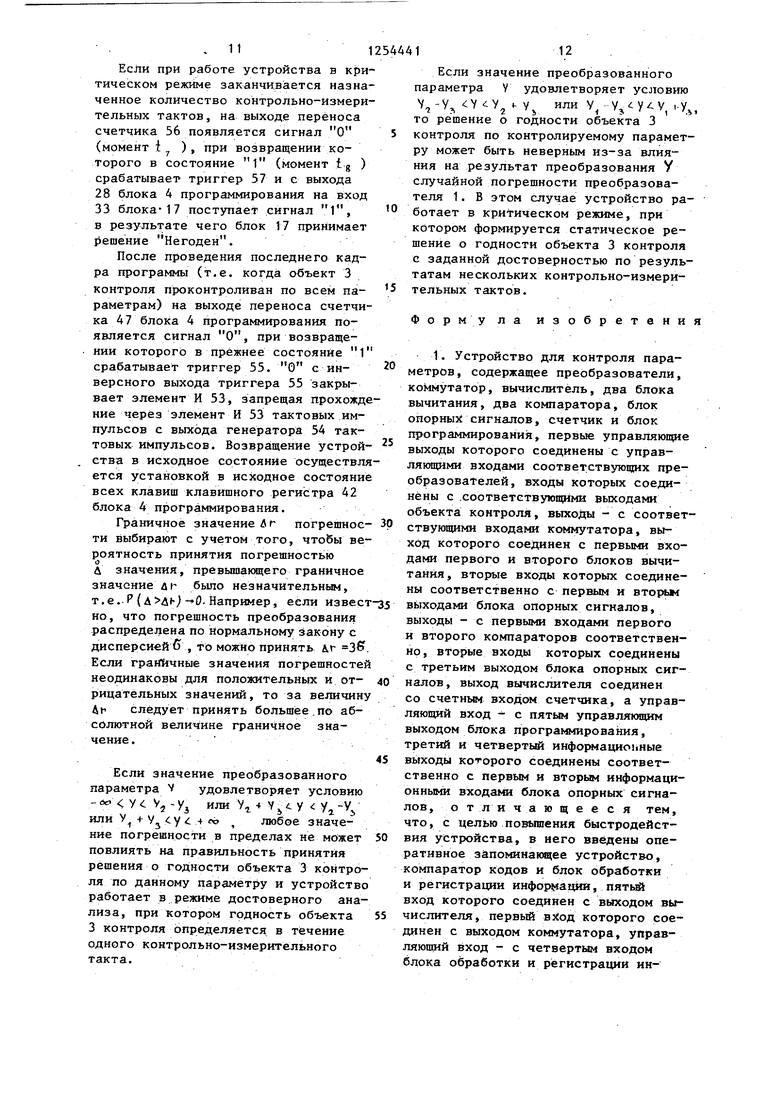

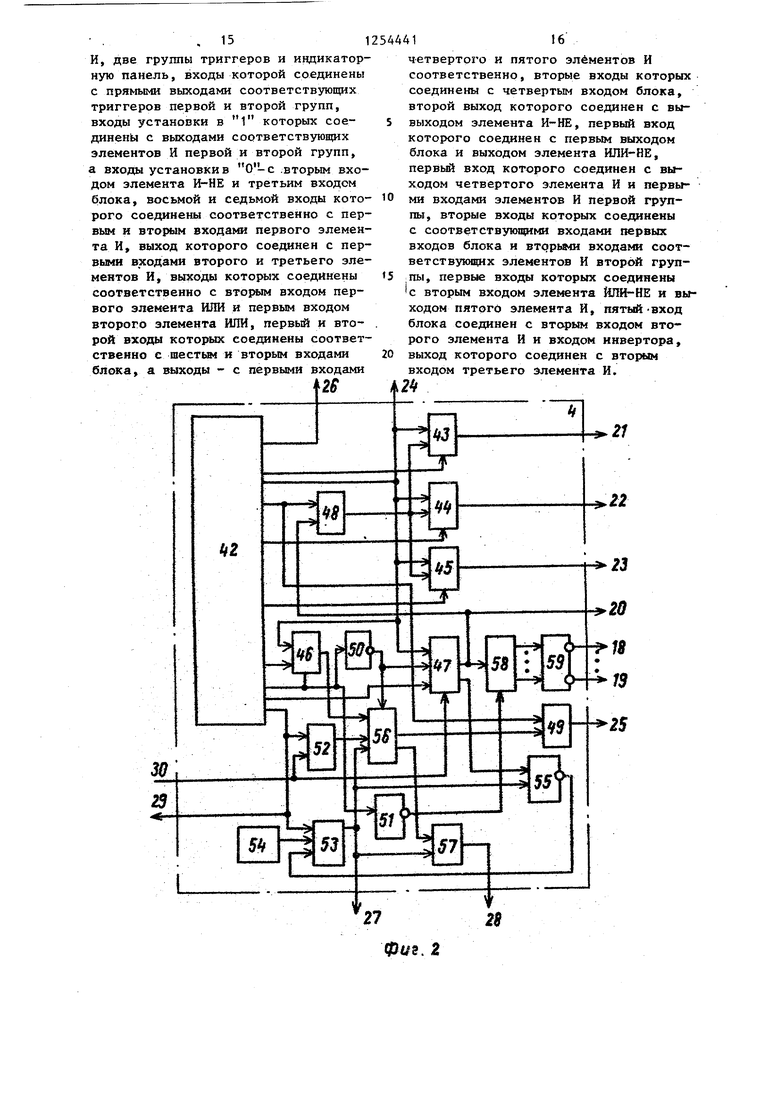

Первьй 8 и второй 9 компараторы (фиг. 3) выполнены аналогично и состоят из элементов 60 и 61 сравнения, аналогового инвертора 62 и :5лемента ИЛИ 63.

Вычислитель 13 (фиг. 4) содержит элементы 64 и 65 сравнения и элементы И 66 и 67.

Блок 17 (фиг. 5) состоит из элемента И 68, инвертора 69, элементов И 70 и 71, элементов ИЛИ 72 и 73, элементов И 74 и 75, элемента ИЛИ-НЕ 76, элемента И-НЕ 77, элементов И 78 и 79, триггеров 80 и 81, элементов И 82 и 83, триггеров 84 и 85, индикаторной панели 86, первой 87 и второй 88 групп элементов И и первой 89 и второй 90 групп триггеров.

Преобразователи преобразуют параметры объекта контроля (например, амплитудное, среднее и действующее значения переменного напряжения, частота, разность фаз, параметры двухполюсных электрических цепЁй и т.п.) в постоянное напряжение. Ком- мутатор 5 обеспечивает подключение соответствующего -го входного ка- нала к выходу, причем номер i конт- ролируемого входного канала определяется значением кода на управляющем входе коммутатора 5. Клавишный регистр 42 может быть выполнен в виде панели с клавишами для набора кодов информации. При нажатии клавиши осуществляется подключение напряжения, соответствующего уровню О и 1 на соответствующие выходы клавишного регистра 42.

Устройство работает следующим образом.

Программа контроля состоит из нескольких кадров, в каждом из которых осуществляется контроль очередного параметра X объекта 3 контроля. Объект 3 контроля признается годным по данному параметру, если последний

лежит в пределах нижнегь

и верхнего Хд допустимых значений, т.е. если выполняется условие Х. В противном случае объект 3 контроля признается негодным.

При переходе на очередной кадр программы контроля под воздействием сигналов блока 4 программирования, передаваемых по цепям управления на управляющие входы преобразователей 1 и коммутатора 5, очередной параметр У преобразуется в соответствующем преобразователе 1 в сигнал У в виде постоянного напряжения, который через коммутатор 5 поступает на вход вычислителя 13 и первые входы блоков 6 и 7 вычитания. На другие входы блоков 6 и 7 вычитания и вычислителя 13 поступают опорные напряжения V и V.j , сформированные в источниках 12 и 11 опорного напряжения под воздействием управляющих сигналов с блока 4 программирования и соответственно равные верхнему X нижнему Х„ до- пустимьм значениям контролируемого параметра в очередном кадре программы. Третий источник 10 опорного напряжения формирует опорное напряжение У,

, величина которого равна

граничному значению а г- погрешности д соответствующего преобраэова- теля. Напряжение поступает на вторые входы компараторов 8 и 9. Компараторы 8 и 9 формируют на выходе сигнал 1, если разности преобразованного параметра V и соответственно опорных СИГНАЛОВ У и V, , равных верхнему Х и нижнему Х допустимым значениям контролируемого параметра X , поступающих на первые входы компараторов 8 и 9, по модулю превышают значение опорного напряжения Vj равного граничному

значению Лс погрешности Л соот- ветствукмцего преобразователя 1, поступающего на вторые входы компараторов, т.е. если I У - У, f Y, , или |Х+л-Х | Дг , выходной сигнал компаратора 8 равен 1, в противном случае - если или (, Н , выходной сигнал компаратора 9 равен 1, в противном случае - О. Результаты сравнения с выходов компараторов 8 и 9 поступают в блок 17.

На выходе вычислителя 13 появляется сигнал 1, если объект 3 контроля признан годн1 по данному параметру X , т.е. если , или )( В случае признания объекта 3 контроля негодным по параметру X , т.е если У У

или ,

или

5

X V

1254441

или .

. f / у

13 появляется

выходе вычислителя сигнал О. В зависимости от соотношения сигналов У, V , V., , у поступающих соответственно от преобразователей 1 и источников 12, 11 и 10 опорного напряжения устройство работает в двух режимах: режиме достоверного анализа и критическом режиме.

Если разность преобразованного сигнала V и соответствующего опорного сигнала у или У,, по модулю больше опорного сигнала УЭ , т.е. если -Xg, и}Х- Л-А„| г, то устройство работает в режиме достоверного анализа. При этом на выходах компаратора 8 или 9 появляется сигнал t, поступанмций на входы 49 и 39 блока t7.

Под действием 1 с выходов ком- параторав 8 и 9 блок 17 анализирует сигнал на входе 37, поступающий с выхода вычислителя 13, и если он равен 1, т.е. когда вычислитель 13 признает объект 3 контроля годным по данному параметру (т.е. Х Xg ) и при этом выполняются неравенства lX+A-Xgf Af и (Х.+Д-Хц1 Лг, фиксируемые блокаьш 6 и 7 вычитания и компараторами 8 и 9, г о объект 3 контроля признается годным по данному параметру. Если сигнал на выходе вычислителя t3 равен О, т.е. если

, то объект конт- негодным по данX Х J или X Х„

ч. о

роля 3 признается ному периметру.

БХ:ЛИ разность .преобразов анного сигнала У и соответственно опорного сигнала У или сигнала У, по модулю меньше опорного сигнала У, ,

т.е. если }Х -й или fX Л - Хя I Лг , fo устройство работает в критическом режиме, т.е. информация о годности объекта 3 контроля (уровень О или 1), формируемая на выходе вычислителе 13, не является достовер|ной, из-за чего появляется необходимость проведения внутри данного кадра программы нескольких контрольно-измерительных тактов. В данном режиме логический сигнал на выходе одного из компараторов 8 или 9 равен О.

В каждом контрольно-измеритель- такте, включая и первый, в случае признания вычислителем 13 годности объекта 3 контроля код на вына ходе счетчика 14, соединенного входом с выходом вычислителя 13, увеличивается на 1. Данный код с выхода счетчика 14 поступает на первый вхоД 5 компаратора 16 кодов, в котором в каждом такте кадра программы сравнивается с кодом, поступающим с выхода ОЗУ 15 на второй вход компаратора 16 кодов. В каждом контррльно-из 0 мерительном такте на выходе ОЗУ 15

появляется записанный ранее код чис- ла результатов Годен (формируемого вычислителем 13 и подсчитываемого счетчиком 14), необходимого для

15 признания объекта 3 контроля годным по данному параметру X при проведении данного числа контрольно-измерительных тактов. Таким образом, если по окончании очередного, контроль20 но-измерительного такта коды на входах компаратора 16 кодов равны, логический сигнал на выходе последнего равен 1 и поступает на вход 38 блока 17, в результате чего

25 объект 3 контроля признается годным.

Если при проведении очередного контрольно-измерительного такта на выходах компараторов 8 и 9 появляется сигнал 1 т.е. в данном такте

30 выполняется условие |)( + Л и 1Х д - X J UJ- , то устройство переходит из критического режима 9 достоверньй и блок 17 принимает суждение о годности объекта 3 конт35 роля по сигналу на выходе вычислителя 13, как было описано вшпе, и осуществляется переход на следуювщй кадр программы.

Если же в течение времени, отве40 денного на проведение назначенного числа контрольных тактов, устройство не переходит из критического В достоверный и на выходе компаратора 16 кодов не появляется 1, т.е.

45 решение Годен не может быть принято с заданной достоверностью, то на входе 33 блока 17 появляется сигнал t, поступаюпщй с выхода 29 блока 4 программирования, в резуль50 тате чего блок 17 принимает решение Негоден.

По окончании каждого кадра программы (при этом блок 17 прин5 л суждение о годности объекта контро55 ля 3 по данному параметру) на выходе блока 17 появляется сигнал 1, который поступает на вход 30 блока 4 программирования, в результате чего

1254441

последний осуществляет переход на новый кадр программы контроля.

До начала контроля все клавиши клавишного регистра 42 блока 4 программирования находятся в отжатом состоянии, обеспечивая подключение второго, шестого, седьмого, восьмог девятого выходов клавишного регистр 42 к напряжению, соответствующему уровню 8, а всех остальных выходов - к напряжению, соответствующем уровню 1. При этом в О установлены буферный регистр 46 О с восьмого выхода клавишного регистра 42, счетчики 47 и 56 - 1 с выхода инвертора 50, триггеры 55 и 57 - О с выхода элемента И 53, дешифратор 58 - 1 с выхода инвертора 51, тригеры 80, 81, 84 и 85 блока 17 - О с выхода 29 блока 24 программирования. На выходах 35 и 41 блока 17 присутствуют сигналы 1. Счетчик 14 установлен в О сигналом 1 с выхода 41 блока 17.

До начала первого кадра программы контроля (до нажатия кнопки Запуск) устройство работает в режиме записи информации. В элементы 43-45 памяти записываются коды опорных напряжений источников 12, 11 и 10 опорных напряжений для каждого кадра программы контроля, т.е. для каждого контролируемого параметра. Причем в каждую ячейку элементов 43-45 памяти заносятся коды для соо ветствуюи1их кадров программы. Коды адресов ячеек нажатием соответству- кщих клавиш клавишного регистра 42 устанавливаются на шестом выходе клавишного регистра 42 и через группу 48 элементов ИЛИ (на втором вхо де группы 48 элементов ИЛИ установлен код О с выхода счетчика 47) поступают на адресные входы элементов 43-45 памяти. В буферньй регист

46записывается код числа контрольно-измерительных тактов, проводимых при контроле каждого параметра в критическом режиме. В счетчик

47записывается код N числа контролируемых параметров объекта 3 контроля. Требуемые коды поступают на информационные входы элементов 43-45 памяти, буферного регистра 46 счетчика 47 со второго выхода клавишного регистра 42, в котором набираются нажатием соответствующих клавиш. В ОЗУ 15 записываются ко

ды hi числа результатов Годен

s

0

5

5

необходимых для признания с заданной достоверностью годным объекта 3 контроля для каждого числа i ( 1, 2,...,h ) контрольно-измерительных тактов. Причем для малых значений, при которых объект 3 контроля не может быть признан годным с заданной достбверностью, при работе в критическом режиме выбирается большим, чтобы не произошло формирование ложного результата Годен. Требуемый код поступает с выхода 24 блока 4 программирования на информационный вход ОЗУ 15. Код адреса ячейки (т.е. числа i ) поступает с выхода 25 блока 4 программирования на адресньй вход ОЗУ 15. Выбор блока, в который требуется записать код, сформированный на вторюм выходе клавишного регистра 42, осзлцествляется нажатием соответствующих клавиш клавишного регистра 42. При этом при записи информации в элементы 43-45 памяти, ОЗУ 15 и счетчик 47 сигнал О появляется соответственно на первом, третьем, четвертом, пятом, десятом выходах клавишного регистра 42. При записи информации в буферн1й регистр 46 на седьмом выходе клавишного регистра 42 появляется 1. Причем перед записью информации в буферный регистр 46 и счетчик 47 нажатием соответствующей клавиши осуществляется их вывод из режима установки в О (1 появляется на восьмом выходе клавишного регистра 42). После записи информации клавиша адреса соответствующего блока или узла возвращается в исходное состояние. До нажатия кнопки Запуск (по окончании режима записи информации) на выходе счетчика 47 установлен код N , в результате чего устройство подготовлено для проведения первого кадра програмь&1 контроля. Это означает, что на выходах источников 12, 11 и 10 опорного напряжения установлены опорные напряжения, необ- ходж4ые при контроле первого параметра , дешифратор 58 блока 4 программирования осуществил вьщачу управляющего сигнала на соответствующий преобразователь 1, осуществляю- 5 вщй преобразование первого параметра объекта 3 контроля, а блоки 6 к 7 вычитания и компараторы 8 и 9 определили режим работы устройства

0

0

5

0

по первому параметру (режим достоверного анализа или критический).

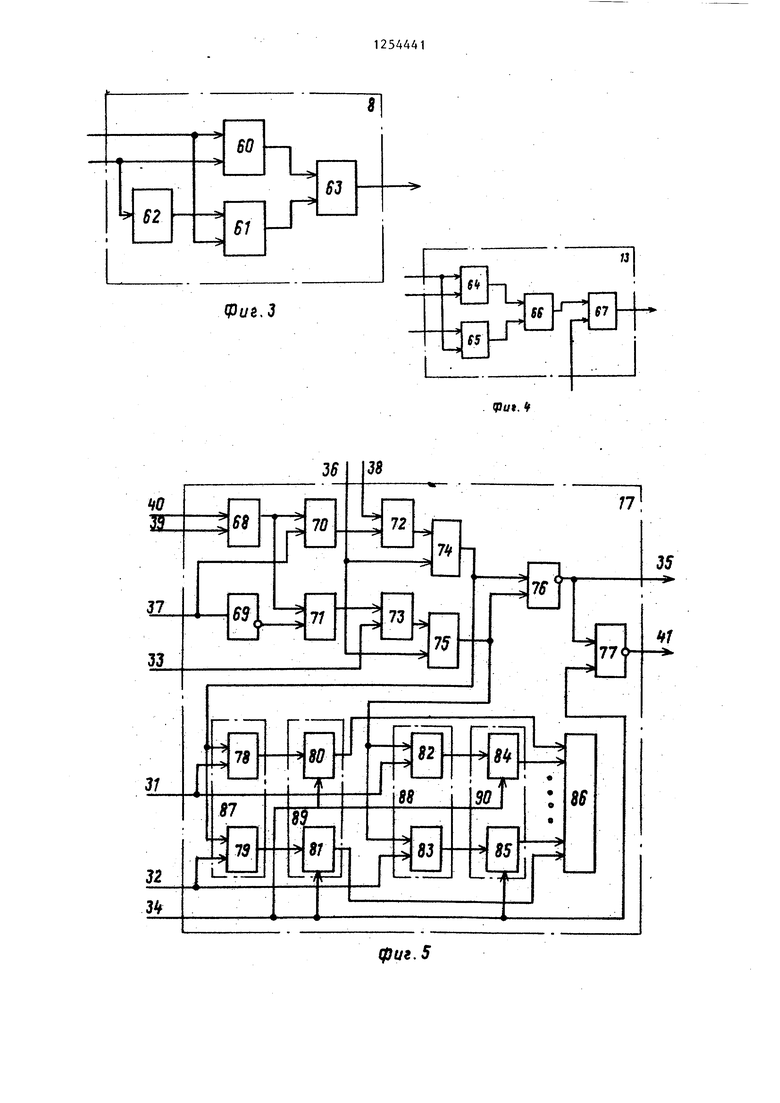

При нажатии кнопки Запуск (момент времени t, ) сигнал Г с девятого выхода клавишного регистра 42 разрешает прохождение тактовых импульсов с выхода генератора 54 тактовых импульсов через элемент И 53.

С появлением первого тактового импульса на выходе элемента И 53 начинается первый кадр программы (момент времени t,, ) . Тактовый импульс уменьшает состояние счетчика 56 на единицу (счетчик 56, как и счетчик 47, работает в режиме вычитания) и сбробирует блок 17, т.е. разрешает формирование суждения о годности объекта контроля. Если устройство работает в достоверном режиме, то сигнал 1 на выходе элемента И 68 блока 17 открывает элементы И 70 и 71, разрешая прохождение Г через элемент И 70 или 71 в зависимости от сигнала на выходе вычислителя 13 Если вычислитель 13 признал объект 3 контроля годным, то 1 появляется на выходе элемента И 70 и на выходе элемента И 74, на второй вход которого пришел тактовый импульс (момент времени t ). При этом 1 появляется на выходе элемента И 78 или 79 в зависимости от контролируемого параметра (вторые входы соединены с соответствующими выxoдa ш инвертора 59 блока 4 программирования) , в результате чего срабатывает соответствую1дай триггер 80 или 81 и на индикаторной панели 86 индицируется результат Годен по соответствующему параметру. В случае признания вычислителем 13 объекта 3 контроля негодным сигнал Г появляется на выходе элемента И 71 и на выходе элемента И 75 (момент времени t ). Еря этом срабатывает триггер 82 или 83 (в зависимости от контролируемого параметра) и на индикаторной панели 86 индицируется результат Негоден по соответствующему параметру.

Каждый кадр программы контроля заканчивается, если состояние объекта 3 контроля по данному параметру определено (Годен или Негоден), При этом на выходах 35 и 41 блока 17 появляются сигналы О и 1 соответственно. В результате этого

5444110

счетчик 14 возвращается в исходное состояние, а на выходе счетчика 56 устанавливается код и числа контрольно-измерительных тактов, перепи- 5 санный из буферного регистра 46, что необходимо для проведения .следующего кадра программы .

По окончании тактового импульса на выходе 35 блока 17 происходит скачок логического уровня из О , в 1, в результате чего код на выходе Счетчика 47 уменьшается на единицу, т.е. осуществляется подключение следующего канала объекта конт- 5 роля 3 и начинается следующий кадр

программы контроля (например, моменты времени tj и t, ). До прихода нового тактового импульса на выходе соответствунлцего преобразователя 1 устанавливается значение Y , т.е. соответствующий канал годен для принятия решения о годности объекта контроля.

Если в первом контрольно-измерительном такте очередного кадра программы на выходе элемента И 68 присутствует О при наличии.О на выходе одного из компараторов 8 или 9, то устройство работает в критическом режиме. В этом случае, как было сказано выше, проводятся еще несколько тактов. Казкдый новый контрольно-измерительньй такт начинается с появлением очередного Тактового импульса на выходе элемента И 53 блока 4 программирования. При этом код на выходе счетчика 56, отсчитывающего число проведенных контрольно-измерительных .тактов в каждом кадре программы, уменьшается на единицу (счетчик 56 работает в режиме вычитания).

Если в очередном контрольно-измерительном такте при работе в крити- ческом режиме вычислитель 13 признает объект 3 контроля годным, то код на выходе счетчика 14, подсчитывающего число результатов Годен, формируемых вычислителем 13, увеличивается на единицу.

55

Если в очередном контрольно-измерительном такте при работе в критическом режиме срабатывает компаратор 16 кодов, что имеет место при равенстве кодов счетчика 14 и ОЗУ 15, принимается решение Годен (момент времени t, ).

Если при работе устройства в критическом режиме заканчивается назначенное количество контрольно-измерительных тактов, на выходе переноса счетчика 56 появляется сигнал О (момент i ), при возвращении которого в состояние 1 (момент tg ) срабатывает триггер 57 и с выхода 28 блока 4 программирования на вход 33 блока 17 поступает сигнал 1, в результате чего блок 17 принимает решение Негоден.

После проведения последнего кадра программы (т.е. когда объект 3 контроля проконтроливан по всем па- раметрам) на выходе переноса счетчика 47 блока 4 программирования появляется сигнал О, при возвращении которого в прежнее состояние 1 срабатывает триггер 55. О с ин- версного выхода триггера 55 закрывает элемент И 53, запрещая прохождение через элемент И 53 тактовых импульсов с выхода генератора 54 тактовых импульсов. Возвращение устрой- ства в исходное состояние осуществляется установкой в исходное состояние всех клавиш клавишного регистра 42 блока 4 программирования.

Граничное значение & г погрешнос- ти выбирают с учетом того, чтобы вероятность принятия погрешностью д значения, превышакндего граничное значение Д| было незначительн1Ф1, т.е. f (. Например, если извест но, что погрешность преобразования распределена по нормальному закону с дисперсией , то можно принять 4г 3. Если граничные значения погрешностей неодинаковы для положительных и от- рицатёльных значений, то за величину 4h следует принять большее.по абсолютной величине граничное значение .

Если значение преобразованного параметра V удовлетворяет условию

- бе. у V, - у, ИЛИ

Vr у,-У,,

или У + y,j у + , любое значение погрешности в пределах не может повлиять на правильность принятия решения о годности объекта 3 контроля по данному параметру и устройство работает в режиме достоверного анализа, при котором годность объекта 3 контроля определяется в течение одного контрольно-измерительного такта.

Если значение преобразованного параметра V удовлетворяет условию

5

0 5 0

5

0 5

I- у или V

, , ,.у.,,

объекта 3

v,-y,

то решение о годности контроля по контролируемому параметру может быть неверным из-за влияния на результат преобразования У случайной погрешности преобразователя 1. В этом случае устройство ра- ботает в критическом режиме, при котором формируется статическое решение о годности объекта 3 контроля с заданной достоверностью по результатам нескольких контрольно-измерительных тактов.

Форму л а изобретения

1. Устройство для контроля параметров , содержащее преобразователи, коммутатор, вычислитель, два блока вычитания, два компаратора, блок опорных сигналов, счетчик и блок программирования, первые управляющие выходы которого соединены с управляющими входами соответствующих преобразователей, входы которых соединены с .соответствующими выходами объекта контроля, выходы - с соответствующими входами коммутатора, выход которого соединен с первыми входами первого и второго блоков вычитания, вторые входы которых соединены соответственно с первым и вторьм вь1хода в1 блока опорных сигналов, выходы - с первыми входами первого и второго компараторов соответственно, вторые входы которых соединены с третьим выходом блока опорных си1- налов, выход вычислителя соединен со счетнь входом счетчика, а управляющий вход - с пятым управляющим выходом блока програья ирования, третий и четвертьй информационные выходы которого соединены соответственно с первым и вторьа4 информаци- онньп№ вxoдa ш блока опорных сигналов, о тли ча ю щ е е с я тем, что, с целью пок 1шения быстродействия устройства, в него введены оперативное запоминающее устройство, компаратор кодов и блок обработки и регистрации инфор ации, пятьй вход которого соединен с выходом вычислителя, первый вход которого соединен с выходом коммутатора, управляющий вход - с четвертым входом блока обработки и регистрации ин

131

формации , а второй и третий входы - соответственно с первым и вторым выходами блока опорных.сигналов, третий информационный вход которого соединен с вторым информационным вы- Ходом блока программирования, шестой информационный выход которого соединен с управляющим входом коммутатора, первые управляющие выходы - с первыми входами блока обра- ботки и регистрации информации, седьмой и восьмой входы которого соединены с выходами первого и второго компараторов соответственно, а второй выход - с управляющим входом счетчика, информационный выход которого соединен с первым информационным входом компаратора кодов, выход которого соединен с шестым входом блока обработки и регистрации информации, второй и третий входы и первый выход которого соединены соответственно с третьим и четвертым управляющими выходами и входом блока программирования, первьй и пятый информационные и второй управляющий выходы которого соединены соответственно с информационным, адресным и управляющда входами оперативного запоминакицего устройства, выход кото рого соединен с вторым информационным входом компаратора кодов.

2. Устройство по п. 1, отличающееся тем, что блок про- граммирования содержит клавишный ре- гистр, три элемента памяти, генератор тактош 1х импульсов, дешифратор, два счетчика, буферный регистр, два триггера, два элемента И, две группы элементов ИЛИ, два инвертора и груп- пу инверторов, выходы которой соединены с первыми управляющими выходами блока, а входы - с соответствующими разрядами выхода дещифратора, информационный вход которого соеди- нен с информационным выходом первого счетчика, шестым информационным выходом блока и вторым входом первой группы элементов Ш1И, первый вход которой соединен с шестым выходом клавишного регистра и первым входом второй группы элементов ИЛИ, выход которой соединен с пятым информационным выходом блока, второй вход - с информационньи выходом второго счетчика, управляющий вход которого соединен с выходом первого элемента И, а выход переноса - с входом уста0

5

444

5 О 5 0

5 0 5 0 5

114

новки в 1 второго триггера, прямой выход которого соединен с третьим управляющим выходом блока, вход установки в О со счетньм входом втo рого счетчика, пятым управляющим выходом блока, выходом второго элемента И и входом установки в О первого триггера, вход установки в 1 которого соединен с выходом переноса первого счетчика, инверсный выход - с третьим входом второго элемента И, второй вход которого соединен с выходом.генератора такто- вых импульсов, первый вход - с четвертым управляювщм выходом блока, девятым выходом клавишного регистра и первым входом первого элемента И, второй вход которого соединен с входом блока и счетным входом первого счетчика, информационньй вход которого соединен с информационными . входами первого, второго и третьего элементов памяти, первым информащ- онным выходом блока, вторым выходом клавишного регистра и информационньм входом буферного регистра, управляющий вход которого соединен с седьмьм BbixoAONi клавишного регистра, выход - с информационным входом второго счетчика, вход установки в О которого соединен с выходом первого инвертора и входом установки в О первого счетчика, управляющий вход которого соединен с десятым выходом клавишного регистра, восьмой выход которого соединен с входом установки в О буферного регистра, входом первого инвертора и входом второго инвертора, выход которого соединен с входом установки О дещифратора, первый, третий и четвертый выходы клавишного регистра соединены с уп- р авляющими входами соответственно первого, второго и третьего элементов памяти, адресные входы которых соединены с выходом первой группы элементов ИЛИ, а выходы - соответственно с четвертью, третьим и вторым информахдаонным вьскодами блока, второй управляющий выход которого соединен с выходом клавишного регистра.

3. Устройство по п. 1, о т л и- чающееся тем, что блок обработки и регистрации информации содержит пять элементов И, два элемента ИЛИ, инвертор, элемент ИЛИ-НЕ, элемент И-НЕ, две группы элементов

.15

И, две группы триггеров и индикаторную панель, входы которой соединены с прямыми выходами соответствующих триггеров первой и второй групп, входы установки в 1 которых соединены с выходами соответствующих элементов И первой и второй групп, а входы установки в с вторым входом элемента И-НЕ и третьим входом блока, восьмой и седьмой входы кото рого соединены соответственно с пер вым и вторым входами первого элемен та И, выход которого соединен с пер вьв4И входами второго и третьего эле ментов И, выходы котор« 1х соединены соответственно с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, первый и второй входы которых соединены соответ ственно с шестЕ в4 и вторым входами блока, а выходы - с первыми входами

10

25444116

четвертого и пятого элементов И соответственно вторые входы которых соединены с четвертым входом блока, второй выход которого соединен с вы- выходом элемента И-НЕ, первый вход которого соединен с первым выходом блока и выходом элемента ИЛИ-НЕ, первый вход которого соединен с выходом четвертого элемента И и первыми входами элементов И первой группы, вторые входы которых соединены с соответствующими входами первых входов блока и вторюш входами соответствующих элементов И второй груп 5 пы, первые входы которых соединены с вторым входом элемента ЙЛИ-НЕ и выходом пятого элемента И, пятый-вход блока соединен с втарым входом второго элемента И и входом инвертора,

20 выход которого соединен с вторым входом третьего элемента И.

0tfS. 2

. V

фиг. 5

te Фиъ.6

Редактор Л.Пчелинская

Составитель 6.Копылов Техред И.Попович

Заказ 4719/51

Тираж 836Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35 Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Е.Сирохмам

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параметров | 1985 |

|

SU1291930A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство контроля | 1984 |

|

SU1198542A1 |

| Устройство для контроля параметров | 1980 |

|

SU960743A2 |

| Устройство для контроля параметров микросборок | 1986 |

|

SU1328797A1 |

| Устройство для автоматизированного контроля параметров | 1988 |

|

SU1647520A1 |

| Устройство для автоматического контроля и индикации | 1991 |

|

SU1807452A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1987 |

|

RU1612956C |

Изобретение относится к области контрольно-измерительной техники и может быть использовано при построении систем автоматизированного контроля многопараметрических объектов и позволяет повысить быстродействие устройства. Устройство для контроля параметров содержит преобразователи t, входы которых подключены к выходам объекта 3 контроля, управляющие входы - к первым выходам блока 4 программирования, а выходы соединены с входами коммутатора 5, выход которого подключен к первым входам первого и второго блоков 6 и 7 вычитания, выходы которых соединены с первыми входами первого и второго .компараторов 8 и 9, вторые входы которых соединены с выходом третьего источника 10 опорного напряжения , вход которого подключен к с (Л С фиг.)

| 1970 |

|

SU418833A1 | |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля параметров | 1980 |

|

SU960743A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| (ЗА) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ | |||

Авторы

Даты

1986-08-30—Публикация

1985-01-16—Подача