Изобретение относится к контрольно-измерительной и вычислительной технике и может быть использовано при построении систем автоматизированного контроля параметров микросборок.

Целью изобретения является повышение достоверности результатов контроля за счет итерационного метода коррекции погрешности измерения„

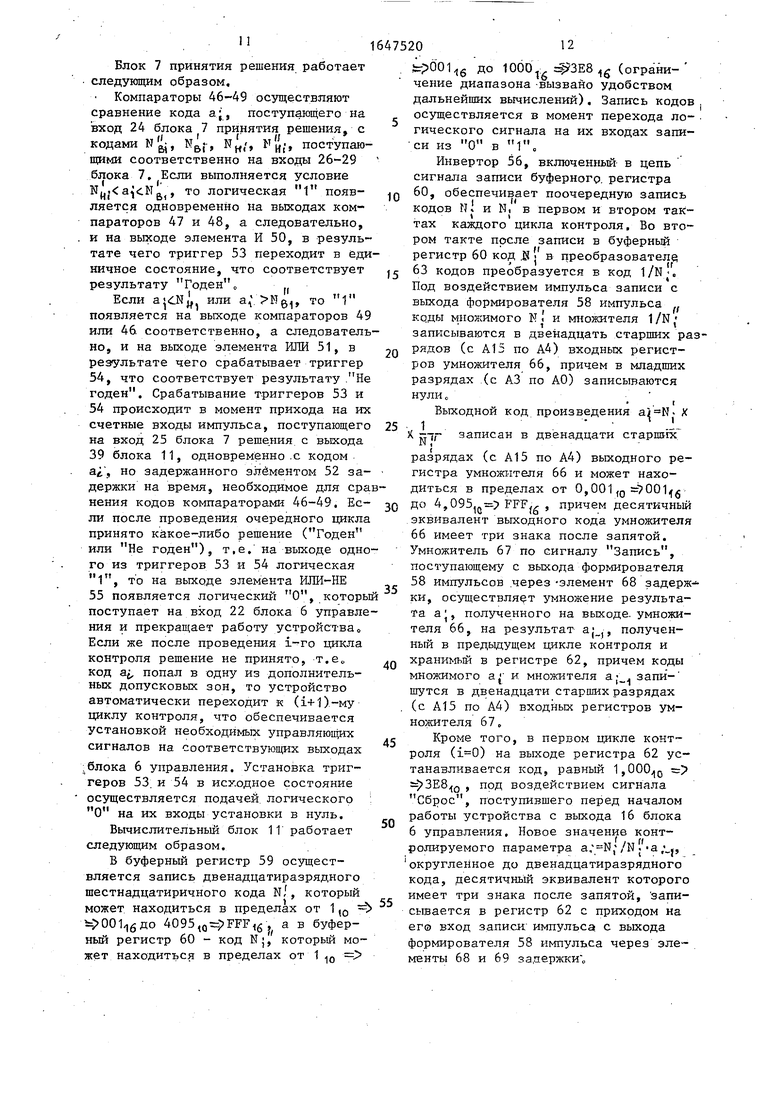

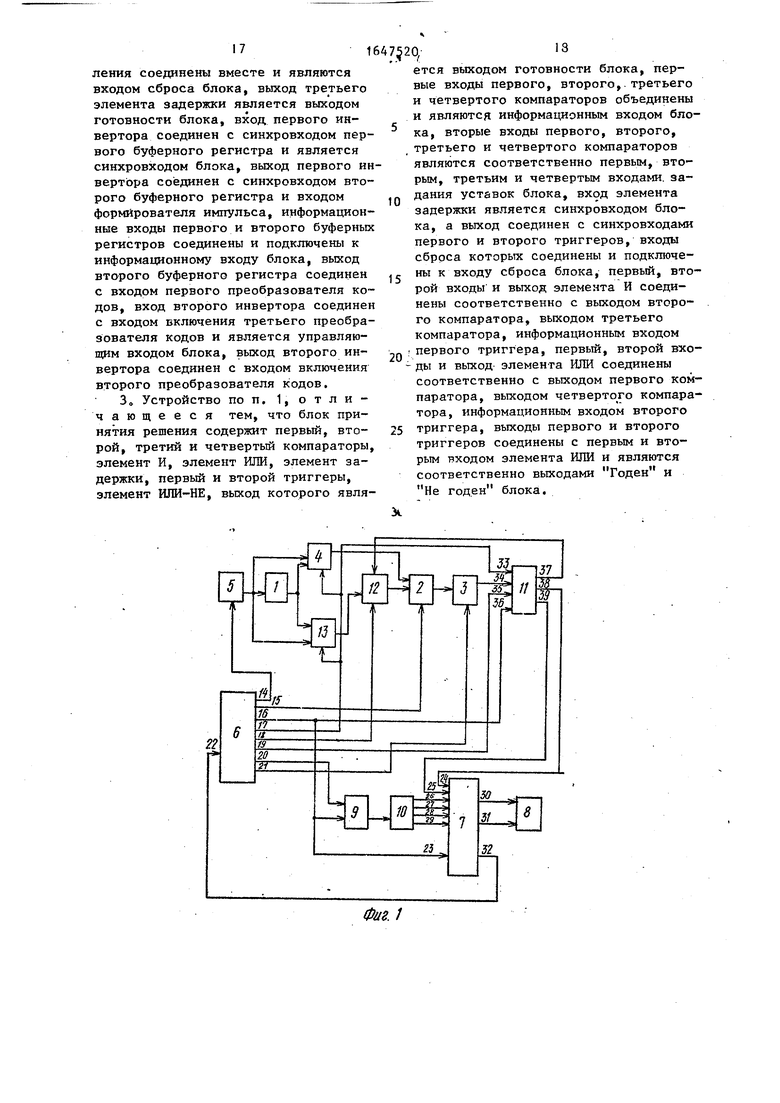

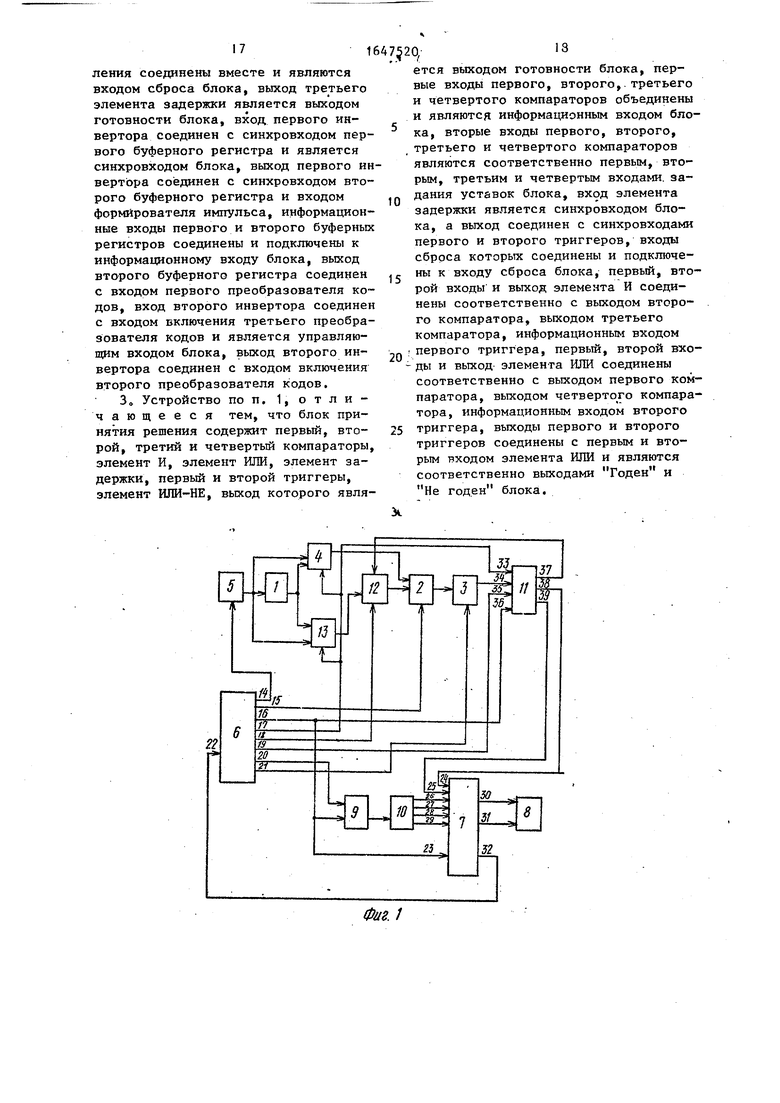

На фиг„ 1 представлена структурная схема устройства для автоматизированного контроля параметров; на фиг. 2 - структурная схема блока управления;- на фиг. 3 - структурная.

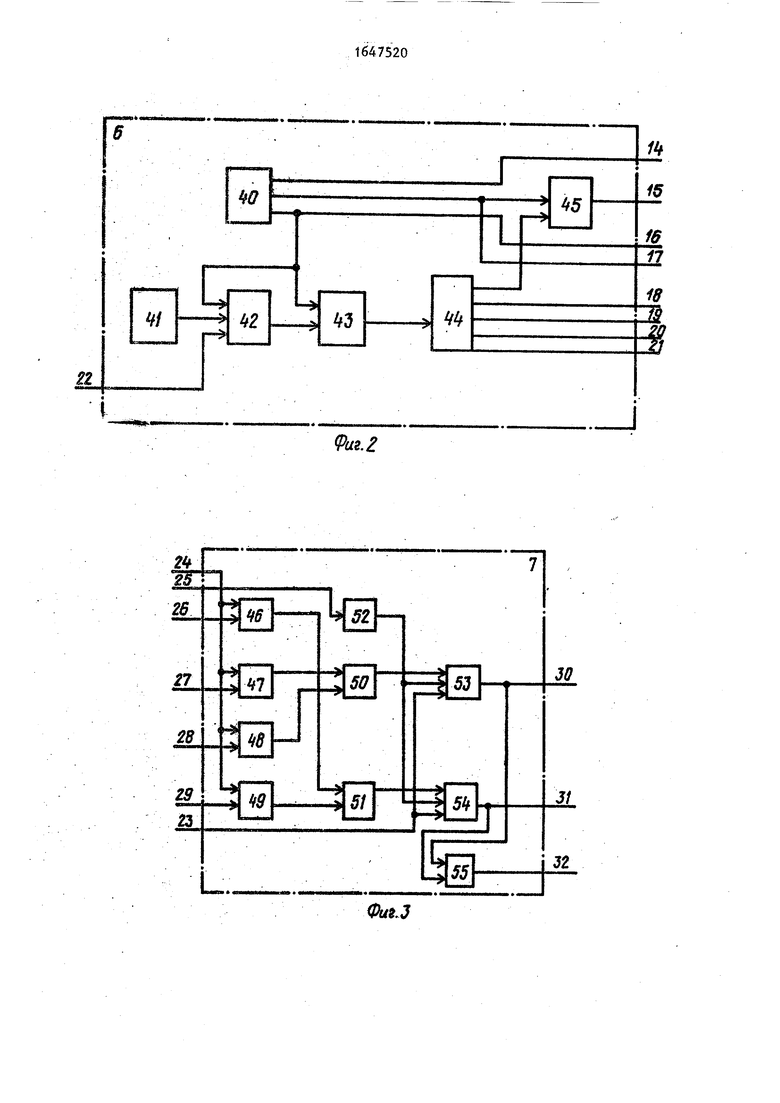

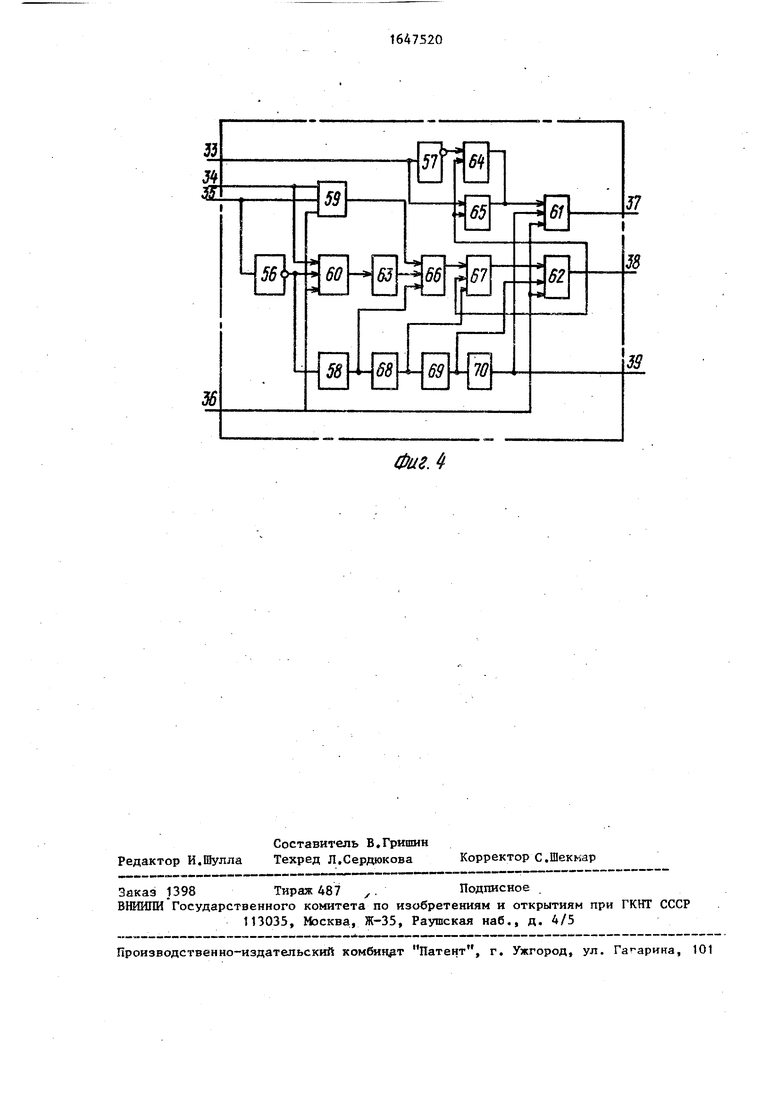

схема блока принятия решения; на фиг, 4 - структурная схема блока обработки результата измерения.

Устройство содержит объект 1 контроля, первый коммутатор 2, аналого- цифровой преобразователь 3, второй коммутатор 4, генератор 5 тестовых сигналов, блок 6 управления, блок 7 принятия . решения, блок 8 индикации, счетчик 9, блок 10 хранения уставок, блок 11 обработки результата измерения, блок 12 деления, третий коммутатор 13.

О

4 1

сл ьо

На фиг„ 1 также показаны выходы 14-21 и вход 22 блока 6 управления, вход 23 сброса, информационный вход 24, синхровход 25, входы 26-29 задания уставок, выходы 30-3-2 блока принятия решения, управляющий вход 33 информационный вход 34, синхровход 35, вход 36 сброса выход 37 коэффициента целения, выход 38 результата, выход 39 готовности блока обработки результата измерения

Блок 6 управления содержит пульт 40 управления, генератор 41 тактовых импульсов, элемент И 42, счетчик 439 узел 44 памяти управляющих сигналов, элемент ИСКЛЮЧАЩЕЕ ИЛИ 45 „

Блок 7 принятия решения (фиг„ 3) содержит компараторы 46-49, элемент И 50,гэлемент ИЛИ 51, элемент 52 задержки, триггер 53 и 54, элемент ИЛЙ-НЕ 55 о

Блок 11 (фиг„ 4) содержит инверторы 56 и 57, формирователь 58 импульса, буферные регистры 59 и 60, регистр 61 коэффициента деления, ре гистр 62 результата, преобразователи 63-65 кодов, умножители 66 и 67, элементы 68-70 задержки

В регистре 61 для реализации единичного состояния на всех выходных разрядах по сигналу Сброс информация снимается с инверсного выхода, а на вход подается информация в инверсном коде, в регистре 62 для уставов- ки кода, соответствующего числу 1, по сигналу Сброс информация соответствующих разрядов снимается с ин- версных выходов, а для исключения искажений передачи последующей информации информационные входы этих разрядов подключаются через инверторы При использовании двенадцатиразрядных АЦП 3 и блока 12 деления все вычисления в блоке 11 производятся в шестнадцатиричном двенадцатиразрядном кодес Таким образом, для реализации кода, соответствующего числу 1, по сигналу Сброс в регистре 62 необходимо инвертировать разряды А9, А8, А7, А6, А5, A3, что соответствует коду (ЗЕ816), десятичный эквивалент которого имеет три знака после запятой.

Преобразователи кодов 63-65 могут быть реализованы, например, на микросхемах 556 РТб, 556 РТ7, причем значение выходного кода N ebt)C преобразователя 63 кодов обратно пропорционально значению входного кода N

9Х

BfcfX / &X где JBX может находить- пределах от 11й(в десятичном ко СЯ 3

де) , что соответствует шестнадцатиричном коде), до , NBb(y соответственно находится в пределах от 1,00040- ЗЕ8|5 до 0, 5001 л. (этот диапазон обусловлен

0 Удобством вычислений).

Преобразователи 64 и 65 кодов обеспечивают формирование управляющего кодаs подаваемого на блок 12 деленияг при реализации итерационно5 го алгоритма для случаев, когда контролируемой - параметр а 1 шш а 1 соответственно. Выходной код твь(Х преобразователя 64 кодов соответствует инверсному двоичному коду произведения входного кор,а N6X (десятичный-эквивалент которого имеет три знака после запятой и равен /10001С) на максимальный управляющий

код N.

(N

макс блока 12 деления,

. ЛТ -- - ВХ 1 АШГ

N1

6WX

где N ex находится в пределах о т С,001,0 Ф0011б до 0,

ЗЕ71б fWr(409V- FFFi6 ля двенадцатиразрядного кода), 1Твыхна-

холится соответственно в пределах от (S до 40911вв 00116(в инверсных кодах). Значение выходного кода NSbjy преобразователя 65 кодов соответствует инверсному двоичному

0

5

«, ,NMQKUK В °ДН°МУ К°ДУ

к av (десятичный эквивалент которого э РЛ

запятой

коду отношькия

(Iff

ьмеет три

знака после .№

и ра- н

р„ ивх/юоо), .

HUV может находиться в пределам

0

5

вен

где К может находиться в пределах от, 1,000,0 J ЗЕ816 до 4,09510 FFFf6 , ВЫУ соответственно в пределах от 409510 - 000,бдо 100010 С1716 (в инверсном коде. -V

В умножителях 66 и 67 в сомножителях используется по 12 разрядов (в остальных разрядах записаны нули). В десятичном эквиваленте выходных Феодов умножителей 66 и 67 условно принимается три младших знака после запятой. Таким образом, результаты умножения состоят из целой и дробной частей, причем, если контролируется величина а .. 1, то десятичный эквивалент результата умножения меньше единицы и может находиться в пределах от 0,001w 5001f6 до 0,999 0 ЗЕ71б, а при десятичный эквивалент результата умножения больше единицы, содержат целую и дробные части и на31647520 .6

ходятся в пределах от 1, ЗЕ8,б должен находиться в пределах от до 4,095,0 FFF,6 .(°0lt6+NP до (ЗЕ8( Учет мак

симально возможной погрешности измерительно-преобразовательного канала позволяет исключить переполнение двенадцатиразрядного кода при реалиПринцип работы заключается в следующем.

Программа контроля параметра а объекта 1 контроля может состоять из одного и более циклов. Причем в каждом отдельном случае число циклов контроля не одинаковое Объект 1 контроля считается кодным, если значение параметра а лежит в пределах нижнего ви и верхнего а„ допусковых значений, т.е. если выполняется условие ац-а-ав° ® противном случае объект 1 контроля считается не годным.

Рассмотрим работу устройства при а 1 а В этом режиме второй коммутатор А обеспечивает подключение выхода генератора 5 тестовых сигналов к первому входу первого коммутатора 2, а третий коммутатор 13 - подключение выхода объекта 1 контроля к входу делимого блока 12 деления. Каждый цикл контроля состоит из двух тактов. В первом такте первого цикла контроля под действием сигнала управления, поступающего с выхода 15 блока 6 управления на управляющий вход первого коммутатора 2, осуществляется подключение выхода объекта

Iконтроля через блок 12 деления

к входу аналого-цифрового преобразователя 3. Причем в первом цикле управляющим кодом с выхода 37 блока

I1устанавливается значение коэффициента деления блока 12 деления, равное| единице. Преобразованный в код N.. аналого-цифровым преобразователем 3 выходной сигнал блока 12 деления запоминается в блоке 11, причем код NO должен находиться в пределах от (00116+Кд) до (FFF46-N&), где N. - код, величина которого учитывает максимально возможную погрешность измерительно-преобразовательного каналао

Во втором такте блок 6 управления вырабатывает управляющий сигнал на первый коммутатор 2 для переключения выхода генератора 5 тестовых сигналов к входу аналого-цифрового преобразователя 3, исключая таким образом объект 1 контроля и блок 12 деления из измерительного канала. Выходной код N0 аналого-цифрового преобразователя 3, соответствующий выходному сигналу S генератора 5 тестовых сигналов, поступает в блок 11„ Код Nfl

зации итерационного алгоритма. Кроме того, коды N и N0 подаваемые на 10 блок 11, при а 1 должны удовлетворять соотношению:

(3E8,6+Nfl)Ј(NX )c(FrF16-Nu),

5 Тестовый сигнал генератора 5 тестовых сигналов выбирается из условия минимальной погрешности квантования аналого-цифрового преобразователя 3„ Это условие выполняется, когда на

20 аналого-цифровой преобразователь 3 в первом и втором тактах преобразования поступают сигналы, соответствую1- щие максимально возможным кодам F (FFF,), N0 (ЗЕ8(б-Рд)„

25 В блоке 11 осуществляется деление кода N на NQ „ Результат a

У --J)- может находиться в пределах от

(1,000%е5 ЗЕ81б) до (4,096 0 ; FFF16),

30 причем десятичный эквива -снт выходного кода ал имеет три знака после зарезуль-блока 7 принятия решения, где сравнивается

35 с кодами , F|,O, N BO, I g0, представ ленными шестнадцатиричными двенадцатиразрядными кодами, десятичный эквивалент которых имеет три знака после запятой, поступающих с блока 10 хра4Q нения уставок соответственно на входы 29, 28, 27 и 26 блока 7 принятия решения.

Если а0 , или а0 N8o, то прини мается решение Не годен, если Мцо

45 Ј бо то принимается решение Годен, причем в обоих случаях погрешность измерительного канала не влияет на достоверность принятого решения Результат контроля индици50 РУется в блоке 8 индикации и контроль прекращается ,

Если выполняется условие Nu0 или NBOЈ aftЈN.0, . результат

.о

пятой. С выхода 38 блока 11 тат а0 поступает на вход 24

измерения aQ находится в непосредст- 55 венной близости от нижней а или

верхней ag границ допуска, то решение о качестве объекта 1 контроля, принятое по соотношению aQ, ак и ал, может быть ошибочным.

В

зации итерационного алгоритма. Кроме того, коды N и N0 подаваемые на блок 11, при а 1 должны удовлетворять соотношению:

(3E8,6+Nfl)Ј(NX )c(FrF16-Nu),

5 Тестовый сигнал генератора 5 тестовых сигналов выбирается из условия минимальной погрешности квантования аналого-цифрового преобразователя 3„ Это условие выполняется, когда на

0 аналого-цифровой преобразователь 3 в первом и втором тактах преобразования поступают сигналы, соответствую1- щие максимально возможным кодам F (FFF,), N0 (ЗЕ8(б-Рд)„

5 В блоке 11 осуществляется деление кода N на NQ „ Результат a

У --J)- может находиться в пределах от

(1,000%е5 ЗЕ81б) до (4,096 0 ; FFF16),

0 причем десятичный эквива -снт выходного кода ал имеет три знака после зарезуль-блока 7 принятия решения, где сравнивается

5 с кодами , F|,O, N BO, I g0, представленными шестнадцатиричными двенадцатиразрядными кодами, десятичный эквивалент которых имеет три знака после запятой, поступающих с блока 10 храQ нения уставок соответственно на входы 29, 28, 27 и 26 блока 7 принятия решения.

Если а0 , или а0 N8o, то принимается решение Не годен, если Мцо

5 Ј бо то принимается решение Годен, причем в обоих случаях погрешность измерительного канала не влияет на достоверность принятого решения Результат контроля индици0 РУется в блоке 8 индикации и контроль прекращается ,

Если выполняется условие Nu0 или NBOЈ aftЈN.0, . результат

.о

пятой. С выхода 38 блока 11 тат а0 поступает на вход 24

измерения aQ находится в непосредст- венной близости от нижней а или

верхней ag границ допуска, то решение о качестве объекта 1 контроля, принятое по соотношению aQ, ак и ал, может быть ошибочным.

В

716475

В данном случае для уменьшения влияния погрешности измерительного канала на достоверность результатов контроля проводится дополнительная серия циклов контроля, в течение которых осуществляется итеративная коррекция погрешности измерительного канала с анализом результата измерения

после каждого цикла„

В каждом из этих циклов (,2,.jc) работа устройства осуществляется так

10

же, как и в первом цикле

(),но

отличие от первого цикла контроля, в каждом i-м цикле, начиная с второго (), коэффициент деления управляемого делителя блока 12 устанавливается равным а;,,, т.е„ результату измерения, полученному, в предыдущем цикле, а для обработки в блок 7 принятия решений поступает код ; х

1 а

N /N/ , где N. и NC - выходные коды аналого-цифрового преобразователя 3 соответственно в первом и втором тактах 1-го цикла. Решение о качестве объекта 1 контроля принимается так же, как и в первом цикле, но в каждом очередном i-м цикле контроля блок 10 хранения уставок формирует новые

. . Т I Т 11 ЧТ . VT I -. -.л.15

20

25

N

ц; NHf NB« , NB|, соответству- 30

коды

ющие границам дополнительных допусковых зон , и ag-.,

V

ностъю результата измерения после 1-го шага итерации„

Причем значение погрешности результата измерения с каждым шагом итерации уменьшается, а следовательно, уменьшается и ширина дополнительных допусковых зон Формирование уставок, необходимых для 1-го цикла контроля, обеспечивается подачей адресного кода с выхода счетчика 9 на вход блока 10 хранения уставок 10. Наращивание выходного кода счетчика 9 на единицу в каждом новом цикле контроля осуществляется под воздействием тактового импульса, поступающего на его счетный вход с выхода 20 блока 6 управления.

Итерация осуществляется до тех пор, пока результат измерения а не

аи+ П и

ft - i к RI И i J 6; I, где QI - определяется погрешв

35

40

45

выйдет за пределы дополнительной допусковой зоны, т„е„ выполняется одно из условий, aj«ЈN4j или а , N в; (принимается решение Не годен), Ni .cacNa (принимается решение Готри знака после зап ходиться в пределах

„ выполняется ,.

55 до (0,99910 ЗЕ71б)

Ч)

ден). .

Сравнение резуль граничных уставок о же, как и при 1,

8

При а . 1 второй коммутатор 4 обеспечивает подключение1 выхода объекта 1 контроля к первому входу первого коммутатора 2, а третий коммутатор 13 - подключение выхода генератора 5 тестовых сигналов к входу делимого блока 12 деления„ Таким образом, к входу делимого блока 12 деления подключается не объект 1 контроля (как для а 1), а генератор 5 тестовых сигналов. Работа устройства осущест

15

20

25

30

вляется так же, как и для а 1, но

учитывая, что при коммутаторы 4 и 13 обеспечивают подключение к своим выходам соответственно выходы объекта 1 контроля и генератора 5 тестовых сигналов (при а 1 наоборот) s то соответственно меняется и очередность коммутации входных сигналов в первом коммутаторе . Это обеспечивается подачей на его управляющий вход инверсного управляющего сигнала с выхода 15 блока 6 управления,, В первом такте на информационный вход блока 11 поступает преобразованный в код NQ аналого-цифровым преобразователем 3 выходной сггнал объекта 1 контроля, который может находиться в пределах от () до (ЗЕ7 NA). Во втором такте на информационный вход блока 11 поступает преобразованный в код N выходной сигнал блока 12 деления, который может находиться в пределах от (001fg + +Нд) до ( -Мд) о

При а-с: 1 коды N влетворять соотношению (001 (NQ/NQ) Ј (ЗЕ716 -%) . тестовый нал генератора 5 тестовых сигналов выбирается из условия минимальной погрешности квантования Это условие выполняется, когда на аналого-цифровой преобразователь 3 в первом и втором тактах преобразования поступают сигналы, соответствующие максимально возможным кодам для заданного режима работы, N0(3E716-N) , 1(ЗЕ8нб-Нд)о

На выходе блока 11 десятичный эквивалент результата деления x

X --,- всегда меньше единицы, имеет

о

три знака после запятой и может находиться в пределах от (0,)

35

a«i 1 коды N и No должны удо1f6 +% сиг40

45

55 до (0,99910 ЗЕ71б)

Сравнение результата а6 с кодами граничных уставок осуществляется так же, как и при 1, при этом десятичный эквивалент кодов граничных уставок также меньше единицы. Кроме того, при а с1 на каждом i-м шаге итерации (,2,..) коэффициент деления управляемого делителя 12 устанавливается равным не а,(, а 1/а-.

Блок 6 контроля работает следующим образом.

До начала контроля при отсутствии JQ сигнала Запуск, что соответствует логическому О на втором выходе пульта АО управления, счетчик 43 сброшен, а элемент И 42 не пропускает импульсы с выхода 41 генератора тактовых импульсов на счетчик 43. Кроме того, по логическому О на выходе 16 блока 6 управления сброшены в нуль счетчик 9, триггеры 53 и 54 блока 7 принятия решения, а также о буферные регистры 59 и 60, установлены выходной код (FFF) регистра 6Т и код (ЗЕ8) регистра 62 блока 11 , До начала контроля выбирается необходимый режим работы устройства (а с 1 25 или ), это обеспечивается установкой в необходимое положение пере- ключателя на пульте 40 управления, в результате чего на его третьем выходе устанавливается соответствующий ло- зо гический уровень (О или 1), С пульта 40 управления задается режим работы генератора 5 тестовых сигналов. Это обеспечивается установкой в необходимое положение клавиш- ,, ных переключателей управления генератором 5 тестового сигнала, в результате чего на первом выходе пульта 40 управления устанавливается

СООТВеТСТВУЮЩИЙ УПраВЛЯЮЩИЙ КОД, В дд

блоке 10 хранения уставок устанавливаются граничные значения контролируемого параметра для каждого шага итерации.

При нажатии клавиши Запуск на пульте 40 управления сигнал логической 1 на его втором выходе разрешает прохождение тактовых импульсов с выхода генератора 41 тактовых импульсов через элемент И 42 на счет- ный вход счетчика 43„ Счетчик 43 формирует адрес ячеек памяти узла 44 памяти управляющих сигналов В результате чего по тактовым импульсам на выходах последнего, а следовательно, и на соответствующих выходах блока 6 управления устанавливается необходимая комбинация управляющих

50

о 5 о ,

д

0

сигналов, которые осуществляют синхронизацию работы устройства.

Кроме того, сигнал Запуск поступает на выход 16 блока 6 управления и переводит в рабочее состояние блок 7 принятия решения, счетчик 9 и блок 11. Сигнал на выходе 14 блока 6 управления управляет работой генератора 5 тестовых сигналов. На выходе 15 устанавливается необходимый логический уровень для управления первым коммутатором 2„ Данный логический уровень формируется на пятом выходе узла 44 памяти управляющих сигналов и через элемент ИСКЛКМАЩЕЕ ИЛИ 45 поступает на выход 15 блока 6 управления, причем в зависимости от режима работы устройства ( или ) логический уровень подается в прямом или инверсном состояниях, это обеспечивается подачей на второй вход элемента ИСКЛЮЧАЩЕЕ ИЛИ 45 сигнала управления режимами с третьего выхода пульта 40 управления, который также поступает через выход 17 блока 6 управления на управляющие входы второго 4 и третьего 13 коммутаторов и блока 11. На выходе 18 Аормируется импульс запуска блока 12 деления, на выходе 21 w импульс запуска аналого- циАрового преобразователя 3„

На выходе 19 формируются импульсы записи выходных кодов аналоге- .. цифрового преобразователя 3 М. и N1 в блок 11 соответственно в первом и во втором тактах преобразования.Пе- рисд следования тактовых импульсов превышает суммарное время срабатывания блока 11 и блока 7 принятия реше/ /9

ния. Если после записи кодов N, и N в блок 11 за следующий период тактовых импульсов в блоке 7 принятия решения не принято решение о годности объекта контроля и не произойдет остановка работы устройства, то на выходе 20 блока 6 управления формируется импульс для наращивания выходного кода счетчика 9, и начинается новый цикл контроля. Остановка работы устройства осуществляется подачей логического О с выхода 32 блока 7 принятия решения на вход 22 блока 6 управления, закрывающего по первому входу элемент И 42„ Установка устройства в исходное состояние осуществляется установкой в исходное состояние клавиши Запуск пульта 40 управления.

Блок 7 принятия решения работает следующим образом.

Компараторы 46-49 осуществляют сравнение кода aj, поступающего на вход 24 блока 7 принятия решения, с кодами N , NB,-, NH(, тц( поступающими соответственно на входы 26-29 блока 7. Если выполняется условие ), то логическая 1 появ- ляется одновременно на выходах компараторов 47 и 48, а следовательно, и на выходе элемента И 50, в результате чего триггер 53 переходит в единичное состояние, что соответствует результату Годен

Если или a, Ng1, то 1 появляется на выходе компараторов 49 или 46 соответственно, а следовательно, и на выходе элемента ИЛИ 51, в результате чего срабатывает триггер 54, что соответствует результату Не годен. Срабатывание триггеров 53 и 54 происходит в момент прихода на их счетные входы импульса, поступающего на вход 25 блока 7 решения с выхода 39 блока 11, одновременно с кодом в.1, но задержанного элементом 52 задержки на время, необходимое для сранения кодов компараторами 46-49. Если после проведения очередного цикла принято какое-либо решение (Годен или Не годен), т.е. на выходе одного из триггеров 53 и 54 логическая

. то на выходе элемента ИЛИ-НЕ

появляется логический О1

„ 35 который

30

0

5

S 0011g до 10001 ; jJ3E8 1б (ограни- чение диапазона вызвано удобством дальнейших вычислений). Запись кодов осуществляется в момент перехода логического сигнала на их входах записи из О в 1.

Инвертор 56, включенный в цепь сигнала записи буферного регистра 60, обеспечивает поочередную запись кодов N. и N; в первом и втором тактах каждого цикла контроля. Во втором такте после записи в буферный регистр 60 код В . в преобразователе 5 63 кодов преобразуется в код 1/N- Под воздействием импульса записи с выхода формирователя 58 импульса „ коды множимого F и множителя 1 /N, записываются в двенадцать старших разрядов (с А15 по А4) входных регистров умножителя 66, причем в младших разрядах (с A3 по АО) записываются нули „ t

Выходной код произведения a)N- X

записан в двенадцати старших

разрядах (с А15 по А4) выходного регистра умножителя 66 и может находиться в пределах от 0,001,0 7001 0 До 4,095j FFFjg причем десятичный эквивалент выходного кода умножителя 66 имеет гри знака после запятой. Умножитель 67 по сигналу Запись, поступающему с выхода формирователя 58 импульсов через -элемент 68 задерж-

0

5 , 1

KN7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параметров | 1985 |

|

SU1278894A1 |

| Устройство контроля параметров микросборок | 1984 |

|

SU1246058A1 |

| Устройство для контроля температуры | 1988 |

|

SU1515176A1 |

| Устройство для контроля параметров | 1985 |

|

SU1277138A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ | 1996 |

|

RU2106679C1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство для диагностики неисправностей технических объектов | 1988 |

|

SU1536357A1 |

| Устройство автоматического контроля параметров | 1983 |

|

SU1201850A1 |

| Способ диагностики отказов динамических объектов и устройство для его осуществления | 1990 |

|

SU1718190A1 |

| Устройство для вычисления спектра сигналов | 1989 |

|

SU1667102A1 |

Изобретение относится к контрольно-измерительной и вычислительной технике и может быть использовано при1 построении систем автоматизированного контроля параметров аналоговых объектов. Цель изобретения - повышение достоверности результатов контроля за счет применения итерационного метода коррекции погрешности измерения, вносимой измерительным трактом. Устройство содержит объект контроля, три коммутатора, аналого- цифровой преобразователь, генератор тестовых сигналов, блок управления, блок принятия решения, блок индикации, счетчик, блок хранения уставок, блок деления, блок обработки результата измерения. Устройство осуществляет итерационную коррекцию погрешности контрольно-измерительного канала с анализом значения контролируемого параметра после каждого шага итерации, исключая тем самым влияние погрешности на достоверность результатов контроля. 2 з.п. ф-лы, 4 ил. (Л

поступает на вход 22 блока 6 управлния и прекращает работу устройства„ Если же после проведения 1-го цикла контроля решение не принято, т.е„ код aj, попал в одну из дополнительных допусковых зон, то устройство автоматически переходит к (1+1)-му циклу контроля, что обеспечивается установкой необходимых управляющих сигналов на соответствующих выходах

„блока 6 управления. Установка триггеров 53 и 54 в исходное состояние осуществляется подачей логического О на их входы установки в нуль.

Вычислительный блок 11 работает следующим образом.

В буферный регистр 59 осуществляется запись двенадцатиразрядного шестнадцатиричного кода N/, который может находиться в пределах от 1,0 ь 0011бдо 4095,0 - FFF16 а в буферный регистр 60 - код NJ, который может находиться в пределах от 1 10

та а , полученного на выходе умножителя 66, на результат а- , полученный в предыдущем цикле контроля и хранимый в регистре 62, причем коды

множимого а.1 и множителя

запи5

0

шутся в двенадцати старших разрядах (с А15 по А4) входных регистров умножителя 67«,

Кроме того, в первом цикле контроля () на выходе регистра 62 устанавливается код, равный 1,000j,0 ь ЗЕ810 , под воздействием сигнала Сброс, поступившего перед началом работы устройства с выхода 16 блока 6 управления. Новое значение контролируемого параметра a, j-a.Vj, 1 округленное до двенадцатиразрядного кода, десятичный эквивалент которого имеет три знака после запятой, записывается в регистр 62 с приходом на ег® вход записи импульса с выхода формирователя 58 импульса через элементы 68 и 69 яапержки 0

13

Таким образом, двенадцатиразрядный код контролируемого параметра аЈ устанавливается на выходе 38 блока 11. Кроме того, этот код поступает на первый информационный вход умножителя 67, а также на информационные входы преобразователей 64 и 65 кодбВо В зависимости от величины контролируемого параметра а 1 или устанавливается логический сигнал на входе 33 блока 11, который подключен к входам Выбор микросхем преобразователя 65 кодов прямо и преобразователя 64 кодов через инвертор 57, обеспечивая работу одного из них в зависимости от режима работы а 2 1 или a d 1,

При а Ј. 1 выходной код преобразователя 64 кодов соответствует а-, а при выходной код преобразователя 65 кодов - 1/а „ Таким образом, значение контролируемого параметра а , преобразованное в код коэффициента деления, поступающий на вход делителя блока 12 по импульсу записи, с выхода элемента 69 задержки через элемент 70 задержки, записывает- x.k(i+f)+i t+ ;-:; 2Јннр 4- а;- а пт

И

г «- X да

Я U

-згоир-

хс - тестовый сигнал, формируемый генератором 5 тестовых сигналов; k,u, У - коэффициент преобразования,

аддитивная и мультипликатив- нал погрешности аналого-цифрового преобразователя 3„ Итерация продолжается до тех пор, пока код а не выйдет за пределы доt

полнительных допусковых зон, т.е„

если выполнено одно из условий aj i N (,, или а{ N Q( (принимается решение Не годен), . (принимается решение Годен)„ Причем в обоих случаях влияние погрешности аналого-цифрового преобразователя . 3 на результат контроля исключается,1 в результате чего повышается его достоверность

647520 4

ся в буферный регистр 61 и поступает на выход 37 блока 11 для установки коэффициента деления на входе делителя блока 12 в следующем цикле контроля, причем в первом цикле контроля () на выходе буферного регистра 61 под воздействием сигнала Сброс в код FFF, поступившего перед началом работы устройства с выхода 16 блока 6 управления, устанавливается код, соответствующий коэффициенту деления на входе делителя блока 12, равный единице. Управляющий импульс с выхода элемента 70 задержки через выход 39 блока 11 поступает на вход 25 блока 7 принятия решения для синхронизации последнего.

10

15

Устройство осуществляет итеративную коррекцию погрешности контрольно-измерительного канала, тем самым исключая ее влияние на достоверность результатов контроля. После 1-го шага итерации код а, эквивалентный контролируемому параметру а, с учетом погрешности аналого-цифрового преобразователя 3 равен:

И

а 1,

Максимально возможное число шагов итерации п определяет тем шагом итерации при котором погрешность результата измерения становится меньше дискретности аналого-цифрового преобразователя 3.

Ширина дополнительных зон a -Q } и Јал-й ; а„+ 0 7выбирается исходя из максимального значения погрешности Of результата измерения а| на каждом шаге итерации„ С каждым шагом итерации значение погрешности уменьшается, а следовательно, уменьшается и ширина дополнительных допусковых зон (стремится к нулю), что увеличивает с каждым шагом вероятность выхода за ее предепы результата измерения а, а значит и вероятность принятия достоверного решения о качестве объекта 1 контроля

Формула изобретения

соответственно с первым информационным входом первого коммутатора и вторым выходом блока управления, третий выход которого соединен с управляющим входом первого коммутатора, выход

которого соединен с информационным входом аналого-цифрового преобразо

вателя, управляющий вход которого соединен с четвертым выходом блока управления, пятый выход которого соединен с входом сброса блока принятия решения, первый, второй и третий вы25

2„ Устройство по п, 1, о т л и- чающееся тем, что блок .обработки результата измерения содержит первый и второй инверторы, первый и второй входные буферные регистры, регистр результата, регистр коэффициента деления, первый, второй и третий элементы задержки, первый и второй умножители, первый, второй,

ходы которого соединены соответствен- 30 третий преобразователи кодов и форно с первым и вторым входами блока индикации и входом блока управления, второй информационный вход второго коммутатора является входом устройства, служащим для подключения к вы- 35 ВЫХ°Д которого соединены соответст- ходу объекта контроля, отличающееся тем, что, с целью повышения достоверности результатов контроля за счет итерационного метода коррекции погрешности измерения, в устройство введены третий коммутатор, блок деления, блок обработки результата измерения, счетчик и блок хранения уставок, вход и первый, второй, третий и четвертый выходы которого соединены соответственно с выходом счетчика и первым, вторым, третьим и четвертым входами задания уставок блока принятия решений, информационвенно с выходом первого преобразователя кодов, выходом первого входного буферного регистра и первым вхо дом второго умножителя, второй вход

40 которого соединен с выходом первого и входом второго элементов задержки, третий вход - с выходом регистра результата и информационными входами второго и третьего преобразователей

45 кодов и является выходом результата блока, выход второго умножителя соединен с информационным входом регист ра результата, синхровход которого соединен выходом второго и входом

ный вход и вход запуска которого сое- 50 третьего элемента задержки, выход кодинен соответственно с выходом результата и выходом готовности блока обработки результата измерения, выход задания коэффициента деления которого соединен с входом делителя блока деления, выход которого соединен с вторым информационным входом первого коммутатора, первый и второй информационные входы и выход третье. 5

0

5

го коммутатора соединены соответственно с входом устройства, выходом генератора тестовых сигналов и с входом делимого блока деления, пятый выход блока управления соединен с входами сброса счетчика и блока обработки результата измерения, шестой, седьмой и восьмой выходы блока управления соединены с входом запуска блока деления, входом запуска блока обработки результата измерения и счетным входом счетчика соответственно, причем управляющие входы третьего коммутатора и блока обработки результата измерения соединены с вторым выходом блока, а информационный вход блока обработки результата измерения подключен к выходу аналого-циф- рового преобразователя

2„ Устройство по п, 1, о т л и- чающееся тем, что блок .обработки результата измерения содержит первый и второй инверторы, первый и второй входные буферные регистры, регистр результата, регистр коэффициента деления, первый, второй и третий элементы задержки, первый и второй умножители, первый, второй,

мирователь импульса, выход которого соединен с входом первого элемента задержки и первым входом первого умножителя, второй, третий входы и

ВЫХ°Д которого соединены соответст-

венно с выходом первого преобразователя кодов, выходом первого входного буферного регистра и первым входом второго умножителя, второй вход

которого соединен с выходом первого и входом второго элементов задержки, третий вход - с выходом регистра результата и информационными входами второго и третьего преобразователей

кодов и является выходом результата блока, выход второго умножителя соединен с информационным входом регистра результата, синхровход которого соединен выходом второго и входом

торого соединен с синхровходом регистра коэффициента деления, информационный вход которого соединен с выходами второго и третьего преобра- зователей кодов, а выход является выходом коэффициента деления блока, входы сброса первого и второго входных буферных регистров, регистра результата и регистра коэффициента де-

17

ления соединены вместе и являются входом сброса блока, выход третьего элемента задержки является выходом готовности блока, вход первого инвертора соединен с синхровходом первого буферного регистра и является синхровходом блока, выход первого инвертора соединен с синхровходом второго буферного регистра и входом формирователя импульса, информационные входы первого и второго буферных регистров соединены и подключены к информационному входу блока, выход второго буферного регистра соединен с входом первого преобразователя кодов, вход второго инвертора соединен с входом включения третьего преобразователя кодов и является управляющим входом блока, выход второго инвертора соединен с входом включения второго преобразователя кодов.

3, Устройство по п. 1, отличающееся тем, что блок принятия решения содержит первый, второй, третий и четвертый компараторы, элемент И, элемент ИЛИ, элемент задержки, первый и второй триггеры, элемент ИЛИ-НЕ, выход которого явля16

10

7$20,13

ется выходом готовности блока, первые входы первого, второго, третьего и четвертого компараторов объединены и являются информационным входом блока, вторые входы первого, второго, третьего и четвертого компараторов являются соответственно первым, вторым, третьим и четвертым входами, задания уставок блока, вход элемента задержки является синхровходом блока, а выход соединен с синхровходами первого и второго триггеров, входы сброса которых соединены и подключены к входу сброса блока, первый, второй входы и выход элемента И соединены соответственно с выходом второго компаратора, выходом третьего компаратора, информационным входом . первого триггера, первый, второй вхо- - ды и выход элемента ИЛИ соединены соответственно с выходом первого компаратора, выходом четвертого компаратора, информационным входом второго триггера, выходы первого и второго триггеров соединены с первым и вторым входом элемента ИЛИ и являются соответственно выходами Годен и

15

20

25

Не годен блока.

L..

ss

t

0uiJ

Фиг Л

| Иапенко Н.П | |||

| Измерительные информационные системы | |||

| - М., Энерго- атомиэдат, 1985, с | |||

| Способ модулирования для радиотелефона | 1921 |

|

SU251A1 |

| Устройство для контроля параметров | 1975 |

|

SU607190A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-05-07—Публикация

1988-12-08—Подача