11

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении диагностируемых устройств обработки цифровой информации.

Цель изобретения - расширение функциональных возможностей за счет реализации всех логических функций от двух переменных.

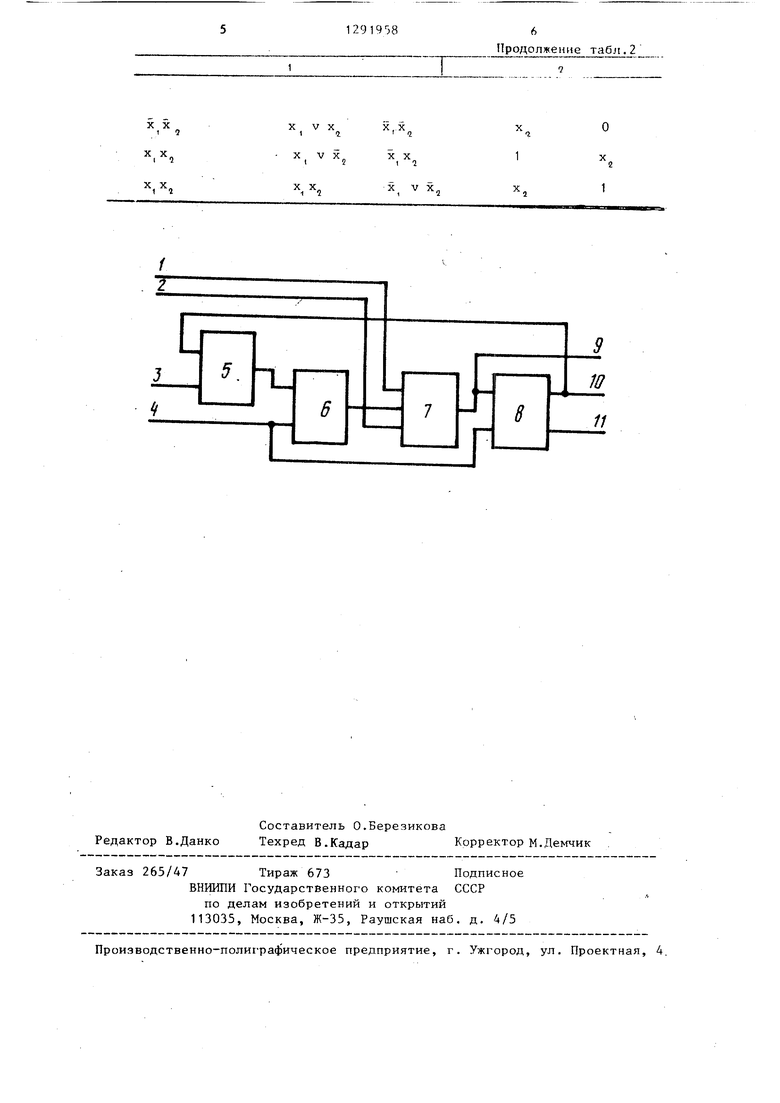

На чертеже представлена функцио- нальная схема многофункционального модуля.

Многофункциональный модуль содержит входы 1-4, элемент И-НЕ 5, элементы РАВНОЗНАЧНОСТЬ 6 - 8,выходы 9 -11.

Многофункциональный модуль имеет три режима функционирования.

В первом режиме, если на первый вход 1 подать сигнал логического нуля (и, 0), а на третий вход 3 - сигнал, равный единице (U, 1), то многофункциональный модуль реализует функции D-триггера, причем второй вход 2 (х ) является входом синхронизации, четвертый вход 4 (иj) - информационным входом,а инверсный выход третьего элемента РАВНОЗНАЧНОСТЬ 8 - выходом триггера 11 Пусть f - функция, реализуемая на выходе элемента И-НЕ 5; fj - функция, реализуемая

на выходе первого элемента РАВНОЗНАЧНОСТЬ 6 f - функция, реализуемая

на выходе второго элемента РАВНОЗНАЧНОСТЬ

f - функция, реализуемая

на прямом выходе третего элемента РАВНОЗНАЧНОСТЬ 8;

F - функция, реализуемая на инверсном выходе третьего элемента РАВНОЗНАЧНОСТЬ 8. Тогда

V f Д ; f и. f,x. V и, f X.

F fjU, f F;

(1) (2) 50

- J -1 1 1 2 t

f, f,U3 V f,U3; (4) f, f7U, .(5)

Подставляя (2-5) в (1) получим огическое выражение 55

. F ((( Uj) ITj V F U,U,) U,x V (U, FJJ V Uj (F V Uj.)) U, X,) Uj V (((F V U,) U у F U-jU,) U, X, v (U, F Ua V Uj(F V U,)) U, x,) Uj.

5

0

9

5

0

0

0

5

58;

Тлк как li, 0, Uj 1, TO функция F на выходе 11 имеет вил F F D.x v V F U, V H устройстве выпо/тняет функции D-триггера.

Во втором ре жиме - режиме контроля работоспособности на первый вход

1подается сигнал Константа 1 при значении сигнала на третьем входе 3 U,j 1 . В этом случае, при наличии на входе 2 логической единицы устройство генерирует импульсы типа меандр.

Наличие любой неисправности,ведущей к появлению логических ошибок (типа 1, О) любого элемента схемы приведет к срыву генерации. Метод контроля работоспособности проверкой генерации позволяет осуществить контроль за один такт изменением сигнала на первом входе 1 с константы О на константу 1 с одновременной подачей по второму входу

2логической единицы.

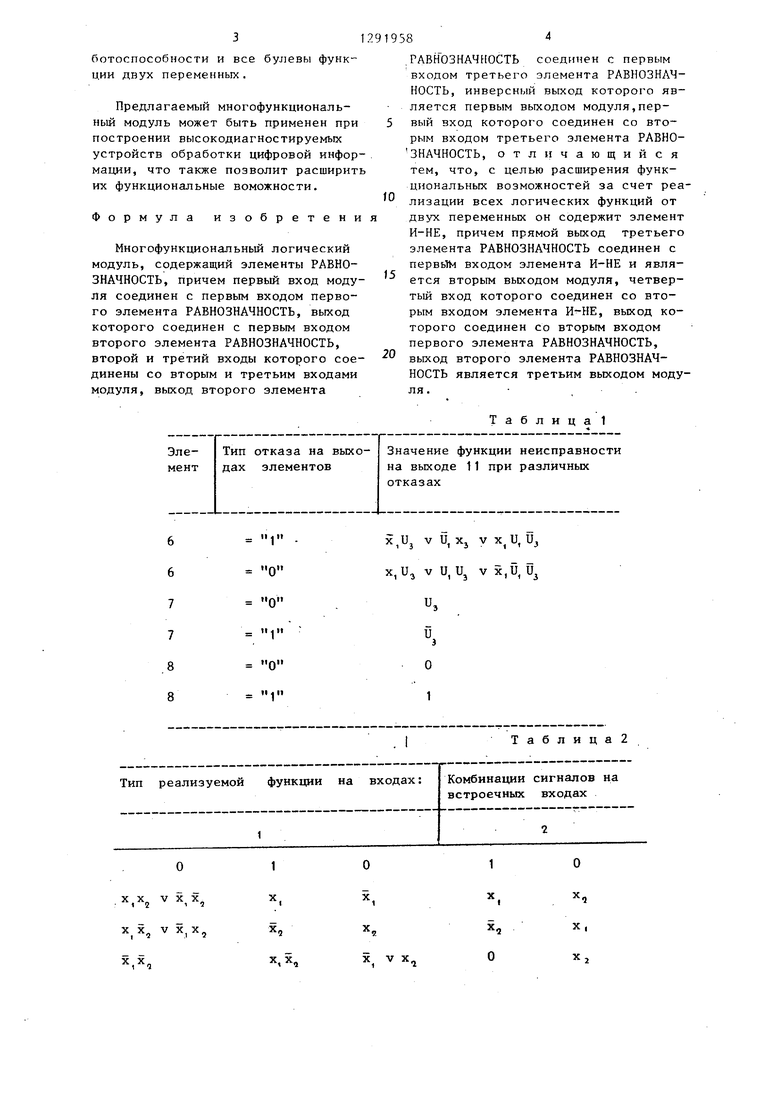

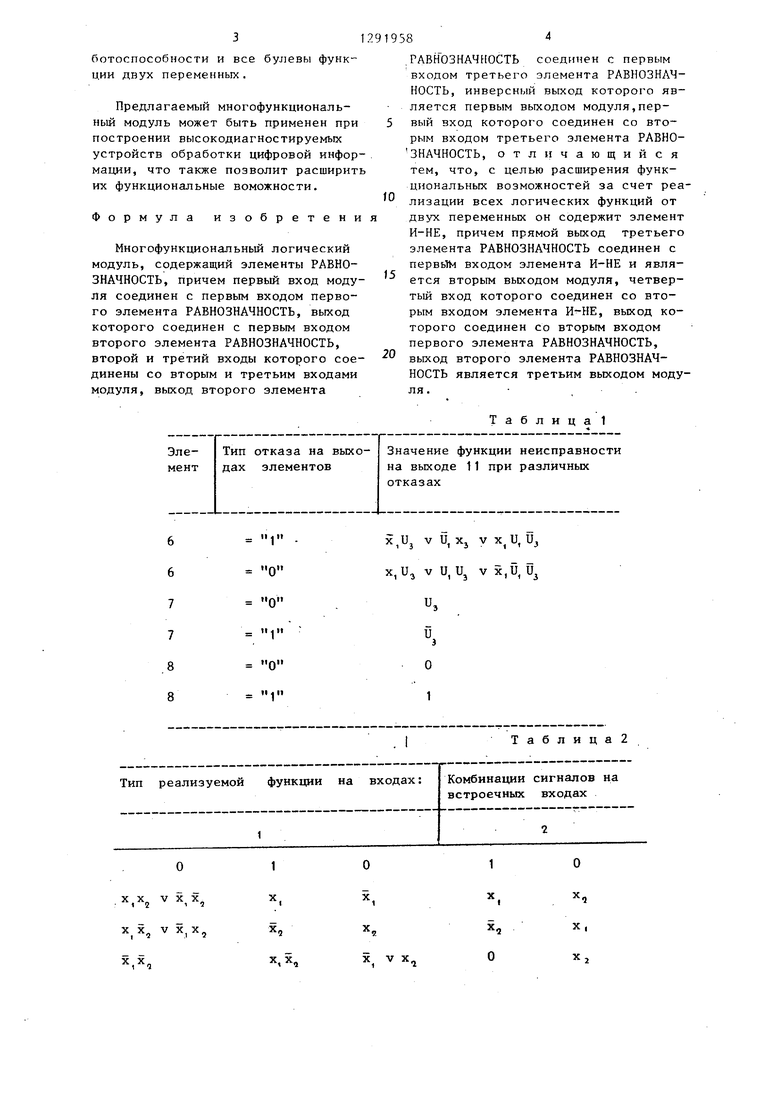

Появление ошибок на выходах элементов схемы устройства приводит к появлению-функций неисправности, которые приведены в табл. 1. I

Таким образом, предлагаемое устройство обладает простой системой контроля и полностью диагностируется с точностью до типа неисправности любого элемента устройства.

В третьем режиме, если на третий вход 3 подать сигнал, равный нулю и 2 О, устройство реализует все булевы функции двух переменных в зависимости от сигналов управления U ,, Uj на первом и четвертом входах 1 и 4. На входы 1 и 4 в соответствии с алгоритмом настройки (табл. 2) подается набор управляющих сигналов, на вход 2 - входная переменная х . Причем алфавит настроечных сигналов будет {о, 1, X,, X а, Xj). Минималь-. мое количество векторов настроек равно семи. При этом в соответствии с табл. 2 с выходов 9-11 снимаются следующие логические зависимости, представленные в табл. 2.

Таким образом, в данном режиме при соответствующих управляющих сиг-. .налах на входах 1 и 4,многофункциональный модуль реализует все булевы функции двух переменных.

Следовательно, многофункциональный модуль реализует функции D- триггера с автономной проверкой ра31

ботоспособности и все булевы функции двух переменных.

Предлагаемый многофункциональный модуль может быть применен при построении высокодиагностируемых устройств обработки цифровой информации, что также позволит расширить их функциональные воможности.

Формула изобретени

Многофункциональный логический модуль, содержащий элементы РАВНОЗНАЧНОСТЬ, причем первый вход модуля соединен с первым входом первого элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ, второй и третий входы которого соединены со вторым и третьим входами модуля, выход второго элемента

Элемент

Тип отказа на выходах элементов

11 J II

II II

II 4 II

Х,Х V Х,Х,

, V Х,Х,

х,х.

10

919584

РАВН ОЗНАЧНОСТЬ соединен с первым входом третьего элемента РАВНОЗНАЧНОСТЬ, инверсный выход которого является первым выходом модуля,пер- 5 вый вход которого соединен со вторым входом третьего элемента РАВНО- ЗНАЧНОСТЬ, отличающийся тем, что, с целью расширения функциональных возможностей за счет реализации всех логических функций от двух переменных он содержит элемент И-НЕ, причем прямой выход третьего элемента РАВНОЗНАЧНОСТЬ соединен с первьТЫ входом элемента И-НЕ и является вторым выходом модуля, четвертый вход которого соединен со вторым входом элемента , выход которого соединен со вторым входом первого элемента РАВНОЗНАЧНОСТЬ, выход второго элемента РАВНОЗНАЧНОСТЬ является третьим вькодом модуля. , .

Таблица 1

15

20

Значение функции неисправности на выходе 11 при различных отказах

V и, Xj V х,и, и V и, и, V x,U, и,

и,

з О

1

Таблица2

V Х

1

X, X,

X X

1

X V X

1 1

X X

I 9

X V X

1 5

1

X Х„

1 1

Редактор В.Данко

Составитель О.Березикова

Техред В.КадарКорректор M.

Заказ 265/47 Тираж 673 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. д. 4/5

Производственно-поли1 ра(|)ическое предприятие, г. Ужгород, ул. Проектная, 4.

Продолжение табл. 2

7

г.

X X

I 7

X V Х„

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический элемент | 1985 |

|

SU1251066A1 |

| Универсальный логический модуль | 1986 |

|

SU1319019A1 |

| Многофункциональный логический модуль двух переменных с самоконтролем | 1984 |

|

SU1275444A1 |

| Тестопригодное логическое устройство | 1986 |

|

SU1451695A1 |

| Универсальный логический модуль | 1984 |

|

SU1234825A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1259243A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1661752A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1320808A1 |

| Универсальный логический модуль | 1983 |

|

SU1148024A1 |

| Универсальный логический модуль | 1987 |

|

SU1536370A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть реализовано при построении высокодиагностируемых устройств обработки цифровой информации с широкими функциональными во зможностями. Целью изобретения является расширение функциональных возможностей D-триггера с автономной проверкой работоспособности за счет реализации всех булевых функций двух переменных. Многофункциональный логический модуль содержит четыре входа, элемент И-НЕ, три элемента РАВНОЗНАЧНОСТЬ,три выхода. Модуль функционирует в трех режимах. При определенном виде постройки модуль реализует либо функции D-триггера, либо все функции двух переменных, либо осуществляет автономный контроль. 1 ил., 2 табл. с ел N9 ;О QD сл 00

| Универсальная логическая ячейка | 1984 |

|

SU1196845A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| @ -Триггер с автономной проверкой работоспособности | 1981 |

|

SU997253A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1987-02-23—Публикация

1985-10-10—Подача