&

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах, функционирующих в реальном масштабе времени.

Целью изобретения является расширение области применения за счет вы полнения нелинейной фильтрации комплексных сигналов.

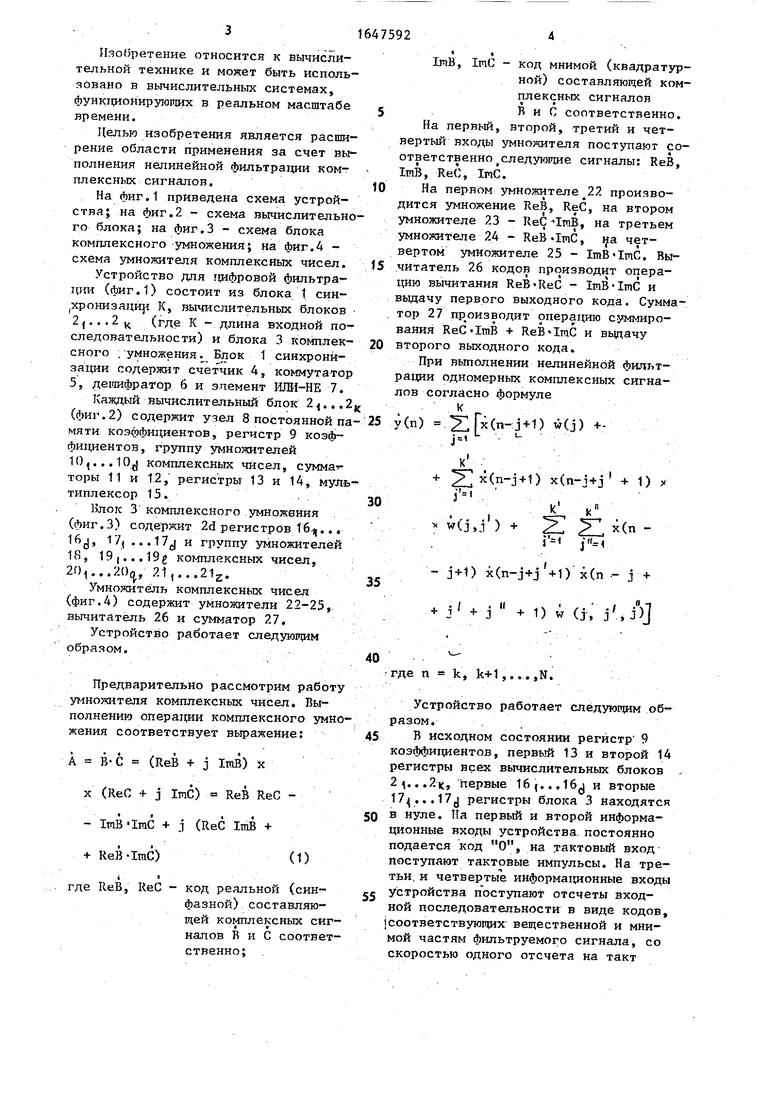

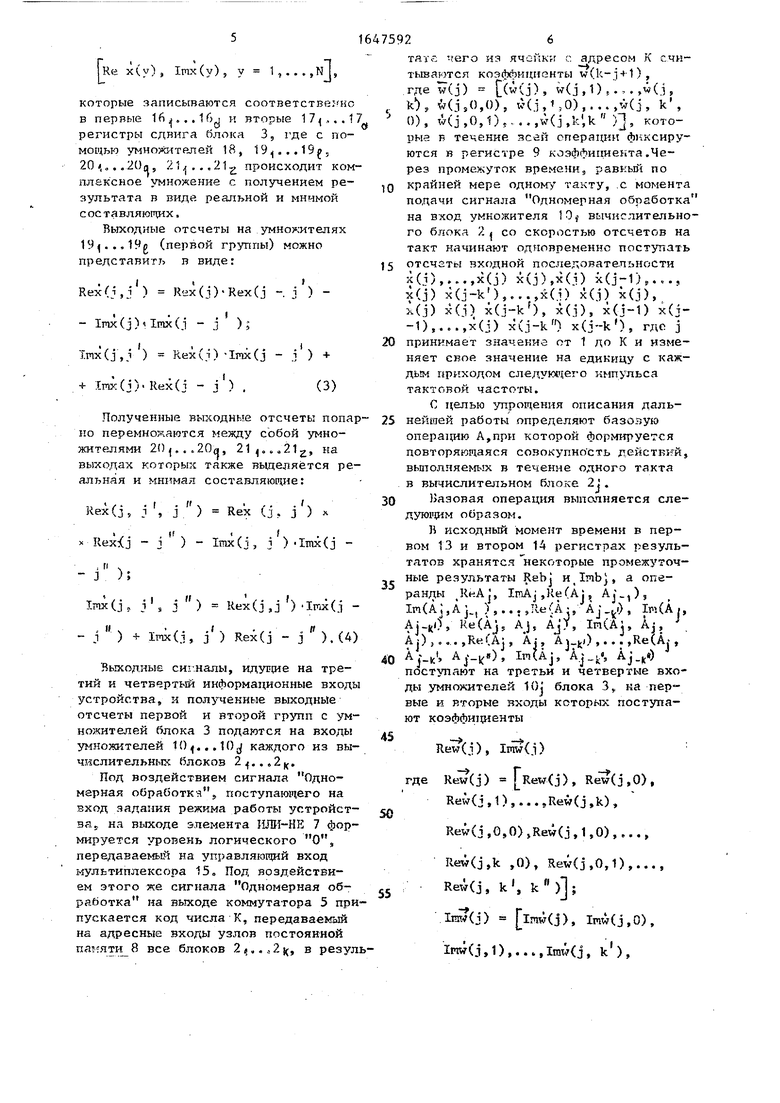

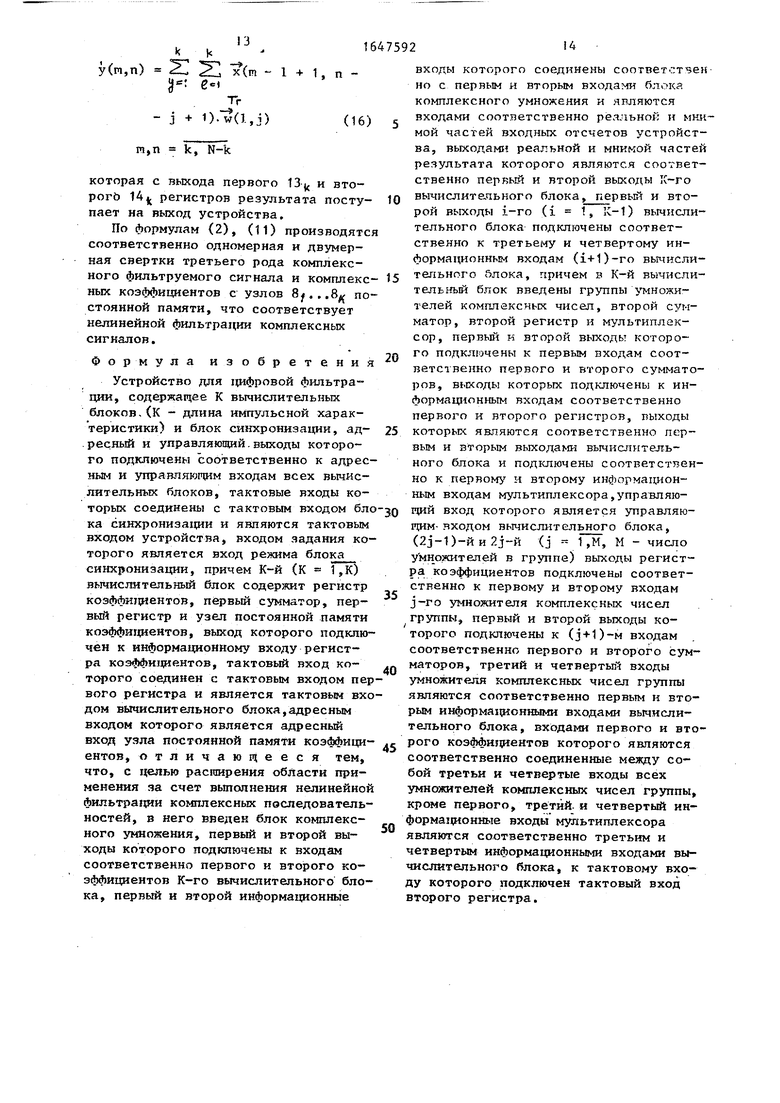

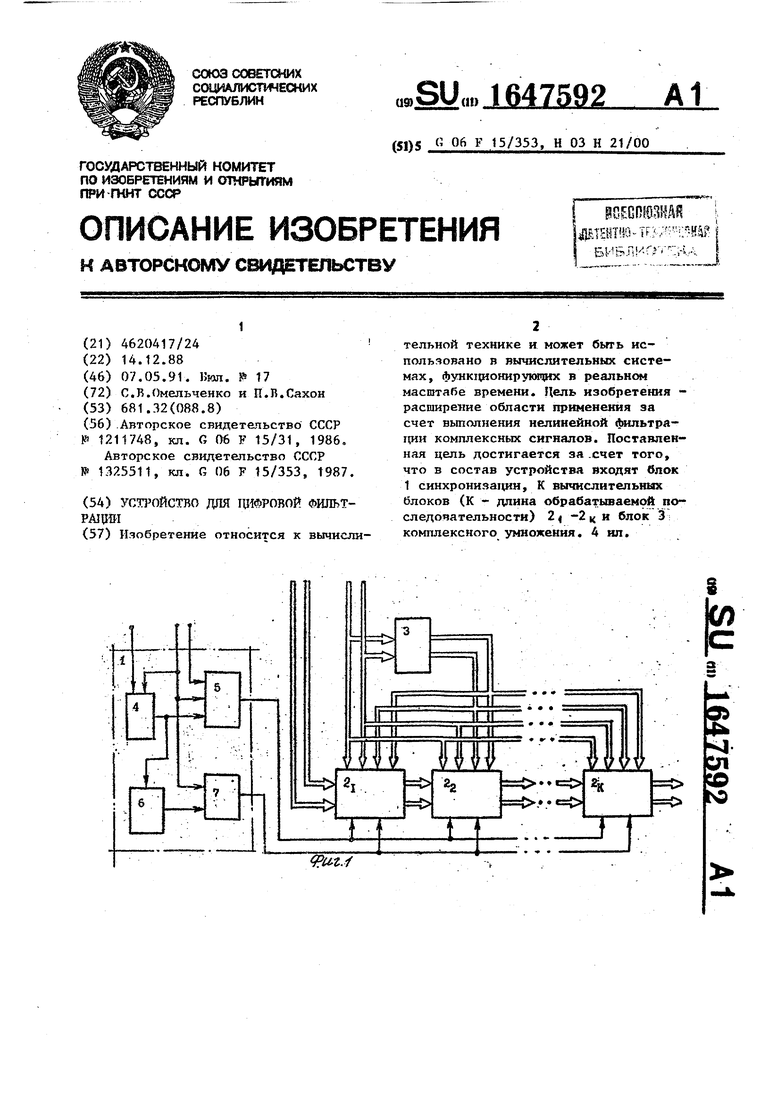

На Лиг.1 приведена схема устройства; на фиг.2 - схема вычислительного блока; на фиг.З - схема блока комплексного умножения; на фиг.А - схема умножителя комплексных чисел.

Устройство для цифровой фильтрации (фиг.1) состоит из блока 1 син- (хронизации К, вычислительных блоков 2|...2 к (где К - длина входной последовательности) и блока 3 комплексного . умножения. Блок 1 синхронизации содержит счетчик 4, коммутатор 5, дешифратор 6 и эпемент ШШ-НЕ 7.

Каждый вычислительный блок 2j...2K

ImB, InC - код мнимой ( ной) составл плексных сигн

5R и С соответ

На первый, второй, третий вертый входы умножителя пос ответственно gследующие сигна InB, ReC, ImC.

10 На первом умножителе 22 п дится умножение ReB, ReC, н умножителе 23 - ReC ImB, на умножителе 24 - ReB«ImC, н вертом умножителе 25 - ImB 15 читатель 26 кодов производит цию вычитания - InB выдачу первого выходного код тор 27 производит операцию с вания ReC«ImB + ReB IraC и вы 20 второго выходного кода.

При выполнении нелинейной рации одномерных комплексных лов согласно формуле К

--r-. f

(фиг.2) содержит узел 8 постоянной па- 25 у(п) 21 x(n-J+1) w(j) +- мяти коэффициентов, регистр 9 коэф-j 1 u

фициентов, группу умножителей

K + 2 «(n-j + 1) x(n-j+j

10,...10 комплексных чисел, сумма - 11 и 12, регистры 13 и 14, муль

,...

торы

типлексор 15.

Блок 3 комплексного умножения (Лиг.З) содержит 2d регистров 16... 16 j, 17( ...17 и группу умножителей 18, 19|..,19g комплексных чисел, 201..., 21,...212.

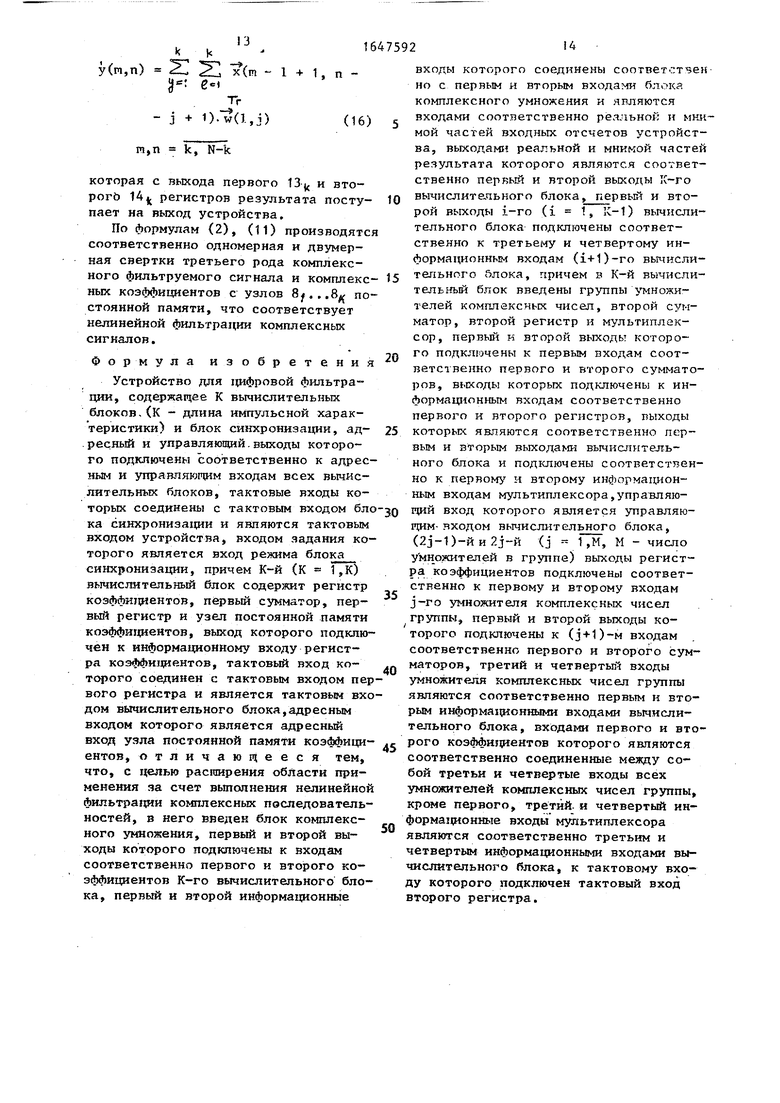

Умножитель комплексных чисел (фиг.4) содержит умножители 22-25, вычитатель 26 и сумматор 27,

Устройство работает следующим образом.

Предварительно рассмотрим работу умножителя комплексных чисел. Выполнению операции комплексного умножения соответствует выражение:

В-С (ReB + j ImB) x

х (ReC + j InC) a ReB ReC - ImB ImC + j (ReC ImB +

+ ReB-ImC)(1)

ReB, ReC код реальной (синфазной) составляющей комплексных сигналов В и С соответственно;

ImB, InC - код мнимой (квадратурной) составляющей комплексных сигналов

R и С соответственно.

На первый, второй, третий и четвертый входы умножителя поступают соответственно gследующие сигналы: ReB, InB, ReC, ImC.

На первом умножителе 22 производится умножение ReB, ReC, на втором умножителе 23 - ReC ImB, на третьем умножителе 24 - ReB«ImC, на четвертом умножителе 25 - ImB ImC. Вы- 5 читатель 26 кодов производит операцию вычитания - InB-ImC и выдачу первого выходного кода. Сумматор 27 производит операцию суммирования ReC«ImB + ReB IraC и выдачу 0 второго выходного кода.

При выполнении нелинейной фильтрации одномерных комплексных сигналов согласно формуле К

--r-. f

K + 2 «(n-j + 1) x(n-j+j

+ 1) x

r)

W(j,j ) +

k1

$

k

z:

,-M

x(n 35

- j+1) x(n-j+j +1) x(n - л +

+

j + 1) w (j, j .jYj

где n k, k-H,...,N.

Устройство работает следующим образом.

В исходном состоянии регистр 9 коэффициентов, первый 13 и второй 14 регистры всех вычислительных блоков 2 {...2к, первые 16{...16 и вторые 17,..17j регистры блока 3 находятся в нуле. На первый и второй информационные входы устройства постоянно подается код О, на тактовый вход поступают тактовые импульсы. На третьи и четвертые информационные входы устройства поступают отсчеты входной последовательности в виде кодов, (соответствующих вещественной и мнимой частям фильтруемого сигнала, со скоростью одного отсчета на такт

x(y), Imx(y), у I,...,N,

которые записываются

- V

в первые 16... и вторые

соответствй: нс j и вторые 17 ... 17

регистры сдвига блока 3, где с помощью умножителей 18, 19 . .. 19у 5 20 ,„. „20а , 21 ,.„,21 происходит комплексное умножение с получением результата в виде реальной и мнимой с ос т а в л ,

Выходные отсчеты на умножителях 19f...19g (первой группы) можно представить в виде:

Rex(j,i ) Rex(i)-Rex(j - Imx(j)«Inix(j - j ); Itnx(j,i ) Kex(i) -Imx(j + lnx(j)«Rex(j - j ) ,

Полученные выходные отсчеты попар но перемножаются между собой умножителями 2П{...20я, 21...21г, на выходах которых также выделяется реальная и мнимая составляющие:

г

ч

j

Irox(j, i ) -Imx(j i , j ) Rex

j , j ) Kex(j , j ) .Inx(j - т

JЦ | -К . С ЧЛ «5 Л J ,

) + lnx(i, j ) Rex(j - j ).(4) Aj),...,Re(Xj, Ai,

ранды tRe.Aj, ImAj, In(Aj, A j, ),...,Ile Aj-nili, Re(Aj, AJ,

А , k ,

Aj -K b

, Ai, IMA

Выходные сигналы, идугще на третий и четвертый информационные входы устройства, и полученные выходные отсчеты первой и второй групп с умножителей блока 3 подаются на входы умножителей Ю.Ш каждого из вычислительных блоков 2...2К.

Под воздействием сигнала Одномерная обработка поступающего на вход задания режима работы устройства., на выходе элемента ИЛИ-НЕ 7 формируется уровень логического О, передаваемый на управляющий вход мультиплексора 15, Под воздействием этого же сигнала Одномерная обработка на выходе коммутатора 5 припускается код числа К, передаваемый на адресные входы узлов постоянной пакяти 8 все блоков ,2ц, в резуль10

6475926

тате из ячейки адресом К считываются коэффициенты w(), где w(j) (w(j), w(j,1),.,.,w(i, , k), w(jsO,0, w(.i,150),...)w(j, k ,

0), w(j,0t1),...,w(jfkik Г} которые я течение всей операции фиксируются в регистре 9 коэффициента.Через промежуток времени, равный по крайней мере одному такту, с момента подачи сигнала Одномерная обработка на вход умножителя 10$ вычислительного блока 2 со скоростью отсчетов на такт начинают одновременно поступать отсчгты входной последовательности x(j),...,x(j) x(j),x(i) x(j-1),..., x(j) x(j-k ),...,x(i) x(j) x(j), x(j) x(j)t x(j-kf), x(j), x(j-1) x(j- -1),...,x(j) x(j-k) x(j-k )9 где j принимает значение от 1 до К и изменяет свое значение на единицу с каждым приходом следующего импульса тактовой частоты.

С целью упрощения описания дальнейшей работы определяют базовую опера:цию А,при которой формируется повторяющаяся совокупность действий выполняемых в течение одного такта в вычислительном блоке 2j.

Базовая операция выполняется сле- дуюр{им образом.

Ii исходный момент времени в первом 13 и втором 14 регистрах результатов хранятся некоторые промежуточ- , ные результаты Rebj ), а опе15

20

25

30

| -К . С ЧЛ «5 Л J ,

Aj),...,Re(Xj, Ai,

ранды tRe.Aj, ImAj,ReCAj, А,ч,), In(Aj, A j, ),...,Ile(A:, ), , Aj-nili, Re(Aj, AJ, AjT, In(Aj, A j, ;

40

А , k ,

Aj -K b

, Ai, ,I) ,... ,Re(A.-, IMAj, Aj..«, Aj.fc«)

поступают на третьи и четвертые входы умножителей 10j блока 3,. ка первые и вторые входы которых поступают коэффициенты

где

Rew(j), Imw(j)

Re(j) R«W(J), Rew(j,0), Rew(j,1),....Rew(j,k),

Rew(j,0,0),Rew(j,1,0),...,

Rew(j,k ,0), Rew(j,0,1),..., Rew(j, k1, k);

IEB(J) imw(j), Imw(j,0), IPiw(j,1),...,Imw(j, k ),

11647592 .8

Imw(j, 0,0,), Hw(j, 1, 0),..., Re(;, + Reb.lmi. + Inb-., Imw(j, k , 0), Irw(j,0,1),...,

,. .1 , Лкоторые с приходом импульсов такто- частоты записываются в первый

„,,п 1П .13 и второй 14 регистры результатов.

Затем в умножителях 10i...10j форми- „ .

1 оРассмотрим Формирование проиэвольруются произведения комплексных чисел..-/ jniOного отсчета v(n) выходной последоваТак, для умножителя 10 Справедливотельности СОГЛаСНо выражению

Rei, - Rew(j)-Rex(n-j+1) --(n) 7 n-j+1) ,Tr(j) (7)

- ImwCjMmxU-j+O;|5 где «0) ш (j) i(jto)fi(jf1)i...f

Ind, - RewCjMmxCn-j+D +.()) -(j)0j0) i(ji1,o),...,

+ I(j).Rei(3+t)(5) x(j,k , 0),x(j,0,1),...,

а для умножителя 10j.,. i « .T

, K- к / I

ReCi Rew(j, k , k )(n-j ,., Г /-% / «ч /

dJ L Jw(j) w(j), w(j,0),w(j,1),...,

k ).i(n-j+1-k ), i(n-j +25(jf k )g i(jf 0 0)j

+ 1)-W(j, k , k). ItnfxCn-w(j,1,0),...,w(j,k , 0),

w( ,1),... ,w( j ,k , k )J,

n k, N ImCd Rew (j , k , k ) - In x(n -TaRT 1. „a первый и BTQpoft

- j + 1) x (n-j+1-k ) , x(n - j +

.);

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1986 |

|

SU1327120A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1282156A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1984 |

|

SU1242986A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1984 |

|

SU1211750A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1101836A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1982 |

|

SU1101835A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

Изобретение относится к вычислительной технике и может быть ис- польчовано в вычислительных системах, Аункционирукщих в реальном масштабе времени. Цель изобретения - расширение области применения за счет выполнения нелинейной фильтрации комплексных сигналов. Поставленная цель достигается за счет того, что в состав устройства входят блок 1 синхронизации, К вычислительных блоков (К - длина обрабатываемой последовательности) 2{ -2 к и блок 3 комплексного умножения. 4 ил.

.,. . « ,4 /входы умножителя 10 поступают новые

-j + 1).x(n - j + 1 - k).x(n - входнь1е OTC4eTbI().

-. ) + т f k ® вычислительном блоке 2 выполня-1 J ется базовая операция А, в результаk ).Re х(п - j + 1) . x (n -Те КОТ°РОЙ СУММЙ

-j 1 - k ).x(n - j + 1 - k)/° У(П) i(n - k + °(k) +i (n k +

(6)+ 1) .x(n - k - j + 1). wf(k,

К К

причем реальные и мнимые составляю-. . .r - ,.

щие раздельно подаются на первые 11 Гл и вторые 12 сумматоры, соответственно. Одновременно с выходов первого- k + 11 f v + 1 - ч г 13 и второго 14 регистров результата с вычислительного блока 2 на вто-, . 4 .1 . ич ,, ,

, „50 k+1-j-j) .we(k, k +

рой информационный вход мультиппек- 4

сора 15 выдаются промежуточные ре-. t ,+ (Л)

зультаты Rebj. и Itnbj, которые

(поскольку на управляющий вход муль-записывается в первые 13 и второй 14

типлексора 15 подан логический О)регистры результатов вычислительнопередаются на входы первых 11 и вто- го блока 2.

рых 12 сумматоров соответственно.Такт n-k+2. На первый и второй

Первый 11 и второй 12 сумматоры фор-входы умножителя Ю| поступают номируют суммывые входные отсчеты x(n-k+1). В вычислительном блоке 2 выполняется базовая операция А, результате которой сумма

У 2.00 У,(п) +()(k-1)

(9)

записывается в первый 13 и второй 14 регистры результатов вычислительного блока 2.

Такт п. В блоке 2к выполняется базовая операция, в результате которой окончательное значение

Ук(п) yk./n) + х(п) З О ) (TO)

записывается в первый 13 и второй 14 регистры результатов вычислитель

ного блока 2, откуда поступает на выход устройства.

Таким же образом выполняется формирование других отсчетов y(i) с тон лишь разницей, что формирование результата в вычислительном блоке 2 происходит в такте i-k+1, а в вычислительном блоке 2к - п такте i, тем самым осуществляется корреляция одномерных нелинейных сигналов.

При выполнении нелинейной фильтра ции двумерных комплексных сигналов согласно выражению

k К у(п,п) 2 2L)x(m-l + 1,n-j +

е-1

k lc + 1)-w(l,j) + ZH 2C

- 1 +1, 1 , п - + 1,j )

w(l, l , j, j ) +

К К1 ic k

2-.2L (n - i + i, i ,

jv, et«e i

с

}

п - j + 1 , j

);(

i

где x(n -l+1,l,n-j+1,j )

x(m-l+1,l,n-j+

+ 1, j ) (1-1 ) + 1, n-- (j - j ) + m,n k, k-t-1,...,N.

0

0

При этом указанные коэффициенты получают в блоке 3 способом, аналогичным описанному для одномерной нелинейной цифровой фильтрации. Устройство работает следующим образом.

Б исходном состоянии счетчик 4 (по модулю k) обнулен. Чатем на вход задания режима работы устройства поступает сигнал Двумерная обработка, под воздействием которого счетчик 4 начинает реагировать на поступающие на его вход импульсы тактовой частоты, осуществляя их счет по модулю k. Под воздействием этого же сигнала Двумерная обработка на вход коммутатора 5 пропускается содержимое счетчика 4, передаваемое затем на адресный вход узлов PJ постоянной памяти. В результате этого в течение такта с номером т (где т - 1, 2,...) таким, что т 1 из ячейки узла 8j постоянной памяти, с адресом 1-1 происходит микрооперация считывания 5 вектора коэсЪфтр ентов:

5

- 30

35

40

w(k - 1 + 1, k) - w(k - 1 + 1,k), w(k - 1 + 1, 0, k, 0), w(l, 0, k, 1 ),.„., w(k - + 1, l,k,k ),..., w(k - 1 + + 1, k , k, k )t w(k -1 + 1,0, 0, k, 0, 0),...,w(k - 1 + 1, k ,

, II.. I .

k , k, k , k )J ,

которые в течение следующего такта фиксируются в регистре 9, коэффици)

ента.

Содержимое счетчика 4 дешифрируется с помощью дешифратора 6, на выходе которого в течение такта с дс номером Т таким, что т t mod, вырабатывается уровень логической 1, под воздействием которого на выходе элемента ШШ-НЕ 7 формируется уро

50

55

вень логического О , передаваемый на управляющий вход мультиплексора 15,.. В течение остальных тактов на выходе элемента ИЛИ-НЕ 7 формируется уровень логического О, передаваемый на управляющий вход мультиплексора 15.

Таким образом, в течение такта с номером Т таким, что Т 1 modK, в вычислительном блоке 2j выполняется базовая операция А.

11164759212

В течение остальных тактов в вы- , -, , ч -,,

,- о - 1 + х(а + q, b + d) w(k - a +

числительном блоке 2 выполняется базовая операция Б, которая отличает- + 1 k - 1 + Пfn ся от базовой операции А лишь тем,

что мультиплексор 15 (поскольку на.

„где d - номер вычислительного блоего управляющий вход поступает ло-,, --.

гическая 1) передает на вход пер-

.. Тоа номеР отсчета первой пере- вого 11 и второго 12 сумматоров променнои текущего CVMMHPO- мехуточный результат, хранярщися в щ

0 л,1и вания входного двумерного

первом 13 и втором 14 регистрах ре-, г-г,

сигнала (а 1,k):

зультата.,

„b - номер переменной, определя- Рассмотрим Формирование произволь-„ v

/ ющеи цикл суммирования для

ного отсчета у(п,п) выходного массива, Г/,

J первого индекса k + b (b

согласно выражениюj5 Q-п-ъ)

к П номер переменной, определяю« ( 1ще Дикл суммирования для

у(.п,п; - Ј, х .п ,второго индекса двумерного

сигнала (q 0,N-k);

Тгм „% 1o 2° (d-1)

п - j + 1) ,w(l, У), (12)

X

н-1 ( .xk+a - номер очередного суммирогде x(l,j) (1, т), х (l,0,j,0),вания для одного выходно, ( /го отсчета,

х(1 J О х(1, 1, J,k )25 причем при d 1 выполняется бачо, I . I .вая операция А, а в остальных слух(1 , j, k ), x(l,0,0,i,0,чаях вьтолняется базовая операция В.

0),..., х(1, k , k , j, k ,Например, при d 1, q О,

..30 b 0, a 1.

k )Ъ

Такт R d-k + 1 для вычислитель w(1,l) w(l,0,j,0),ного блока с индексом d вычисляется

-следуюл м образом:

w(l,0,j,Ow(l,1,j,lt ),f 35 ,.

ээ y(k,k)d-k+1 y(k,k) d-k +

w(l, k , j, k ), w(l,0,0,j,0, ., , ..

+ x(1,1+d)- w (k,k-d).

„. /,,,,, 1

0),...,w(l, k , k , j,k , k )J ,

40( }

где Тг - операция транспортирования

вектора.Я блоке 2 выполняется базовая

Обозначим , , операция В, в результате которой I k - а + 1 i k-d+1.B первый 13 и второй 14к регистры

с результата в такте R k2 + JJZ- (N Рассмотрим работу устройства по - k) -Ij k-q + k1b записывается сум- тактам.ма

Такт R (d - 1) k + (2- (N-k) - - l)-bq + b-k + d,tК

На выходы умножителей Ю.-.Ю с y(k + q, k + b) Li r j x(a + блока 3 подаются отсчеты, соответству-а о«1

ющие вектору х(а + q, b + d). В бло-- Тг

ке выполняется базовая операция A+q, b+d)-w (k-a+1,k(или В), в результате которой вычисляется:- d + 1);(15)

y(k + q, k + d)(d - 1)%k-i-a при замене переменных k + q in,

,l k-a+1, y(k+q, k+b)(d-1)-k+a- -d+1, соответствующая выражению

X

(n,n)

k

-z:

8-:

13 x(n

- J

Ц

Zl

: e«i

rr

+ 1).wO,j)

16

-1 + 1,

n (16)

m,n k, N-k

которая с выхода первого 13 и второго 14 k регистров результата поступает на выход устройства.

По формулам (2), (11) производятся соответственно одномерная и двумерная свертки третьего рода комплексного фильтруемого сигнала и комплекс- ных коэффициентов с узлов 8...8 постоянной памяти, что соответствует нелинейной фильтрации комплексных сигналов.

Формула изобретения

Устройство для цифровой фильтрации, содержащее К вычислительных блоков.(К - длина импульсной характеристики) и блок синхронизации, ад- ресный и управляющий выходы которого подключены соответственно к адресным и управляющим входам всех вычислительных блоков, тактовые входы которых соединены с тактовым входом бло ка синхронизации и являются тактовым входом устройства, входом задания которого является вход режима блока синхронизации, причем К-й (К 1,К) вычислительный блок содержит регистр коэффициентов, первый сумматор, первый регистр и узел постоянной памяти коэффициентов, выход которого подключен к информационному входу регистра коэффициентов, тактовый вход которого соединен с тактовым входом первого регистра и является тактовым входом вычислительного блока,адресным входом которого является адресный

вход узла постоянной памяти коэффици- ., рого коэффициентов которого являются

ентов, отличающееся тем, что, с целью расширения области применения за счет выполнения нелинейной фильтрации комплексных последовательностей, в него введен блок комплексного умножения, первый и второй выходы которого подключены к входам соответственно первого и второго коэффициентов К-го вычислительного блока, первый и второй информационные

50

соответственно соединенные между собой третьи и четвертые входы всех умножителей комплексных чисел группы, кроме первого, третий и четвертый информационные входы мультиплексора являются соответственно третьим и четвертым информационными входами вычислительного блока, к тактовому входу которого подключен тактовый вход второго регистра.

1647592

14

0

5

5 о

5

0

входы которого соединены соответствен но с первым и вторым входами блока комплексного умножения и являются входами соответственно реальной и мнимой частей входных отсчетов устройства, выходами реальной и мнимой частей результата которого являются соответственно первый и второй выходы К-го вычислительного блока, первый и второй выходы i-го (i t, К-1) вычислительного блока подключены соответственно к третьему и четвертому информационным входам (i+1)-ro вычислительного блока, причем в К-й вычислительный блок введены группы умножителей комплексных чисел, второй сумматор, второй регистр и мультиплексор, первый и второй выходь которого подкличены к первым входам соответственно первого и второго сумматоров, выходы которых подключены к информационным входам соответственно первого и второго регистров, выходы которых являются соответственно первым и вторым выходами вычислительного бпока и подключены соответственно к первому и второму информационным входам мультиплексора,управляющий вход которого является управляющим-входом вычислительного блока, (2j-1)-ft (j - 1,М, М - число умножителей в группе) выходы регистра коэффициентов подключены соответственно к первому и второму входам j-го умножителя комплексных чисел группы, первый и второй выходы которого подключены к (j + D-м входам соответственно первого и второго сумматоров, третий и четвертый входы умножителя комплексных чисел группы являются соответственно первым и вторым информационными входами вычислительного блока, входами первого и вто0

соответственно соединенные между собой третьи и четвертые входы всех умножителей комплексных чисел группы, кроме первого, третий и четвертый информационные входы мультиплексора являются соответственно третьим и четвертым информационными входами вычислительного блока, к тактовому входу которого подключен тактовый вход второго регистра.

.„

tor, 2

Фив, 4

| Устройство для цифровой фильтрации | 1984 |

|

SU1211748A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1325511A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-07—Публикация

1988-12-14—Подача