фиг. /

112

Изобретение относится к импульсной технике и может быть использовано для задержки импульсов, а также для генерирования прямоугольных импульсов.

Цель изобретения - расширение диапазона выдержек времени и повышение точности за счет устранения искажени длительности выходных импульсов.

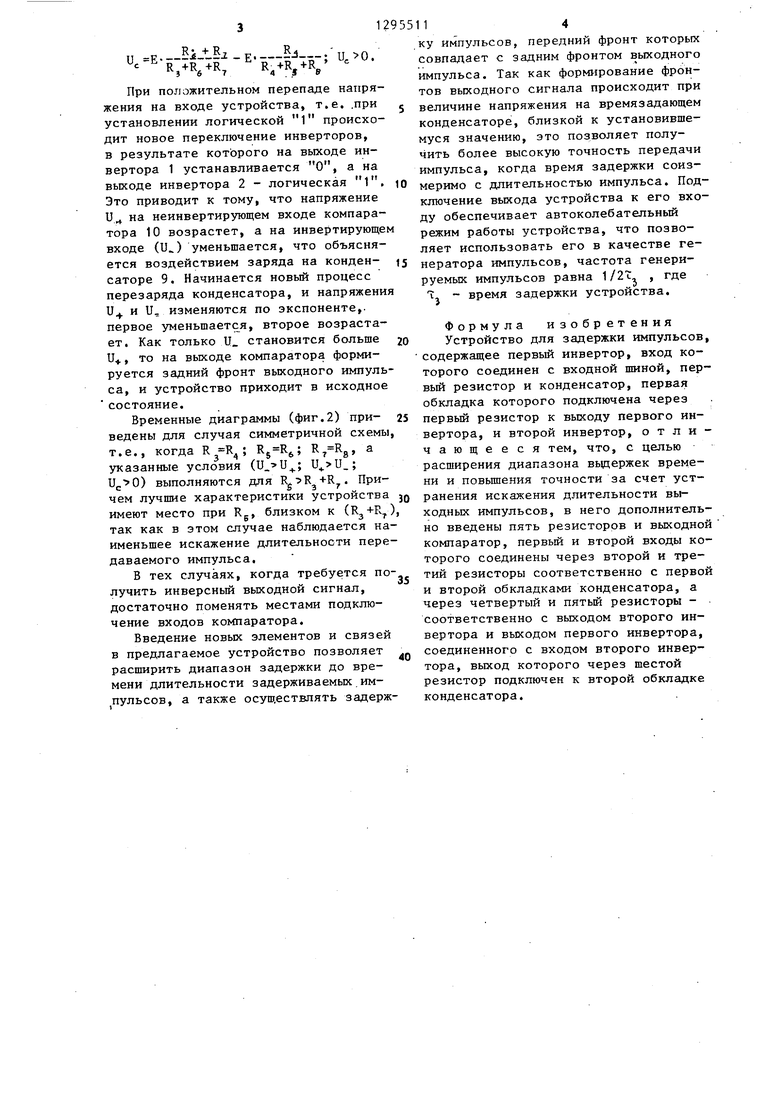

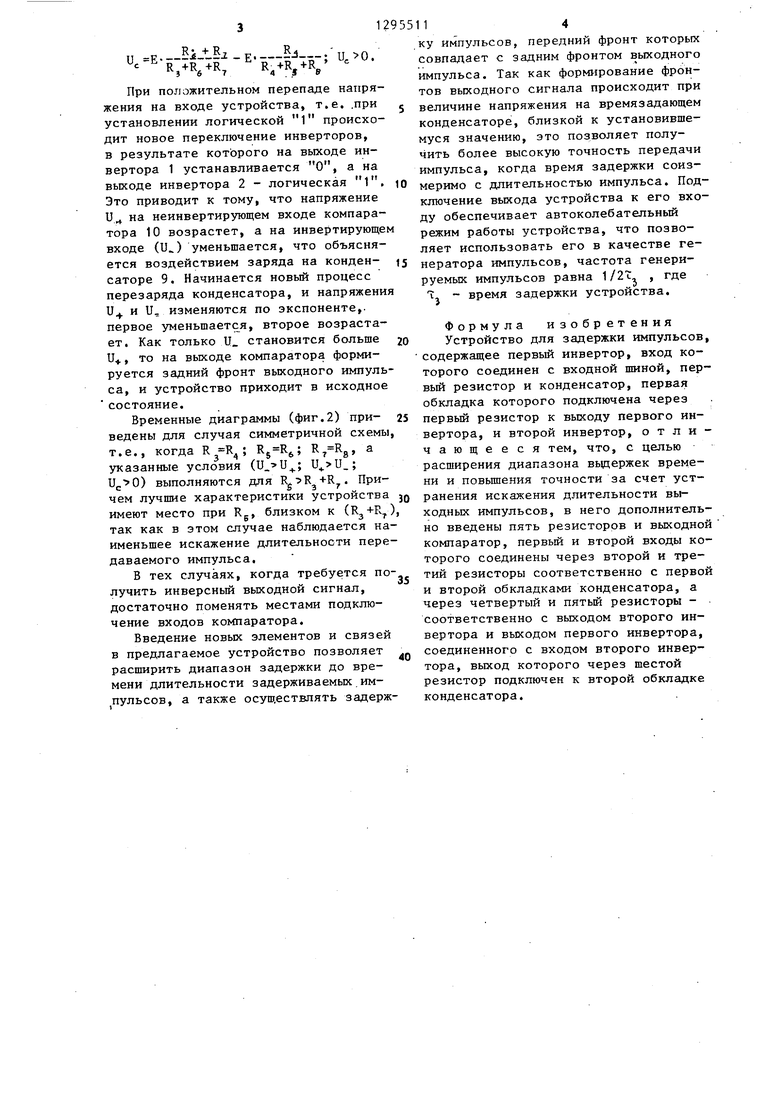

На фиг.1 представлена схема уст- ройства; на фиг.2 - временные диаграммы напряжений в соответствующих точках схемы, поясняющие работу устройства.

Устройство для задержки импульсов содержит инверторы 1 и 2, резисторы 3-8, конденсатор 9, компаратор 10, входную шину 11, выходную шину 12. На схеме обозначены выход 13 первого инвертора 1, вькод 14 второго инвер- тора 2, первый (неинвертирующий) вход 15 компаратора 10, второй (инвертирующий) вход 16 компаратора 10.

В качестве компаратора 10 в устройстве используется операционный усилитель с дифференциальными входами

Входная шина 11 подключена к вход первого инвертора 1, выход которого соединен через цепочку последователь o соединенных резисторов 3 и 7 с первым входом 15 компаратора 10 и подключен к входу второго инвертора 2. Выход второго инвертора 2 соединен через резистор 6 с первым входом 15 компаратора и подключен через цепоч ку последовательно соединенных резисторов 4 и 8 к второму входу 16 компаратора 10, который через резистор 5 соединен с выходом первого инвертора 1. Конденсатор 9 подключен одной обкладкой к общим точкам резисторов 3 и 7, а другой - к общим точкам резисторов А и 8.

Устройство работает следующим образом.

В исходном состоянии на входе устройства присутствует высокий потенциал (логическая 1), на выходе первого инвертора 1 - логический О, на выходе второго инвертора 2 - ло- гическая 1. Будем считать, что уровень логической 1 равен напряжению источника питания +Е, а уровень логического О равен нулю.

Уровень напряжения на первом (не- инвертирующем) входе компаратора U .

Р и Е---5- - --

.-

15

25

55

5

.

, -

35

40

45

112

где RJ, R - сопротивление резисторов 3, 6 и 7 соответственно.

Уровень напряжения на втором (инвертирующем) входе компаратора U. равен

- R- ifrR4 5 8

где R, Rg и R - сопротивление резисторов 4, 5 и 8 соответственно.

Напряжения U. и U близки по величине, однако и больше U, поэтому на выходе комларатора - логический О. Конденсатор 9 заряжен током, протекавшим по цепи выход второго инвертора - резистор 4 - конденсатор 9 - резистор 3 - выход первого инвертора 1. Величина напряжения U, до которой зарялсен конденсатор 9, определяется разностью потенциалов

IT : W&J5±J.a ТГ5j П О

Vv ..R/

При отрицательном перепаде напряжения на входе устройства, т.е. при установлении логического О происходит переключение инверторов, в результате чего на выходе инвертора 1 устанавливается логическая 1, а на выходе инвертора 2 - логический О. Это приводит к тому, что напряжение и на инвертирующем входе 16 компаратора возрастет, так как опред епяет- ся сзт«1марным воздействием высокого .потенциала на вькоде инвертора 1 и напряжением на конденсаторе 9, а напряжение и на инвертирующем входе компаратора 10 падает. Далее по мере перезаряда конденсатора 9 напряжения и. и U- изменяются по экспоненте, причем и стремится к величине большей, чем величина напряжения, к которой стремится и . Как только U. становится больше и, на выходе компаратора формируется передний фронт задержанного импульса. Напряжения U и и устанавливаются и равны

и Е .§Jl

R3-bR.R/ - R.

Причем U больше U, но оба напряжения близки по величине. Конденсатор 9 заряжается током, протекающим по цепи выход инвертора 1 - резистор 3 - конденсатор 9 - резистор 4 - выход инвертора 2. Величина напряжения на конденсаторе равна разности потенциалов

I -V5i t..5j n n

c R,.R,.R, R,-R,-R/

При положительном перепаде напряжения на входе устройства, т.е. .при установлении логической 1 происходит новое переключение инверторов, в результате которого на выходе инвертора 1 устанавливается О, а на выходе инвертора 2 - логическая 1. Это приводит к тому, что напряжение и на неинвертирующем входе компаратора 10 возрастет, а на инвертирующем входе (и) уменьшается, что объясняется воздействием заряда на конден- саторе 9. Начинается новый процесс перезаряда конденсатора, и напряжения и и и, изменяются по экспоненте,, первое уменьшается, второе возрастает. Как только и становится больше и, то на вькоде компаратора формируется задний фронт выходного импульса, и устройство приходит в исходное состояние.

Временные диаграммы (фиг.2) при- ведены для случая симметричной схемы.

6

R

т.е., когда R указанные условия (.; ) выполняются для Rg sR +R. Причем лучшие характеристики устройства JQ имеют место при R, близком к (R.j+R), так как в этом случае наблюдается наименьшее искажение длительности передаваемого импульса.

В тех случаях, когда требуется по-, лучить инверсный выходной сигнал, достаточно поменять местами подключение входов компаратора.

Введение новых элементов и связей в предлагаемое устройство позволяет расширить диапазон задержки до времени длительности задерживаемых импульсов, а также осуш.ествлять задерж35

40

10

мjjя 20

25 .

2955114

ку импульсов, передний фронт которых совпадает с задним фронтом выходного импульса. Так как формирование фронтов выходного сигнала происходит при величине напряжения на времязадающем конденсаторе, близкой к установившемуся значению, это позволяет получить более высокую точность передачи импульса, когда время задержки соизмеримо с длительностью импульса. Подключение выхода устройства к его входу обеспечивает автоколебательный режим работы устройства, что позволяет использовать его в качестве генератора импульсов, частота генериJQ), -,

35

40

руемых импульсов равна 1/2, , где 7 - время задержки устройства.

Формула изобретения Устройство для задержки импульсов, содержащее первый инвертор, вход которого соединен с входной шиной, первый резистор и конденсатор, первая обкладка которого подключена через первый резистор к выходу первого инвертора, и второй инвертор, отличающееся тем, что, с целью расширения диапазона вьщержек времени и повьш1ения точности за счет устранения искажения длительности выходных импульсов, в него дополнительно введены пять резисторов и выходной компаратор, первый и второй входы которого соединены через второй и третий резисторы соответственно с первой и второй обкладками конденсатора, а через четвертый и пятый резисторы - соответственно с выходом второго инвертора и выходом первого инвертора, соединенного с входом второго инвертора, выход которого через тестой резистор подключен к второй обкладке конденсатора.

7/ f3

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов по длительности | 1984 |

|

SU1226637A1 |

| Фиксатор уровня | 1984 |

|

SU1228242A1 |

| Формирователь задержки импульсов | 1984 |

|

SU1236599A1 |

| Измерительный преобразователь температуры с частотным выходом | 1985 |

|

SU1278623A1 |

| Способ определения входного сопротивления усилителя заряда и устройство для его осуществления | 1984 |

|

SU1205060A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Устройство для дифференциальной защиты | 1988 |

|

SU1610533A2 |

| Устройство для дифференциальной защиты электроустановки | 1983 |

|

SU1141498A1 |

| Генератор пилообразного напряжения с переменной крутизной | 1987 |

|

SU1495982A1 |

| Электронная приставка к транзисторной системе зажигания | 1991 |

|

SU1800086A1 |

Изобретение относится к импульсной технике и может быть использовано для задержки импульсов, а также для генерирования прямоугольных импульсов. Цель изобретения - расширение диапазона вьщержек времени и повьпиение точности достигается за счет устранения искажения длительности выходных импульсов. Устройство содержит инверторы 1 и 2, резистор 3, конденсатор 9, входную шину 11, выходную шину 12. Для достижения поставленной цели в устройство дополнительно введены компаратор 10 и резисторы 4, 5, 6, 7 и 8. На чертеже также показаны выход 13 первого инвертора, выход 14 второго инвертора, неинвертирующий 15 и инвертирующий 16 входы компаратора, в качестве которого в устройстве используется операционный усилитель с дифференциальными входами. 2 ил. // 15 bs 8 16

16 15

12

i

| Устройство для задержки импульсов | 1982 |

|

SU1083353A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-07—Публикация

1984-09-14—Подача