Изоб11етение относится к измерительной технике, в частности к изме рениго и контролю параметров измерительных преобразований малых токов и зарядов.

Целью изобретения является повышение точности измерения путем устранения погрешностей измерения, обусловленных входными токами смещения и напряжением смещения нуля усилителя заряда.

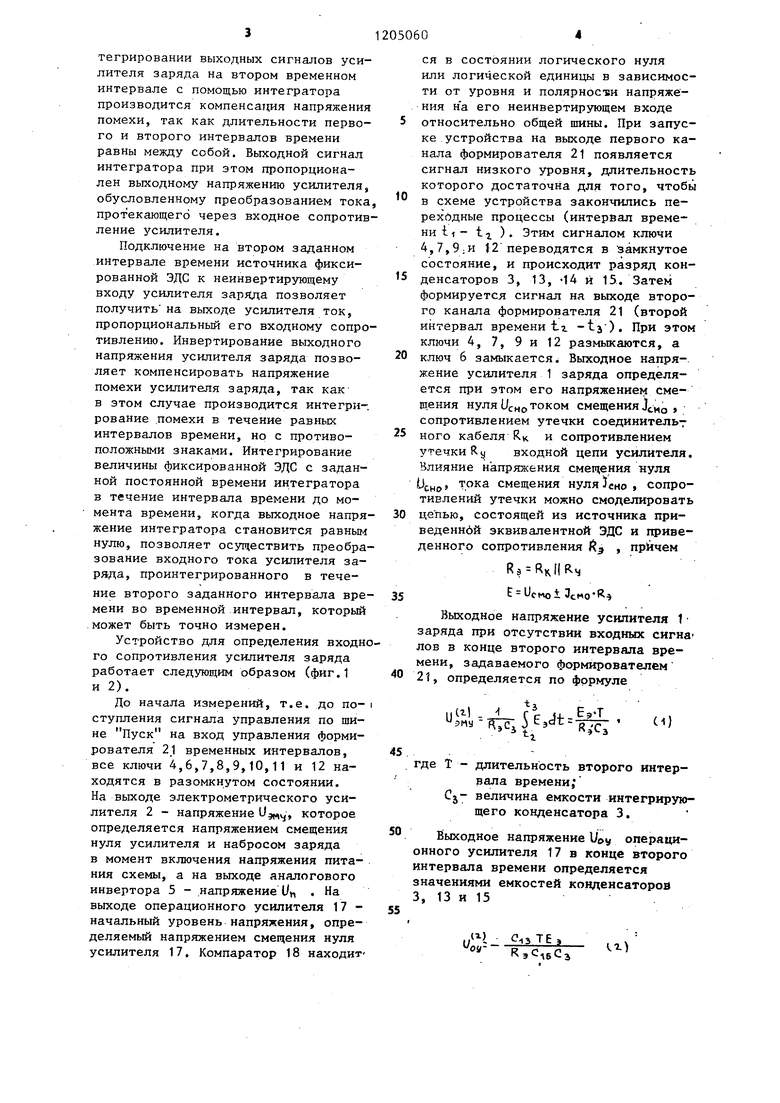

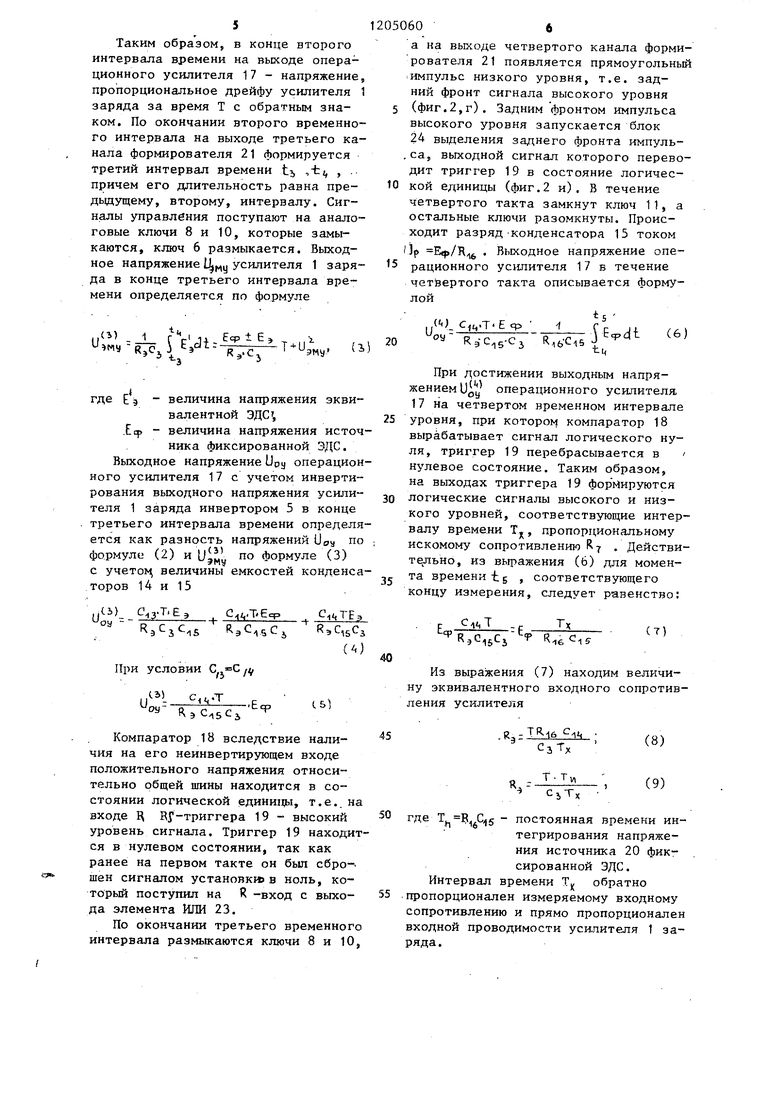

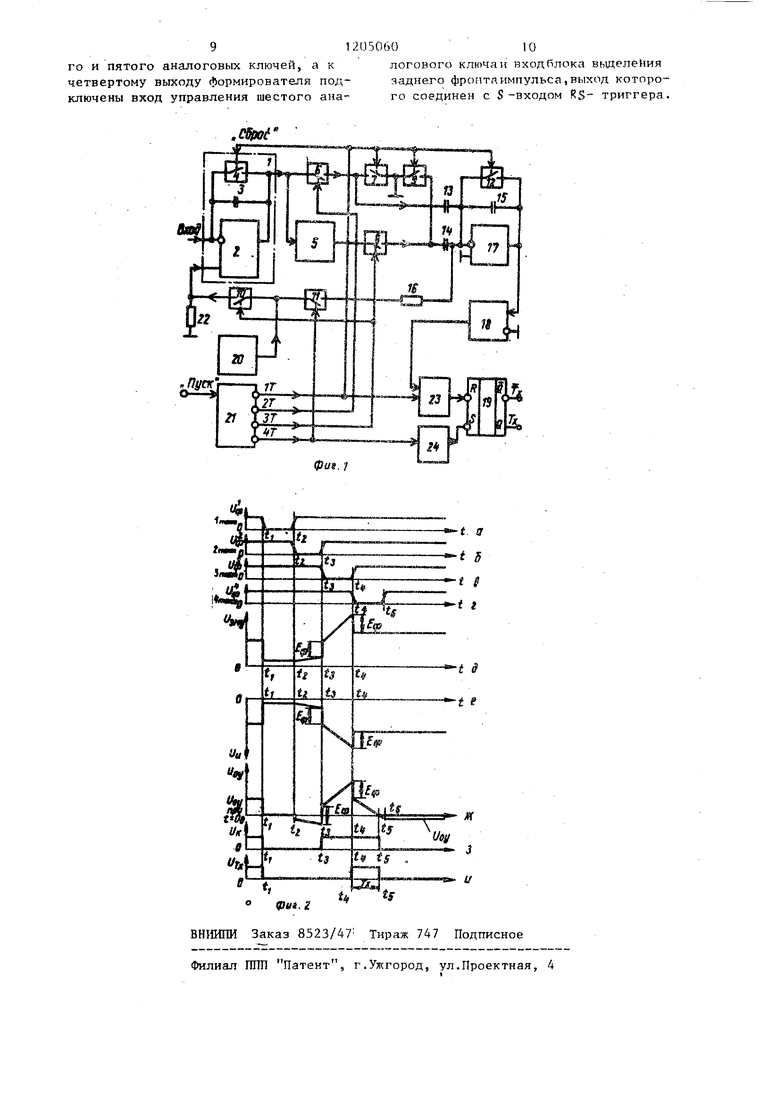

На фиг,1 приведена функциональная схема устройства, осуществляю- п(его предлагаемый способ; на фиг. 2 временная диаграмма его работы.

Устройство содержит усилитель 1 заряда, Б общем случае включающий электрометрический усилитель 2, интегрирующий конденсатор 3 и разрядный ключ 4, вход управления которого подключен к входу Сброс усилитля 1 заряда, аналоговый инвертор 5, )первый 6, второй 7, третий 8, чет- шертый 9, пятый 10, шестой 11 и седьмой 12 аналогсЯзые ключи, каждый |из которых имеет по два информацион ных вывода и вход управления, первы 13, второй 14 и третий 15 конденсаторы, дополнительный резистор 16, операционный усилитель 17, компаратор 18, RS Триггер 19, источник

20фиксированной ЭДС, формирователь

21временных интервалов, резистор 22, подключенный к неинвертирующему входу электрометрического усилителя 2, логический элемент ИЛИ 23

и блок 24 выделения заднего фронта к-1пульса, при этом первый информационный вывод разрядного ключа 4 и первая обкладка интегрирующего конденсатора 3 подключены к инвертирующему входу электрометрическогс усилителя 2, являющемуся входом усилителя 1. К выходу усилителя 2 подключены второй информационный вывод разрядного ключа 4, вторая обкладка интегрирующего конденсатора 3, вход аналогового инвертора 5 и первый информационный вывод акалого Бого ключа 6, К первой обкладке кон дексатора 13 подключены вторые информационные выводы аналоговых ключей 6 и 7. Выход инвертора 5 подключен к первому информационному выводу аналогового ключа 8. Вторые информационные выводы аналоговых ключей 8 и 9 подключены к перво обкладке конденсатора 14. Первый

5

0

5

0

О

5

O

3

информационный ключа 12, первая обкладка конденсатора 15, вторые обкладки конденсаторов 13 и 14 и первый вывод догюлнительного резистора 16 подключены к инвертирующему входу операционного усилителя 17, выход которого соединен с не- инвертирую1цим компаратора 18, выход которого подключен к первому входу элемента 23 ИЛИ. Первые информационные выводы аналог О1 ь Х ключей 10 и 11 подключены к выходу источника 20 фиксированной ЭДС, а их вторые информационные выводы - соответственно к неинвертирующему входу усилителя 2 и второму выводу .дополнительного резистора 16. Вход фор мирователя 21 временньЕ интервалов подключен к шине Пуск устройства. К выходу первого канала формирователя 21 подключены вход Сброс усилителя 1 заряда, вход управления аналоговых ключей 7, 9 и 12 и второй вход логического элемента ;11И 23,

. выход которого соединен с Я-входом RS -триггера 19. К вьгходу второго канала формирователя 21 подключен

вход управления аналогового ключа б. Входь) управления аналоговых ключей 10 и 11 соединены с вьгходом третье- го канала формирователя 21. К выходу четвертох о канала формирователя 21 подключены вход управления ключа 11 и вход блока 24 выделения заднего фронта импульса, выход которого соединен с 5 -входом RS -триг - гера 19.

Второй вывод резистора 22, неинвертирующий вход опера:;ионного усилителя 17, первые информационные выводы аналоговых ключей 7 и 9 и инвертирующий вход компаратора 18 подключены к общей ишне устройства.

Сущность способа определения : входного сопротивления усилителя заряда заключается в том, что дифференцирование выходного сигнала усилителя заряда, обусловленного токами смещения и напряжением щения нуля усилителя, с помощью дифференцирующей цепи с заданной постоянной времени, а затем интегрирование полученного сигнала позволяет получить на выход,- интегратора уровень напряжения, равный уровню помехи на выходе усилителя при его работе в течение заданного интервала времени. Таким образом, при ийтегрировании выходных сигналов усилителя заряда на втором временном интервале с помощью интегратора производится компенсация напряжения помехи, так как длительности первого и второго интервалов времени равны между собой. Выходной сигнал интегратора при этом пропорционален выходному напряжению усилителяj обусловленному преобразованием тока протекающего через входное сопротивление усилителя.

Подключение на втором заданном интервале времени источника фиксированной ЭДС к неинвертирующему входу усилителя зарНда позволяет получить на выходе усилителя ток, пропорциональный его входному сопротивлению. Инвертирование выходного напряжения усилителя заряда позволяет компенсировать напряжение помехи усилителя заряда, так как в этом случае производится интегрирование помехи в течение равных интервалов времени, но с противоположными знаками. Интегрирование величины фиксированной ЭЛС с заданной постоянной времени интегратора в течение интервала времени до момента времени, когда выходное напряжение интегратора становится равным нулю, позволяет осуществить преобразование входного тока усилителя заряда, проинтегрированного в течение второго заданного интервала времени во временной интервал, который .может быть точно измерен.

Устройство для определения входнго сопротивления усилителя заряда работает следующим образом (фиг.1 и 2).

До начала измерений, т.е. до поступления сигнала управления по шине Пуск на вход управления формирователя 21 временных интервалов, все ключи 4,6,7,8,9,10,11 и 12 находятся в разомкнутом состоянии. На выходе электрометрического усилителя 2 - напряжение которое определяется напряжением смещения нуля усилителя и набросом заряда в момент включения напряжения питания схемы, а на выходе аналогового инвертора 5 - напряжение Uy, .На выходе операционного усилителя 17 - начальный уровень напряжения, определяемый напряжением смещения нуля усилителя 17. Компаратор 18 находится в состоянии логического нуля или логической единицы в зависимости от уровня и полярнос-ви напряжения н а его неинвертирующем входе

относительно общей шины. При запуске устройства на выходе первого канала формирователя 21 появляется сигнал низкого уровня, длительность которого достаточна для того, чтобы

в схеме устройства закончились пе- рехлдные процессы (интервал времени ii- 1г ). Этим сигналом ключи 4,7,9;И 12 переводятся в замкнутое состояние, и происходит разряд конденсаторов 3, 13, -14 и 15. Затем формируется сигнал на выходе второго канала формирователя 21 (второй интервал времени tг -tj ). При этом ключи 4, 7, 9 и 12 размыкаются, а

ключ 6 замыкается. Выходное напряжение усилителя 1 заряда определяется при этом его напряжением смещения nynnUc f TOKOM смещения JtHo сопротивлением утечки соединительт

кого кабеля RK и сопротивлением утечки Rj| входной цепи усилителя. Влияние напряжения смещения нуля UCHO Т.ока смещения нуля JCHO сопротивлений утечки можно смоделировать

цепью, состоящей из источника при- веденнбй эквивалентной ЭДС и приведенного сопротивления Jk , причем

Яэ «кНЯч

E UcMoi3cHo-R

Выходное напряжение усилителя 1 заряда при отсутствии входных сигналов в конце второго интервала времени, задаваемого формирователем 21, определяется по формуле

БэТ

С с . , 01

где Т - длительность второго интервала времени;

Cj- величина емкости интегрирующего конденсатора 3.

Выходное напряжение Uoy операционного усилителя 17 в коице второго интервала времени определяется значениями емкостей конденсаторов 3, 13 и 15

--эТЕ - R,c,,C

т-)

Таким образом, в конце второго интервала времени на выходе операционного усилителя 17 - напряжение, пропорциональное дрейфу усилителя 1 заряда за время Т с обратным знаком. По окончании второго временного интервала на выходе третьего канала формирователя 21 формируется третий интервал времени tj, ,i:i, , причем его длительность равна предыдущему, второму, интервалу. Сигналы управления поступают на аналоговые ключи 8 и 10, которые замыкаются, ключ 6 размыкается. Выхода на выходе четвертого канала форм рователя 21 появляется прямоугольн импульс низкого уровня, т.е. задний фронт сигнала высокого уровня 5 (фиг.2,г). Задним фронтом импульса высокого уровня запускается блок 2 выделения заднего фронта импуль ,са, выходной сигнал которого перев дит триггер 19 в состояние логичес 10 кой единицы (фиг.2 и). В течение четвертого такта замкнут ключ 11, остальные ключи разомкнуты. Происходит разряд-конденсатора 15 током р Еф/К . Выходное напряжение оп

ное напряжение усилителя 1 заря- 5 рационного усш1ителя 17 в течение

четвертого такта описывается форм лой

да в конце третьего интервала времени определяется по формуле

t

ГЕ .,.

RyCj

где Е 9 величина напряжения эквивалентной ЭДС ,

.Еср - величина напряжения источника фиксированной ЭДС. Выходное напряжение Upy операционного усилителя 17 с учетом инвертирования выходного напряжения усилителя 1 заряда инвертором 5 в конце третьего интервала времени определяется как разность напряжений (Joy по формуле (2) и по формуле (3) с учето величины емкостей конденсаторов 14 и 15

С..Т Е

is

C vTEcp эСгбС,

1.ТЕэ sCisCj

(А)

При условии fif

«- R C.sCi

€ср

15

Компаратор 18 вследствие наличия на его неинвертирующем входе положительного напряжения относительно общей шины находится в состоянии логической единицы, т.е., на входе Д Rf-триггера 19 - высокий уровень сигнала. Триггер 19 находится в нулевом состоянии, так как ранее на первом такте он был сбро-- шеи сигналом установки) в ноль, который поступил на R -вход с выхода элемента ИЛИ 23.

По окончании третьего временного интервала размыкаются ключи 8 и 10,

2050606

а на выходе четвертого канала формирователя 21 появляется прямоугольный импульс низкого уровня, т.е. задний фронт сигнала высокого уровня 5 (фиг.2,г). Задним фронтом импульса высокого уровня запускается блок 2 выделения заднего фронта импуль- ,са, выходной сигнал которого переводит триггер 19 в состояние логичес- 10 кой единицы (фиг.2 и). В течение четвертого такта замкнут ключ 11, а остальные ключи разомкнуты. Происходит разряд-конденсатора 15 током р Еф/К . Выходное напряжение рационного усш1ителя 17 в течение

5 рационного усш1ителя 17 в течение

20

четвертого такта описывается формулой

s .С-). .Т Еср -f

и,

оу

Ri6-Ci6

JEcpdt (6)

t

жением

При достижении выходным напряоперационного усилителя 17 На четвертом временном интервале

уровня, при котороь компаратор 18 вырабатывает сигнал логического нуля, триггер 19 перебрасывается в нулевое состояние. Таким образом, на выходах триггера 19 фор йируются

логические сигналы высокого и низкого уровней, соответствующие интервалу времени Tj, пропорциональному искомому сопротивлению R Действительно, из вьфажения (6) для момента времени t 5 , соответствующего концу измерения, следует равенство:

«J-,

R.c.jCj

-Е

TX

f R-ifeCis

(Т)

40

Из выражения (7) находим величину эквивалентного входного сопротивления усилителя

45

. Rg ;

СзТ;,

(8)

Т.Т,

CiTx

(9)

где постоянная времени интегрирования напряжения источника 20 фиксированной ЭДС. Интервал времени Т обратно пропорционален измеряемому входному сопротивлению и прямо пропорционален входной проводимости усилителя 1 заряда .

10

71205060

Формула изобретения

1. Способ определения входного опротивления усилителя заряда, за- лючаю цийся в интегрировании тока, ротекающего через входное сопротивение усилителя с помощью интегриующего конденсатора, отличаюийся тем, что, с целью повыения точности, производят начальную установку выходного напряжения силителя заряда, формируют первый заданный интервал времени, в конце оторого запоминают величину выходного напряжения усилителя заряда, ормируют Бторой интервал времени, авный первому, и подают на прямой вход усилителя заряда напряжение заданной величины, находят разность между выходными напряжениями конце первого и второго интерваов времени и производят интегрирование напряжения заданной величины о момента времени, когда найденная азность напряжений и проинтегриованное значение напряжения заданной величины станут -равны, и входное сопротивление Rg усилителя заряа определяют по формуле

15

20

25

ус че ме ло де вы пе ан го вы вы кл ин ма во вы го кл ры де го он кл ре ще к об ро ан вх под ко ци ан вх ве че ци ан ду вт че щем ром тор ват че пер клю ряд вер и в ИЛИ вхо ду упр ча под

Чх То - Ти

TX-

где

и Т. С интервал времени интегрирования напряжения заданной величины, с; постоянная времени интегрирования, с;

интервал времени от момента начала интегрирования до момента времени, когда разность напряжений станет равна проинтегрированному значению напряжения заданной величины, с, величина емкости конденса- т ора цепи обратной связи усилителя заряда, ф, 2, Устройство для определения входного сопротивления усилителя заряда Содержащее усилитель заряда и резистор, подключенный к неинвертирующему входу этого усилителя и к общей шине, отличающееся тем, что в него дополнительно введены аналоговый инвертор, три конденсатора, семь аналоговых ключей, источник фиксированной ЭДС, дополнительный резистор, операционный

10

15

20

5

0

5

0

5

0

усилитель, компаратор, RS -триггер, четырехканальный формирователь временных интервалов, двухвходовый логический элемента ИЛИ и блок выделения заднего фронта liMnynbca, к выходу усилителя заряда подключены первый информационный вывод первого аналогового ключа и вход аналогового инвертора, вторые информационные выводы первого и второго аналоговых ключей подключены к первой обкладке первого конденсатора, выход инвертора подключен к первому инфор- мационному выводу третьего аналогового ключа, вторые информационные выводы третьего и четвертого аналоговых ключей соединены с первой обкладкой второго конденсатора, вторые обкладки первого и второго конденсаторов, первая обкладка третьего конденсатора, первый информационный вывод седьмого аналогового ключа и первый вывод дополнительного резистора подключены к инвертирующему входу операционного усилителя, к выходу которого подключены вторая обкладка третьего конденсатора, второй информационный вывод седьмого аналогового ключа и неинвертирующий вход компаратора, выход которого подключен к первому входу логического элемента ИЛИ, первые информационные выводы второго и четвертого аналоговых ключей, неинвертирующий вход операционного усилителя и инвертирующий вход компаратора подключены к общей шине, первые информа- ционные вьшоды пятого и шестого аналоговых ключей подключены к ду источника фиксированной ЭДС, их вторые информационные выводы подключены соответственно к неинвертирующему входу усилителя заряда и второму вьюоду дополнительного резистора, вход четырехканального формиро вателя временных интервалов подключен к пшие Пуск устройства, к первому выходу формирователя подключены вход Сброс усилителя за- ряда, входы управления второго, четвертого и седьмого аналоговых ключей и второй вход логического элемента ИЛИ, выход которого соединен с R - входом RS -триггера, к второму выходу формирователя подключен вход управления первого аналогового ключа, к третьему выходу формирователя подключены входы управления третье9120506010

го и пятого аналоговьгх ключей, а к логового ключа и входблока выделения четвертому выходу формирователя под- заднего фронта импульса,выход которо- ключены вход управления шестого ана- го соединен с S-входом RS триггера,

фаа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электрометрический преобразователь заряда | 1986 |

|

SU1420537A1 |

| Электрометрический преобразователь заряда | 1984 |

|

SU1239610A1 |

| Преобразователь частоты в напряжение | 1988 |

|

SU1640821A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1499242A1 |

| Интегрирующий преобразовательНАпРяжЕНия B иНТЕРВАл ВРЕМЕНи | 1979 |

|

SU809560A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ В ПОСТОЯННОЕ НАПРЯЖЕНИЕ | 1990 |

|

RU2007028C1 |

| Интегратор с весовым усреднением сигналов | 1987 |

|

SU1583859A1 |

| Преобразователь угла поворота вала в длительность импульсов | 1987 |

|

SU1534755A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием напряжения в частоту | 1982 |

|

SU1102035A1 |

| Устройство для геоэлектроразведки | 1990 |

|

SU1777110A1 |

Изобретение касается измерения и контроля параметров измерительных преобразований малых токов и зарядов. Цель изобретения - повышение точности измерения - достигается путем устранения погрешностей измерения, обусловленных входными токами смещения и напряжением смещения нуля усилителя заряда (УЗ). Способ предусматривает дифференцирование вьсходного сигнала УЗ с помощью дифференцирующей цепи с заданной постоянной времени. Последующее интегрирование полученного сигнала формирует на выходе интегратора уровень напряжения, равный уровню помех на выходе УЗ при его работе в течение заданного интервала времени. При интегрировании выходных сигналов УЗ во втором временном интервале с помощью интегратора производится компенсация напряжения помехи. Выходной сигнал интегратора будет при этом пропорционален выходному напряжению УЗ. В описании изобретения приводятся функциональ- . ная схема устройства, реализующего данный способ, и временные диаграммы, поясняющие его работу. 2 с.п. ф-лы. 2 ил.

| Аналоговые интегральные схемы/Под ред | |||

| Дж.Коннели, М.: Itop, 1977, с | |||

| Деревянное стыковое скрепление | 1920 |

|

SU162A1 |

| Илюкович A.M | |||

| Техника электрометрии | |||

| М.:Энергия, 1976, с | |||

| ТКАЦКИЙ СТАНОК | 1920 |

|

SU300A1 |

Авторы

Даты

1986-01-15—Публикация

1984-05-30—Подача