1

Изобретение относится к измерительной технике и может быть использовано для измерения электрических величин в условиях высокого уровня сетевой .помехи.

Цель изобретения - повышение точности цифрового интегрирующего вольметра при сохранении высокой степен подавления сетевой помехи за счет иключения зависимости результата изм рения от параметров элементов интегрирующих цепей.

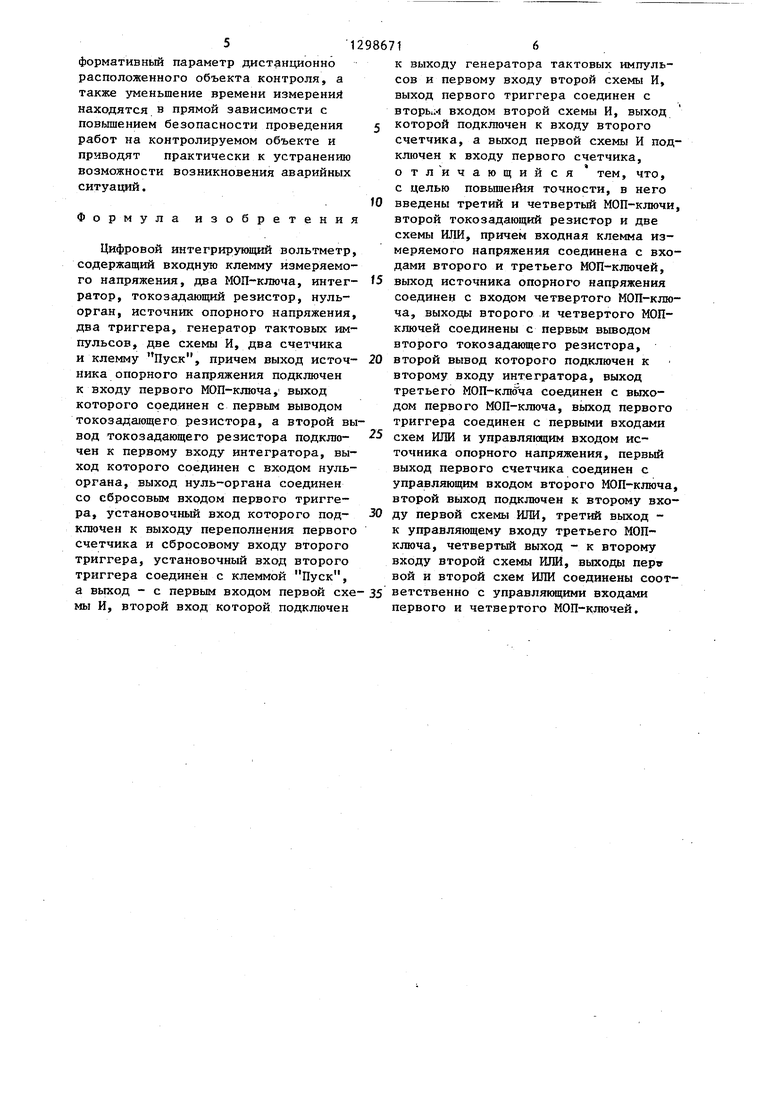

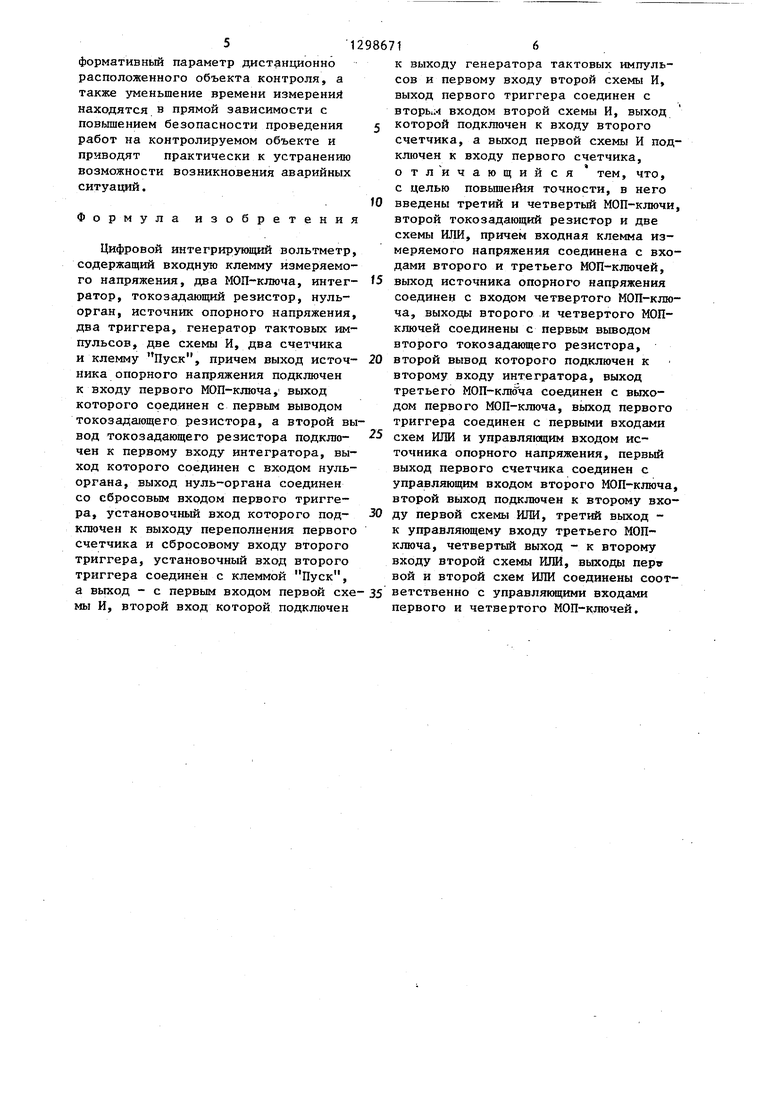

На фиг. 1 приведена функциональная схема цифрового интегрирующего вольтметра; на фиг. 2 - временные диаграммы, поясняющие работу вольтметра.

На диаграммах (фиг. 2) показаны сетевое напряжение (а), весовая функция, реализуемая вольтметром (8 напряжения на выходе интегратора при измерении нулевого (I), положительного (II) и отрицательного (III напряжений (6), временной интервал, пропорциональный положительному измеряемому напряжению (г), временной интервал, пропорциональный отрицательному измеряемому напряжению (j)

Цифровой интегрирующий вольтметр (фиг. 1) содержит входную клемму 1 измеряемого напряжения U, МОП-ключи 2-5, токозадающие резисторы 6 и 7, интегратор (например, на операционном усилителе 8 и конденсаторе 9 обратной связи), нуль-орган 10, источник 11 опорного напряжения (Uj,), триггеры 12 и 13, генератор 14 тактовых импульсов, схемы И 15 и 16, счетчики 17 и 18, схемы ИЛИ 19 и 20 Вход1|; клемма 1 измеряемого напряжения U соединена с входами МОП-ключей 2 и 4, а выход источника 11 опоного напряжения подключен к входам МОП-ключей 3 и 3, выходы МОП-ключей 2 и 5 соединены с первым выводом . токозадающего резистора 6, а выходы МОП-ключей 3 и 4 - с первым выводом токозадающего резистора 7, вторые вьшоды токозадающих резисторов 6 и подключены к входам интегратора, выход интегратора соединен с входом нуль-органа 10, выход которого подключен к сбросовому входу триггера

13, установочный вход последнего сое- сг вдвое по сравнению с .первым интервалом в случае равенства сопротивЛен1Й резисторов Rg и R. Здесь Rg, R, C,j - значения сопротивлений и ти соответственно резисторов 6 и / и

динен с выходом переполнения счетчика 17 и сбросовым входом триггера 12, установочный вход которого под-, ключей к клемме Пуск, выход тригге 7емкос7

ра

12 соединен с первым входом схемы И 15, второй вход которой соединен с выходом генератора 14 тактовых им- , пульсов и первым входом схемы И 16,

второй вход которой подключен к выходу триггера 13, первым входам схем ИЛИ 19 и 20 и управляющему входу источника 11 опорного напряжения, выходы схем И 15 и 16 соединены соответственно с входами счетчиков 17 и 18, первьй выход счетчика 17 соединен с управляющим входом МОП-ключа 2, второй выход - с вторым входом схем ИЛИ 19, третий выход - с управляющим

входом МОП-ключа 4, четвертый выход - с .вторым входом схемы ИЛИ 20, выходы схем ИЛИ 19 и 20 подключены соответственно к управляющим входам МОП-ключей 3 и 5.

Цифровой интегрирующий вольтметр работает по методу двухтактного интегрирования со смещенным нулем, модифицированного введением ступенчатой весовой функции. Причем время

первого (прямого) такта интегрирования составляет 3/2 периода Т сетевого напряжения.

0

5

0

Изм грение начинается с приходом сигнала Пуск, который опрокидывает триггер 12,. Выход последнего открывает схему И 15, через которую на вход счетчика 17 поступают тактовые импульсы генератора 14. С приходом первого тактового импульса на первом и втором выходах счетчика 17 появляется единичный уровень, кото- рьй приводит к замыканию МОП-ключей 2 и 3, Такое состояние поддерживается на протяжении временного интервала О-Т/2 (фиг. 2). В этом интервале происходит интегрирование измеряемого напряжения с постоянной времени интегрирования, равной ,, и опор- 5 него напряжения с постоянной - ,. Во временном интервале Т/2 - Т счетчик 17 устанавливает единичные уровни на своих первом и третьем выхода, что приводит к замыканию МОП- ключей 2 и 4. В этом интервале осуществляется интегрирование измеряемого напряжения с постоянной времени (Rg 11 R7)Cq, т.е. с постоянной времени интегрирования, уменьшенной

0

тервавЛен1ЙR, и / и

7 емкос7

конденсатора 9, Во временном интервале Т - ЗТ/2 счетчик 17 устанавливает единимные уровни на своих третьем и четвертом выходах, замыкаются МОП-ключи 4 и 5. Это приводит к ин- тегрированию измеряемого напряжения с постоянной времени RvCg и опорного ;Напряжения с постоянной RgC. В момент времени, равный ЗТ/2, происходит переполнение счетчика. На его пер- вом - четвертом выходах устанавливается нулевые уровни напряжения, а на выходе переполнения появляется пусковой перепад, опрокидывающий триггер 13 и возвращающий в исходное состояние триггер 12. Возврат триггера 12 в исходное состояние прекращает подачу тактовых импульсов на ;счетчик 17, Выходной сигнал триггера 13 переключает полярность ис- точника опорного напряжения на противоположную, замыкает МОП-ключи 3 и 5 и открывает схему И 16 для прохождения тактовых (счетных) импульсов на счетчик 18.

Начинается разряд интегратора с постоянной времени (Rg )| R)C. Разряд интегратора продолжается до достижения выходным напряжением интегратора исходного уровня. Этот момент фиксируется нуль-органом 10, который своим выходным сигналом возвращает триггер 13 в исходное состояние. Возврат триггера 13 приводит к размыканию МОП-ключей, переключению поляр- ности источника опорного напряжения и закрытию схемы И 16 для прохождения счетных импульсов на счетчик 18. Число, записанное в счетчике 18, пропорционально измеряемому напряжению. Счетчик 18 является реверсивным счетчиком, находящимся в вычитания от момента начала счета до достижения- своего нулевого состояния и

в режиме сложения после перехода че- рез нулевое состояние. Емкость счетчика выбрана из условия совпадения . момента возврата выходного напряжения интегратора в исходное состояние при нулевом измеряемом напряжении (фиг. 2в, I) с переходом счетчика в нулевое состояние. .Тогда при измерении положительных напряжений (фиг. 2в, II) возврат интегратора в исходное состояние наступает до пе- рехода счетчика в нулевое состояние, а при измерении отрицательных напряжений (фиг. 2в, III) - после этого

перехода. Временные интервалы, про- порциона.льные измеряемым положительному и отрицательному напряжениям, представлены соответственно на фиг. 2г, д.

Процесс интегрирующего преобразования, реализуемого предлагаемым вольтметром, для постоянного измеряемого напряжения без учета помехи представляется следующим выражением:

X г

Ud t +

d t +

IT

Ud t +

iMi)

где Tj( - время второго такта интегрирования (разряда интегратора) . Из выражения (1) непосредственно

следует

и и„ (-|2L-), (2)

т.е. измеряемое напряжение равно нулю при Т, равном Т/2, при

при .

Измеряемое напряжение U не зависит от погрешностей сопротивлений и емкости интегратора, так как последние не входят в выражение (2). На точность измерения не влияют и погрешности временных интервалов Tj( и Т, так как оба эти интервала определяются частотой одного генератора тактовых импульсов. Погрешност измерения напряжения зависит только от погрешности источника опорного напряжения U.

В вольтметре исключена зависимость результата измерения от параметров сопротивлений, используемых в схеме. Погрешность результата измерения зависит только от погрешности источника опорного напряжения. В предлагаемом вольтметре расчетньй коэффициент подавления сетевой помехи составляет 128 дБ, а время прямого интегрирования равно 1,5 периодам сетевого напряжения, что приводит к уменьшению времени измерения.

Повышение точности измерения напряжения, представляющего собой информативньш параметр дистанционно расположенного объекта контроля, а также уменьшение времени измерений находятся в прямой зависимости с повьшением безопасности проведения работ на контролируемом объекте и приводят практически к устранению возможности возникновения аварийных ситуа1Щй.

Формула изобретения

Цифровой интегрирующий вольтметр, содержащий входную клемму измеряемого напряжения, два МОП ключа, интегратор, токозадающий резистор, нуль- орган, источник опорного напряжения, два триггера, генератор тактовых импульсов, две схемы И, два счетчика и клемму Пуск, причем выход источника опорного напряжения подключен к входу первого МОП-ключа, выход которого соединен с первым выводом токозадающего резистора, а второй вывод токозадающего резистора подключен к первому входу интегратора, выход которого соединен с входом нуль- органа, выход нуль-органа соединен со сбросовым входом первого триггера, установочный вход которого подключен к выходу переполнения первого счетчика и сбросовому входу второго триггера, установочный вход второго триггера соединен с клеммой Пуск, а выход - с первым входом первой схемы И, второй вход которой подключен

к выходу генератора тактовых импульсов и первому входу второй схемы И, выход первого триггера соединен с вторым входом второй схемы И, выход

5 которой подключен к входу второго счетчика, а выход первой схемы И подключен к входу первого счетчика, отл и чающийся тем, что, с целью повыше1А1я точности, в него

0 введены третий и четвертый МОП-ключи, второй токозадающий резистор и две схемы ИЛИ, причем входная клемма измеряемого напряжения соединена с входами второго и третьего МОП-ключей,

f5 выход источника опорного напряжения соединен с входом четвертого МОП-ключа, выходы второго и четвертого МОП- ключей соединены с первым вьтодом второго токозадакнцего резистора,

0 второй вывод которого подключен к второму входу интегратора, выход третьего МОП-ключа соединен с выходом первого МОП-ключа, выход первого триггера соединен с первыми входами

25 схем ИЛИ и управляющим входом источника опорного напряжения, первый выход Первого счетчика соединен с управляющим входом второго МОП-ключа, второй выход подключен к второму вхо-

30 ду первой схемы ИЛИ, третий выход - к управляющему входу третьего МОП- ключа, четвертый выход - к второму входу второй схемы ИЛИ, выходы nepw вой и второй схем ИЛИ соединены соот- 35 ветственно с управляющими входами первого и четвертого МОП-ключей.

a

/л /л

IK/

u

Составитель A. Морозов Редактор Н. Бобкова Техред Н.Глущенко Корректор Л. Пилипенко

Заказ 884/47 Тираж 731Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная-, 4

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегрирующий вольтметр | 1990 |

|

SU1798711A1 |

| Многоканальный цифроаналоговый преобразователь | 1984 |

|

SU1269269A1 |

| Цифровой измеритель активных сопротивлений | 1985 |

|

SU1308936A1 |

| СПОСОБ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2354955C1 |

| Цифровой омметр | 1973 |

|

SU454506A1 |

| Цифровой интегрирующий вольтметр | 1989 |

|

SU1698813A1 |

| Цифровой термометр | 1986 |

|

SU1404844A1 |

| СЧЕТЧИК ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2001 |

|

RU2190860C2 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Устройство для измерения сопротивления | 1980 |

|

SU938198A1 |

Изобретение относится к измерительной технике и может быть использовано для измерения электрических величин в условиях высокого уровня сетевой помехи. Целью изобретения является повышение точности цифрового интегрирующего вольтметра при сохранении высокой степени .подавления сетевой помехи за счет исключения зависимости результата измерения от параметров элементов интегрирую- .. щих цепей. Устройство содержит входную клемму 1 измеряемого напряжения и, МОП-ключи 2 и 3, интегратор (например, на операДионном усилителе 8, конденсаторе 9) нуль-орган 10, источник 11 опорного напряжения, триггеры 12 и 13, генератор 14 тактовых импульсов, схемы И 15 и 16, счетчики 17 и 18, токозадающий резистор 6. Для достижения поставленной цели в устройство введены МОП-ключи 4 и 5, токозадающий резистор 7, схемы ИЛИ 19, 20 и образованы новые функциональные связи. В вольтметре исключена зависимость результата измерения от параметров сопротивлений, используемых в схеме. Погрешность результата измерения зависит только от погрешности источника опорного напряжения. 2 ил. i (Л С I(u; 2 о to 00 05 -4 Фиг.

Авторы

Даты

1987-03-23—Публикация

1985-07-17—Подача