СЛ

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегрирующий вольтметр | 1978 |

|

SU789839A1 |

| Интегрирующий аналого-цифровой преобразователь | 1984 |

|

SU1314457A1 |

| Цифровой вольтметр с автоматическим выбором пределов измерения | 1990 |

|

SU1734032A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU949807A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1444950A1 |

| Способ аналого-цифрового преобразования с весовым интегрированием и устройство для его реализации | 1981 |

|

SU953722A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU790286A1 |

| Аналого-цифровой преобразователь | 1976 |

|

SU652704A1 |

| Цифровой вольтметр среднеквадратического значения переменного напряжения | 1988 |

|

SU1652933A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

Изобретение относится к технике электроизмерений. Цель изобретения -повышение точности. Вольтметр содержит коммутатор 1, источник 2 опорного напряжения, источник3 компенсирующего напряжения, аналого-цифровой преобразователь 4, дешифратор 5, интегратор 6, компаратор 7, блок 8 логики, запоминающий блок 9, счетчик 10, матрицу 11 резисторов, генератор 12, цифровой счетчик 13,отсчетный блок 14, логический коммутатор 15. 4 ил.

фигЛ

ск ю

00 00

со

Изобретение относится к электроизмерительной технике и может быть использовано для построения цифровых измерительных приборов или информационно-измерительных систем.

Цель изобретения - повышение точности измерений.

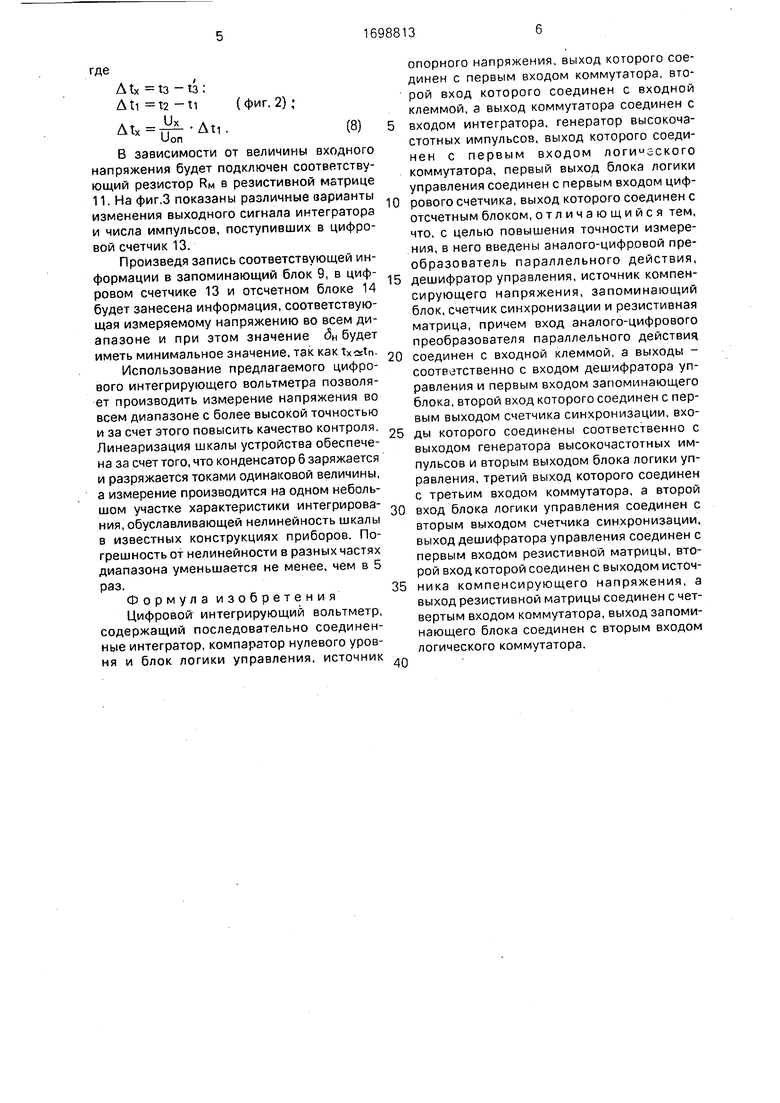

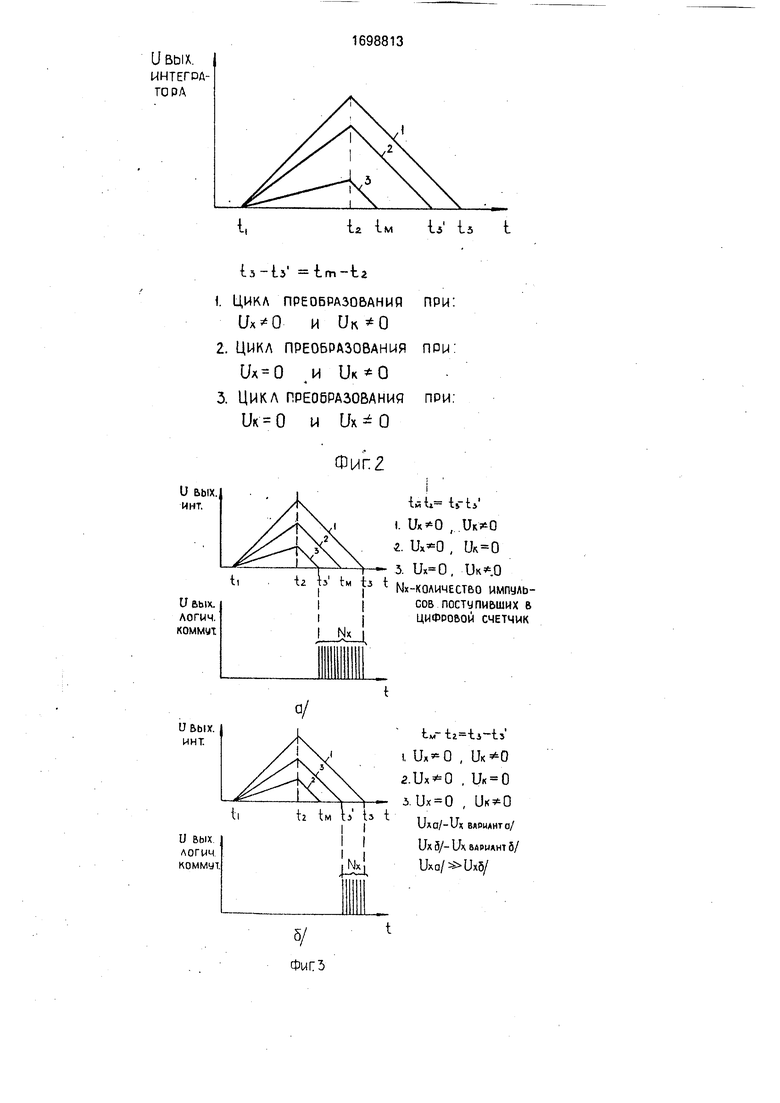

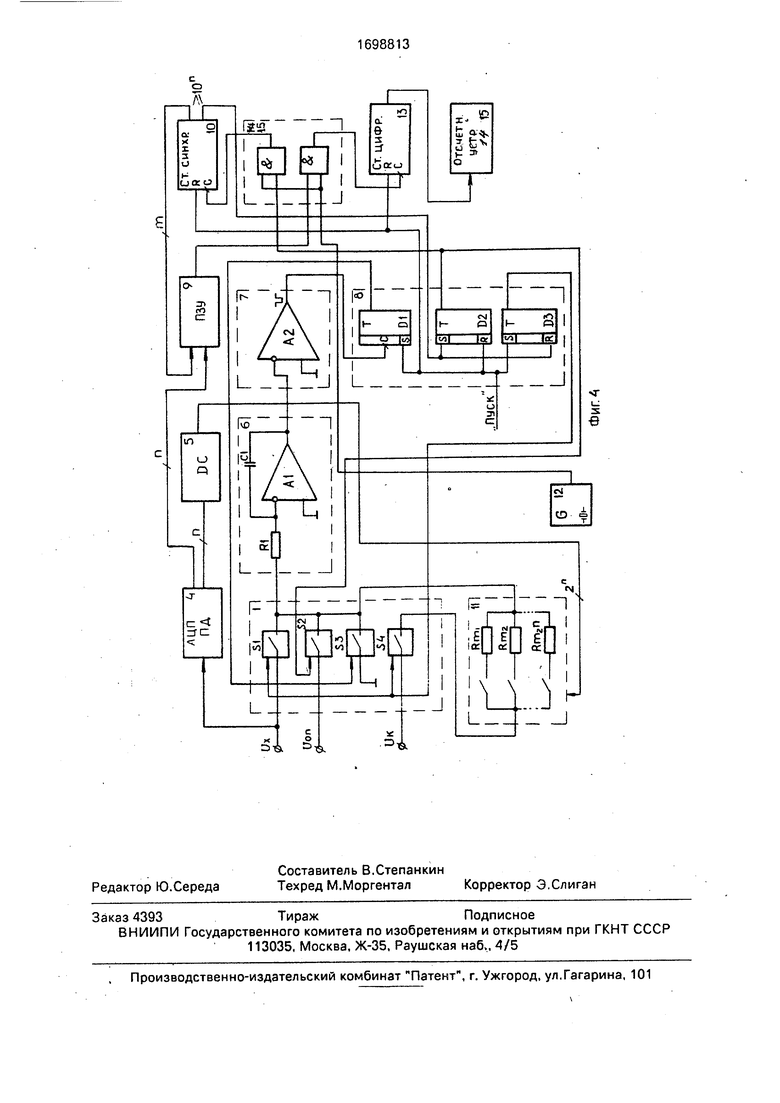

На фиг. 1 представлена блок-схема цифрового интегрирующего вольтметра; на фиг.2 и 3 - временные диаграммы работы вольтметра; на фиг.4 - пример выполнения устройства.

Цифровой интегрирующий вольтметр (фиг.1) содержит коммутатор 1, к первому входу которого подключен выход источника 2 опорного напряжения, источник3 компенсирующего напряжения, аналого-цифровой преобразователь 4 параллельного действия, вход которого подключен к второму входу коммутатора 1, а выход подсоединен к входу дешифратора 5 управления, а к выходу коммутатора последовательно подсоединены интегратор 6, компаратор 7 нулевого уровня и блок 8 логики управления, а также запоминающий блок 9, своим входом подсоединенный к аналого-цифровому преобразователю 4 параллельного действия, а выходом - к входу счетчика 10 синхронизации, причем выход дешифратора 5 управления подсоединен к входу мат- рицы резисторов 11, а ее выход подключен к третьему входу коммутатора 1, генератор 12 высокочастотных импульсов, цифровой счетчик 13, выход которого подсоединен к отсчетному блоку 14, а вход - к первому выходу логического коммутатора 15, второй выход которого подсоединен к счетчику 10 синхронизации,

Устройство работает следующим образом.

В исходном состоянии ключ ЗЗкоммута- тора 1 замкнут, остальные разомкнуты, а счетчики 10 и 13 находятся в нулевом состоянии.

В первом такте измерения после прихо- да сигнала Пуск замыкают ключи S1 и S4 размыкают ключ S3 коммутатора 1. Одновременно с этим аналого-цифровой преобразователь 4 параллельного действия производит приближенную оценку величи- ны входного сигнала Ux и выдает результат измерения на дешифратор 5 управления, который, в свою очередь, включает соответствующий ключ резистивной матрицы 11. В результате этого сигнал на выходе интегра- тора 6 имеет величину иВых (tz) в интервале ti-t2:

U8b,x(t2) - Uxdt- l:- Ukdt.

(1)

где ti- постоянная интегратора б в первом такте интегрирования:

Ci , Ri и Ci - элементы интеграторов 6;

Гмх - постоянная интегратора,определяемая величиной резистора RMx, подключенного дешифратором 5 управления после определения величины Ux аналого-цифровым преобразователем 4:

мх RMX Ci ; Ux - величина измеряемого напряжения;

UK - величина компенсирующего напряжения.

Количество резисторов RM в резистивной матрице 11 определяется требованиями к величине погрешности от нелинейности интеграторов 6, в соответствии с которой вся шкала диапазона разбивается на п интервалов. Таким образом в диапазоне элемента дискретизации выходное напряжение определяется из

Uebix (t2 ) JJ5 Ux dt Const (2)

Во втором такте т.2-хзключи S1 и S4 размыкаются, а ключ 82замыкаетЬя. Выходной сигнал изменяется на выходе интегратора ивых (ts) (фиг.2):

UBb,x(t3) - /gUondt(3)

где Uon - величина опорного компенсирующего напряжения.

Допустим, что напряжение , тогда в конце второго такта интегрирования (фиг.2)

- Uk dt+w43u-dt °-

где t3 - момент времени при соответствующий концу второго такта, но:

i

т Л UK dt +сопзг,тадэи1 / 3 UOT dt

Гм

t1

Г1 Jt2

Тмс

( rt2

/t1 Ukdt.

©

Тогда во втором такте, произведя задержку при отсчете числа импульсов в цифровой счетчик 13 на интервале времени с помощью логического коммутатора 15 в цифровом счетчике 13 будет записано число импульсов, соответствующее интервалу t3 - тз (фиг.2)

- U d -i-.d +

+ 4 Uon dt + т7 Јз Uon dt 0 ;(6) Uon -4г и 4 АЧ ()

Atx гз -ts;

Atl t2 tl

Ux

(Фиг. 2) ;

Atx

U

on

Ati.

В зависимости от величины входного напряжения будет подключен соответствующий резистор RM в резистивной матрице 11. На фиг.З показаны различные варианты изменения выходного сигнала интегратора и числа импульсов, поступивших в цифровой счетчик 13.

Произведя запись соответствующей информации в запоминающий блок 9, в цифровом счетчике 13 и отсчетном блоке 14 будет занесена информация, соответствующая измеряемому напряжению во всем диапазоне и при этом значение 5Н будет иметь минимальное значение, так как .

Использование предлагаемого цифрового интегрирующего вольтметра позволяет производить измерение напряжения во всем диапазоне с более высокой точностью и за счет этого повысить качество контроля. Линеаризация шкалы устройства обеспечена за счет того, что конденсатор 6 заряжается и разряжается токами одинаковой величины, а измерение производится на одном небольшом участке характеристики интегрирования, обуславливающей нелинейность шкалы в известных конструкциях приборов. Погрешность от нелинейности в разных частях диапазона уменьшается не менее, чем в 5 раз.

Формула изобретения

Цифровой интегрирующий вольтметр, содержащий последовательно соединенные интегратор, компаратор нулевого уровня и блок логики управления, источник

опорного напряжения, выход которого соединен с первым входом коммутатора, второй вход которого соединен с входной клеммой, а выход коммутатора соединен с 5 входом интегратора, генератор высокочастотных импульсов, выход которого соединен с первым входом логического коммутатора, первый выход блока логики управления соединен с первым входом циф10 рового счетчика, выход которого соединен с отсчетным блоком, отличающийся тем, что, с целью повышения точности измерения, в него введены аналого-цифровой преобразователь параллельного действия,

15 дешифратор управления, источник компенсирующего напряжения, запоминающий блок, счетчик синхронизации и резистивная матрица, причем вход аналого-цифрового преобразователя параллельного действия

20 соединен с входной клеммой, а выходы - соответственно с входом дешифратора управления и первым входом запоминающего блока, второй вход которого соединен с первым выходом счетчика синхронизации, вхо25 ды которого соединены соответственно с выходом генератора высокочастотных импульсов и вторым выходом блока логики управления, третий выход которого соединен с третьим входом коммутатора, а второй

30 вход блока логики управления соединен с вторым выходом счетчика синхронизации, выход дешифратора управления соединен с первым входом резистивной матрицы, второй вход которой соединен с выходом источ35 ника компенсирующего напряжения, а выход резистивной матрицы соединен с четвертым входом коммутатора, выход запоминающего блока соединен с вторым входом логического коммутатора.

40

U вы

ИНТЕГРАТОРА

I. I

Ь-1з tm-ta

И UK О

.И

Ш 0 и

Фиг2

U Е.ЫХ.

инт.

U вых. логкч КОММУТ

и вых. инт

{,

t2 tM U t

I I

5/ ФыгЗ

M

Ь1 is t

. , г. , 3. , Ш.0

Nx-КОЛИЧЕСТБО ИМПУЛЬСОВ ПОСТУПИВШИХ В ЦИФРОВОЙ СЧЕТЧИК

tM-b ti-b i ,

5 Ux 0 ,

UxO/-Un BAPUAHTO/

Ux S/- Ux ВАРИАНТ 5/

| Шляндин В.М | |||

| Цифровые измерительные устройства | |||

| М.: Высшая школа, 1971, с | |||

| Приспособление для обрезывания караваев теста | 1921 |

|

SU317A1 |

| Цифровой интегрирующий вольтметр | 1978 |

|

SU789839A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-12-15—Публикация

1989-05-23—Подача