I

Изобретение относится к автоматике и вычислительной технике и может быть использовано в многоканальных измерительных цифроаналоговых системах автоматики и вычислительной техники.

Цель изобретения - расширение функциональных возможностей за счет многоканальной обработки информации.

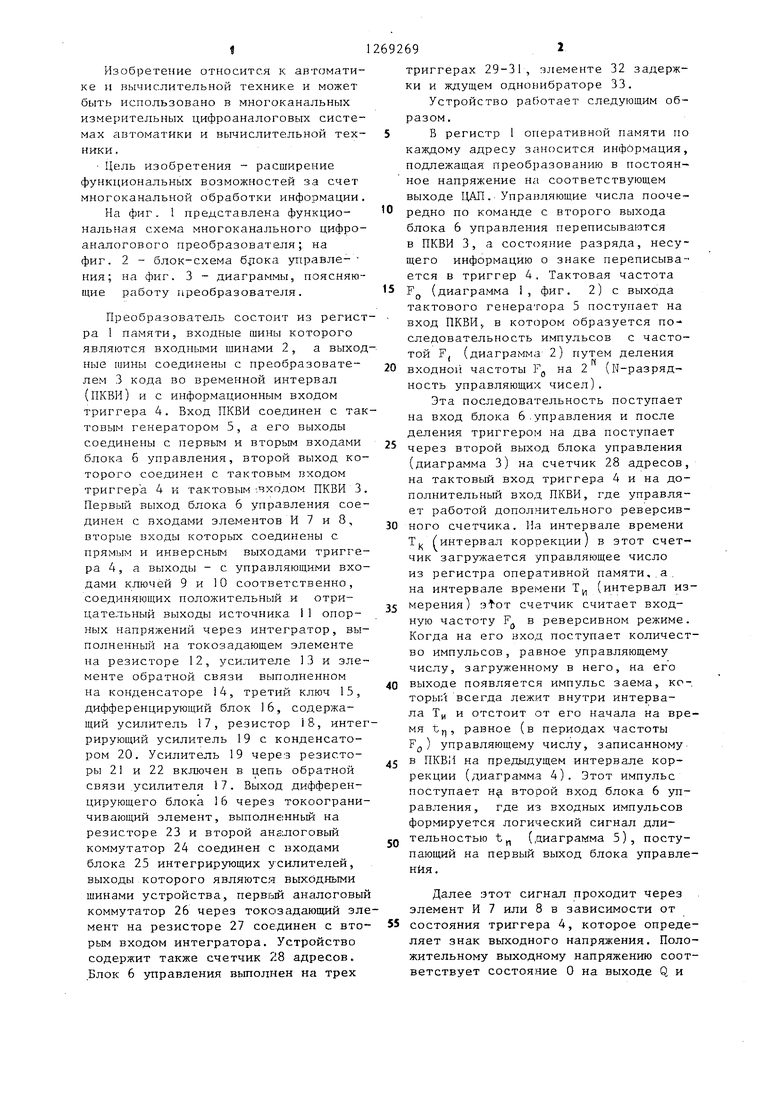

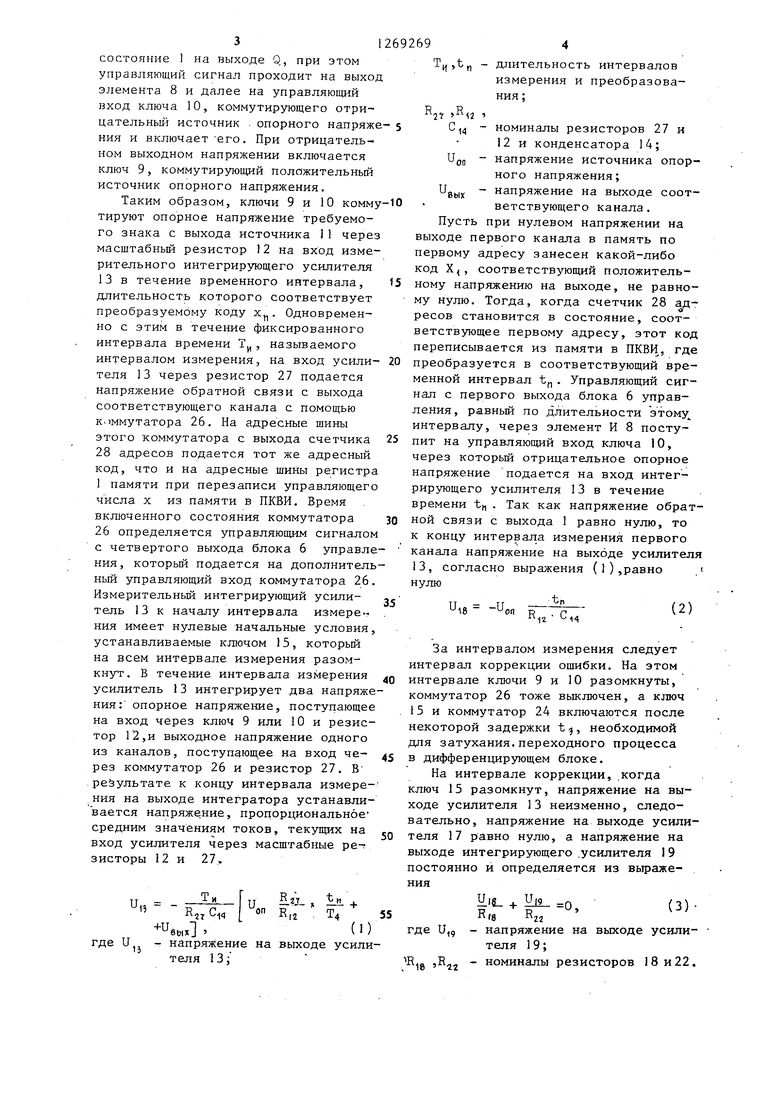

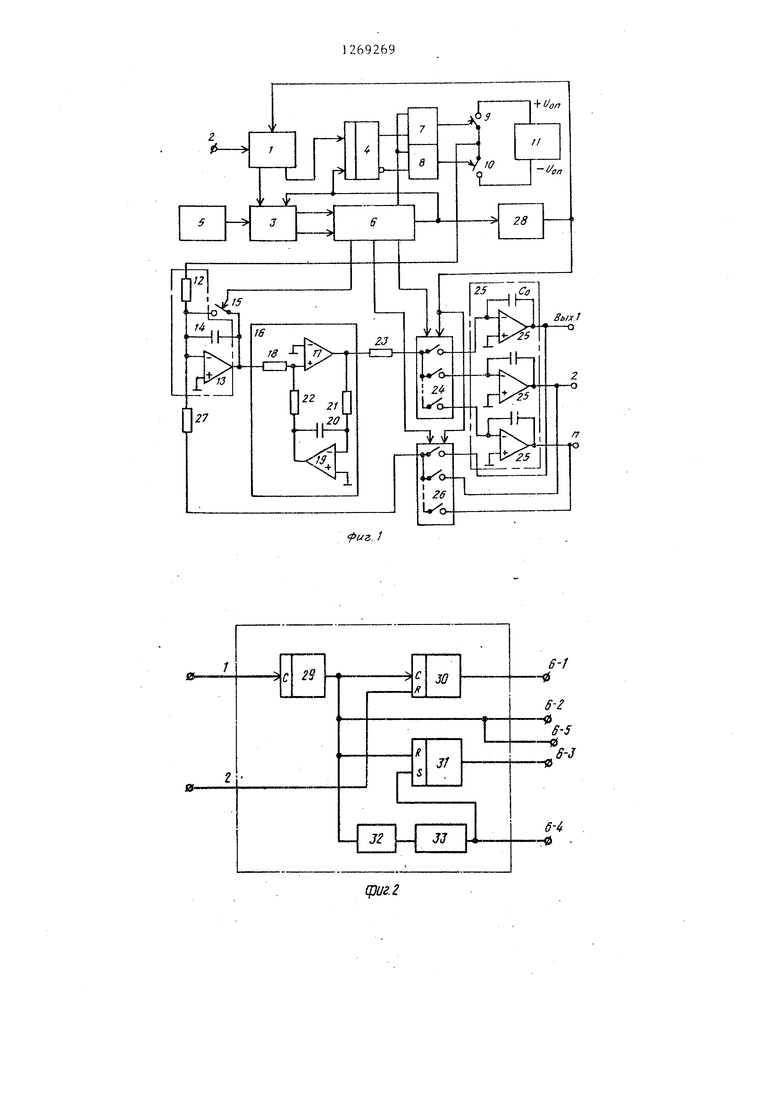

На фиг. I представлена функциональная схема многоканального цифроаналогового преобразователя; на фиг. 2 - блок-схема брока управления; на фиг. 3 - диаграммы, поясняющие работу преобразователя.

Преобразователь состоит из регистра 1 памяти, входные шины которого являются входными шинами 2, а выходные тины соединены с преобразователем 3 кода во временной интервал (ПКВИ) и с информационным входом триггера 4. Вход ПКВИ соединен с тактовым генератором 5, а его выходы соединены с первым и вторым входами блока б управления, второй выход которого соединен с тактовым входом триггера А и тактовым входом ПКВИ 3. Первый выход блока 6 управления соединен с входами элементов И 7 и 8, вторые входы которых соединены с прямым и инверсным выходами триггера 4, а выходы - с управляющими входами ключей 9 и 10 соответственно, соединяющих положительный и отрицательный выходы источника 11 опорных напряжений через интегратор, выполненный на токозадающем элементе на резисторе 12, усилителе 13 и элементе обратной связи выполненном на конденсаторе 14, третий ключ 15, дифференцирующий блок 16, содержащий усилитель 17, резистор 18, интегрирующий усилитель 19 с конденсатором 20. Усилитель 19 через резисторы 21 и 22 включен в цепь обратной связи .усилителя 17. Выход дифференцирующего блока 16 через токоограничивающий элемент, выполне:нньй на резисторе 23 и второй аналоговый коммутатор 24 соединен с входами блока 25 интегрирующих усилителей, выходы которого являются выходньми щинами устройства, первьй аналоговый коммутатор 26 через токозадающий элемент на резисторе 27 соединен с вторым входом интегратора. Устройство содержит также счетчик 28 адресов. Блок 6 управления вьтолнен на трех

692692

триггерах 29-31, элементе 32 задержки и ждущем одновибраторе 33.

Устройство работает следующим образом.

5 В регистр 1 оперативной памяти по каждому адресу за.носится инфбрмация, подлежащая преобразованию в постоянное напряжение на соответствующем выходе ЦАП. Управляющие числа поочередно по команде с второго выхода

блока 6 управления переписываются в ПКВИ 3, а состояние разряда, несущего информацию о знаке переписывается в триггер 4, Тактовая частота

FJJ (диаграмма 1, фиг. 2) с выхода тактового генератора 5 поступает на вход ПКВИ, в котором образуется последовательность импульсов с частотой F, (диаграмма 2) путем деления

ВХОДНО1 частоты Fg на 2 (N-разрядность управляющих чисел).

Эта последовательность поступает на вход блока 6.управления и после деления триггером на два поступает

через второй выход блока управления (диаграмма 3) на счетчик 28 адресов, на тактовый вход триггера 4 и на дополнительный вход ПКВИ, где управляет работой дополнительного реверсивного счетчика. Па интервале времени Т( интервал коррекции) в этот счетчик загружается управляющее число из регистра оперативной памяти,.а. на интервале времени Т у, (интервал измерения) счетчик считает входную частоту F в реверсивном режиме. Когда на его вход поступает количество импульсов, равное управляющему числу, загруженному в него, на его

выходе появляется импульс заема, которьп всегда лежит внутри интервала T, и отстоит от его начала на время tf, равное (в периодах частоты FO) управляющему числу, записанному

в ПКВИ на предыдущем интервале коррекции (диаграмма 4). Этот импульс поступает н второй вход блока 6 управления , где из входных импульсов формируется логический сигнал длительностью t (диаграмма 5), поступающий на первый выход блока управления.

Далее этот сигнал проходит через элемент И 7 или 8 в зависимости от состояния триггера 4, которое определяет знак выходного напряжения. Положительному выходному напряжению соответствует состояние О на выходе Q и состояние 1 на выходе Q, при этом управляющий сигнал проходит на выход элемента 8 и далее на управляющий вход ключа 10, коммутирующего отрицательньш источник . опорного напряж НИН и включает его. При отрицательном выходном напряжении включается ключ 9, коммутирующий положительный источник опорного напряжения. Таким образом, ключи 9 и 10 комму тируют опорное напряжение требуемого знака с выхода источника 11 через масштабньй резистор 12 на вход измерительного интегрирующего усилителя 13 в течение временного интервала, длительность которого соответствует преобразуемому коду х. Одновременно с этим в течение фиксированного интервала времени Т, , называемого интервалом измерения, на вход усилителя 13 через резистор 27 подается напряжение обратной связи с выхода соответствующего канала с помощью коммутатора 26, На адресные шины этого коммутатора с выхода счетчика 28 адресов подается тот же адресный код, что и на адресные шины регистра 1 памяти при перезаписи управляющего числа X из памяти в ПКВИ, Время включенного состояния коммутатора 26 определяется управляющим сигналом с четвертого выхода блока 6 управле ния, который подается на дополнитель ный управляющий вход коммутатора 26 Измерительный интегрирующий усилитель 13 к началу интервала измере-г ния имеет нулевые начальные условия устанавливаемые ключом 15, который на всем интервале измерения разомкнут. В течение интервала измерения усилитель 13 интегрирует два напряже ния: опорное напряжение, поступающее на вход через ключ 9 или 10 и резистор 12,и выходное напряжение одного из каналов, поступающее на вход через коммутатор 26 и резистор 27. В .результате к концу интервала измере.ния на выходе интегратора устанавливается напряжение, процорциональное средним значениям токов, текущих на вход усилителя через масштабные ре- зисторы 12 и 27, „ С,, I оп К,г и-з - - I +Ue,,. , - напряжение на выходе усили теля 13 j 694 T,t - длительность интервалов измерения и преобразования ; р р 14 номиналы резисторов 27 и 12 и конденсатора 14; UQI, - напряжение источника опорного напряжения; вых напряжение на выходе соответствующего канала, Пусть при нулевом напряжении на выходе первого канала в память по первому адресу занесен какой-либо код X, соответствующий положительному напряжению на выходе, не равному нулю. Тогда, когда счетчик 28 адресов становится в состояние, соответствующее первому адресу, этот код переписывается из памяти в ПКВИ, где преобразуется в соответствующий временной интервал t( . Управляющий сигнал с первого выхода блока 6 управления, равный по длительности этому интервалу, через элемент И 8 поступит на управляющий вход ключа 10, через которьш отрицательное опорное напряжение подается на вход интегрирующего усилителя 13 в течение времени tj, , Так как напряжение обратной связи с выхода 1 равно нулю, то к концу интервала измерения первого канала напряжение на выходе усилителя 13, согласно выражения (1),равно . нулю U,R -и„ М8 оп R , р За интервалом измерения следует интервал коррекции ощибки. На этом интервале ключи 9 и 10 разомкнуты, коммутатор 26 тоже выключен, а ключ 15 и коммутатор 24 включаются после некоторой задержки t , необходимой для затухания,переходного процесса в дифференцирующем блоке, На интервале коррекции, .когда ключ 15 разомкнут, напряжение на выходе усилителя 13 неизменно, следовательно, напряжение на выходе усилителя 17 равно нулю, а напряжение на выходе интегрирующего .усилителя 19 постоянно и определяется из вьфаженияUit. + , (3) -напряжение на выходе усилителя 19; -номиналы резисторов 18 и 22, «18 Если принять R|g Rj, , то тогда и,, +и„ 0.(4) При замыкании ключа 15 на выходе усилителя 13 устанавливается нулевое напряжение, т.е. напряжение изменяется на величину, равную исходному значению, взятую с обратным знаком и iU,, -и„ и„. К,г 14 Это приращение вводит усилитель 7 в ограничение, который находится в этом состоянии до тех пор, пока интегрирующий усилитель 19j интегрируя выходное напряжение усилителя 17 не скомпенсирует это изменение равным ему, но противоположным по знаку изменением своего выходного напряжения. Изменение выходного напряжения усилителя 19 с одной стороны из выражения (5) равно UU,, -uU,, --и„п R,,j С 4 С другой стороны это прираш;ение, как результат интегрирования выходно интервале Т.. го напряжения равно - / и, (t) dt. (7 .и,, - --Но выходное напряжение усилителя I7 через резистор 23 и замкнутый ключ коммутатора 24 поступает на вх интегрирзлощего усилителя первого ка нала. Его выходное напряжение тоже изменится на величину. и,- (t)dt, (8 2 0 . емкость конденсатора выход ных интеграторов. Решая совместно выражения (7) и (8), получим lU,p Если постоянные времени и RJ, С„ равны между собой, а по С,4 взять равной времен стоянную измерения Т , то выходной усилитель первого канала, интегрируя на интервале коррекции ошибки выходное напряжение усилителя 17, изменяет свое напряжение на величину - -П ли,,„,-Лп т и ° - управляющее число, записанное в первый канал; -максимальное значение управ ляющих чисел. 694 Из этого ВЕлраження видно, что осле первого измерения ошибки и ее оррекции напряжение на выходе первоо канала становится пропорциональьЕм коду X, , записанному в регистр перативной памяти по первому адресу, с точностью, до которой выполняются еречисленные требования на постоянные времени. На следующем интервале измерения устройство измеряет соответствие выходного напряжения во втором канале кода, записанного по второму адресу., и корректирует его на интервале коррекции и т.д. Аналогично измеряются и корректируются все п каналов и затем цикл повторяется снова. Сигнал ошибки, измеренный интегрирующим усилителем, равен нулю, если в уравнении (l) выражение в скобках равно нулю. Тогда - j.( X-iL т т -Uon При нулевом сигнале ошибки корректирующий сигнал на интервале коррекции равен HyjDo, так как напряжение на выходе усилителя 13 не имеет скачка при закорачивании ключа 15. Следовательно, выходное напряжение корректируемого канала остается неизменным. Для того, чтобы процесс установления -выходной величины заканчивался за один интервал коррекции, необходимо, чтобы приращение выходной величины из выражения (9) соответствовало выходной величине при нулевой в этом случае выходная величина устанавливается в соответствии с входным кодом в каждом канале за первый интервал коррекции с точностью, с которой .вьтолняется последнее равенство, а также равенства г т R/a (4 J-и

Формула изобретения

1. Многоканальный цифроаналоговый преобразователь, содержащий источник опорных напряжений, первый и второй выходы которого соединены с соответствующими .информационными входами первого и второго ключей, управляющие входь которых соединены с выходами соответственно первого и второго элементов И,первые входы которых объединены и подключены к первому выходу блока управления, а вторые входы соединены соответственно с прямым и инверсным выходами триггера информационный вход триггера соедине со знаковыми разрядом регистра памяти, информационные выходы которого подключены к информационным входам преобразователей кода во временной интервал, информационные входы регистра памяти являются входными шинами, второй выход блока управления подключен к синхронизирующему входу преобразователя кода во временной интервал, выход тактового генератора подключен к тактовому входу преобразователя кода во временной интервал, а информационные выходы первого и второго ключей объединены и подключены к первому входу интегратора, третий ключ, отличающийся тем, что, с целью расширения функЦиональных возможностей за счет многоканальной обработки информации, в него введены дифференцирующий блок токоограничивающий элемент, два аналоговых коммутатора, счетчик адресов и блок интегрирующих усилителей, выходы которого являются выходными шинами и подключены к соответствующим входам первого аналогового коммутатора, выход которого через токозадающий резистор подключен к второму

входу интегратора, выход которого подключен к информационному входу третьего ключа и к входу дифференцирующего блока, выход которого через токоогранивающий элемент подключен к информационному входу второго аналогового коммутатора, информационные выходы которого соединены с входами блока интегрирующих усилителей, а адресные входы объединены с адресными входами первого аналогового коммутатора и адресными входами регистра памяти и подключены к выходам счетчика адресов, вход которого объединен с тактирующим входом триггера и подключен к второму выходу блока управления, третий и четвертый выходы которого соединены с управляющими входами первого и второго аналоговых коммутаторов соответственно,

-ВХОДЫ соединены с выходами преобразователя кода во вpe eннoй интервал, а пятый выход - с управляющим входом третьего ключа, выход которого подключен к третьему входу интегратора. 2. Преобразователь по п. 1, о т личающийся тем, что -блок управления выполнен на трех тригге-. pax, элементе задержки и ждущем одновибраторе, выход которого подключен к S-входу первого триггера и является третьим выходом блока, четвертым выходом которого является выход первого триггера, R-вход которого объе- динен с входом элемента задержки, с входом второго триггера, подключен к выходу третьего триггера и является вторым и пятым выходами блока,

первым выходом которого является выход второго триггера, R-вход которого и С-вход первого триггера являются первыми входами блока, выход элемента за держки соединен с входом ждущего одновибратора.

Фие.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоканального интерполирования функций | 1986 |

|

SU1377878A1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Источник калиброванных напряжений | 1985 |

|

SU1283726A1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Измеритель временных интервалов | 1985 |

|

SU1307444A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Калибратор напряжения | 1984 |

|

SU1191892A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в многоканальных измерительных цифроаналоговьгх системах. Изобретение позволяет расширить функциональные возможности устройства, содержащего источник опорных напряжений, первый, второй . и третий ключи, первьш и второй элементы И, блок управления, триггер, регистр памяти, интегратор, преобрдзователь кода во временной интервал, за счет введения в него дифференцирующего блока, двух аналоговых коммутаторов, счетчика адресов, блока интегрирующих усилителей, токоограничивающего элемента. I з.п. ф-лы, а € 3 ил.

| Многоканальный цифроаналоговый преобразователь | 1981 |

|

SU995311A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3646545, кл | |||

| 340347 ST, 1972. | |||

Авторы

Даты

1986-11-07—Публикация

1984-10-11—Подача