лов. Тот или иной режим задается путем подачи разрешающего потенциала на соответствующие, управляющие входы 6, 16, 20, 25, 26 и 29 устройства. При вьтолненйи операции деления указанный потенциал подается на управляющие входы 6 и 20 (подготавливаются элементы И 19. 21 и элемент И-НЕ 4). За время, равное длительности меньшего временного интервала Т,, в счетчике 10 формируется код N Т,- fo , где fg - частота такто- вых импульсов (ТИ) генератора 1. После окончания этого временного интервала начинается заполнение реверсивного счетчика (РС) 8 тактовыми импульсами, проходящими на суммирующий вход PC - до момента времени, соответствующего достижению в PC кода N , что фиксируется схемой 9 сравнения, импульс с выхода которой, пройдя через элемент И 19, сбрасывает PC в нуль, и, пройдя через элементы ШМ 12, И 21 и ИЛИ 17, заносится в счетчик 22. Далее PC начинает заполняться вновь, срабатывает схема 9 и т.д. Процесс вычисления в данном режиме заканчивается в момент времени, соответствующий окончанию большего временного интервала Т. При этом в счетчике 22 образуется код, отображающий Е„ (, ) , При ыполнении операции умножения разреающий потенциал подается на управяющие входы 16 и 26 (подготавливаются элементы И 15, 24). За время Tj

. Изобретение относится к автоматике и вычислительной технике и может быть использовано в информационно-измерительных системах для выполнения арифметических операций под времяимпульс- ными сигналами.

Цель изобретения - увеличение быстродействия устройства в режиме сложения временных интервалов.

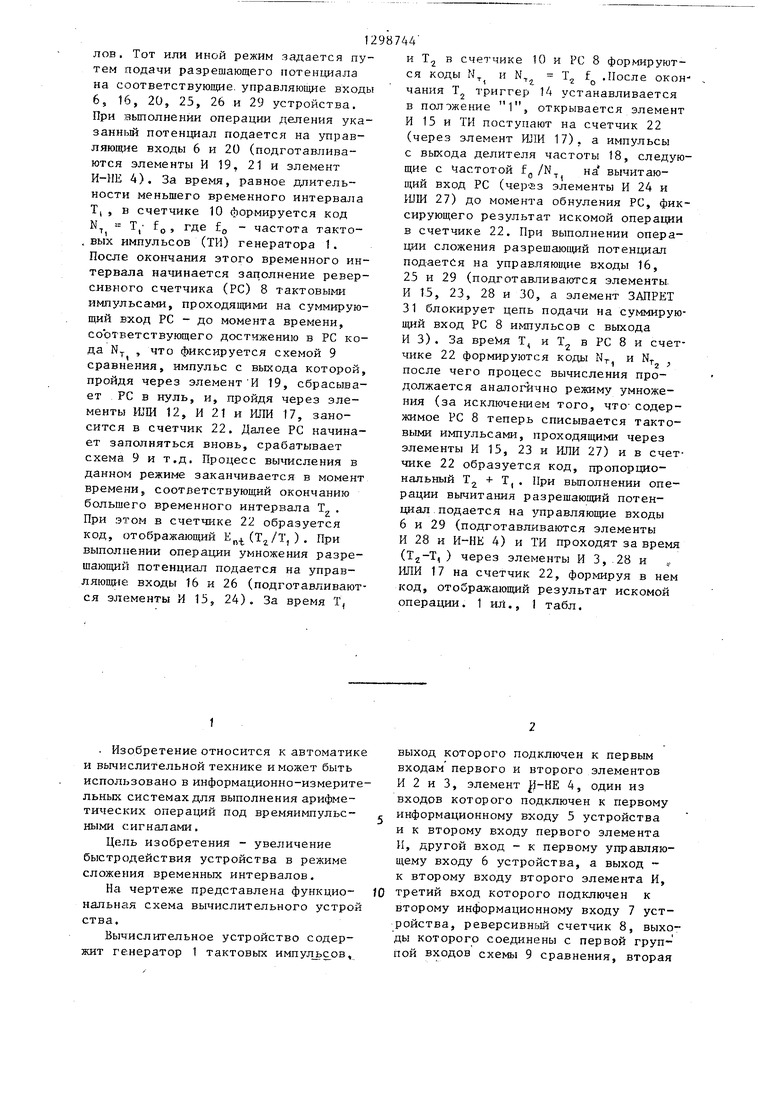

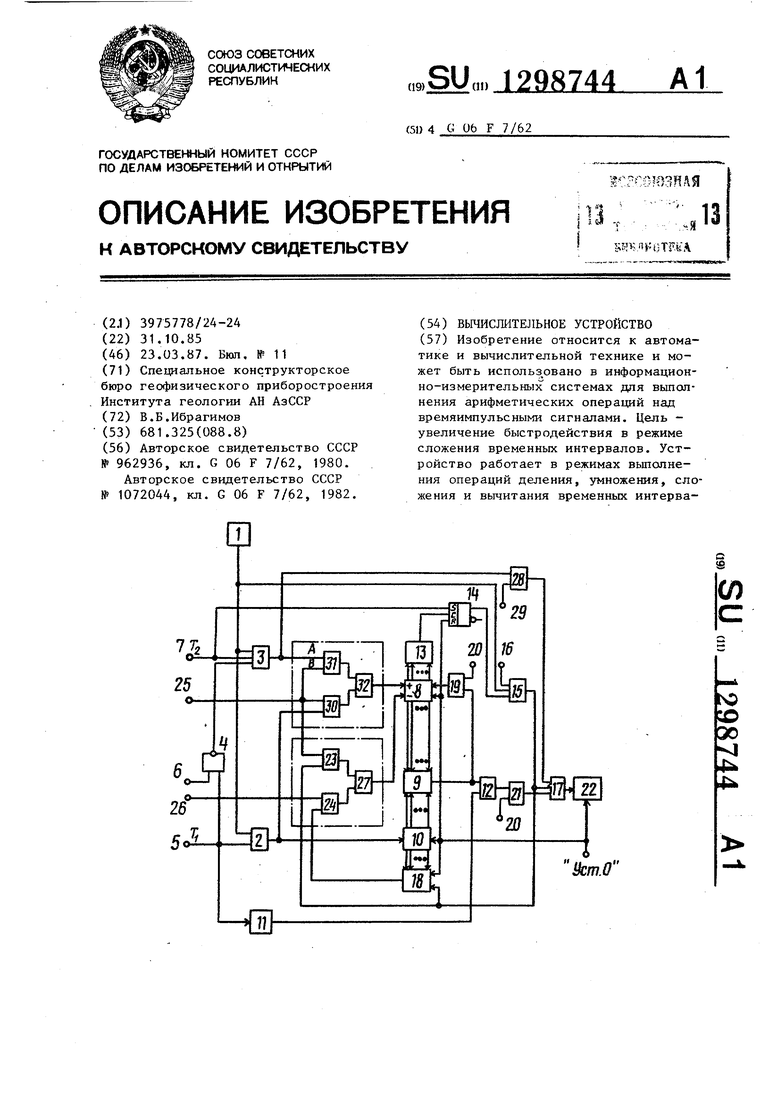

На чертеже представлена функцио- нальная схема вычислительного устрой ства.

Вычислительное устройство содержит генератор 1 тактовых импульс ов.

и Т в счетчике 10 и PC 8 формируются коды N. и NT. Т f .После окон чания Т триггер 14 устанавливается в положение 1, открывается элемент И 15 и ТИ поступают на счетчик 22 (через элемент ИЛИ 17), а импульсы с выхода делителя частоты 18, следующие с 1астотой fg /N на вычитающий вход PC (чер Ез элементы И 24 и ШШ 27) до момента обнуления PC, фиксирующего результат искомой операции в счетчике 22. При выполнении операции сложения разрешающий потенциал подается на управ.пяющие входы 16, 25 и 29 (подготавливаются элементы. И 15, 23, 28 и 30, а элемент ЗАПРЕТ 31 блокирует цепь подачи на суммирующий вход PC 8 импульсов с выхода ИЗ). За вре-мя T и Т в PC 8 и счетчике 22 формируются коды NT- и N. , после чего процесс вычисления продолжается анало№чно режиму умножения (за исключе шем того, что- содержимое PC 8 теперь списывается тактовыми импульсами, проходящими через элементы И 15, 23 и ИЛИ 27) и в счетчике 22 образуется код, пропорциональный Т + Т,. При выполнении операции вычитания разрешающий потенциал подается на управляющие входы 6 и 29 (подготавливаются элементы И 28 и И-НЕ 4) и ТИ проходят за время (, ) через элементы И 3, .28 и ИЛИ 17 на счетчик 22, формируя в нем код, отображающий результат искомой операции. 1 иЛ., 1 табл.

2

выход которого подключен к первым входам первого и второго элементов И 2 и 3, элемент J-HE 4, один из входов которого подключен к первому информационному входу 5 устройства и к второму входу первого элемента И, другой вход - к первому управляющему входу 6 устройства, а выход к .второму входу второго элемента И, третий вход которого подключен к второму информационному входу 7 устройства, реверсивньй счетчик 8, выходы которого соединены с первой группой входов схемы 9 сравнения, вторая

группа входов которой соединена с выходами первого счетчика 10, счетный вход которого подключен к выходу первого элемента И, одновибратор 11, вход которого подключен к первому информационному входу устройства, а выход - к одному из входов первого элемента ИЛИ 12, другой вход которого соединен с выходом схемы сравнения дешифратор 13 нуля, входы которого соединены с выходами реверсивного счетчика, а выход - с одним из вхо- дов (R) триггера 14, другой вход (S) которого подключен к второму информационному входу устройства, а в.ы- ход - к первому входу третьего элемента И 15, второй вход которого соединен с выходом генератора тактовых импульсов, третий вход - с вторым управляющим входом 16, а выход - с первым входом второго элемента ИЛИ 17 и со счетным входом управляемого делителя 18 частоты, управляющие входы которого соединены с выходами первого счетчика, четвертый элемент И 19, входы которого соединены с выходом схемы сравнения и с третьим управлякшщм входом 20 устройства, а выход - с входом сброса реверсивного счетчика, пятый элемент И 21, входы которого соединены с третьим управляюпщм входом устройства и с выходом первого элемента ИЛИ, а выход - с вторым входом второго элемента ИЛИ, выход которого подключен к счетному входу второго счетчика 22, выход которого является выходом устройства, шестой и седьмой элементы И 23 и 24, первые входы которых соединены с четвертым 25 и пятым 26 уп- равляющими входами устройства соответственно, вторые входы - с выходами третьего элемента И и управляемого делителя частоты, а выходы через третий элемент ИЛИ 27 - с вычитающим входом реверсивного счетчика, восьмой элемент И 28, входы которого соединены с шестым управляющим входом

1 X

29 устройства и с выходом второго элемента И, а выход - с третьим вхо- дом второго элемента ШШ, девятый

элемент И 30, входы которого соединены с четвертым управляющим входом устройства и с выходом первого элемента И, и элемент ЗАПРЕТ 31, входы которого Соединены с четвертым управляющим входом устройства и с выходом второго элемента И, а выход - с одним из входов четвертого элемента ШШ 32, другой вход которого подключен к выходу девятого элемента И, а .выход - к суммирующему входу реверсивного счетчика. Элементы, обведенные на чертеже пунктиром, образуют г двухканальные мультиплексоры на входах реверсивного счетчика.

Устройство работает в режимах выполнения операций деления,-умножения сложения и вычитания временных интервалов. Режим задается путем подачи разрешающего потенциала высокого уровня, соответствующего уровню логической 1 (в дальнейшем - разрешающего потенциала), на определенные управляющие входы устройства, указанные в таблице.

В исходном состоянии устройства счетчики В, 10, и 22, управляемый делитель 18 частоты и триггер 14 установлены в нулевое положение (импульсом, поступающим на шину Установка О) .

Режим деления временных интервалов .

Этот режим задается путем подачи разрешающего потенциала на управляющие входы 6 и 20 устройства. При этом подготавливаются элементы И 19 и 21 и элемент И-НЕ 4. Тактовые импульсы с выхода генератора 1 проходят через элемент И 2 в течение временного интервала Т, , поданного на первый информационный вход 5 устройства, и поступают на счетчик 10, содержимое которого линейно увеличивается по мере его заполнения и в момент времени, соответствующий окончанию указанного интервала, становится равным NT T,fg, где f частота тактовых импульсов. Это значение кода в дальнейшем сохраняется неизменным в счетчике 10 в течение всего цикла.

Первый временный интервал, кроме того, инвертируется элементом И-НЕ 4 и подается на элемент И 3, закрывая последний. В результате тактовые импульсы генератора 1 в течение времени Т не могут пройти через указанный элемент И, хотя на один из его входов и подан временный интервал T(Tj Т,) с второго информационного входа 7 устройства (начало интервала Tj, совпадает с началом интервала Т, ).

В момент времени, соответствуюищй окончанию временного интервала Т , одновибратор 11 формирует короткий импульс, который через элементы ИЛИ 12, И 21 и ИЛИ 17 заносится в

.счетчик 22. Это значит, что в больший временной интервал Т.уложился ровно один временной интервал Т. Одновременно элемент И 3 открывается (так как на выходе элемента И-НЕ 4

.с окончанием временного интервала Т устанавливается потенциал высокого уровня 1) и пропускает тактовые импульсы генератора 1, которые, пройдя далее через элемент ЗАПРЕТ 31 и элемент ИЛИ 32 на вход сложения реверсивного счетчика 8, начинают заролнять его. Элемент 31, установленный в указанной цели подачи тактовых импульсов на счетчик 8 (1-3- 31-32-8), реализует логическую функцию ЗАПРЕТ : W АБ, где А - сигнал на его первом (информационном) входе, связанном с выходом элемента И 3,

чанию временного интервала Т, при ; этом в счетчике 22 образуется код, отображающий целую часть отношения , как результат деления интерва 5 лов времени. Устройство устанавлива ется в исходное состояние и готово .к выполнению операи й следующего цикла.

Режим перемнойсения временных ин- W тервалоВо

Этот режим задается путем подачи разрешающего потенциала на управляю щие входы 16 и 26 устройства. При этом подготавливаются элементы И 15 15 и 24,

В течение времени, равного дли- тех ьности временньпс интервалов Т, и Т, счетчики 10 и 8 считают такто вые импульсы, форшфуемые генерато- 20 ром 1. В момент времени, соответствующий окончанию временного интер вала Т, , код в сметчике 10, устанав ливаюнщй требуемый коэффициент деления управляемого делителя 18 часа В - сигнал на его втором (управляю-25 тэты, равен KV . В момент времени.

щем) входе, связанном с управляющим входом 25 устройства. Так как в данном режиме В О, элемент 31 не препятствует прохождению тактовых импульсов на реверсивный с четчик В.

С каждым тактовым импульсом содержимое реверсивного счетчика увеличивается до тех пор, пока не становится равным N. . Момент равенства фиксируется схемой 9 сравнения, импульс с выхода которой, пройдя через элемент И 19, сбрасывает в нуль реверсивный счетчик и, пройдя через элементы ИЛИ 12, И 21 и ШШ 17, заносится в , счетчик 22. Это значит, что в больший временной интервал Т, уложился

соответствующий окончанию временноТ

14 в положение 1,

гера

код в ре30

версивном счетчике 8 равен N-

т -f

12 i о

Потенциал высокого уровня 1 с единичного выхода триггера 14 подается на один из управляющих входов

элемента И 15 (на другой управляющи вход этого элемента в данном режиме подан разрешающий потенциал с управ ляющего входа 16 устройства) и откр вает eroj в результате, тактовые им

Q пульсы генератора 1, пройдя через элемент И 15, поступают на счетный вход счетчика 22 через элемент ШШ 1 и далее на вычитающий вход реверсив ного счетчика 8 через делитель 18

Q пульсы генератора 1, пройдя через элемент И 15, поступают на счетный вход счетчика 22 через элемент ШШ 1 и далее на вычитающий вход реверсив ного счетчика 8 через делитель 18

второй временной интервал 1,.

Содержимое реверсивного счетчика 8 опять начинает увеличиваться (так как элемент И 3 открыт и тактовые им- 45 частоты, элементы И 24 и ИЖ 27. На пульсы генератора 1 продолжают пос- выходе делителя 18 частоты с коэф- тупать на его суммирующий вход) и увеличивается до тех пор, пока не становится равным N, . Дальнейшая последовательность операций аналогична рассмотренной: срабатывает схема 9

фициептрм деления, равным NT, , частота импульсов оказывается равной fg/Ny . Эти импульсы, поступая на

Q вычитающий вход реверсивного счетчика 8, списывают содержащийся в нем

код N до тех пор, пока содержимое счетчика не становится равным нулю. В этот момент времени дешифратор 13 нуля, подключенньм к выходам разрядов реверсивного счетчика, формиру- рует импульс, который возвращает триггер 14 в исходное положение 0 при этом элемент И 15 закрывается и

сравнения, импульс с выхода которой, пройдя через элемент И 19, сбрасывает реверсивный счетчик в нуль, а, пройдя через элементы ИЛИ 12, И 21 и 55 ИЛИ 17, заносится в счетчик 22 и т.д.

Процесс вычитания заканчивается в

момент времени, соответствующий окон чанию временного интервала Т, при этом в счетчике 22 образуется код, отображающий целую часть отношения , как результат деления интерва- лов времени. Устройство устанавливается в исходное состояние и готово к выполнению операи й следующего цикла.

Режим перемнойсения временных ин- тервалоВо

Этот режим задается путем подачи разрешающего потенциала на управляющие входы 16 и 26 устройства. При этом подготавливаются элементы И 15 и 24,

В течение времени, равного дли- тех ьности временньпс интервалов Т, и Т, счетчики 10 и 8 считают тактовые импульсы, форшфуемые генерато- ром 1. В момент времени, соответствующий окончанию временного интерЧ вала Т, , код в сметчике 10, устанав-; ливаюнщй требуемый коэффициент деления управляемого делителя 18 частэты, равен KV . В момент времени.

соответствующий окончанию временноТ

14 в положение 1,

гера

код в ре30

версивном счетчике 8 равен N-

т -f

12 i о

Потенциал высокого уровня 1 с единичного выхода триггера 14 подается на один из управляющих входов

элемента И 15 (на другой управляющий вход этого элемента в данном режиме подан разрешающий потенциал с управляющего входа 16 устройства) и открывает eroj в результате, тактовые импульсы генератора 1, пройдя через элемент И 15, поступают на счетный вход счетчика 22 через элемент ШШ 17 и далее на вычитающий вход реверсивного счетчика 8 через делитель 18

частоты, элементы И 24 и ИЖ 27. На выходе делителя 18 частоты с коэф-

45 частоты, элементы И 24 и ИЖ 27. На выходе делителя 18 частоты с коэф-

фициептрм деления, равным NT, , частота импульсов оказывается равной fg/Ny . Эти импульсы, поступая на

Q вычитающий вход реверсивного счетчика 8, списывают содержащийся в нем

частоты, элементы И 24 и ИЖ 27. На выходе делителя 18 частоты с коэф-

код N до тех пор, пока содержимое счетчика не становится равным нулю. В этот момент времени дешифратор 13 нуля, подключенньм к выходам разрядов реверсивного счетчика, формиру- рует импульс, который возвращает триггер 14 в исходное положение 0 при этом элемент И 15 закрывается и

поступление тактовых импульсов генератора 1 на счетчик 22 (через элементы И 15 и ИЛИ 17) и делитель 18 частоты (через элемент И 15) прекращается.

Триггер 14 находится в положении 1 в течение времени ut, равного

it

li.

NT.

и за это время в счетчике 22 образуется код, равный

N ut-f N,. N,,

что соответствует результату выполняемой операции.

Ре жим сложения временных интервалов.

Этот режим задается путем подачи разрешающего потенциала на управляющие входы 16, 25 и 29 устройства, при этом подготавливаются элементы И 15, 23, 2 и 30 устройства, а элемент ЗАПРЕТ (на управляющем входе которого теперь сигнал В 1) блокирует цепь подачи на суммируюдай вход реверсивного счетчика тактовых импульсов с выхода элемента И 3.

В течение времени, равного длительности меньшего временного интервала TV, реверсивный счетчик 8 считает тактовые импульсы генератора 1,

20 бьшо отмечено выше - путем подсчета тактовых импульсов через элементы ИЗ, 28 и ИЛИ 17 за время Т,,), то результирующий код в нем окажется равным N N + NT- , что соответст25 вует результату сложения временных интервалов. Бремя вьшолнения рассмотренной операщш, как следует из описания, равно Т + Т,

Режим вычитания временных интер- 30 валов.

Этот режим задается путем подачи разрешающего потенциала на управляющие входы 6 и 29 устройства. При этом подготавливаются элементы И 28 которые поступают на его суммирующий и-НЕ 4.

вход через элементы И 2, 30 и ИЛИ 32, при наличии на управляющем входе В момент времени, соответствующий (, разрешающего потенциала меньший окончанию этого интервала, в реверсивном счетчике 8 фиксируется код

N . Б течение времени, равного дли- Q ент И 3, закрывает его на время, тельности большего временного интер- равное Т,. Это значит, что в течение

временного интервала Т, , начало которого совпадает с началом интервала Tj, тактовые импульсы генератора 1 45 не могут пройти через элемент ИЗ,

временной интервал инвертируется элементом И-НЕ 4 и, поступая на элевала Tj, счетчик 22 считает тактовые импульсы генератора 1, которые поступают на его счетн вход через элементы И 3, 28 и ИЛИ 17. В момент времени, соответствующий окончанию этого интервала (к указанному моменту

т.е. из Tg как бы вырезают Т, .

В момент времени, соответствуюпщй окончанию временного интервала Т

В момент времени, соответствуюпщй окончанию временного интервала Т

I

времени формирование кода N в реверсивном счетчике В уже закончено,элемент И 3 открывается и.на его вы- так как Т, Т) и установке триггера 50 ходе появляются тактовые импульсы

14 в положение 1, код в счетчике 22 равен N.

Потенциал высокого уровня 1 с еданичного выхода триггера 14 подается на соответствуюпщй.управляющий вход элемента И 15,открывая его; и результате тактовые импульсы проходят через этот элемент и поступа ют на счетный вход счетчика 22 (через

генератора 1, которые через элементы И 28 и ИЛИ 17 (в течение времени, равного ,) поступают на счетчик 22, формируя в нем код N N. N., 55 отображающий результат искомой операции.

Формула изобретения Вычислительное устройство, содер- жащее генератор тактовых импульсов.

з, 2987448

элемент ИЛИ 17) и на вь читаюа1:ин вход реверсивного 8 (через эле- .менты И 23 и Ш1И 27) списывая со- держагцийся в последнем код N,. до

5 тех пор, пока содержимое реверсивного счетчика не становится равным нулю. В этот момент времени импульсом с выхода срабатывающего дешифратора 13 нуля триггер 14 возвращается в

fO исходное положение О, элемент И 15 закрывается и поступление тактовых импульсов на счетчики 8 и 22 прекращается.

Очевидно, что за время Т,

)5 от установки триггера 14 в положение 1 до обнуления реверсивного счетчика 8, в счетчик 22 поступает число импульсов, равное N , а так как в счетчик 22 уже записан код N (как

20 бьшо отмечено выше - путем подсчета тактовых импульсов через элементы ИЗ, 28 и ИЛИ 17 за время Т,,), то результирующий код в нем окажется равным N N + NT- , что соответст25 вует результату сложения временных интервалов. Бремя вьшолнения рассмотренной операщш, как следует из описания, равно Т + Т,

при наличии на управляющем входе (, разрешающего потенциала меньший

временной интервал инвертируется элементом И-НЕ 4 и, поступая на элет.е. из Tg как бы вырезают Т, .

В момент времени, соответствуюпщй окончанию временного интервала Т

I

элемент И 3 открывается и.на его вы- ходе появляются тактовые импульсы

генератора 1, которые через элементы И 28 и ИЛИ 17 (в течение времени, равного ,) поступают на счетчик 22, формируя в нем код N N. N., 55 отображающий результат искомой операции.

Формула изобретения Вычислительное устройство, содер- жащее генератор тактовых импульсов.

одновнбратор, реверсивный счетчик, первый и второй счетчики, схему сравнения, дешифратор нуля, триггер, делитель частоты, девять элементов И, элемент И-НЕ, три элемента ИЛИ, причем выход генератора тактовых импульсов соединен с первыми входами первого, второго и третьего элементов И, второй вход которого соединен с первым входом управления сложением и умножением устройства, первый информационный вход устройства соединен с входом одновибратора, с первым входом элемента И-НЕ и вторым входом первого элемента И, выход которого соединен со счетным входом первого счетчика и первым входом четвертого элемента И, второй вход которого соединен с первым входом srпpaвлeния сложением устройства, первый вход управления делением и вычитанием устройстве соединен с вторым входом элемента И-НЕ, выход которого соединен с вторым входом второго элемента И, третий вход которого соединен с вторым информационным входом устройства и S-входом триггера, R-вход которого соединен с выходом дешифратора нуля, входы которого соединены соответственно с выходами разрядов реверсивного счетчика и входами первой группы схемы сравнения, входы второй группы которой соединены соответственно с выходами разрядов первого счетчика и устано- вочньош входами делителя частоты, счетньШ вход которого соединен с выходом третьего элемента И, первым входом первого элемента ШШ и первым входом пятого элемента И, второй вход й оторого соединен с входом управления сложением устройства, вход управления умножением устройства соединен с первым входом шестого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, выход второго элемента ИЛИ соеданен с входом управления вычитанием реверсивного счетчика, вход сброса которого . соединен с выходом седьмого элемента И, первый вход которого соединен с входом управления делением, второй вход седьмого элемента И соединен с выходом схемы сравнения и первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом од- новибратора, вход.управления делением устройства соединен с первым входом восьмого элемента И, второй вход которого соединен с выходом третьего элемента ИЛИ, выход восьмо- го элемента И соединен с вторым входом первого элемента ИЛИ, выход которого соединен со счетным входом второго счетчика, выход которого соединен с выходом результата устройст- ва, выход делителя частоты соединен с вторым входом шестого элемента И, выход второго элемента И соединен с первым входом девятого элемента И, второй вход которого соединен с вхо- дом управления сложением и вычитанием устройства, выход девятого элемента И соединен с третьим входом первого элемента ШШ, единичный выход триггет1а соединен с третьим входом третьего элемента И, отличающееся тем, что, с целью увеличения быстродействия в режиме сложения временных интервалов, в него введены четвертый элемент ИЖ и элемент ЗАП- PET, причем прямой вход элемента ЗАПРЕТ соединен с выходом второго элемента И, вход управления сложением устройства соединен с инверсным входом элемента ЗАПРЕТ, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, вход управления сложением реерсивного счетчика соединен с выхо- ом четвертого элемента ШШ, вход становки в О сумматора соединен . входами установки в О первого второго счетчиков, делителя частоы л реверсивного счетчика.

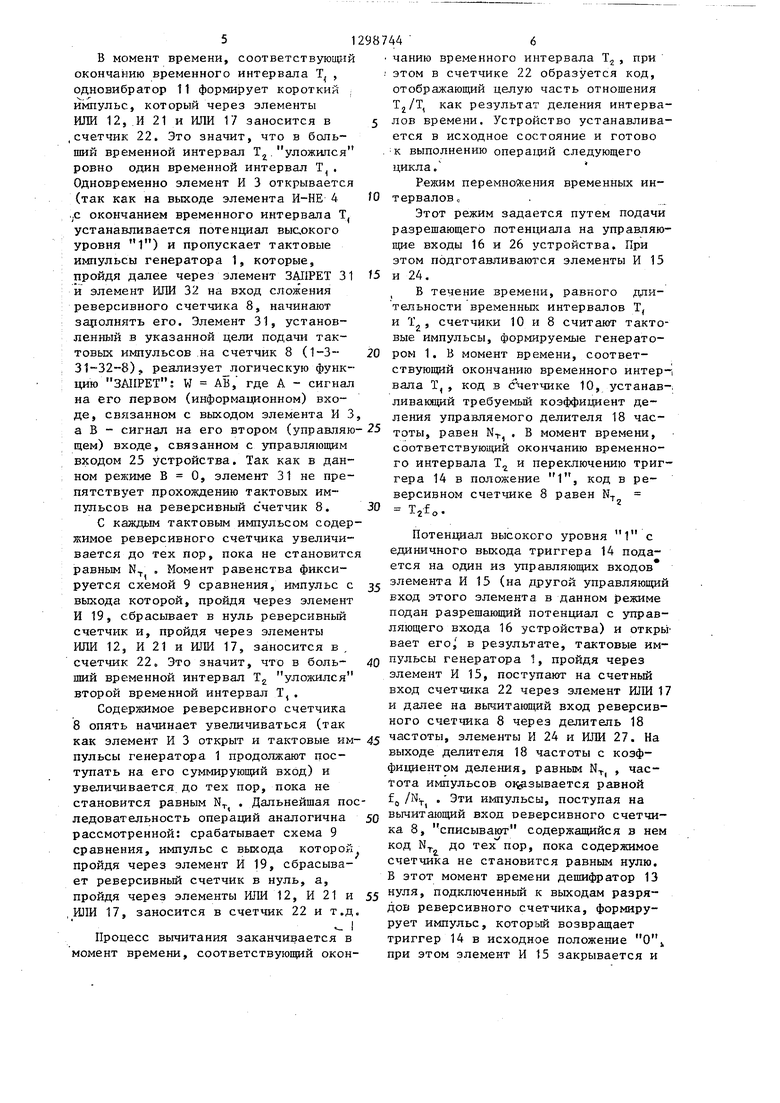

Деление Умножение Сложение Вычитание

Редактор Е.Папп

Составитель М.Есенина

Техред М.Ходаннч Корректор А.Зимокосов

890/51

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1982 |

|

SU1072044A1 |

| Функциональный преобразователь угла поворота вала в код | 1983 |

|

SU1170616A1 |

| Цифровая следящая система | 1983 |

|

SU1180841A1 |

| Цифровая следящая система | 1981 |

|

SU1012196A1 |

| Трехфазный генератор кодов для управления вентильным преобразователем | 1984 |

|

SU1244769A1 |

| Цифровой измеритель частоты заполнения радиоимпульсов | 1982 |

|

SU1161892A1 |

| Устройство для отсчета времени | 1985 |

|

SU1379771A1 |

| Вычислительное устройство | 1983 |

|

SU1120324A1 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| Устройство стабилизации амплитуды видеосигнала | 1985 |

|

SU1252973A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использ овано в информационно-измерительных системах дал вьшол- нения арифметических операций над времяимпульсными сигналами. Цель - увеличение быстродействия в режиме сложения временных интервалов. Устройство работает в режимах выполнения операций деления, умножения, сложения и вычитания временных интерва(Л с Уст.О

| Устройство для суммирования временных интервалов | 1980 |

|

SU962936A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1982 |

|

SU1072044A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-23—Публикация

1985-10-31—Подача