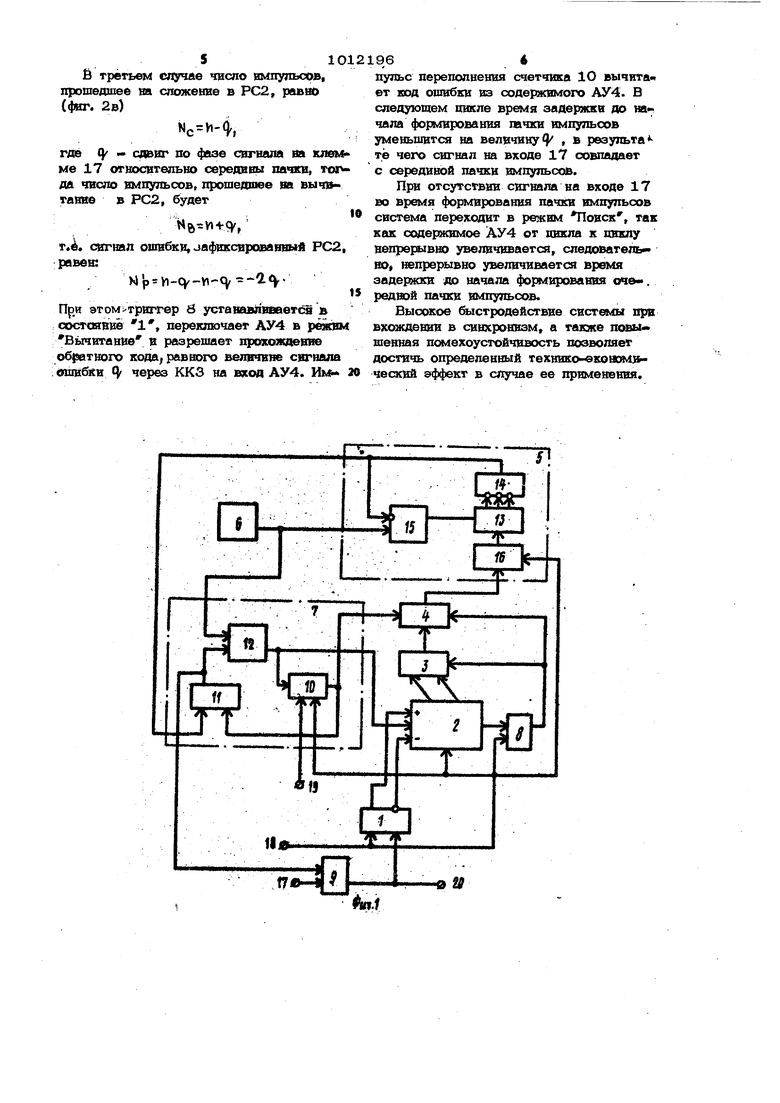

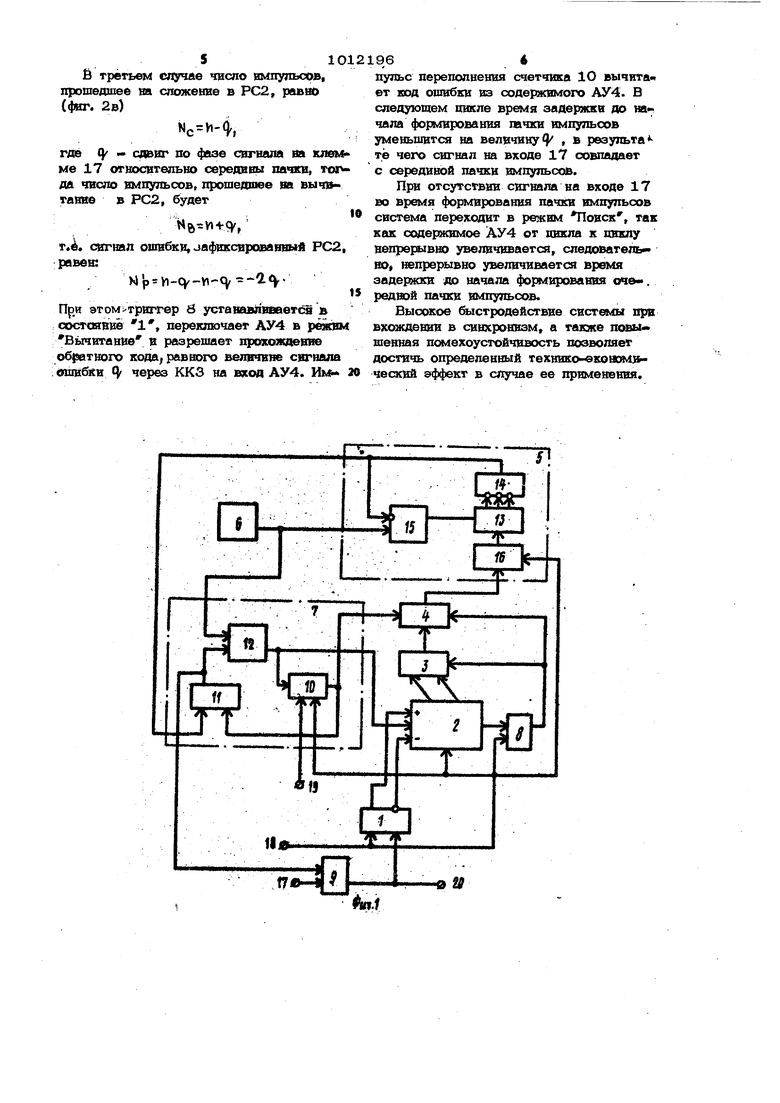

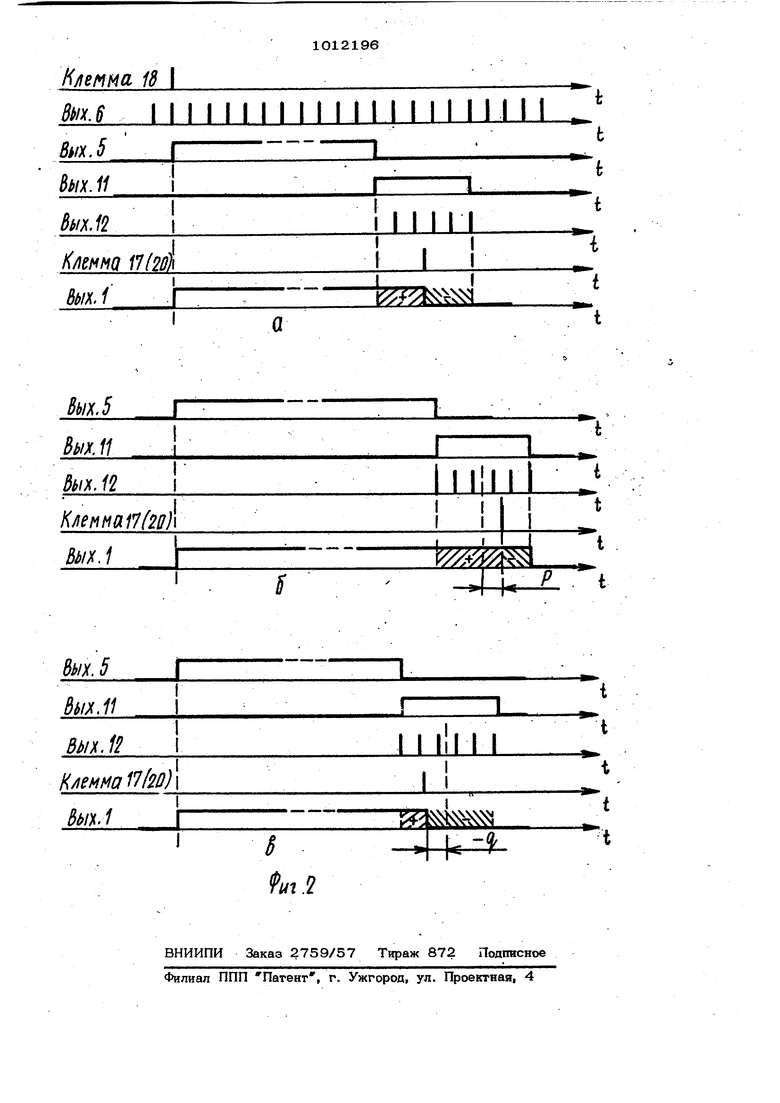

Изобретение относигся к автоматике и может быть использовано в геоакустике для автоматического выделения геофи зических сигналов, отраженных от дна м рей и океана. Известна цифровая следящая система, содержащая генератор подключенный чере преобразователь временной интервал код, преобразователь код - напряжение усилитель, исполнительный орган и объект к фазовращателю; формирователь им пульсов начальной установки, соединенны через триггер и элемент И с входом сче чика, и формирователь фазовых импульсо подключенный через схему сравнения ко второму входу преобразователя време ной интервал - код l. Недостатком известной системы является низкое быстродействие, так как оно содержит механические узлы. Наиболее близкой к изобретению по технической сущеости является цифровая следящая система, содержащая триггер, реверсивный счетчик и последовательно соединечаные генератор импульсов и делитель частоты 2J. Недостатками этой системы являют ся относительно низкие быстродействие И помехозащищенюсть, так как за один период входного сигнала импульсы на выходе делителя смещаются во времени на один период следования импульсов на выходе генератора и отсутствует време ное стробирование входного сигнала Цель изобретения - повыщение быстродействия и помехозащищенности. Указанная цель достигается тем, что в цифровую следящую систему введены первый элемент И, формирователь импульсов, второй триггер и госледочвательно соединенные коммутатор-кодов и арифметическое устройство, вЫход которого подключен к второму входу делителя частоты, второй вход - к выходу второго триггера и к управляющему вхо ду к ймутатора кодов, информационные входы которого соединены с соответствующими разрядными выходами реверсивног счетчика, причем выход генератора импульсов через формирователь импульсов и реверсивный счетчик подключен к первому входу второго триггера, второй выход формирователя импульсов через первый элемент И и первый триггер - к вто рому Та третьему входам реверсивного счетчика, а третий выход - к третьему входу ари4метического устройства, первы вход системы соединен с вторым входом первого элемента И, выход которого подключен к выходу системы, второй вход системы - с вторыми входами первого и второго триггеров, с четвертым входом реверсивного счетчика, с вторым вводом формирователя импульсов и с третьим входом делителя частоты, а третий вход системы - с третьим входом формирователя импульсов, четвертый вход которого подключен к выходу делителя частоты. Кроме того, формирователь импульсов сх держит второй элемент И, первый вход которого соединен с первым входом формирователя импульсов, а выход - с первым выходе формирователя импульсов в через первый счетчик импульсов и третий триггер - с вторым входом второго элемента И, причем второй, третий и четвертый входы формирователя импупьсх в юдключены соответственно к второму И третьему входам первого счетчика импульсов и ко второму входу третьего триггера, а второй и третий выходы к выходу третьего триггера и к выходу первого счетчика импульсов. Делитель частоты содержит последо ВАтельно соединенные третий элемент И, второй счетчик импульсов и четвертый элемент И, выход которого подключен к выходу делителя частоты и через пятый элемент И - к второму втоду второго счетчика импульсов, причем первый, второй и третий входы делителя частоты соединены соответственно с вторым входом пятого элемента И, с первым и вторым входами третьего элемента И. На фиг. 1 приведена блок-схема цифровой следящей системы; на фиг. 2 временные диаграммы сигналов на выходах функциональных элементов. Схема содержит первый триггер 1, реверсивный счетчик 2, коммутатор кодов 3, арифметическое устройство 4, делитель частоты 5, генератор импульсов 6, формирователь импульсов 7, второй триггер 8, первый элемент И 9, первый счетчик импульсов 10, третий триггер 11, второй элемент И 12, второй счетчик импульсов 13, четвертый, и третий элементы И 14,15 и 16, первый, второй и третий входы системы 17,18 и 19, выход системы 2О, Работа системы происходит следующим образсж. Ошрный и:v пyльc с входа 18 устаНаапивае г в состояние О реверсивный счетчик (PC) 2 и триггер 8, в состояние триггер 1, записывает начальный код N с входа 19 в счетчик 1О ф ыврователя импульсов (ФИ) 7 и переписывает содержимое арифметического устройства (АУ) 4 через элемент И 16 в счетчик 13 делителя частоты (ДЧ) 5, Элемент И 15 открывается, так как элемент И 14, выполняющий фушсгшю ратора.кода ....О, вырабатывает разрешающий потенциал шЬспе записи со- . дёржимогх) АУ 4 в счетчик 13. Импупысы, поступающие с выхода генератора 6, проходят через элемент И 15 и уменьшают содержимое вычитаюшего счетчика 13. В М(ент р енства содержимого счетчика 13 коду ОО....О срабатывает элемент И 14, выходная команда которо го закрывает элемент И 15, остатавлЕь вая ДЧ 5. По заднему фронту импульса /с выхода элемента И 14 устанавливается в состояние триггер 11 «Ш 7, разрешая прохождение импульсов генератора 6 через элемент И 12 на вход счетчика 1О и на счетный вход PC 2. Потенциал с выхода триггера 11 откралвает элемент И 9, Так как триггер 1 в состоянии 1переключает PC 2 в режим Сложение, то реверсивный счетчик 2 производит подсчет импульсов, посту- паюших с выхода элемента И 12, одновременно со счетчиком Ю. Импульс переполнения счетчика 1О устанавливает триггер 11 в состояние О, который закрывает элементы И 12 и 9, щрекра- шая формирование пачки, содержащей четное число импульсов. Если во время фо1 л НрЬвания пачки импульсов (элемент И 9 открыт) на вхо де 1 7 отсутствуетВХОДНОЙ сигнал, то триггер 1 остается в сзостоянии , вс . импульсы пачки PC 2 подсчитывает в ренййме Сложение, триггер 8 включает АУ4 в режим Слежение и разрешает щюхождение через коммутатьр кодов (КК)3 на АУ4 содержимого РС2 в npsi мом коде с од{ювремен1а 1м делением на 2 (сдвиг содержимого PC2 на один разряд в сторону младших разрядов). Импульс переполнения счетчика 10 прибавляет содержимое PC 2 к содержимом АУ4, увеличивая время задержки до шчала формирования пачки импульсов в следующем цикле. Если во время формирования пачки импульсов на входе 17 появляется вход ной сигнал, то он проходит через элемеет И 9 на выход системы 20 и устанавливает триггер 1 в состояние О, переключая PC 2 в режшл Вычитание, т.е. РС2 часть времени работает на Сложение, а часть - на Вычитание. При этом возможны три случая: РС2

1О12196 оловину длительности пачки импульсов аботает на Сложение, половину - на Вычитание; большую часть времени длительности пачки РС2 работает на Сложение, меньшую - на Вычитание; меньшую часть времени деятельности пачки РС2 работает на Сложение, большую - На вычитание . В первом случае числа импульсов, прошедшие на Сложение и на Вычетание, равны (число импульсов в пачке четное). Суммарный код РС2 после окончания пачки будет 00....О. Следовательно, по импульсу переполнения сче чика 1О содержимое АУ4 не изменятся (фиг. 2а) и время задержки до начала формирования пачки импульсов в спеау ющем цикле останется прежним. Во втором случае число импульсов, прошедшее на сложение в РС2, равно (фаг. 26) NC VXI-P, где И число импульсов, приходящееся на половину длительности па ки; Р - смещение входного сигнала на входе 17 от середины пачки импульсов. Тогда число импульсов, прошедЬее на |вычитание в РС2, будет равно , а счетчик 2 зафиксирует разностный код, обусловленный сдвигом по фазе сигнала на клемме 17 относительно середины пачки, равный Нр и1-р-и р-ар, т.е. сигнал ошибки, зафиксированный РС2, равен удвоен1юй величине cMeice- ния входного сигнала относительно середины пачки импульсов Выходной код РС2 делится на 2 сдвшгом содержимого РС2 на один разряд в сторону мдадшизс разрядов на входе ККЗ. Так как Триггер 8 не изменил своего состояния, то- через ККЗ на вход АУ4 поступает прямой код, равный величине сигнала ошибки Р, который по импульсу переполнения счет чика 1О складывается с содержимым АУ4. Следовательно, в следукяцем овкле время задержки до начала формировавня пачки импульсов увеличится ва Р перв одов следования импульсов на выходе ге нератора 6. В результате чего сигнал ва входе 17 совпадает с середивьй пачкв импульсов (фиг. 2а). 10 Ё третьем cyijraae число импульсов, прошедшее ва сложение в РС2, равш) (фиг. 2в) Nc Vt4, где f сдвиг по фазе сигнала йа KOSSMме 17 отиосительно середины пачки, число импульсов, прошедшее ва выч гание в РС2, будет , т.. сшйал ошибки, аафиксвроваяный РС2, равеш ( При 9Т ом i-триггер 8 устававливаетсЗШ в состоявиё 1, переключает АУ4 в режим Вычитание и разрешает прсясожпевие об тного кода; равного величине сигнала «яаибйи tV через ККЗ на вход АУ4. Ик 96 путхьс переполнения счетчика Ю вычитавт код ошибки из содержимого АУ4. В следующем шосле время задержки до на чала формирования гачки импульсов уменьшится на величину J , в результа те чего сигнал на входе 17 совпадает с серединой пачки импульсов. При отсутствии сигнала на входе 17 во время формирования пачки импуттьсов система переходит в резким Поиск , так как содержимое АУ4 от цикла к киклу вепрерывно увеличивается, следовательно, непрерывно увеличивается время задержки яо начала формирования оч. редшй пачки импульсов. Высокое быстродействие системы при вхсшдении в синхронизм, а также повы шенная помехоустойчивость позволяет достичь определенный технико-экономический эффект в случае ее применения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая следящая система | 1983 |

|

SU1180841A1 |

| Преобразователь пачки импульсов в прямоугольные импульсы | 1984 |

|

SU1251309A1 |

| Цифровой следящий фазометр | 1990 |

|

SU1748085A1 |

| Вычислительное устройство | 1985 |

|

SU1298744A1 |

| ОБНАРУЖИТЕЛЬ ПАЧКИ СИГНАЛОВ | 2006 |

|

RU2308046C1 |

| Устройство задания скорости в системах числового программного управления | 1986 |

|

SU1328793A1 |

| Генератор напряжения инфранизкой частоты | 1983 |

|

SU1088104A1 |

| Разностный счетчик импульсов | 1980 |

|

SU936433A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Преобразователь угла поворота вала в код | 1976 |

|

SU635504A1 |

1. СЛЕДЯЩАЯ СИСТЕМА, содержащая первый триггер, реверсивный счетчик и последовательно соединенные генератор и й1ульсов и делитель частоты, о т л и ч а ю щ а я с я тем, что, с целью повышения быстродейI сгвия и пс 1ехоза11ппценирсти, в нее введены первый элемент И, формирователь импульсов, второй триггер и последовательно соединенные коммутатор кодов и арифметическое устройство, выход которого подключён к второму входу делителя чао тоты, второй вход - к выюду второго триггера и к управляющему входу коммутатсфа кодов, ииформационные входы которого соединены с соответствующими разрядными выходами реверсивного счетчика, причем выход генератора импульсов через формирователь импульсов и реверсивный счетчик подключен к первому входу второго триггера, второй выход формирователя импульсов через первый элемент И в пе{шый трштер -« к второму и третьему входам реверсивного счетчика, а третий выход - к третьему входу арифметического устройства, первый вход сио темы соединен с вторым входом элемента И, выход которого подключен к выходу системы, второй вход системы - с вторыми входами первого и второго триггеров, с четвертым входом реверсивного счетчика, с вторым входом формирователя импульсов и с третьим вкошял делителя частоты, а третий вход системы - с третьим входом формирователя . импульсов, четвертый вход которого подключен к заыходу делителя частоты.. 2.Система по п. 1, о т л и ч а ю - щ а я с я тем, что формирователь импульсов содержит второй И, первый вход которого соединен с первым входом формирователя импульсов, а выходс первым выходом формирователя импутшсов и через первый счетчик импульсов и (О третий триггер - со вторым входом второго элемента И, причем второй, третий и четвертый входы формирователя импульсов подключены соответственно к втоi рому и третьему входам первого счетчика .импульсов и к второму входу третьего триггера, а второй и третий выходы к вь1ходу третьего триггера и к выходу первохч) счетчика импульсов. 3.Система по п. 1, о т л и ч а ю « , Ю щ а я с я тем, что делитель частоты содержит последовательно соединенные тре тий элемент И, второй счетчрк импульсов О) И четвертый элемент И, выход которохх) подключен к выходу делителя частоты и через пятый элемент И - ко BTOpCKviy вхо ду второго счетчика импульсов, причем первый, второй и третий входы делителя частоты соединены соответственно с вторым входом пятого элемента И, с пер- . вым V. вторым входами третьего элемеи. та И.

K/ien a Id I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЦИФРОВАЯ СЛЕДЯЩАЯ СИСТЕМА | 0 |

|

SU407277A1 |

| кп | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-04-15—Публикация

1981-12-29—Подача