Изобретение относится к автоматике и вычислительной технике и может быть применено при построении устройств выдачи команд, формирователей параллельных кодов распределителей уровней и специальных пересчетных ;:. устройств.

Цель изобретения - расширение функциональных возможностей путем

а управляющий 1К-триггер 4 ничное (1) исходное сост

При приложении к шине 8 потенциала, а к шинам 9 и ничных потенциалов обеспеч режим формирования кодов Ли Крейга (фиг. 2а), При этом левого потенциала на шине ются по входам, первые стру

обеспечения двух дополнительных режи- элементов И-ИЛИ 2.1-2.N. В

мов пересчета.

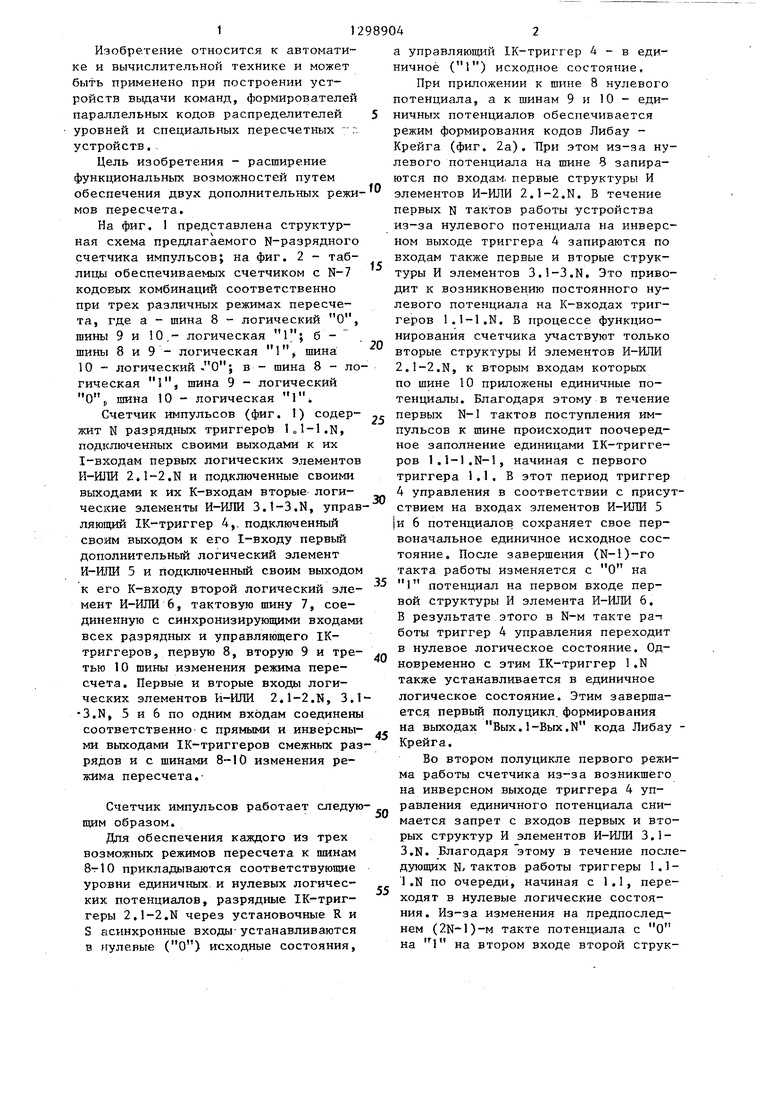

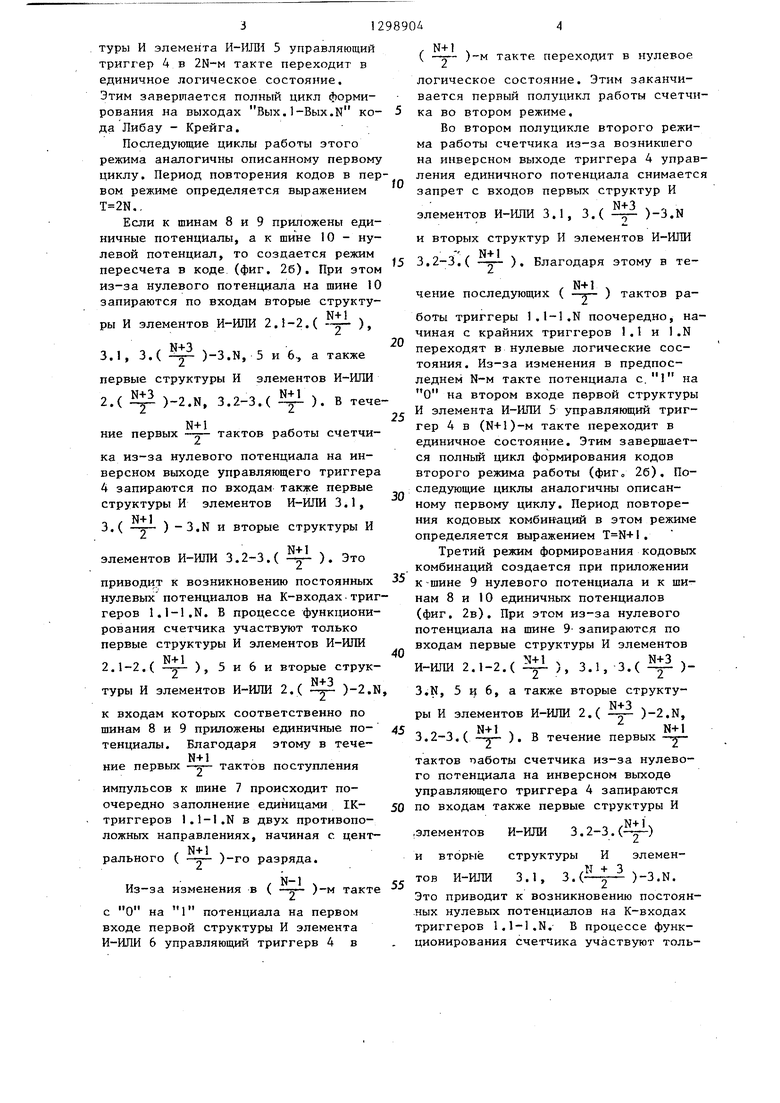

На фиг. 1 представлена структурная схема предлагаемого N-разрядного счетчика импульсов; на фиг. 2 - таблицы обеспечиваемых счетчиком с N-7 кодовых комбинаций соответственно при трех различных режимах пересчета, где а - шина 8 - логический О, шины 9 и 10,- логическая б - шины 8 и 9 - логическая % шина 10 - логический , в - шина 8 - логическая I, шина 9 - логический шина 10 - логическая 1 Ч

Счетчик импульсов (фиг. 1) содержит N разрядных триггеров Kl-l.N, подключенных своими выходами к их 1-входам первых логических элементов И-ИЛИ 2.1-2.N и подключенные своими выходами к их К-входам вторые логические элементы И-ИЖ 3.1-3.N, управляющий 1К-триггер 4,. подключенный своим выходом к его 1-входу первый дополнительный логический элемент И-И.Т1И 5 и подключенный своим выходом к его К-входу второй логический элемент И-ИЛИ 6, тактовую шину 7, соединенную с синхронизирующими входами всех разрядных и управляющего IK- триггеров, первую 8, вторую 9 и третью 10 шины изменения режима пересчета. Первые и вторые входы логических элементов И-ИЛИ 2.1-2.N, 3.1 3.N, 5 и 6 по одним входам соединены соответственно с прямыми и инверсны- ми выходами 1К-триггеров смежных разрядов н с шинами 8-10 изменения режима пересчета,

Счетчик импульсов работает следующим образом.

Для обеспечения каждого из трех возможных режимов пересчета к шинам 8-10 прикладываются соответствующие уровни единичных, и нулевых логических потенциалов, разрядные 1К-триг- геры 2.1-2.N через установочные R и S асинхронные входы-устанавливаются в нулевые (О) исходные состояния.

а управляющий 1К-триггер 4 - в единичное (1) исходное состояние.

При приложении к шине 8 нулевого потенциала, а к шинам 9 и 10 - единичных потенциалов обеспечивается режим формирования кодов Либау - Крейга (фиг. 2а), При этом из-за нулевого потенциала на шине 8 запираются по входам, первые структуры И

элементов И-ИЛИ 2.1-2.N. В

течение

0

5

.,

0

5

0

0

5

первых N тактов работы устройства из-за нулевого потенциала на инверсном выходе триггера 4 запираются по входам также первые и вторые структуры И элементов 3.1-3.N. Это приводит к возникновению постоянного нулевого потенциала на К-входах триггеров 1.1-1.N. В процессе функционирования счетчика участвуют только вторые структуры И элементов И-ИЛИ 2.1-2.N, к вторым входам которых по шине 10 приложены единичные потенциалы. Благодаря этому в течение первых N-1 тактов поступления импульсов к шине происходит поочередное заполнение единицами 1К-тригге- ров 1.1-1.N-1, начиная с первого триггера 1.1. В этот период триггер 4 управления в соответствии с присутствием на входах элементов И-ИЛИ 5 |и 6 потенциалов сохраняет свое первоначальное единичное исходное состояние. После завершения (N-l)-ro такта работы изменяется с О на 1 потенциал на первом входе первой структуры И элемента И-ИЛИ 6. В результате этого в N-M такте ра-т боты триггер 4 управления переходит в нулевое логическое состояние. Одновременно с этим 1К-триггер 1.N также устанавливается в единичное логическое состояние. Этим завершается первый полуцикл, формирования на выходах Вых. l-Bbix.N кода Либау - Крейга.

Во втором полуцикле первого режима работы счетчика из-за возникшего на инверсном выходе триггера 4 управления единичного потенциала снимается запрет с входов первых и вторых структур И элементов И-ИЛИ 3.1- 3.N. Благодаря этому в течение последующих N тактов работы триггеры 1.1- 1.N по очереди, начиная с 1.1, переходят в нулевые логические состояния. Из-за изменения на предпоследнем (2N-1)-M такте потенциала с О на 1 на втором входе второй структуры и элемента И-ШМ 5 управляющий триггер 4 в 2N-M такте переходит в единичное логическое состояние, Этим завершается полный цикл формирования на выходах Вых. l-Bbix.N кода Либау - Крейга.

Последующие циклы работы этого режима аналогичны описанному первому циклу. Период повторения кодов в первом режиме определяется выражением ,,

Если к шинам 8 и 9 приложены единичные потенциалы, а к шине 10 - нулевой потенциал, то создается режим пересчета в коде (фиг, 2б). При этом из-за нулевого потенциала на шине 10 запираются по входам вторые структуN+ l 2 N+3

ры И элементов И-ИПИ 2.J-2,(

),

3,1, 3,(

)-3,N, 5 и 6, а также

первые структуры И

N+4 2,( - )-2,N, 3,2-3,(

элементов N+1

), ние первых

N+1

тактов работы счетчи3,( ) -3,N и вторые структуры И элементов И-ИЛИ 3,2-3,( - ). Это

ка из-за нулевого потенциала на инверсном выходе управляющего триггера 4 запираются по входам также первые структуры И элементов И-ИЛИ 3,1, N+1 2

N+1 2

приводит к возникновению постоянных нулевых потенциалов на К-входах триггеров 1,1-1,N, В процессе функционирования счетчика участвуют только первые структуры И элементов И-ИЛИ

2,1-2,(Н

туры и элементов И-ИЛИ 2,(

), 5 и 6 и вторые струкN+3Т

)-2,N

к входам которых соответственно по шинам 8 и 9 приложены единичные по- тенциалы. Благодаря этому в течеN+1ние первых „ тактов поступления

импульсов к шине 7 происходит поочередно заполнение единицами IK- триггеров 1,1-1,N в двух противоположных направлениях, начиная с цент N+1

рального (

)-го разряда.

Из-за изменения в (

N-1

)-м такте

с О на 1 потенциала на первом входе первой структуры И элемента И-ИЛИ 6 управляющий триггерв 4 в

(

N+1

)-м такте переходит в нулевое

логическое состояние. Этим заканчивается первый полуцикл работы счетчика во втором режиме.

Во втором полуцикле второго режима работы счетчика из-за возникшего на инверсном выходе триггера 4 управления единичного потенциала снимается запрет с входов первых структур И

элементов И-ИЛИ 3,1, 3,(

N+3

)-3,N

и вторых структур и элементов И-ИЛИ

N+1 3,2-3,( ), Благодаря этому в теN+1

чение последующих (

) тактов ра

20

25

30

35

40

,

45 50

боты триггеры 1,1-1,N поочередно, начиная с крайних триггеров 1,1 и 1,N переходят в нулевые логические состояния. Из-за изменения в предпоследнем N-M такте потенциала с.1 на О на втором входе первой структуры И элемента И-ШШ 5 управляниций триггер 4 в (N+1)-M такте переходит в единичное состояние. Этим завершается полньй цикл формирования кодов второго режима работы (фиг 2б), Последующие циклы аналогичны описанному первому циклу. Период повторения кодовых комбикаций в этом режиме определяется выражением ,

Третий режим формирования кодовых комбинаций создается при приложении к шине 9 нулевого потенциала и к шинам 8 и 10 единичньтх потенциалов (фиг, 2в), При этом из-за нулевого потенциала на шине 9- запираются по входам первые структуры И элементов

3,1, 3,(ii)3.N, 5 ц 6, а также вторые структуN+4ры И элементов И-ИЛИ 2,( - )-2,N,

,„,,,, N+l .„N+1

J,2-3,( ), В течение первых -я-

тактов чаботы счетчика из-за нулевого потенциала на инверсном выходе управляющего триггера 4 запираются по входам также первые структуры И

.N+1,

N+1 И-ИЖ 2,1-2,( ) .

.элементов

И-ИЛИ 3,2-3,(-)

И ,N +

элемени вторые структуры

тов И-ИЛИ 3,1, 3,(- )-3,N,

Это приводит к возникновению постоян- .ных нулевых потенциалов на К-входах триггеров 1,1-1,N, В процессе функционирования счетчика участвуют толь2.1-2.( illJ- ), 5 и 6 и туры и элементов И-ИЛИ 2,

(

)-2.

ко вторые структуры И элементов И-Ш

N+1 -S- ), Ь и b и первые струкN+3

2

на входы которых соответственно по шинам 8 и 10 приложены единичные потенциалы. Благодаря этому в течение

N+1

первых -у- тактов поступления импулсов к шине 7 происходит поочередное заполнение единицами ТК-триггеров 1,1-l.N в двух противоположных направлениях, начиная с крайных (1-го и N-ro) разрядов. Из-за изменения в

( Hll )-м такте с О на 1 потенц

ала на первом входе второй структуры И элемента И-ИЛИ 6 управляющий тригN+1гер 4 в ( -я- )-м такте переходит в

нулевое логическое состояние Этим заканчивается первый полуцикл работы счетчика в третьем режиме.

Во втором полуцикле третьего режима работы счетчика из-за появления на инверсном выходе триггера 4 управления единичного потенциала снимается запрет с входов вторых струк-

N+3

тур И элементов И-ИЛИ 3.1, 3.(

)3.N и первых структур N+1 2

И элементов

И-ИЛИ 3.2-3.(

). Благодаря это, N+1 , му в течение последующих ( ) тактов работы триггеры 1.1-1.N поочередно, на чиная с центрального разряда, переходят в нулевые логические состояния. Из-за изменения в предпоследнем N-M такте потенциала с 1 на О на втором входе второй структуры И элемента И-ИЛИ 5 управляющий триггер 4 в (N+1)-M такте переходит в едини 1Ное состояние. Этим завершается полный цикл формирования кодов третьего режима работы (фиг. 2в). Последующие циклы аналогичны описанному первому циклу. Период повторения кодовых комбинаций в этом режиме также определяется вьфяжением .

Таким образом, предлагаемый N-раз- рядный счетчик импульсов позволяет обеспечить три различных режима пересчета, в связи с чем обладает расширенными функциональными возможностями: .

р м у л а

6

изо

бретения

Счетчик импульсов, содержащий в каждом из N, где N - нечетное число, разрядов 1К-триггер, подключенный синхронизирующим входом к тактовой шине, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения двух дополнительных режимов пересчета, дополнительно содержит управляющий 1К-триггер, входы I и К которого соединены с выходом первого и второго дополнительных элементов И- ИЛИ, три шины изменения режима пересчета и первый и второй логические элементы И-ИЛИ с первой и второй структурами И в каждом разряде, соединенные своими выходами соответственно с I- и К-входами всех разрядных 1К-триггеров, прямой выход каждого 1К-триггера с второго по

30

(

N+1

)-й разряд и с (

)-го по

25

N4-5

2 первым входом

N-Й разряд соединен с первой структуры И первого элемента И-ИЛИ предыдущего разряда, прямой

N+1 2 да и инверсный выход 1К-триггера

N+3 ( -75 )го разряда соединены соотвыход 1К-триггера (

)-го разря

ветственно с первым и вторым входами первой структуры И первого допол- нительного элемента И-ИЛИ, прямой выход 1К-триггера N-ro разряда и инверсный выход 1К-триггера (N-l)--ro разряда соединены соответственно с первьгм и вторым входами- второй структуры И первого дополнительного элемента И-ИЛИ, прямой выход 1К-триг- гера (N-l)-ro разряда и инверсный выход 1К-триггера N-ro разряда соединены соответственно с первым и вторым входами первой структуры И второго дополнительного элемента И-ИПИ, прямой выход 1К-триггера

N+3 ( -я- )-го разряда и инверсный выход

/ N+1 . 1К-триггера ( -;:- )-го разряда сое

динены соответственно с первым и вторым входами второй структуры И второго дополнительного элемента 5 И-ИЛИ, инверсный выход каждого IKN+1

триггера с разряд и с

по (

Г

)-й

третьего

f N+5 « .. „

( -S- )-го по N-и разряд

соединен с первым входом первой структуры И второго элемента И-ИЛИ предыдущего, разряда, инверсный выход 1К-триггера второго разряда соединен с первым входом второй структуры Н второго элемента И-ИЛИ первого разряда, прямой выход управляющего IK- триггера соединен с первыми входами

первых структур И первых элементов N+1

И-ИЛИ (

)-го и N-ro -разрядов и

с первым входом второй структуры И первого элемента И-ИЛИ, первого разряда, прямой и инверсный выходы каж- доге 1К-триггера с первого по (N-l)-й разряд соединены с первь1ми входами .вторых структур И первых и вторых элементов И-ИЛИ последующего разряда, инверсный выход управляющего IK- триггера соединен с вторыми входами первых и вторых структур И вторых элементов И-ИПИ всех разрядов, первая шина изменения режима пересчета соединена с вторыми входами первых структур И первых элементов И-ИЛИ всех разрядов-, с первыми входами пер- вьпс структур И вторых элементов И-И1Ш

N+1 ( ) и N-ro разрядов и с третьим входом второй структуры И второго дополнительного элемента И-ШШ, вторая шина изменения режима пересчета соединена с третьим и первым входами первой структуры И соответ-

ствеипо первого и второго элемента И-ИЛИ первого разряда, с третьими входами первых структур И и с третьими входами вторых структур И соответственно первого и второго элементов

N+1 . „

- ;-и разряд.

И-ИПИ с второго по (

0

5 0 5

;

с вторыми входами вторых структур И и с третьими входами первых структур И соответственно первого и второго

N+T элементов И-ИЛИ ( - )-го по N-й

разряд и с третьими входами первых структур И первого и второго дополнительных элементов И-ИЛИ, третья шина изменения режима пересчета соединена с вторым входом второй структуры И и с третьим входом второй структуры И соответственно первого и второго элементов И-ИЛИ первого разряда, с вторым входом второй структуры И и с третьим входом первой структуры И соответственна первых и вторых элементов И-ИЛИ с втоN+1рого по ( -2 )-й разряд, с третьим

входом первой структуры И и с третьим входом второй структуры и соответственно первого и второго элементов

N+3 с ( )-го по N-й р.азряд и

с третьим входом второй структуры И и с четвертым входом второй структуры И соответственно п ервого и второго дополнительных элементов И-ИЛИ,

И-ИЛИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный кольцевой счетчик | 1980 |

|

SU919092A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1981 |

|

SU964951A1 |

| Кольцевой счетчик | 1987 |

|

SU1437995A2 |

| Функциональный счетчик | 1988 |

|

SU1531214A1 |

| Функциональный счетчик | 1984 |

|

SU1270891A1 |

| Кольцевой счетчик | 1985 |

|

SU1298905A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1981 |

|

SU993428A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1980 |

|

SU909784A1 |

| Реверсивный счетчик | 1981 |

|

SU982201A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1982 |

|

SU1061230A1 |

Изобретение относится к автоматике и вычислительной технике и мо8б/код1 дымдг дйкод дымд бб/ход5 дьмВб вшо жет быть применено при построении устройств выдачи команд, распределителей уровней и специальных пересчетных устройств. Цель изобретения - расширение функциональных возможностей путем обеспечения двух дополнительных режимов. Устройство содержит N разрядов, в каждом содержится IK- триггер 1.1-1.N. Для достижения поставленной цели в устройство введены , управляющий 1К-триггЕр 4, элемент И-ИЛИ 2.1-2.(N-1), 3,1-3.(N-1), 5 и 6 и образованы соответствующие связи. 2 нп. Фиг.1

а

J3 о о о о о о чо о о о о о

0000 чО о о о

о о о о

«ч

о о о

000 0000

о о о с о

000000

1000000

ВНИИПИ Заказ 898/59 Тираж 902

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Подписное

| Счетчик импульсов | 1977 |

|

SU784003A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ГуГников B.C | |||

| Интегральная электроника в измерительных приборах | |||

| Л.: Энергия, 1974, с | |||

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

Авторы

Даты

1987-03-23—Публикация

1985-11-26—Подача