(54) СЧЕТЧИК ИМПУЛЬСОВ.

I

Изобретение относится к автоматике и вычислительной технике и может использоваться при построении пересчетньрс устройств ,накопителей импульсов, устройств выдачи команды и т. п. 5

Известен счетчик импульсов, содержащий ЗК-триггер, прямой и инверсный выходы которого соединены соответ ственно с и и К входами следующего триггера, и элемент И ll . 10

Недостатком этого счетчика импульсов является относительно иизкая помехоустойчивость.,

Известен также счетчик импульсов, содержащий три ЗК-Григгера и элемент j И, первые три входа которого соединены с прямыми выходами соответствен-,но первого, второго и третьего ЗК-триггеров, Эй К входы второго ОК-триггера соединены соответственно 2Q с прямым и инверсным выходами первого JK-триггера, J и К входы третьего ЦК-триггера соединены соответственно с прямым и инверсным выходами второго ОК-триггера, а тактовые входь 25 всех ЗК-триггеров соединены с входом счетчика 21., .

Недостатком этого счетчика является относительно низкая помехоустойчивость . .30

Целью изобретения является повы.шение помехоустойчивости.

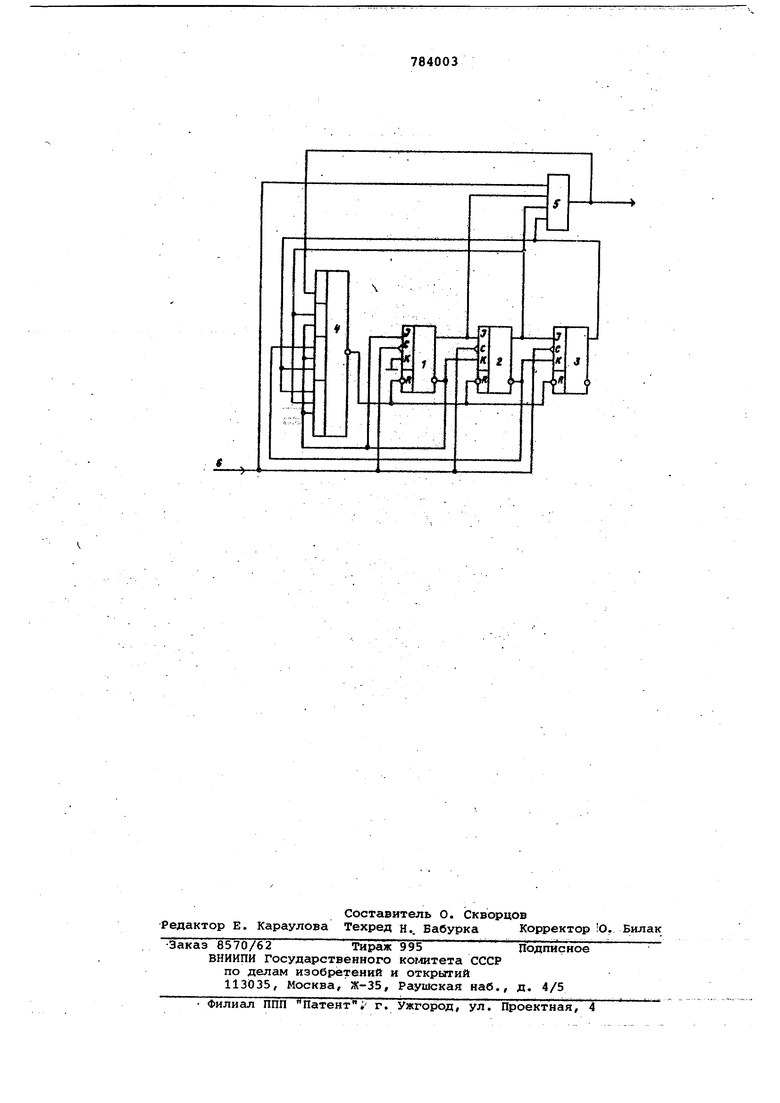

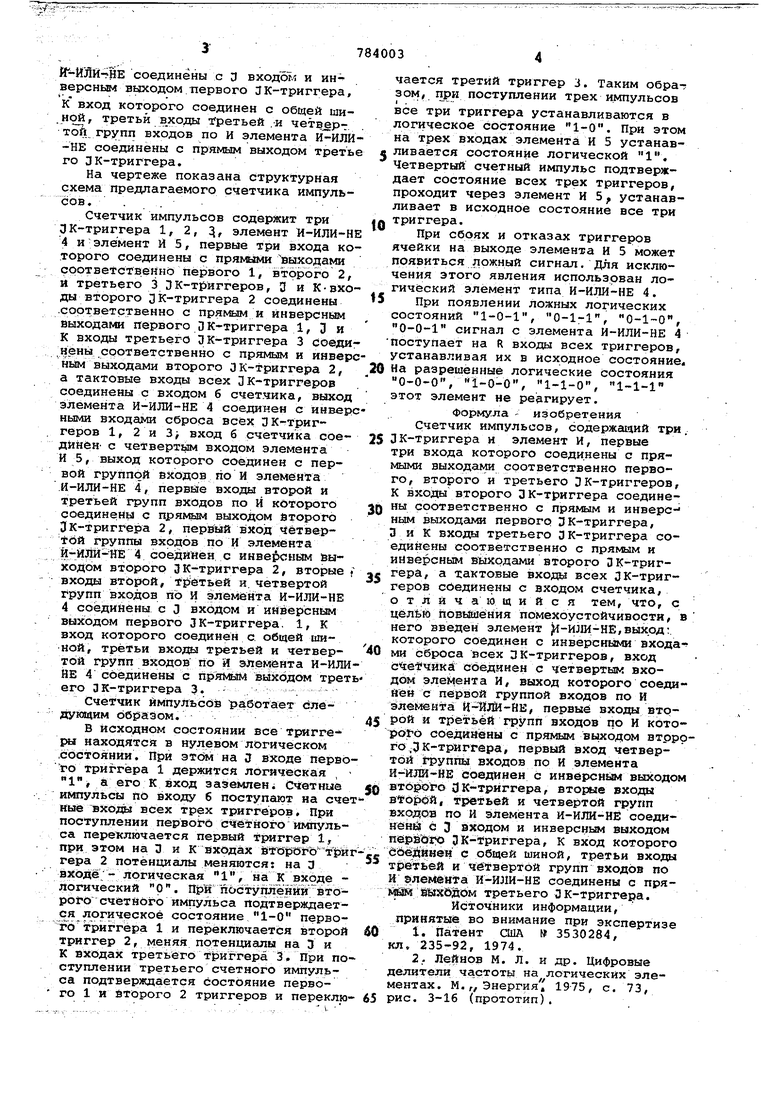

Это достигается тем, что в счетчик импульсов, содержащий три ЛК-триггера и элемент И, первые три входа которого соединены с прямыми выходами соответственно I inepsoro, второго и третьего ЛК-триггерйв, К входы второго ЗК-триггера соединены соответственно с прямым и инверсным выходами первого ЗК-триггера, 3 и К-входы третьего ЗК-триггера соединены соответственно с прямым и инверсным выходами второго Зк-триггера, а тактовые входы всех ЗК-триггеров соединены с входом счетчика, введен элемент И-ИЛИ-НЕ, выход которого соединен с инверсными входами сброса всех ЗК-триггеров, вход счетчика соединен с четвертым входом элемента И, выход которого соединен с первой группой входов по И элемента И-ИЛИ-НЕ, первые входы второй и третьей групп входов по И которого соединены с пряким выходом второго ЗК-триггера, первый вход четвертой группы входов по И элемента И-ИЛИ-НЕ соединен с инверсНь 1 выходом второго ЗК-триггера, вторые входы второй, третьей и четвертдй групп входов по И элемента И-ИЯИгНЕ соединены с D входом и ин версным выходом первого JK-триггера, К вход которого соединен с общей ши.ной, третьи входы тгретьей .и четв ртой. групп входов по И элемента И-ИЛИ -НЕ соединены с прямым выходом треть го ЗК-триггера. На чертеже показана структурная схема предлагаемого счетчика импульсов. . . - . . Счетчик импульсов содержит три рК-триггера 1, 2, Д, элемент И-ИЛИ-Н 4 и элемент И 5, первые три входа ко торого соединены с прямыми выходами срответственно первого 1, втсэрого 2, и третьего 3DК-трйггеров, 3 и К-вхо ды второго ЗК-триггера 2 соединены .соответственно с прямым и инверсным выходами первого р К-триггера 1, 3 и К входы третьего UK-триггера 3 соеди нены соответственно с прямым и инвер ным выходами второго ОК-триггера 2, а тактовые входы всех ЗК-триггеров соединены с входом б счет.чика, выход элемента И-ИЛИ-НЕ 4 соединен с инвер ными входа ш сброса всех ЗК- триггеров 1, 2 и 3 j вход 6 счетчика соедйнбн- с входом элемента И 5, выход которого соединен с первой группой входов по И элемента .И-ИЛИ-НЕ 4, первйе входы второй и третьей групп входов по И кбторого соединены с прямым выходом второго ОК-триггера 2, первый вход Четвертой группы входов по И элемента И-ЙЛЙ-НЁ 4 соединён с йыходбм второго 3К-триггера 2, вторые входы второй, третьей и. четвертой групп входов по И элемента И-ИЛИ-НЕ 4 соединены с О входом и инйерсным выходом первого 3К-триггера. 1, К вход которого соединен с общей тиной, третьи входа третьей и четвертой групп входов по и И-ИЛИ НЕ 4 соединены с пряМЕлМ )эы:к:ддом трет его ЗК-триггера 3.. Счетчик импульсов работает слеяуюадим Образом. В исходном состоянии все тригге- ры находятсй в нулевом логическом .состоянии. При этОм на J входе перво го триггера 1 держится логическая , 1, а его К вход заземлен i Счетные импульсы по йходу б поступают на сче ные входа всех трех триггеров. При поступлении nepBoi-O сметного импульса переключается первый т жггер 1, при этом на D и К входах e OptSro гера 2 потенциалы меняются: на 3 входе - логическая 1, на К входе логический О. При 1(т6ступлейй Г йтОро осчетйого импульса подтверждает ся логическое состояние 1-0 перво f-b триггера 1 и переключается второй триггер 2, меняя потенциалы на Э и К входах третьего триггера 3. При по ступлении третьего счетного импульса подтверждается состояние первого 1 и второго 2 триггеров и переклю чается третий триггер 3. Таким обрат зом, поступлении трех импульсов все три триггера устанавливаются в огическое состояние 1-0. При этом на трех входах элемента И 5 устанавивается состояние логической 1. Четвертый счетный импульс подтвержает состояние всех трех триггеров, проходит через элемент И 5, устанавивает в исходное состояние все три триггера. При сбоях и отказах триггеров ячейки на выходе элемента И 5 может появиться ложный сигнал. Для исключения этого явления использован логический элемент типа И-ИЛИ-НЕ 4. При появлении ложных логических состояний 1-0-1, 0-1-1, 0-1-0, 0-0-1 сигнал с элемента И-ИЛИ-НЕ 4 поступает на R входы всех триггеров, устанавливая их в исходное состояние. На разрешенные логические состояния 0-0-0, 1-0-0, 1-1-0, 1-1-1 этот элемент не реагирует. Формула изобретения Счетчик импульсов, содержащий три. ЗК-триггера и элемент И, первые три входа которого соединены с прямыми выходами соответственно первого, второго и третьего ЗК-триггеров, К входы второго ЗК-триггера соединены соответственно с прямым и инверс-ным выходами первого ЗК-триггера, D и К входаа третьего DК-триггера соединены соответственно с прямым и инверсным выходами второго ЗК-триггера, а тактовые входы всех ЗК-триггеров соединены с входом счетчика, о тли ч а 10 1Д и и с я тем, что, с целью гювъКйёния помехоустойчивости, в него введен элемент -ЮШ-НЕ,выход;, которого соединен с инверсными входа- ми сброса всех ЗК-триггеров, вход сч:е чйка соединен с четвертым входом эдеМента И, выход которого соедийей с первой группой входов по И Элемента Й- ЛИ-НЕ, первые входы второй и третьей групп входов по И которого соедийёны с прямым выходом втррого.ЗК-триггера, первый вход четвертой irpynna входов по И элемента И-ИШ-НЕ соединен с инверснйм выходом втОЕЮго ак-трйггера, вторие входы второй, третьей и четвертой групп входов по И элемента И-ИЛИ-НБ соедиneHii с 3 входом и инверсным выходом ЭК-Триггера, К вход которого с общей шиной, третьи входы Т1ретьей и четвёртой групп входов по и элемента И-ИЗШ-НЕ соединены с прядай:шх&ддм третьего ЗК-триггера. Источники информации, принятые во внимание при экспертизе 1.Патент США 3530284, кл. 235-92, 1974. 2.Лейнов М. Л. и др. Цифровые делители частоты на логических элементах. М. „ Энергия 1975, с. 73, рис. 3-16 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования кода цифрового сигнала | 1983 |

|

SU1141580A1 |

| Десятичный счетчик | 1977 |

|

SU738176A1 |

| Устройство для вычитания частот двух независимых сигналов | 1976 |

|

SU599227A1 |

| Телевизионное устройство для измерения координат пятна | 1987 |

|

SU1450136A1 |

| Устройство для дистанционногоизМЕНЕНия ВыХОдНОгО НАпРяжЕНиядЕКОдиРующЕгО пРЕОбРАзОВАТЕля | 1978 |

|

SU845257A1 |

| Устройство для синхронизации импульсов | 1979 |

|

SU841099A1 |

| Синтезатор частот | 1976 |

|

SU799101A1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2110146C1 |

| Устройство для одноканального управления тиристорным преобразователем | 1983 |

|

SU1137560A1 |

| Десятичный счетчик | 1977 |

|

SU699677A1 |

Авторы

Даты

1980-11-30—Публикация

1977-11-10—Подача