напряжений ЦДЛ 15, источника 6 опорного напряжения, эапитывающего ИДП 15 и генератор 25, Для уменьшения нелинейности заряда накопительного элемента 26 преобразователь содержит схему фазировки тактовой частоты генератора 2 тактовых импульсов на триггерах 3,4, элементах И 5,6, элементе НЕ 10 и элементе задержки 9. Для компенсации внутренней задержки

1

Изобретение относится к информационно-измерительной технике и может быть использовано в оптической локации и радиолокации, при построении средств испытаний и регулировки различных радиоэлектронных устройств, а также в измерительной технике и в различных устройствах автоматики.

Цель изобретения - повышение точности формирования временного интервала и расширение диапазона преобразования .

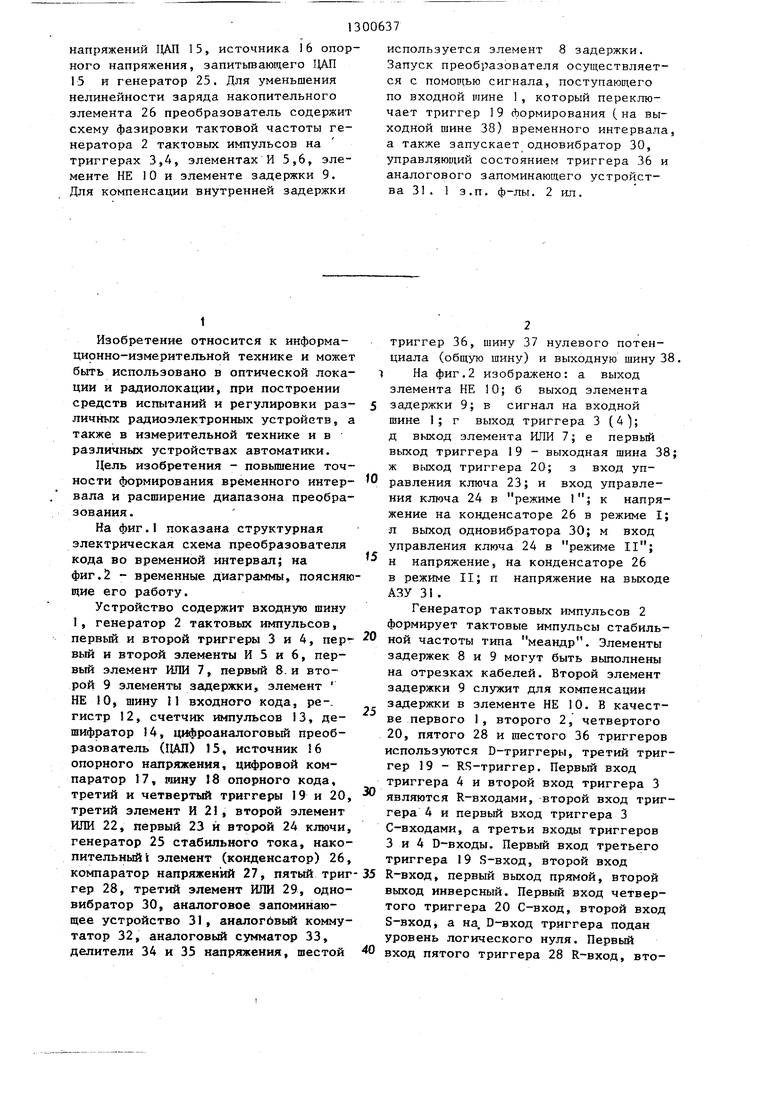

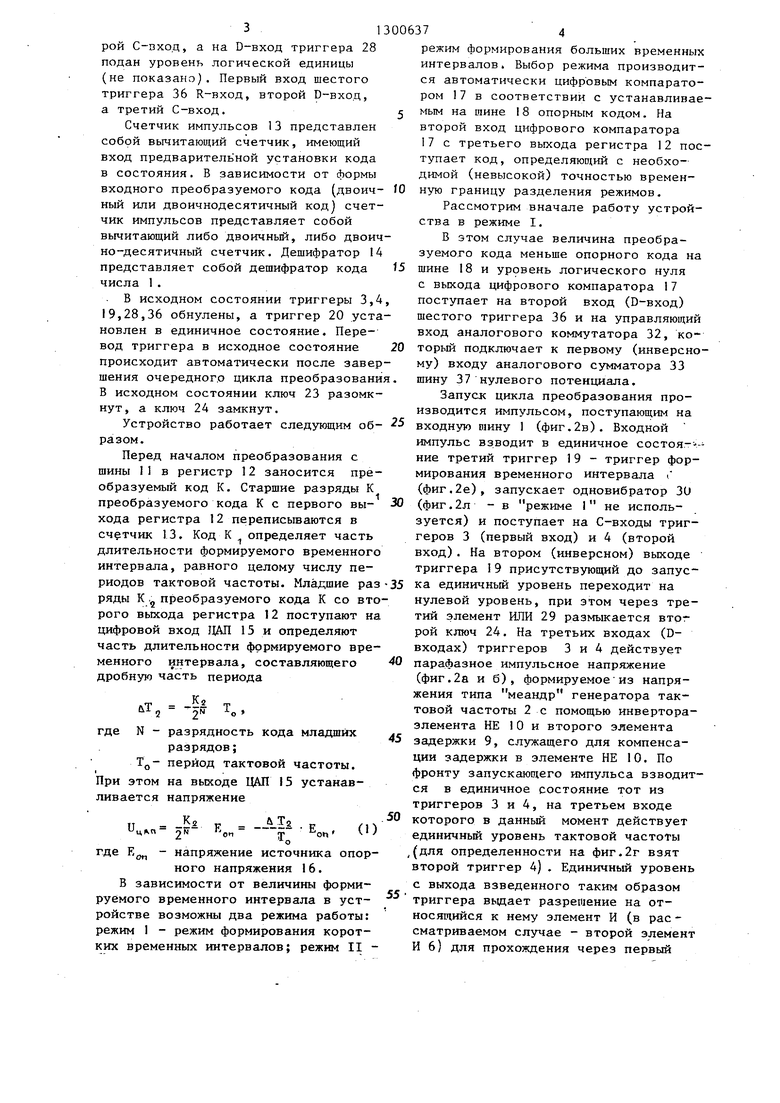

На фиг.1 показана структурная электрическая схема преобразователя кода во временной интервал; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство содержит входную шину 1, генератор 2 тактовых импульсов, первый и второй триггеры 3 и 4, первый и второй элементы И 5 и 6, первый элемент ИЛИ 7, первый 8. и второй 9 элементы задержки, элемент НЕ 10, шину 11 входного кода, ре-, гистр 2, счетчик импульсов 13, дешифратор 14, цифроаналоговый преобразователь (ЦДЛ) 15, источник 56 опорного напряжения, цифровой компаратор 17, шину 18 опорного кода, третий и четвертый триггеры 19 и 20, третий элемент И 2, второй элемент ИЛИ 22, первый 23 и второй 24 ключи, генератор 25 стабильного тока, накопительный элемент (конденсатор) 26, компаратор напряжений 27, пятый триггер 28, третий элемент ИЛИ 29, одно- вибратор 30, аналоговое запоминающее устройство 31, аналоговый коммутатор 32, аналоговый сумматор 33, делители 34 и 35 напряжения, шестой

используется элемент 8 задержки. Запуск преобразователя осуществляется с помощью сигнала, поступающего по входной шине 1, который переключает триггер 19 формирования ( на выходной шине 38) временного интервала а также запускает одновибратор 30, управляющий состоянием триггера 36 и аналогового запоминающего устройства 31 . 1 з.п. ф-лы, 2 ил.

триггер 36, шину 37 нулевого потенциала (общую шину) и выходную шину 38. На фиг.2 изображено: а выход

элемента НЕ 10; б выход элемента задержки 9; в сигнал на входной шине 1; г выход триггера 3 (4); д выход элемента ИЛИ 7; е первый выход триггера 19 - выходная шина 38; ж выход триггера 20; з вход управления ключа 23; и вход управления ключа 24 в режиме к напряжение на конденсаторе 26 в режиме I; л выход одновибратора 30; м вход управления ключа 24 в режиме

н напряжение, на конденсаторе 26 в режиме II; п напряжение на выходе АЗУ 31.

Генератор тактовых импульсов 2 формирует тактовые импульсы стабильной частоты типа меандр. Элементы задержек 8 и 9 могут быть выполнены на отрезках кабелей. Второй элемент задержки 9 служит для компенсации задержки в элементе НЕ 10. В качестве первого I, второго 2, четвертого 20, пятого 28 и шестого 36 триггеров спользуются D-триггеры, третий триггер 19 - RS-триггер. Первый вход триггера 4 и второй вход триггера 3 являются R-входами, второй вход триггера 4 и первый вход триггера 3 С-входами, а третьи входы триггеров 3 и 4 D-входы. Первый вход третьего триггера 19 S-вход, второй вход

R-вход, первый выход прямой, второй выход инверсный. Лервый вход четвертого триггера 20 С-вход, второй вход S-вход, а на, D-вход триггера подан уровень логического нуля. Первый

вход пятого триггера 28 R-вход, вто

рой С-вхоц, а на D-вход триггера 28 подан уровень логической единицы (не показано). Первый вход шестого триггера 36 R-вход, второй D-вход, а третий С-вход.

Счетчик импульсов 13 представлен собой вычитаюошй счетчик, имеющий вход предварительной установки кода в состояния. В зависимости от формы входного преобразуемого кода (двоич- ный или двоичнодесятичный код) счетчик импульсов представляет собой вычитающий либо двоичньй, либо двоично-десятичный счетчик. Дешифратор 14 представляет собой дешифратор кода числа 1.

. В исходном состоянии триггеры 3,4 19,28,36 обнулены, а триггер 20 установлен в единичное состояние. Перевод триггера в исходное состояние происходит автоматически после завершения очередного цикла преобразования В исходном состоянии ключ 23 разомкнут, а ключ 24 замкнут.

Устройство работает следующим об- разом.

Перед началом преобразования с шины 11 в регистр 12 заносится преобразуемый код К. Старшие разряды К преобразуемого кода К с первого вы- хода регистра 12 переписываются в счетчик 13. Код К определяет часть длительности формируемого временного интервала, равного целому числу периодов тактовой частоты. Младшие раз-35 ка единичный уровень переходит на

ряды К .у преобразуемого кода К со второго выхода регистра 12 поступают на цифровой вход 1Щ1 15 и определяют часть длительности формируемого временного интервала, составляющего дробную часть периода

ЬТ,

- К2 „ ofj -о

2 2 N - разрядность кода младших

разрядов;

TQ- период тактовой частоты. этом на выходе ЦАП 15 устанавется напряжение

и

где Е

НЛП

Кг г 2 J

он

(О

on

- напряжение источника опорного напряжения 16. В зависимости от величины формируемого временного интервала в устройстве возможны два режима работы: режим 1 - режим формирования коротких временных интервалов; режим II режим формирования больших временных интервалов. Выбор режима производится автоматически цифровым компаратором 17 в соответствии с устанавливаемым на шине 18 опорным кодом. На второй вход цифрового компаратора 17 с третьего выхода регистра 12 поступает код, определяюп1ий с необходимой (невысокой) точностью временную границу разделения режимов.

Рассмотрим вначале работу устройства в режиме I.

В зтом случае величина преобразуемого кода меньше опорного кода на шине 18 и уровень логического нуля с выхода цифрового компаратора 17 поступает на второй вход (D-вход) шестого триггера 36 и на управляющий вход аналогового коммутатора 32, который подключает к первому (инверсному) входу аналогового сумматора 33 шину 37 нулевого потенциала.

Запуск цикла преобразования производится импульсом, поступающим на входную тину 1 (фиг.2в). Входной импульс вз.водит в единичное состоя-ч-- ние третий триггер 19 - триггер формирования временного интервала Г (фиг.2е), запускает одновибратор 3U (фиг.2л - в режиме 1 не используется) и поступает на С-входы триггеров 3 (первый вход) и 4 (второй вход). На втором (инверсном) выходе триггера 19 присутствующий до запус40

45

50

55

нулевой уровень, при зтом через третий элемент ИЛИ 29 размыкается вто рой ключ 24. На третьих входах (D- входах) триггеров 3 и 4 действует парафазное импульсное напряжение (фиг.2а и б), формируемое из напряжения типа меандр генератора тактовой частоты 2 с помощью инвертора- элемента НЕ 10 и второго элемента задержки 9, служащего для компенсации задержки в элементе НЕ 10. По фронту запускаюп1его импульса взводится в единичное состояние тот из триггеров 3 и 4, на третьем входе которого в данный момент действует единичный уровень тактовой частоты ,(для определенности на фиг.2г взят второй триггер 4). Единичный уровень

с выхода взведенного таким образом триггера выдает разрешение на относящийся к нему элемент И (в рас - сматриваемом случае - второй элемент И 6) для прохождения через первый

элемент ИЛИ 7 на счетный вход счетчика 13, инверсной по отношению к третьему входу этого триггера тактовой частоты (фиг.2д), В результате чего, запускающий импульс будет всегда Опережать первый счетный импульс тактовой частоты на выходе nejiBoro элемента ИЛИ 7 на время лТ, не меньше полупериода тактовой частоты

Т (для определенности по фиг.2д будем полагать, что счетчик 13 срабатывает по спаду тактового импульса).

Первым тактовым импульсом, поступающим с выхода первого элемента ИЛИ 7 и задержанным на время дТ,,, в первом элементе задержки 8, четвертый триггер 20 из исходного единичного состояния переводится в нулевое (фиг.2ж). При этом на выходе третьего элемента И 21 формируется импульс длительностью лХ ьТ + + а Т., которьй поступает через второй элемент ИЛИ 22 на управляющий вход первого ключа 23 (фиг.2з). Так как к этому времени второй ключ 24 выключен, то от генератора стабильного тока 25 (преобразователя напряжения в ток) происходит линейный заряд конденсатора 26 до напряжения

(фиг.2к).

г ,-н дт,,)

ДТ,,

(1)

где а Едп - ток генератора ста-.

бильного тока:; С - величина емкости кон

денсатора 26; а - коэффициент пропорциональности преобразования напряжения в ток генератора 25 (определяется соотношением резисторов преобразователя). После окончания управляющего импульса ключ 23 вновь размыкается и на конденсаторе 26 фиксируется напря жение Uc,.Так как в устройстве всегда обеспечивается условие лТ, 1/2 Тд, то исключается, таким образом, огаибки преобразования за счет нелинейности зар5ща конденсатора 26, имевшие место при малых и близких к нулю значениях его времени заряда у прототипа.

10

20

25

Счетчик 13 осу1чествляет последовательное вычитание единиц из кода К,. По достижении счетчиком 13 состоя- кия, соответствующего числу 1, сра5 батывает дешифратор 14 кода числа 1, при этом взведенный один из триггеров 3 или 4 (в рассматриваемом примере триггер 4) по R-входу сбрасывается в нулевое состояние (фиг,2г), чем прекращается формирование пачки счетных импульсов, состоящей из(К,-1) импульсов (фиг.2д).

Импульс с выхода дешифратора I4 поступает также на первый вход С (R-вход) шестого триггера 36 и второй вход пятого триггера 28. В режиме I шестой триггер 36 не меняет своего исходного нулевого состояния, так как на его второй вход (В-вход) с цифрового компаратора 17 заведен уровень логич:еского нуля, и воздействие импульса одновибратора 30 (фиг,2л) по третьему входу (С-вхо- ду) триггера 36 лишь подтверждает его нулевое состояние. То же самое происходит и от импульса дешифратора I4 по первому входу триггера 36. Пятый триггер 28 под действием импульса дешифратора 14 взводится в единичное состояние. При этом с некоторой задержкой Т через второй элемент ИЛИ вновь замыкается ключ 23 (фиг.2в) и начинается второй в цикле преобразования линейный заряд конден3-5 сатора 26. Задержка Т определяется задержкой в счетчике 13, дешифраторе 14, триггере 28 и элементе ИЛИ 22 и измеряется по отношению к К -1 импульсу счетной тактовой частоты.

По достижению напряжения на конденсаторе 26 уровня порогового напряжения (фиг.2к) , поступающего на первый вход компаратора напряжения 27, компаратор срабатьшает и с некоторой задержкой 12 триггеры 19, 20 и 28 сбрасьшаются в исходные состояния. При этом на выходной шине (фиг.2е) 38 заканчивается формирование временного интервала, четвертый триггер 20 устанавливгнется в единичное состояние (фиг.2ж), пятьй триггер 28 прекращает выработку второго управлякщего импульса для ключа 23, а устанавливающийся на инверсном выходе триггера 19 единичный уровень через третий элемент ИЛИ 29 (фиг.2и) замьпсает ключ 24 и конденсатор 26 быстро разряжается до нулевого уров30

40

50

ня. На этом цикл преобразования заканчивается.

Формируемый устройством временной интервал при линейном заряде конденсатора 26 с коэффициентом а Е /с из выражения ( I) при установке порога

.а. с

(2.1,+

T,)

(2) бусоответствии с фиг.2, составлять;

ЛТ,+ () Т„+7,

.

а

с

к,т,+ м,-ь

(

4)

U Т

Выбрав значение задержки в первом элементе, равной сумме задержек в элементах устройства Т,,,, С, -it , можно, таким образом, полностью исключить систематическую погрешность преобразования, т.е. формируемая задержка равна

К.

TO

-KJ- 2

На фиг.2к пунктиром показан случай работы устройства без компенсации ( О). В этом случае возникла бы систематическая ошибка

t t + с -.

от 1 1

Для того, чтобы устройство было работоспособным в том случае, когда 4.Т iT + лТ, Т , счетчик- 13 до лТз,,т„

считъшает до единичного состояния, а не до нулевого, как в известном преобразователе. Недостающее значение формируемой счетчиком задержки компенсируется соответствукнцим увеличением времени дозаряда конденса- тора 26 путем соответствующего увеличения порога .i на величину, пропорциональную TOПороговое напряжение и,,, задается аналоговым сумматором 33, оно рав но в режиме I сумме двух напряжений, поступай)р;их на второй и третий входа сумматора 33

и

flOP

™lUc.An

где mm - коэффициенты делений делителей напряжений 34 и 35.

Приравняв ( 2) и ( 3), находим требуемые значения коэффициентов деления делителей 34 и 35

-а

m

m

10

Г5

20

25

ЗО

40оКак видно, 3d счет того, что одно и то же опорное напряжение источника 16 используется для питания ЦАП 15, формирования порога элементами 33 35и формирования преобразователем напряжение-ток 25 зарядного тока конденсатора 26, изменение этого напряжения в процессе эксплуатации не будут сказываться на точности формирования временного интервала. Максимальная длительность формируемого временного интервала в режиме I, определяется допустимым для заданной точности преобразования саморазрядом конденсатора .26. На основании этого выбирается значение опорного кода, устанавливаемого (например, с помощью соответствующих перемычек) на п,ррвом входе цифрового компарато- г

ра 17.

В режиме II работы устройства значение преобразуемого кода ока- зьшается больше значения опорного кода и на выходе цифрового компаратора 1 7 поэтому устанавливается единичный уровень, поступающий на второй вход (D-вход) шестого триггера

36и на управляющий вход аналогового коммутатора, который подключает

к первому (инверсному) входу анало- . гового сумматора 33 выход аналогового запоминаюо;его устройства 31. Работа устройства в этом режиме отличается от режима I лишь управлением зар я- да-разряда конденсатора 26 и другим значением порога.

Установившееся при запуске устройства напряжение (фиг.2н) на конденсаторе 26

40-45

50

55

(-Т,

Т,з.)

о, е

в течение времени действия импульса одновибратора (фиг.2л) запоминается в аналоговом запоминающем устройстве 31 (фиг.2п).

Длительность импульса одновибратора 30 выбирается, исходя из требуемого значения времени выборки аналогового запоминающего устройства, и реально лежит в диапазоне единицы- десятки МКС. Спадом импульса одновибратора шестой триггер 36 взводится в единичное состояние, так как в режиме II на его втором входе (D-вхо- де) присутствует единичный уровень. Возникающий на выходе триггера 36 единичньй уровень через третий элемент ИЛИ 29 (фиг.2м)-поступает на

управляющий вход ключа 24, который замыкает конденсатор 26 .и разряжает его. При срабатывании дешифратора 14 шестой триггер 36 сбрасьгаается в исходное нулевое состояние, ключ 24 . размыкается и конденсатор 26 начинает линейно заряжаться, также, как и в режиме I с тем только отличием, что заряжается он не с уровня Ut,, а с нулевого уровня (фиг.2н). Для формир ования временного интервала, заданным преобразуемым кодом, в этом случае необходимо понизить порог на величину Uci т.е.

и.

и

пор 2

ПОР-,

:- с,.

Такую операцию производит аналоговый сумматор 33, на первый (инверс ный) вход которого с аналогового запоминающего устройства 31 поступает постоянное напряжение С точки зрения обеспечения работы режима II опорный код должен соответствовать временному интервалу, величина кото- 25 рого не меньше суммы времени выборJ5 . одновременном обеспечении режима формирования коротких временных интервалов (расширение диапазона преобразования) .

20 Формула изобретения

.Преобразователь кода во временной интервал, содержащий генератор тактовых импульсов, первый.и второй ключи, первый, второй, третий, четвертый, пятый и шестой триггеры, пер вый элемент И, первый вход которого соединен с вькодом первого триггера, первый вход которого объединен с первым входом третьего триггера и является входной шиной, а второй вход первого триггера объединен с первым входом второго триггера и подключен к выходу.дешифратора, вход Таким образом, за счет формирова- которого соединен с выходом счетчика

ки 31, времени установления аналогового сумматора 33 и времени разряда конденсатора 26.

Достижимость поставленной цели подтверждается приведенными расчетами и диаграммами работы, а также применением известных технических эле- ментов и узлов.

30

ния с помощью парафазной сетки такто вых импульсов зарядных интервалов времени не менее полупериода такто- вой частоты исключаются ошибки из-за нелинейности заряда конденсатора в области малых времен. За счет использования в качестве источника стабильного тока преобразователя напряже- . ния-ток и запитки ЦАП, источника стабильного тока (преобразователя напряжение - ток) от одного источника опорного:напряжения, а также использования напряжения источника опорного напряжения для формирования с помощью первого и второго делителей напряжений и аналогового сумматора порога компаратора напряжений,устраняется влияние на точность формирования нестабильности источника опорного напряжения, т.е. к нему не предъявляется специальных требований по стабильности. За счет увеличения при запуске устройства времени заряда

конденсатора на время, равное сумме задержек в элементах устройства, одновременно с использованием дешифратора числа 1 при соответствующем

компенсирующем увеличении порога компаратора напряжений достигается полное устранение систематической погрешности формирования временных интервалов, а за счет введения аналогового запоминающего устройства с

одновибратором импульса выборки, аналогового коммутатора и цифрового ком- парстора обеспечивается формирование больших временных интервалов при

. одновременном обеспечении режима формирования коротких временных интервалов (расширение диапазона преобразования) .

Формула изобретения

0

5

0

5

импульсов, первый вход которого соединен с первым выходом регистра, вход которого является шиной входного кода, а второй выход подключен к первому входу гщфроаналогового преобразователя, второй вход которого соединен с выходом источника опорного напряжения, и первый элемент задержки, выход которого соединен с первым входом четвертого триггера, второй вход которого объединен с вторым входом третьего триггера и i подключен к выходу компаратора напряжений, первый вход которого объединен с первым входом второго ключа и первым вьЕводом накопительного элемента и подключен к выходу первого ключа, первый вход которого соединен с выходом генератора стабильного тока, отличающийся тем, что, с целью повьш1ения точности формирования временного интервала и расширения диапазона преобразования, в него

11 1300637

Е, второй элемент и третий элементы И, третий элементы 1ШИ, нающее устройство, атор, аналоговый и .второй делители ибратор и цифровой й вход которого явного кода, второй третьему выходу соединен с первым

fO

г н х к г г ш г п в д в н н в в п с т с п з м т д м т до кл им

входом аналогового коммутатора, второй вход которого соединен с выходом аналогового запоминающего устройства третий вход является шиной нулевого потенциала, а выход подключен к первому входу аналогового сумматора, второй вход которого через первый делитель напряжения соединен с выходом цифроаналогового преобразователя , выход подключен к второму входу компаратора напряжений, а третий вход соединен с вьшодом второго делителя напряжения, вход которого объединен с входом генератора стабильного тока и подклхгчен к выходу источника опорного напряжения, - при этом первый вход аналогового запоминающего устройства соединен с выходом первого ключа, а вькод компаратора напряжений - с первым входом пятого триггера, второй вход которого объединен с первым входом шестого триггера и подключен к выходу дешифратора, а выход пятого триггера соединен с первым входом второго элемента ИЛИ, выход которого подключен к второму входу первого ключа, а второй вход - к выходу третьего элемента И, первый вход которого соединен с выходом четвертого триг12

O

5

0

5

0

5

0

гера, а второй вход является выходной шиной и подключен к первому выходу третьего триггера, второй выход которого соединен с первым входом третьего элемента ИЛИ, выход которого подключен к второму входу второго ключа, а второй вход - к выходу шестого триггера, второй вход которого соединен с выходом цифрового компаратора, а третий вход объединен с вторым входом аналогового запоминающего устройства и подключен к выходу одновибратора, вход которого объе- динен с вторым входом второго триггег ра и является входной шиной, причем выход второго ключа и второй :выход накопительного элемента являются шиной нулевого потенциала, а вход первого элемента задержки объединен с вторым входом счетчика импульсов, и подключен к выходу первого элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, а второй вход - с выходом второго элемента И, первый вход которого объединен с третьим входом первого триггера и подключен к выходу второго элемента задержки, а второй вход второго элемента И соединен с выходом второго триггера, третий вход которого объединен с вторым входом первого элемента И и подключен к выходу элемента НЕ, вход которого объединен с входом второго элемента задержкн и подключен к выходу генератора тактовых импульсов.

2. Преобразователь по п., о т - личающийся тем, что генератор стабильного тока выполнен на преобразователе напряжение - ток.

Фие.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1984 |

|

SU1247855A1 |

| Преобразователь двоичного кода во временной интервал | 1983 |

|

SU1115223A1 |

| СПОСОБ ИЗМЕРЕНИЯ ФИЗИЧЕСКОГО ПАРАМЕТРА В СКВАЖИНЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013534C1 |

| Кольцевая система громкоговорящей связи с временным разделением каналов | 1990 |

|

SU1699359A3 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Генератор пилообразного напряжения с переменной крутизной | 1987 |

|

SU1495982A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО КОНТРОЛЯ ТЕМПЕРАТУРЫ | 2015 |

|

RU2631018C2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

Изобретение относится к информационно-измерительной технике и может быть использована, например, в радиолокации и в устройствах автоматики. Целью изобретения является повьшение точности формирования временного интервала и расширение диапазона преобразования. Преобразователь работает в двух режимах-формиррвания коротких и больших временных интервалов. Выбор режима осуществляется автоматически цифровым компаратором 17, на входы которого по шине 18 опорного кода и с выхода регистра 12, поступают сравниваемые коды. Код, поступающий по шине 11 входного кода в регистр 12 записывается оттуда в цифроаналоговый преобразователь (ЦАП) 15 и в счетчик 13 импульсов, выход которого соединен с дешифратором 14. Триггер 36 и аналоговый коммутатор 32 управляют-совместно с триггерами 19,20,28, элементом И 21,- элементами ИЛИ 22, 29 и ключами 23, 24 зарядом-разрядом накопительного элемента (конденсатора) 26 с использованием генератора 25 стабильного тока, аналогового запоминающего устройства (АЗУ) 31, аналогового сумматора 33 и делителей 34, 35 напряжения. Порог срабатьшания компаратора 27 напряжений зависит от величин е (Л оо о: со

| Преобразователь код-временной интервал | 1983 |

|

SU1115225A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода во временной интервал | 1983 |

|

SU1115223A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-30—Публикация

1985-07-11—Подача