Изобретение относится к вычислительной и информационно-измерительной технике и может быть использовано в автоматизированных системах регистрации быстропротекающих процессов.

Цель изобретения - расширение фуню циональных возможностей, повышение быстродействия при регистрации аналоговых сигналов и уменьшение динамической погрешности при регистрации аналоговых и цифровых сигналов за счет введения дополнительных режимов работы и промежуточной буферизации данных.

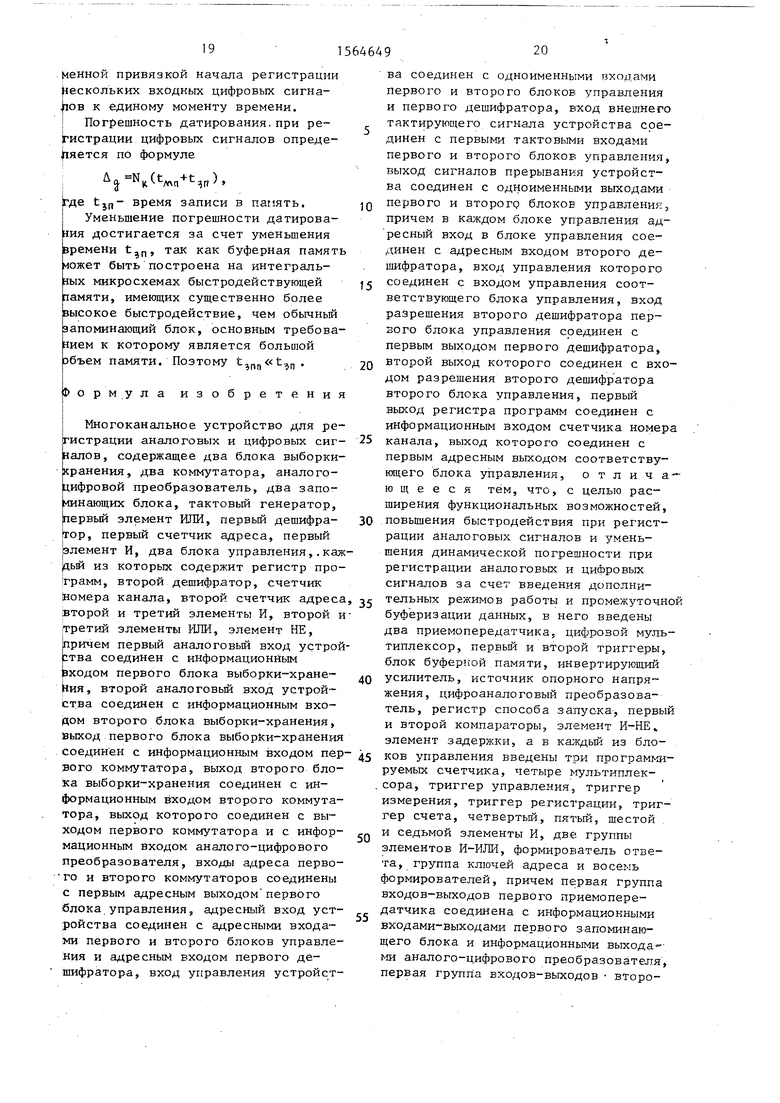

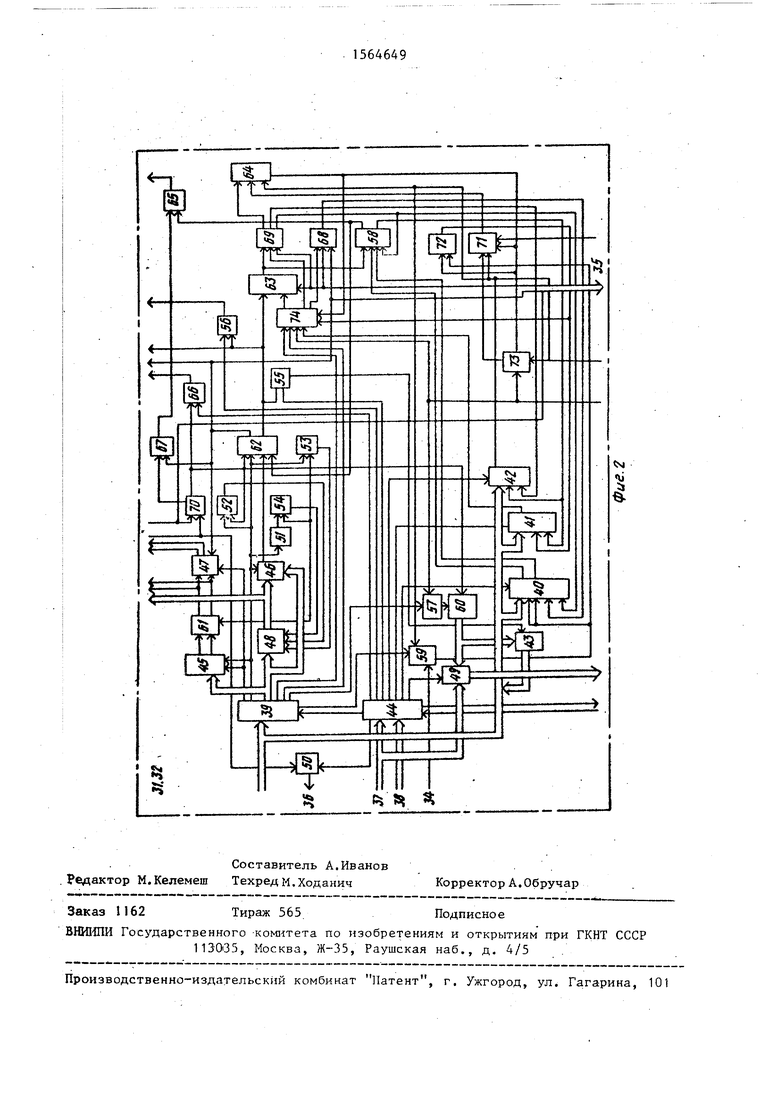

На фиг. 1 представлена блок-схема предложенного устройства; на фиг,,2 - функциональная схема блока управления.

Многоканальное устройство имеет две группы 1, 2 аналоговых входов, группу 3 цифровых -входов и содержит (фиг. 1) первый 4 и второй 5 блоки выборки-хранения, первый 6 и второй 7 коммутаторы, аналого-цифровой преобразователь 8, входы-выходы 9 данных, первый 10 и второй 11 приемопередатчики, первый 12 и второй 13 запоминающие блоки, блок 14 буферной памяти, цифровой мультиплексор 15, первый 16 счетчик адреса, элемент И-НЕ 17, элемент 18 задержки, первый элемент И 19, тактовый генератор 20, первый 21 и второй 22 триггеры, цифроаналоговый преобразователь 23, регистр 24 способа запуска, первый 25 и второй 26 компараторы, источник 27 опорного напряжения, неинвертирующий усилитель 28, инвертирующий усилитель 29, первый элемент ИЛИ 30, первый 31 и второй 32 блоки управления, первый дешифратор 33, а также имеет вход 34 внешнего тактирующего сигнала, выход 35 сигналов прерыва5

0

5

0

5

0

5

0

5

ния, выход 36 управляющего сигнала, выход 37 адреса, вход 38 управления.

Блоки 31 и 32 управления содержат каждый (фиг. 2) регистр 39 про грамм, первый 40, второй 41 и третий 42 программируемые счетчики, группу 43 ключей адреса, второй дешифратор 44, первый 45, второй 46, третий 47 и четвертьй 48 мультиплексоры, счетчик 49 номера канала, формирователь 50 ответа, элемент НЕ 51, второй 52, третий 53, четвертьй 54, пятый 55, шестой 56 и седьмой 57 элементы И, первую 58 и вторую 59 группы элементов И-ИЛИ, второй счетчик 60 адреса, триггер 61 управления, триггер 62 измерения, триггер 63 регистрации, триггер 64 счета, второй 65 и третий 66 элементы ИЛИ, первьй 67, второй 68, третий 69, четвертьй 70, пятый 71, шестой 72, седьмой 73 и восьмой 74 формирователи.

Многоканальное устройство для регистрации работает следующим образом,

Для регистрации аналоговых сигналов используется принцип автоматической цифровой регистрации, включающий: дискретизацию процесса во времени с заданными параметрами дискретизации и одновременную фиксацию мгновенных значений электрических сигналов; измерение зафиксированных мгновенных значений сигналов и получение результатов измерений в двоичном коде; запоминание результатов измерения в запоминающих блоках.

Таким образом, в результате выполненной регистрации в запоминающем блоке находится образ исследуемого процесса в виде массива мгновенных значений входных сигналов, снятых через заданные интервалы дискретизации.

программно задаются от ЭВМ режимы ре гистрации в каждый блок 31, 32 управления. Первый дешифратор 33 под воздействием управляющих сигналов машинной магистрали ввода или вывода, поступающих на вход 38 управления, дешифрует адрес, поступающий с входа 37 адресов ЭВМ, и вырабатывает сигналы выбора первого или второго блоков 31, 32 управления. Сигнал выбора разрешает работу второго дешифратора 44, которьй под воздействием управляющих сигналов ввода или вывода вырабатывает сигналы управления отдельными функциональными узлами в зависимости от значений разрядов входа 37 адресов ЭВМ. Формирователь 50 ответа при наличии обращения от ЭВМ, т.е. поступлении на него выходного сигнала второго дешифратора 44 или сигнала готовности блока 12 или 13, выдает ответный сигнал обмена с ЭВМ по выходу 36 управления с задержкой относительно сигналов обращения ввода или вывода.

Блоки 31, 32 управления обеспечивают два режима коммутации входных измерительных каналов: адресный, когда измеряются входные данные одного канала с программируемым числом дискретизаций; циклический с программируемым числом каналов в дикле и числом дискретизаций каждого канала, а также три режима регистрации: нормальный, когда регистрация производится после прихода сигналов предварительного пуска и пуска на одном или двух участках регистрации с программируемыми числом и интервалом дискретизаций; задержанный, когда после прихода сигналов предварительного пуска и пуска выполняется задержка начала регистрации, величина которой программируется, а затем регистрация входного сигнала на участке регистрации с программируемыми числом и интервалом дискретизаций; предпусковой, когда регистрация начинается в момент прихода сигнала предварительного пуска и состоит из двух участков регистрации: предпусковом и послепусковом с программируемыми интервалом дискретизации для двух участков и числом дискретизаций на послепусковом участке регистрации , Число дискретизаций на предпусковом участке может быть любым, в том чис0

5

0

тов измерений, которое может ститься в запоминающем б тюке. В этом ,случае производится стирание самых старых результатов измерений и замена их новыми.

Вид режима регистрации и его параметры храняться в регистре 39 программ и трех программируемых счетчиках 40, 41 и 42. В них записывается информация с входа режима. Приемопередатчики 10 или 11 обеспечивают связь между входом-выходом 9 данных с ЭВМ к входом режима. Сигналы записи в регистр и программируемые счетчики вырабатываются вторым дешифратором 44

Регистр 39 программ определяет следующие параметры регистрации ре- 0 жим опроса датчиков (адресной, обеспечивающий измерение по одг ому каналу, и циклический, обеспечивающий измерение по группе каналов); вид выборки аналоговых входных сигналов (нормальная, или конвейерная); код номера канала в адресном режиме или число каналов в цикле; режим регист- ращ ,т предпусковой; режим регистрации задержанный; блочная запись в запоминающий блок; вид тактирования (втттг екний или внешний) о

Программируемый счетчкк 40 служит для программной установки частоты дискретизации и работает в режиме делителя частоты.

Программируемый счетчик 41 служит для программной установки задержки импульсов запуска аналого-цифрового преобразователя относительно сигнала пуска.

Программируемый счетчик 42 служит для программной установки числа дискретизаций на одном канале в адресном режиме к числа дискретизаций на каждом канале в циклическом режиме.

После программирования устройство осуществляет процесс измерения и регистрации входных данных.

Для начала работы требуются сигналы предварительного пуска и пуска для обеспечения синхронизации процесса регистрации с исследуемым процессом. Устройство обеспечивает формирование не только сигнала пуска, выполняемого вручную оператором или по программе от процессора, но и по внешнему аналоговому сигналу, в качестве которого используется

5

0

5

0

5

один из входных измеряемых сигналов По внешнему аналоговому сигналу пуск производится в момент пересечения аналоговым сигналом программно установленного уровня запуска на положительном и/или отрицательном наклоне входного сигнала.

Цифреаналоговый преобразователь, принимающий информацию с входа 9 данных, по сигналу записи, вырабатываемому первым дешифратором 33, выдает на вход компараторов 25, 26 аналоговый сигнал, величина которого в зависимости от входного кода на входе 9 данных программируется от предельного положительного до предельного отрицательного значения. Входной код определяется требуемым уровнем запуска и способом запуска. На первый компаратор 25 подается входной сигнал через неинвертирующий усилитель 28, а на второй 26 - через инвертирующий усилитель 29.

При равенстве входного аналогового сигнала и запрограммированного уровня запуска с выхода преобразователя 23 один из компараторов 25, 26 формирует выходной сигнал, поступающий на вход первой схемы ИЛИ 30, на которую поступает также сигнал цифрового пуска, программируемого в регистре 24 способа запуска. Компараторы 25, 26 управляются двумя сигналами, определяющими способ запуска регистрации по аналоговому сигналу. Способ запуска программируется в регистре 24 способа запуска, в который информация записывается с входа 9 данных через ЭВМ по сигналу записи первого дешифратора 33.

Формирование сигнала пуска по аналоговому сигналу производится в мо-, мент пересечения аналоговым сигналом уровня запуска в направлении нарастания, когда наклон сигнала положительный, или падания, когда наклон сигнала отрицательный.

Формирователь 73 воспринимает сигнал с выхода регистра 24 способа запуска, а формирователь 71 - сигнал с выхода первой схемы 30 ИЛИ при наличии сигнала предпуска. Триггер 64 счета формирует сигнал счета по приходу первого тактового импульса генератора 20 тактовых импульсов при наличии сигнала пуска с выхода формирователя 71. По приходу следующего тактового импульса после установления триггера 64 счет формирования сигналов предпуска и пуска заканчивается.

Рассмотрим различные режимы per гистрации.

В задержанном режиме регистрации ча выходе регистра 39 программ уста- ьавливаются: единичный сигнал признака Режим задержанный и нулевой сигнал признака Режим предпусковой, которые поступают на входы восьмого формирователя 74. В задержанном pe- чме сигнал счета с выхода триггера

5 64 счета проходит сразу через формирователь 74 на вход формирователя 68, который Формирует по нему сигнал разрешения работы первого канала программируемого счетчика 40. В послед0 нем с входа режима программно устанавливается частота дискретизации ИД1 и он работает в режиме делителя частоты.

На тактовый вход поступают такто5 вые импульсы с выхода второй группы элементов И-ИЛИ 59. Она пропускает либо внутренние тактовые импульсы от генератора 20 тактовых импульсов, либо внешние тактовые импульсы по

0 входу 34 внешнего тактирования в зависимости от вида тактирования, запрограммированного в регистре 39 программ. Внешнее тактирование используется для привязки моментов дискретизации аналоговых сигналов или запоминания цифровых сигналов к внешнему опорному сигналу. На выходе программируемого счетчика 40 частоты получаются импульсы дискретизации

д ИД1, следующие с частотой, равной частоте тактовых импульсов, деленной на запрограммированный коэффициент деления.

5 В задержанном режиме регистрации формирователь 69 разрешает прохож- ( дение импульсов дискретизации ИД1 на выход первой группы элементов И-ИЛИ 58 и на вход программируемого счетчика 41 в качестве тактовых импульсов. В-программируемом счетчике 41 с входа режима программируется задержка запуска измерений преобразователя 8 в первом блоке 31 управления и начала счета счетчика 16 адреса промежуточной памяти во втором блоке 32 управления относительно сигнала пуска. Сигнал разрешения работы этого программируемого счетчика поступает

5

0

5

с выхода формирователя 72 после срабатывания триггера 64 счета по приходу очередного тактового импульса генератора 20 тактовых импульсов.

После поступления на вход программируемого счетчика 41 числа импульсов дискретизации, определяющих запрограммированный интервал задержки, на выходе программируемого счетчика 41 возникает импульс конца задержки, который проходит через формирователь 74 на вход триггера 63 регистрации, устанавливая его в единичное состояние, одновременно это приводит к появлению сигнала на выходе формирователя 69 и сбросу триггера 64 счета, что снимает сигнал разрешения работы программируемого счетчика 41.

Кроме того, выходной сигнал формирователя 69 поступает на вход программируемого счетчика 42, разрешая его работу. В качестве тактовых импульсов используются выходные импульсы дискретизации ИД1 программируемого счетчика 40 частоты. После выполнения запрограммированного числа дискретизаций на выходе программируемого счетчика 42 появляется сигнал конца программы, который поступает на вход триггера 63 регистрации, заканчивая формирование сигнала регистрации и снимается сигнал разрешения работы программируемого счетчика 42, При появлении сигнала конца программы формирователь 68 прекращает разрешение работы программируемого сметчика 40 и прекращается выдача импульсов дискретизации ИД1. Импульсы дискретизации ИД1 проходят через первую группу элементов 58 И-ИЛИ и затем второй элемент 65 ИЛИ, образуя сигналы запуска преобразователя 8 для первого блока 31 управления или счетчика 16 адреса блока буферной памяти для второго блока 32 управления

1

В задержанном режиме регистрации

после прохода сигналов пуска и пред- пуска выполняется задержка начала регистрации, а по ее окончании - регистрация с запрограммированными числом дискретизаций и частотой дискретизации. Импульсы дискретизации, формируемые на интервале задержки, не вызывают дискретизацию входного сигнала, а используются для формирования определенной длительности участка задержки. Последующие импульсы

дискретизации вызывают кзнерение входного сигнала.

В нормальном режиме регистрации предусматривается возможность работы с различной скоростью дискретизации на двух участках ре- истрации. В том случае в программируемом счетчике 41 программируется число дискретиза- Q цнй с первой скоростью, в программируемом счетчике 42 - общее число дискретизаций, интервал дискретизаций ИД1 - в первом канале программируемого счетчика 40, а интервал дис- 5 кретизации ИД2 - во втором канале. Отличие работы в этом режиме от предыдущего (задержанного) заключается в следующем.

Триггер 63 регистрации в этом Q случае устанавливается uo;r.e установления триггера 64 счета по приходу следующего тактового импульса генератора 20 тактовых импульсов. При появлении сигнала с выхода триггера 5 64 счета разрешается работа первого канала программируемого счетчика 40 частоты, с выхода которого появляются н.пульсы дискретизации . После того, как выполнено за:фограммиро- 0 ванное число измерений со скоростью ИД, ыходной сигнал программируемого счетчика 41 через формирователи 74 и 69 сбрасывает триггер 64 счета и через формирователи 74 и 68 запре 5 щает работу первого канала программируемого счетчика 40, а через формирователь 69 разрешает работу вто - рого канала. На выходе появляются импульсы дискретизации ИД2, т.е. Q происходит переключение скорости дискретизации.

При программировании первого и второго каналов программируемого счетчика 40 импульсы дискрети- 5 зацик в течение всего периода дискретизации, определяемого единичным состоянием триггера 63 регистрации, будут идти равномерно с одинаковой скоростью.

Q В предпусковом режиме регистрации программируемый счетчик 41 не используется. Установка триггера 63 регистрации происходит по сигналу предварительного пуска, который при наличии признака Режим предпусковой с выхода регистра 39 программ проходит через формирователь 74 на вход установки. В программируемом счетчике 42 программируется число дискрети5

заций, выполняемых после пуска. Разрешение работы этого программируемого счетчика устанавливается по выходному сигналу триггера 64 счета, разрешение работы первого канала программируемого счетчика 40, где программируется интервал дискретизации до пуска, производится по сигналу предварительного пуска. Если требу- ется изменить частоту дискретизации после пуска,для его программирования используется второй канал программи руемого счетчика 40. Разрешение работы этого канала производится вы- ходным сигналом триггера 64 счета, проходящим через формирователи 74 и 68.

Рассмотрим два режима коммутации входных измерительных сигналов: цик- лический и адресный. Под воздействием импульсов дискретизации, проходящих через первьй вход второго элемента ИЛИ 65, производится запуск преобразователя 8, который после окончания преобразования выдает сигн готовности. Этот сигнал поступает на первый вход формирователя 70, на выходе которого формируется сигнал записи в блок 12, срабатываемый от- ветным сигналом готовности блока 12. Выходной сигнал этого формирователя поступает на вход записи триггера 62 измерения. На вход установки этого триггера поступает импульс дис- кретизации ИД1 и устанавливает его в единичное состояние. На информационный вход этого триггера поступае- сигнал признака Режим циклический с выхода регистра 39 программ. В адресном режиме этот сигнал равен нули и сигнал записи в блок 12 своим задним фронтом возвращает триггер 62 измерения в исходное нулевое состояние. На запуск преобразователя 8 по второму входу второй схемы ИЛИ 65 проходят также импульсы записи в блок 12. С выхода формирователя 70 они проходят на вход формирователя 67, где задерживаются и стробиру- ются выходным сигналом триггера 62 измерения. В адресном режиме сигнал Режим циклический равен нулю, и сигнал записи в блок 12, поступающий на вход записи этого триггера. возвращает его в нулевое состояние. Поэтому задержанные сигналы записи в блок 12 не проходят на выход формирователя 67 и в адресном режиме

5

0 5 0 5 0 5 Q

5

запуск преобразователя 8 осуществляется только импульсами дискретизации по первому входу второй схемы ИЛИ 65.

При работе в адресном режиме по каждому импульсу дискретизации формируется один импульс запуска преоб- оазователя 8, по которому производится измерение. Формирование следующих импульсов запуска в количестве, равном заданному числу дискретизаций, производится с периодом, запрограммированным в программируемом счет- шке 40.

Выходной сигнал триггера 62 измерения поступает в первом блоке 31 управления на вход чтения преобразователя 8, чтобы его выходная информация могла быть записана в первьй блок 12.

Номер канала в адресном режиме программируется в регистре 39 программ четырьмя разрядами. Эти сигналы поступают на информационные входы счетчика 48 номера канала. На один вход элемента И 54 поступают импульсы дискретизации, на второй вход - признак адресного режима, являющийся инверсией сигнала с выхода элемента НЕ 51. В адресном режиме импульсы дискретизаций проходят на ззыход элемента И 54 и вход записи счетчика 48 номера канала и номер канала записывается в него параллельной записью. С выходов счетчика 48 номера канала номер канала в виде кода поступает на входы коммутаторов 6 и 7 для первого блока 31 управления или адресные входы блока 14 буферной памяти второго блока 32 управления.

В циклическом режиме разряды номера канала регистра 39 программ служат для программирования числа каналов в цикле. Прохождение сигнала дискретизаций на вход записи счетчика 48 номера канала, заблокировано элементом И 54, и параллельная запись не производится. По сигналу дискретизаций производится начальная установка счетчика 48 номера кана- гла по входу сброса выходным сигналом схемы И 53. Затем в циклическом режиме сигналы записи с выхода элемента И 52 поступают на счетный вход счетчика 48 номера канала, наращивая его адрес на единицу. С выходов этого счетчика код адреса поступает на входы мультиплексора 46, работа которого разрешена только в циклическом режиме. В зависимости от запрограммированного числа каналов в цикле на выходе мультиплексора 46 появися сигнал после появления сигнала последнего номера канала в цикле.

Выходной сигнал этого мультиплексора сбрасывает триггер 62 измерения В отличие от адресного режима на информационном входе этого триггера единичный сигнял, поэтому после установки триггера по входу установки сигналом дискретизации в единичное состояние сигнал записи, поступающий на вход записи, оставляет его в этом состоянии; сброс триггера производится только по входу сброса; Единичный выходной сигнал триггера 62 измерения пропускает на запуск преобразователя 8 через формирова- тель 67 все сигналы с выхода формирователя 70.

При работе в циклическом режиме, коммутации по каждому импульсу дискретизации формируется Мк импульсов измерения, где NK - число каналов в цикле,с периодом, равным длительности измерения. В процессе регистрации в циклическом режиме для каждого канала будет выполнено число дис- кретизаций, заданных в программируемом счетчике 42.

Для увеличения быстродействия при регистрации аналоговых входных сигналов возможно использование конвей- ерной выборки блоков 4, 5.

Все аналоговые входы разбиты на две группы.

Первая и вторая группы 1 и 2 ана- лотовых входов содержат по восемь каналов каждая. Фиксация мгновенных значений производится установленными на входе каждого канала блоками выборки-хранения. Два многоканаль- ных блока 4 и 5 представляют собой многоканальные устройства, каждое из которых состоит из восьми схем выборки-хранения, и управляются раздельными сигналами разрешения хране- ния; при подаче на вход блоков этих сигналов обеспечивается запоминание мгновенного значения измеряемого сигнала соответствующими блоками 4, 5. Два коммутатора 6 и 7 с объединен- ными выходами подключают на вход преобразователя 8 аналоговые сигналы, зафиксированные в блоках 4, 5 переключение каналов в обоих коммутаторах производится трехразрядным кодом номера канала, формируемым счетчиком 48 номера канала, а разрешение каждого коммутатора производится соответствующими сигналами управления. При работе с ильной выборкой 16 измеряемых входных сигналов подключаются на вход каждого из восьми каналов блоков 4 и 5. Сигналы управления коммутаторами формируются триггером 61 управления, а разрешени хранения - мультиплексором 47.

На входы управления мультиплексора 45 поступают сигналы Режим циклический и Выборка конвейерная с выходов регистра 39 программ на информационные входы-выходы номера канала регистра 39 программ и сигналы от шин питания таким образом, что, если запрограммирован режим циклический и выборка нормальная, на первом выходе мультиплексора 45 устанавливается нулевой сигнал, а на втором - единичный, но только в том случае, если число каналов в цикле не превышает восемь. Выходные сигналы ьул гмплексора 45 поступают на входы К и I триггера 61 управления, на выходах которого при поступлении на вхоп записи импульсов дискретизации устанавливается единичный сигнал на первом выходе и нулевой - на втором, т.е. выбирается первьй коммутатор 6.

Если число каналов в цикле 16, то с нулевого до восьмого канала работает первый коммутатор 6, при переходе на восьмой канал триггер 61 управления перебрасывается в исходное состояние, т.е. выбирается второй коммутатор 7. Мультиплексор 47 управляется сигналом с второго выхода регистра 39, и, если выборка нормальная, на оба выхода мультиплексора 47 проходит сигнал триггера 61 измерения и под воздействием равных сигналов хранения оба блока 4, 5 работают синхронно. После перевода обоих блоков 4, 5 в режим хранения производится последовательное измерение входных сигналов по всем каналам, коммутируемым коммутаторами 6, 7 в течение 16 циклов преобразования. После выполнения измерений по всем каналам оба блока 4, 5 переводятся в режим выборки путем подачи обоих сигналов хранения, равных логическому О.

При конвейерной выборке две группы аналоговых входов 1, 2 объединиготся, каждый датчик подключается на заходы двух блоков 4, 5 и число вход- ЙЕЫХ измерительных каналов сокращаетс Э два раза до восьми. .На обоих выходах мультиплексора 45 устанавливаются единичные сигналы и триггер 61 управления начинает работать в счетном режиме, сигналы На его выходах находятся в противо- пазах, т.е. коммутаторы 6, 7 выбирается поочередно. На оба выхода муль- иплексора 47 проходят выходные сиг- алы триггера 61 управления и сигна- ы хранения изменяются в соответст- :ии с сигналами триггера 61 и нахо- ;ятся также в противофазе. В режиме :ранения находится один из блоков

или 5, включенный на вход выбран- фого коммутатора, другой находится режиме выборки.

В момент фиксации значений входных сигналов один из блоков выборки- хранения переходит в режим хранения, а другой - в режим выборки. Выходы блока, находящегося в режиме хранения, последовательно опрашивается соответствующим коммутатором и измеряются преобразователем 8 в те- пение восьми циклов преобразования. После окончания измерений может быть произведена фиксация следующих значений входных сигналов по этим же каналам, т.е. время выборки блоков зыборки-хранения исключается из интервала времени измерения входного сигнала.

Если запрограммирован режим рабо- гы адресный и выборка нормальная, на iiepBOM выходе мультиплексора 45 устанавливается нулевой сигнал, а на ртОром - единичный. Если номер выбранного канала меньше восьми, работает первый коммутатор 6, если но- Нер канала больше восьми, работает второй коммутатор 7, Мультиплексор 47, как и в циклическом режиме с нормальной выборкой, пропускает на вы- Коды сигналы триггера 62 измерения, Оба блока 4 и 5 работают синхронно. Если запрограммирован режим работы адресный и выборка конвейерная, то работа происходит аналогично режиму циклическому с конвейерной выборкой.

В системе предусмотрены расширенные возможности использования запоминающих блоков.

Сигналы записи на вход записи блоков 12 или 13 проходят с выхода эле

5

0

5

0

5

0

5

0

5

мента ИЛИ 66, обеспечивая возможность записи та запоминающий блок не только результатов измерения преобразователя 8 в первом блоке 31 управления или данных блока 14 буферной памяти во втором блоке 32 управления, но и возможность обращения и записи данных, хранящихся в памяти ЭВМ, например результатов обработки измерений, В этом случае сигнал записи от ЭВМ поступает на второй вход элемента ИЛИ 66, При этом выдаются соответствующие сигналы управления на приемопередатчики 10 или 11 с выхода второго дешифратора 44 и инверсного выход -, триггера 62 измерений, которые при отсутствии процесса измерений в системе разрешают передачу данных с входа 9 данных ЭВМ на вход блоков 12 или 13, Соответственно предусмотрена выдача адреса блоков 12 или 13 либо от счетчика 60 адреса, либо непосредственно с входа 37 адресов ЭВМ с помощью мультиплексора 48.

При записи результатов измерений сигнал с выхода формирователя 70 поступает на счетный вход счетчика 60 адреса. В исходное нулевое состояние счетчик 60 адреса устанавливается сигналом предварительного пуска с выхода элемента И 57, где стробиру- ется сигналом блочной записи с выхода регистра 39 программ, который запрещает сброс. Выходной код счетчика 60 адреса поступает на входы мультиплексора 48, а с его выхода - на адресные входы блоков 12 или 13. На другие входы поступает адрес непосредственно с входа 37 адресов ЭВМ. Управление направлением передачи мультиплексора 48 осуществляется выходным управляющим сигналом второго дешифратора 44.

Число измерений в адресном или циклическом режимах программируется и может быть меньше полного объема запоминающего блока. Предусматривается возможность использования оставшейся свободной части памяти для хранения результатов следующей серии измерений или, как указывалось, данных от ЭВМ, например результатов обработки. Для этого в регистр 39 программ записывается режим Блочная запись, который запрещает сброс счетчика 60 адреса по сигналу предварительного пуска очередной серии измерений, и осуществляется их запись

в оставшуюся свободную часть памяти Если производится запись данных ЭВМ, адрес с выхода счетчика 60 адреса может быть ЭВМ прочитан и произведена запись с начального адреса свободной зоны памяти. Адрес с выхода счетчика 60 адреса поступает на вход группы вентилей 43 адреса и снимается с их выхода при наличии управляющего сигнала с выхода второго дешифратора 44, проходящего через элемент И 55, где стробируется сигналом отсутствия измерений с инверсного выхода триггера 62 измерений.

После записи измеренной входной аналоговой или цифровой информации производится ее чтение в программном обмене с ЭВМ. Кроме того, предусмотрена работа в режиме прерывания - по инициативе самого устройства с выдачей сигнала в ЭВМ по выходу 35 прерываний.

Возможны три вида прерываний: прерывание по концу каждого измерения (сигналом прерывания является готовность преобразователя 8 в первом блоке 31 управления или счетчика 16 блока буферной памяти во втором блоке 32 управления, используется в адресном и циклическом режимах); прерывание по концу цикла коммутации на выбранной группе каналов (сигналом прерывания является выходной сигнал триггера 62 измерений, используется в циклическом режиме); прерывание по концу запрограммированного числа дискретизации (сигналом прерывания является сигнал конца программы, используется в адресном и циклическом режимах).

Сигнал чтения запоминающего блока представляет собой управляющий сигнал с выхода второго дешифратора 44, проходящий через элемент И 56, где стробируется сигналом отсутствия измерений с инверсного выхода триггера 62 измерений. С выхода элемента И 56 этот сигнал поступает на вход чтения блока 12 или 13.

Устройство обеспечивает регистрацию в запоминающих блока как аналоговых, так и цифровых входных сигналов от одинаковых блоков 31, 32 управления. Для регистрации входных цифровых сигналов используется блок 32 управления, аналогичный блоку 31 (фиг. 2).

0

5

Третья группа входов устройства 3 предназначена для регистрации цифровых входных сигналов. с Устройство обеспечивает уменьшение динамической погрешности при передаче цифровых входных сигналов за счет использования промежуточной памяти.

При поступлении сигнала запуска от блока 32 управления на вход записи второго триггера 22 на его выходе устанавливается единичный уровень напряжения. По переднему фронту им5 пульса с выхода генератора 20 тактовых импульсов, частота которых превышает частоту измерений, на выходе первого триггера 21 устанавливается единичный уровень напряжения и тем самым разрешается прохождение импульса сброса через первый элемент И 19 на счетчик 16 адреса блока буферной памяти. Одновременно сбрасывается второй триггер 22.

По переднему фронту каждого следующего тактового импульса сбрасыва-, ется первый триггер 21 и тактовые импульсы через схему И-НЕ 17 воздействуют на счетный вход счетчика 16

0 адреса блока буферной памяти и через элемент задержки 18 на вход записи блока 14 буферной памяти. При этом выход счетчика 16 адреса блока буферной памяти выставляют адрес ячейки блока 14 буферной памяти и управляют цифровым мультиплексором 15. Таким образом, за время, равное

NK(tMn--tinn),

0 где N - число каналов;

t - время задержки в мультиплексоре;VЦ„п- время записи в промежуточную память,

5 происходит запись с тактовой частотой цифрового сигнала по каналам в промежуточную память блока 14. По окончанию записи выдается сигнал готовности, который воспринимается блоком 0 32 управления.

По сигналу готовности блок 32 управления производит передачу содержимого блока 14 буферной памяти Ј блок 13 и выдает следующий сигнал 5 запуска.

Динамическая погрешность представляет собой погрешность датирования, связанную с недостаточной вре5

Менной привязкой начала регистрации нескольких входных цифровых сигналов к единому моменту времени.

Погрешность датирования, при ре- истрации цифровых сигналов опреде- яется по формуле

где tjn- время записи в нанять.

Уменьшение погрешности датирования достигается за счет уменьшения времени , так как буферная память может быть построена на интегральных микросхемах быстродействующей памяти, имеющих существенно более высокое быстродействие, чем обычный запоминающий блок, основным требованием к которому является большой объем памяти. Поэтому t,nn«t,n.

Формула изобретения 1

Многоканальное устройство для регистрации аналоговых и цифровых сиг- налов, содержащее два блока выборки- хранения, два коммутатора, аналого- цифровой преобразователь, два запоминающих блока, тактовый генератор, ртервый элемент ИЛИ, первый дешифра- frop, первый счетчик адреса, первый лемент И, два блока управления,.каж ый из которых содержит регистр программ, второй дешифратор, счетчик Йомера канала, второй счетчик адреса второй и третий элементы И, второй и третий элементы ИЛИ, элемент НЕ, причем первый аналоговый вход устройства соединен с информационным входом первого блока выборки-хране- Йия, второй аналоговый вход устройства соединен с информационным входом второго блока выборки-хранения, Выход первого блока выборки-хранения соединен с информационным входом пер зого коммутатора, выход второго блока выборки-хранения соединен с информационным входом второго коммутатора, выход которого соединен с выходом первого коммутатора и с инфор- мационным входом аналого-цифрового преобразователя, входы адреса перво- го и второго коммутаторов соединены с первым адресным выходом первого блока управления, адресный вход уст- роиства соединен с адресными входами первого и второго блоков управления и адресным входом первого дешифратора, вход управления устройства соединен с одноименными входами Первого и второго блоков управления и первого дешифратора, вход внешнего тактирующего сигнала устройства соединен с первыми тактовыми входами первого и второго блоков управления, выход сигналов прерывания устройства соединен с одноименными выходами первого и второго блоков управления, причем в каждом блоке управления адресный вход в блоке управления соединен с адресным входом второго дешифратора, вход управления которого соединен с входом управления соответствующего блока управления, вход разрешения второго дешифратора первого блока управления соединен с первым выходом первого дешифратора, второй выход которого соединен с входом разрешения второго дешифратора второго блока управления, первый выход регистра программ соединен с информационным входом счетчика номер канала, выход которого соединен с первым адресным выходом соответствующего блока управления, отличающееся тем, что, с целью расширения функциональных возможностей, повышения быстродействия при регистрации аналоговых сигналов и уменьшения динамической погрешности при регистрации аналоговых и цифровых сигналов за счет введения дополнительных режимов работы и промежуточн буферизации данных, в него введены два приемопередатчика, цифровой мультиплексор, первый и второй триггеры, блок буферной памяти, инвертирующий усилитель, источник опорного напряжения , цифро ан ало го вый преобразова- тель, регистр способа запуска, первы и второй компараторы, элемент И-НЕ элемент задержки, а в каждый из блоков управления введены ТРИ программируемых счетчика, четыре мультиплексора, триггер управления, триггер измерения, триггер регистрации, триггер счета, четвертый, пятый, шестой и седьмой элементы И, две группы элементов И-ИЛИ, формирователь ответа, группа ключей адреса и восемь формирователей, причем первая группа входов-выходов первого приемопередатчика соединена с информационными входами-выходами первого запоминающего блока и информационными выхода ми аналого-цифрового преобразователя, первая группа входов-выходов второ

го приемопередатчика соединена с информационными входами-выходами второго запоминающего блока и выходами блока буферной памяти, информационные входы которого соединены с выходами цифрового мультиплексора, управляющие входы которого соединены с адресными входами блока буферной памяти и выходами данных первого сче чика адреса, выход переполнения которого соединен с первым входом элемента И-НЕ и первым входом признаков второго блока управления, вторые входы-выходы первого и второго приемопередатчиков соединены с информационными входами цифроаналогового преобразователя, регистра способа запуска и входом-выходом данных устройства, первый адресный выход второго блока управления соединен с адресным входом блока буферной памяти, цифровой информационный вход устройства соединен с информационным входом цифрового мультиплексора, вторые адресные выходы первого и второго блоков управления соединены с соответствующими адресными входами первого и второго запоминающих блоков, первый и второй управляющие выходы первого блока управления соединены с входами управления первого и второго блоков выборки-хранения соответственно, третий и четвертый управляющие выходы первого блока управления соединены с входами управления первого и второго коммутаторов соответственно, пятый управляющий выход первого блока управления соединен с входом пуска аналого-цифрового преобразователя, пятый управляющий выход второго блока управления соединен с входом записи первого триггера, шестой управляющий выход первого блока управления соединен с входом чтения аналого-цифрового преобразователя, шестой управляющий выход второго блока управления соединен с входом чте- .ния блока буферной памяти, седьмой и восьмой управляющие выходы первого и второго блоков управления соединены с входами управления первого и второго приемопередатчиков соответственно, девятый и десятый управляющие выходы первого и второго блоков управления соединены с входами записи и чтения первого и второго запоминающих блоков соответственно, одиннадцатые управляющие выходы первого

15

20

5

JQ

и второго блоков управления объединены через МОНТАЖНОЕ ИЛИ и соединены с выходом управляющего сигнала устройства, первый вход признаков первого блока управления соединен с выходом готовности аналого-цифрового преобразователя, вторые входы признаков первого и второго блоков управления соединены с выходами готовности первого и второго запоминающих блоков соответственно, входы режимов первого и второго блоков управления соединены с первыми группами входов- выходов первого и второго приемопередатчиков соответственно, выход тактового генератора соединен с вторыми тактовыми входами первого и второго блоков управления, вторым входом элемента И-НЕ, первым входом первого элемента И и входом записи второго триггера, информационный вход которого соединен с прямым выходом первого триггера, вход сброса которого соединен с инверсным выходом второго триггера, прямой выход которого соединен с вторым входом первого элемента И, выход которого соединен с вхо- дом сброса первого счетчика адреса, счетный вход которого соединен с выходом элемента И-НЕ и входом элемента задержки, выход которого соединен с входом записи блока буферной памяти, третий и четвертый выходы первого дешифратора соединены с входами записи цифроаналогового преобразователя и регистра способа запуска соответственно, первый выход которого соединен с первым входом первого компаратора, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго компаратора, первый вход которого соединен с вторым выходом регистра способа запуска, третий выход которого соединен с третьим входом первого элемента ИЛИ, выход которого соединен с третьими входами признаков первого и второго Q блоков управления, четвертые входы признаков которых соединены с четвертым выходом регистра способа запуска, вторые входы первого и второго компараторов соединены с выходом источника опорного напряжения и входом опорного уровня цифроаналогового преобразователя, аналоговый выход которого соединен с третьими входами первого и второго компараторов, четвер0

5

0

5

5

тый вход первого компаратора соединен с входом инвертирующего усилителя и с одним из каналов первого аналогового входа устройства, четвертый $ход второго компаратора соединен Ј выходом инвертирующего усилителя, в саждом блоке управления вход режима Соединен с информационным входом регистра программ, информационными нходами трех программируемых счетчиков и выходами группы ключей адреса, первый выход регистра программ соединен с первыми входами управления первого и второго мультиплексоров, информационный вход второго мультиплексора соединен с выходом счетчика номера канала, второй выход регистра программ соединен с вторым входом управления первого коммутатора и пер- ным входом управления третьего коммутатора, второй и третий входы которого соединены с прямым и инверсным выходами триггера управления и третьим и четвертым управляющими выходами блока управления соответственно, первый и второй управляющие выходы блока управления соединены с первым и вторым выходами третьего вдшьтиплексора, четвертый вход которого соединен с прямым выходом риггера измерения, первыми входами ервого и второго формирователей, естым управляющим выходом и первым IJI3 выходов сигналов прерывания блока травления, второй из выходов сигналов прерывания блока управления соединен с выходом третьего программируемого счетчика, вторым входом лторого формирователя, первым входом Третьего формирователя и информаци- шным входом триггера регистрации, Третий выход регистра программ соединен с третьим входом управления первого мультиплексора, вторым входом управления второго мультиплексора, первым входом второго элемента М, входом элемента НЕ, информационным входом триггера измерения и первым входом третьего элемента И, второй вход которого соединен с входом установки триггера измерения, входом Записи триггера управления, первыми йходами четвертого элемента И и второго элемента ИЛИ и первым выходом Первой группы элементов И-ИЛИ, второй вход второго элемента ИЛИ соединен с выходом первого формирователя, Второй вход которого соединен с пер

5

0

5

вым выходом четвертого формирователя, второй выход которого соединен с первым входом третьего элемента ИЛИ, вторым входом второго элемента И, входом записи триггера измерения и счетным входом второго счетчика адреса, выход которого соединен с первым информационным входом четвертого мультиплексора и информационным входом ключей адреса группы, вход управления которой соединен с выходом пятого элемента И, первый вход которого соединен с инверсным выходом триггера измерения, входом записи триггера регистрации, первым входем шестого элемента И и восьмым управляющим выходом блока управления, девятый управляющий выход которого соединен с выходом третьего элемента ИЛИ, второй вход которого соединен с вторым выходом второго дешифратора, третий, четвертый и пятый выходы которого соединены с входами записи первого, второго и третьего программируемых счетчиков соответственно, шестой и седьмой выходы второго дешифратора соединены с вторыми входами пятого и шестого элементов И соответственно, восьмой выход второго дешифратора соединен с входом управления четвертого мультиплексора, выход которого соединен с вторым адресным выходом блока управления, седьмой управляющий выход которого соединен с девятым выходом второго дешифратора, адресный вход которого соединен с вторым информационным входом четвертого мультиплексора, де- 0 сятый выход второго дешифратора соединен с первым входом формирователя ответа, выход которого является одиннадцатым управляющим выходом блока управления, первый вход признаков которого соединен с первым входом четвертого формирователя и является третьим из выходов сигналов прерывания блока управления, второй вход признаков которого соединен с вторыми входами формирователя ответа и четвертого формирователя, выход первого формирователя соединен с вторым входом второго элемента ИЛИ, выход которого соединен с пятым управляющим выходом блока управления, третий вход признаков которого соединен с первым входом пятого формирователя, второй вход которого соединен с первыми входами шестого,

0

5

5

0

5

седьмого и восьмого формирователей и выходом триггера счета, вход записи которого соединен с третьим входом пятого формирователя, первыми входами элементов И-ИЛИ второй группы, вторым входом седьмого формирователя и вторым тактовым входом блока управления, десятьй управляющий выход которого соединен с выходом шестого элемента И, четвертый вход признаков в каждом блоке управления соединен с третьим входом седьмого формирователя, первым входом седьмого элемента И и вторым входом восьмого формирователя, третий вход которого соединен с четвертым выходом регистра программ, пятый выход которого соединен с четвертым входом восьмого формирователя, пятый вход которого соединен с выходом второго программируемого счетчика, вход управления которого соединен с шестым входом восьмого формирователя и выходом шестого формирователя, второй вход которого соединен с первым и вторым синхровходами первого программируемого счетчика и выходом элементов И-ИЛ второй группы, вторые входы которых соединены с первым тактовым входом блока управления, а третьи входы - с шестым выходом регистра программ, седьмой выход которого соединен с вторым входом седьмого элемента И, выход которого соединен с входом установки второго счетчика адреса, первый выход первого программируемого счетчика соединен с первыми входами элементов И-ИЛИ первой группы,

0

5

0

5

0

5

вход установки которого соединен с первым выходом восьмого формирователя, второй выход которого соединен с третьим входом второго формирователя, выход которого соединен с первым входом управления первого программируемого счетчика, второй выход которого соединен с третьими входами элементов И-ИЛИ первой группы, второй выход которой соединен с синхровходами второго и третьего программируемых счетчиков, вход управления третьего программируемого счетчика соединен с первым выходом третьего формирователя, второй выход которого соединен с входом сброса триггера счета, информационный вход которого соединен с выходом пятого формирователя, четвертый вход которого соединен с выходом седьмого формирователя, третий выход третьего формирователя соединен с четвертыми входами элементов И-ИЛИ первой группы и вторым входом управления первого программируемого счетчика, третий вход третьего формирователя соединен с третьим выходом восьмого формирователя, выход второго мультиплексора соединен с входом сброса триггера измерения, выход элемента НЕ соединен с вторым входом четвертого элемента И, выход которого соединен с входом записи счетчика номера канала, счетный вход которого соединен с выходом второго элемента И, а вход сброса - с выходом третьего эле-, мента И, первый и второй выходы первого мультиплексора соединены с вхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Многоканальный программируемый аналого-цифровой преобразователь | 1985 |

|

SU1266002A1 |

| Программируемый формирователь многочастотного сигнала | 1989 |

|

SU1739472A1 |

| УСТРОЙСТВО ФОТОМЕТРИРОВАНИЯ ИЗОБРАЖЕНИЙ С ВЫРАЖЕННЫМ МАКСИМУМОМ ПРОСТРАНСТВЕННОГО РАСПРЕДЕЛЕНИЯ ОСВЕЩЕННОСТИ | 1995 |

|

RU2084842C1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

Изобретение относится к вычислительной и информационно-измерительной технике и может быть использовано в автоматизированных системах регистрации быстропротекающих процессов. Целью изобретения является расширение функциональных возможностей, повышение быстродействия при регистрации аналоговых сигналов и уменьшение динамической погрешности при регистрации аналоговых и цифровых сигналов за счет введения дополнительных режимов работы и промежуточной буферизации данных. Введение в устройство блока буферной памяти 14, цифроаналогового преобразователя 23, компараторов 25 и 26 и усилителей 28 и 29, а также расширение задания программных режимов работы блоков 31 и 32 управления позволяет обеспечить широкие возможности по запуску, различные частоты дискретизации, гибкость при расширении многоканальности, конвейерный режим работы блоков выборки-хранения, хранение не только результатов измерения, но и результатов обработки их в ЭВМ. 2 ил.

вторые входы которой соединены с вто- лп дами К и I соответственно триггера рым входом третьего формирователя и управления, прямым выходом триггера регистрации,

| Многоканальная система регистрации аналоговых процессов | 1981 |

|

SU951146A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для ввода информации | 1985 |

|

SU1275419A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-15—Публикация

1988-05-26—Подача