Изобретение относится к технике измерения частот методом дискретного счета.

Цель изобретения - повышение быстродействия .

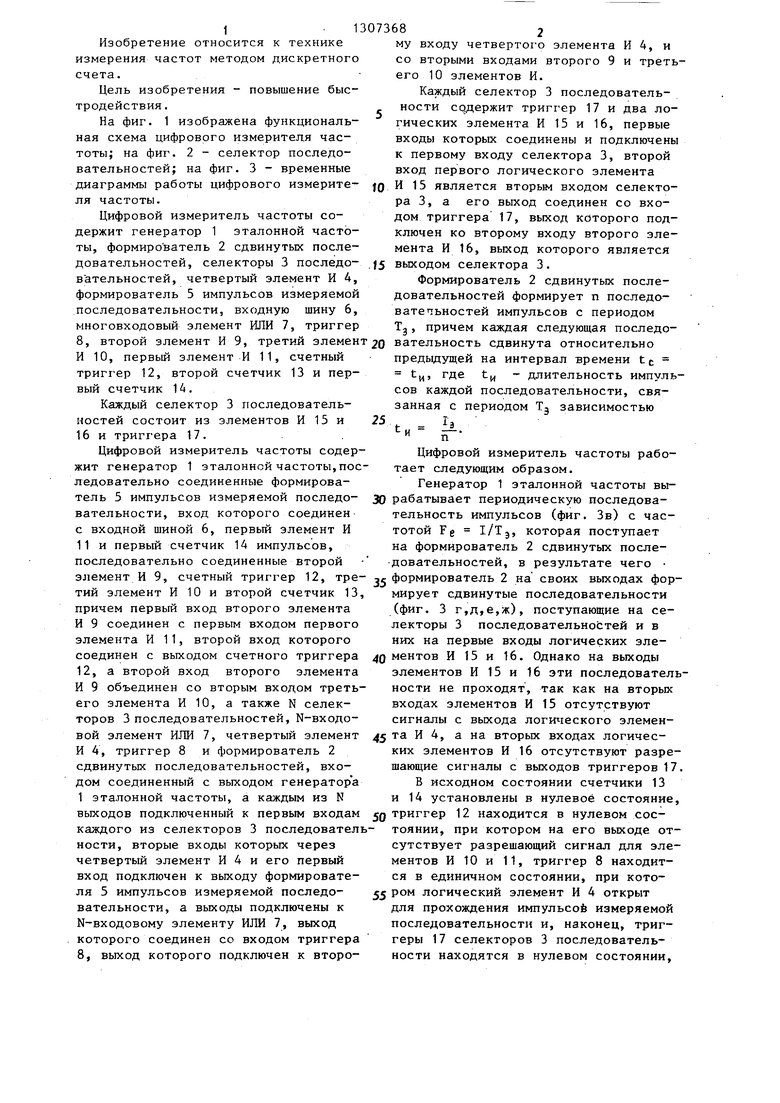

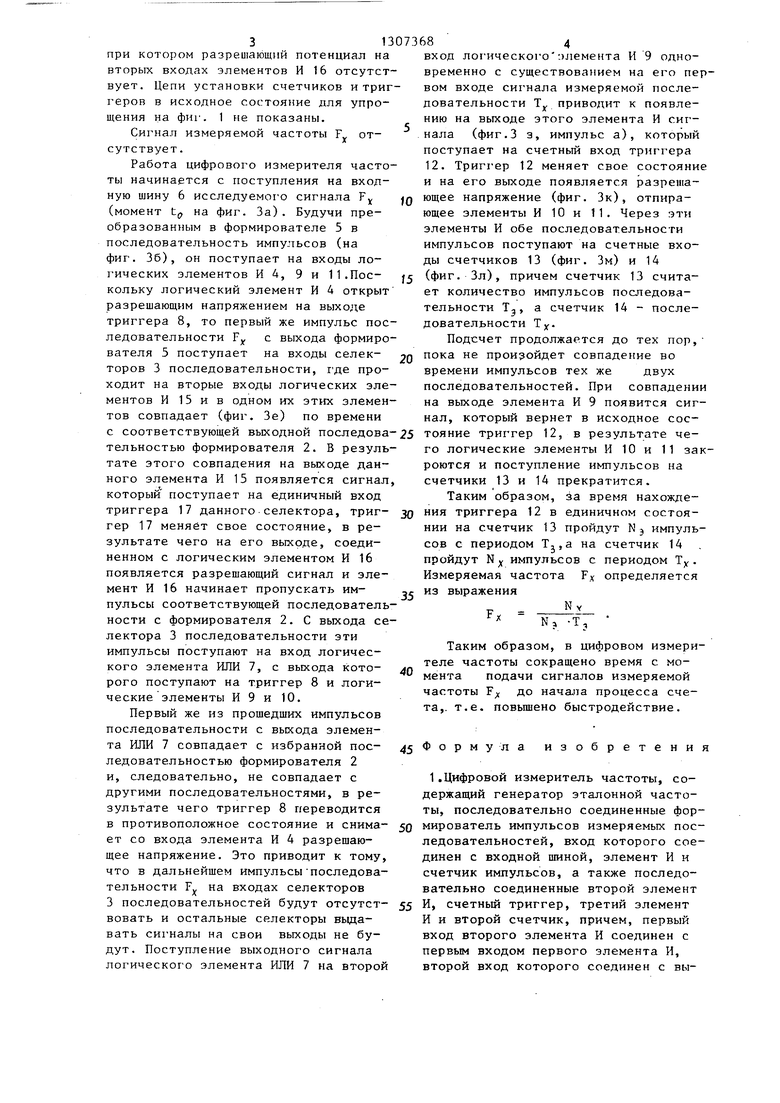

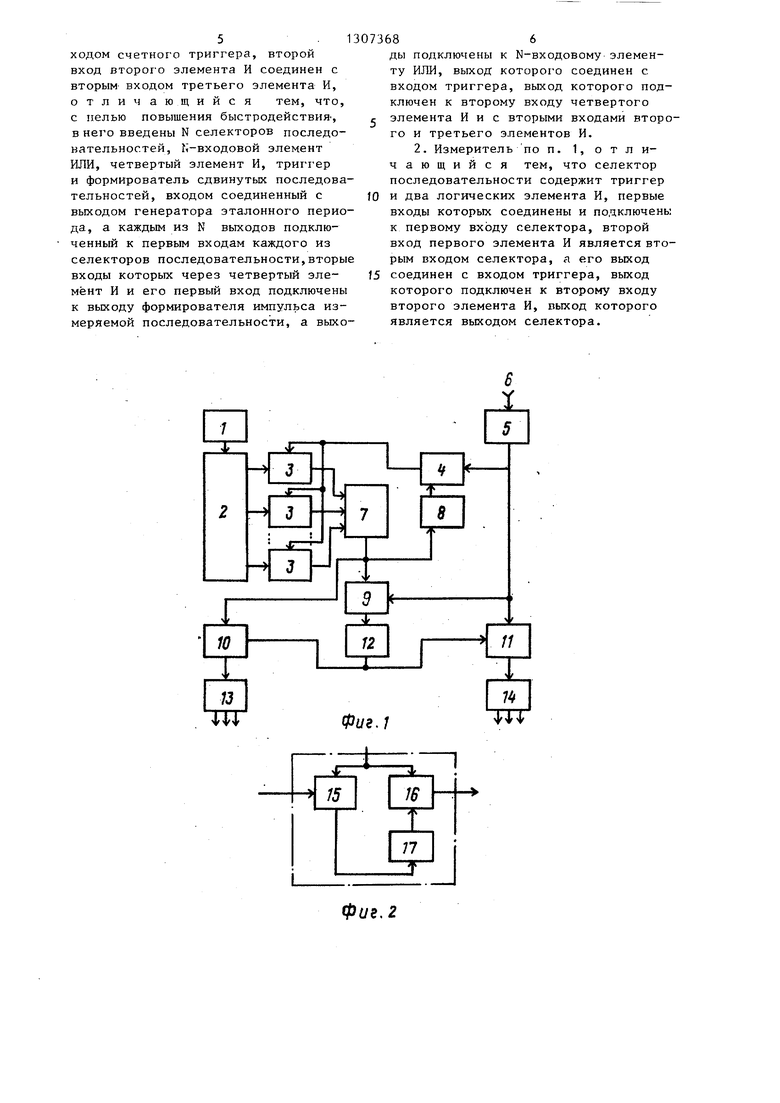

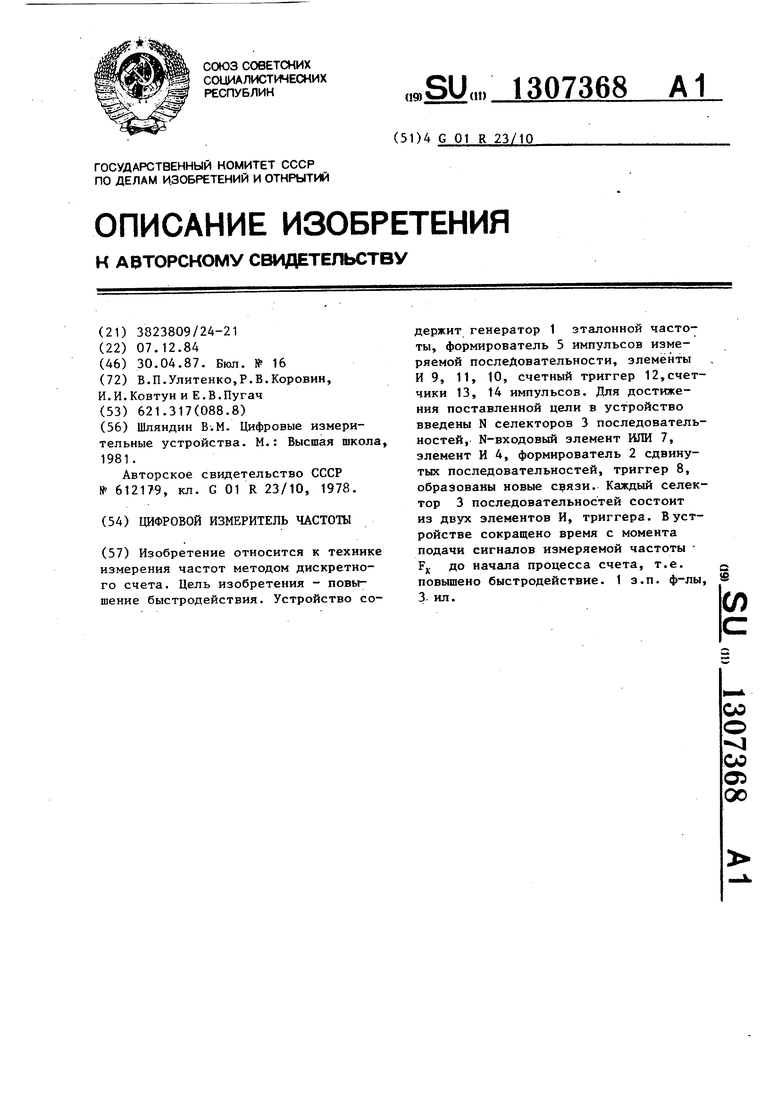

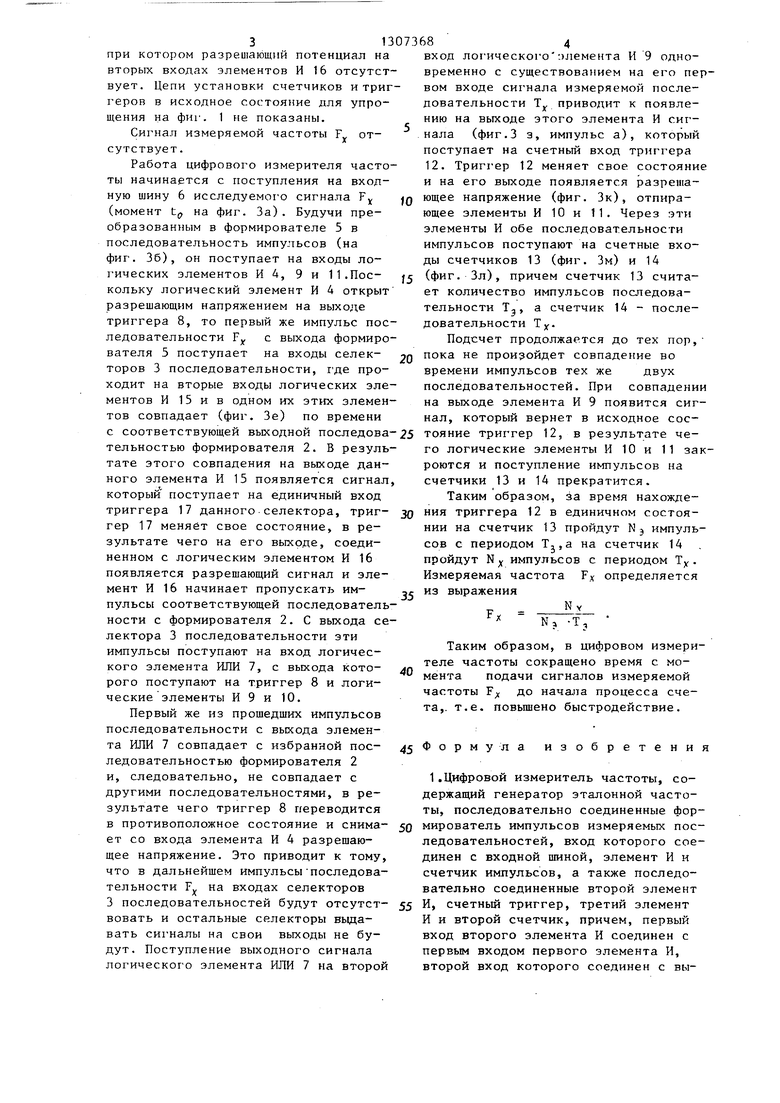

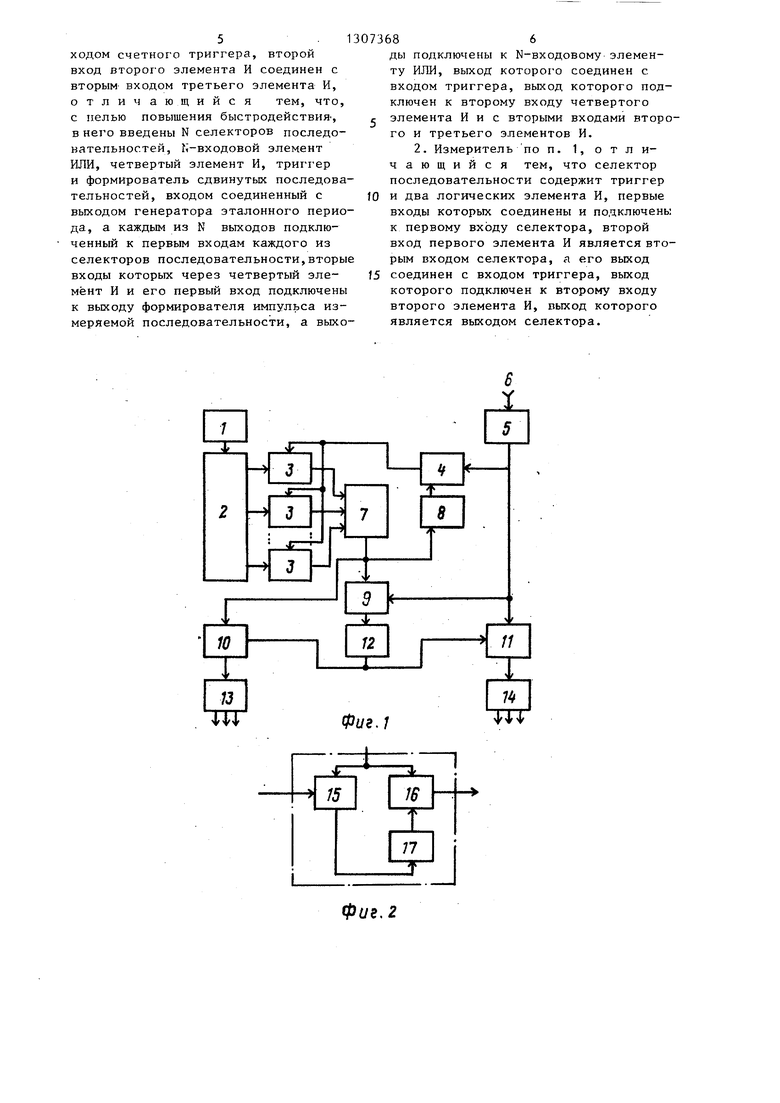

На фиг. 1 изображена функциональная схема цифрового измерителя частоты; на фиг. 2 - селектор последовательностей; на фиг. 3 - временные

диаграммы работы цифрового измерите- |Q И 15 является вторым входом селекто- ля частоты.ра 3, а его выход соединен со вхоЦифровой измеритель частоты со- дом триггера 17, выход которого поддержит генератор 1 эталонной часто- ключен ко второму входу второго эле- ты, формирователь 2 сдвинутых после- мента И 16, выход которого является довательностей, селекторы 3 последо- .ff выходом селектора 3.

Формирователь 2 сдвинутых последовательностей формирует п последо- ватепьностей импульсов с периодом Tj, причем каждая следующая последовательностей, четвертый элемент И 4,

формирователь 5 импульсов измеряемой

последовательности, входную шину 6,

многовходовый элемент ИЛИ 7, триггер

8, второй элемент И 9, третий элемент 20 вательность сдвинута относительно

И 10, первый элемент И 11, счетный предыдущей на интервал времени tc

триггер 12, второй счетчик 13 и пер- t

вый счетчик 14.

Каждый селектор 3 последовательностей состоит из элементов И 15 и

И

где

- длительность импуль25

16 и триггера 17.

Цифровой измеритель частоты содержит генератор 1 эталонной частоты,последовательно соединенные формировасов каждой последовательности, связанная с периодом Tj зависимостью

t э Си Й-Цифровой измеритель частоты работает следующим образом.

Генератор 1 эталонной частоты вы- тель 5 импульсов измеряемой последо- ЗО рабатывает периодическую последова- вательности, вход которого соединен тельность импульсов (фиг. За) с час- с входной шиной 6, первый элемент И тотой Fg I/Tj, которая поступает 11 и первый счетчик 14 импульсов, на формирователь 2 сдвинутых после- последовательно соединенные второй довательностей, в результате чего элемент И 9, счетный триггер 12, тре- ,г формирователь 2 на своих выходах фор- тий элемент И 10 и второй счетчик 13, мирует сдвинутые последовательности причем первый вход второго элемента (фиг. 3 г,д,е,ж), поступающие на се- И 9 соединен с первым входом первого лекторы 3 последовательностей и в элемента И 11, второй вход которого них на первые входы логических зле- соединен с выходом счетного триггера 40 ментов И 15 и 16. Однако на выходы 12, а второй вход второго элемента элементов И 15 и 16 эти последователь- И 9 объединен со вторым входом треть- ности не проходят, так как на вторых его элемента И 10, а также N селек- входах элементов И 15 отсутствуют торов 3 последовательностей, N-входо- сигналы с выхода логического элемен- вой элемент ИЛИ 7, четвертый элемент та И , а на вторых входах логичес- И 4, триггер 8 и формирователь 2 ких элементов И 16 отсутствуют разрешающие сигналы с выходов триггеров 17.

В исходном состоянии счетчики 13 и 14 установлены в нулевое состояние.

сдвинутых последовательностей, входом соединенный с выходом генератор а 1 эталонной частоты, а каждым из N

выходов подключенный к первым входам 50 Р Р находится в нулевом соскаждого из селекторов 3 последовательности, вторые входы которых через четвертый элемент И 4 и его первый вход подключен к выходу формирователя 5 импульсов измеряемой последовательности, а выходы подключены к N-входовому элементу ИЛИ 7, выход которого соединен со входом триггера В, выход которого подключен к второтоянии, при котором на его выходе от сутствует разрешающий сигнал для эле ментов И 10 и 11, триггер 8 находится в единичном состоянии, при кото- 55 ром логический элемент И 4 открыт для прохождения импульсоб измеряемой последовательности и, наконец, триггеры 17 селекторов 3 последовательности находятся в нулевом состоянии.

му входу четвертого элемента И 4, и со вторыми входами второго 9 и третьего 10 элементов И.

Каждый селектор 3 последовательности co epжит триггер 17 и два логических элемента И 15 и 16, первые входы которых соединены и подключены к первому входу селектора 3, второй вход первого логического элемента

И

где

- длительность импультоянии, при котором на его выходе отсутствует разрешающий сигнал для элементов И 10 и 11, триггер 8 находится в единичном состоянии, при кото- 55 ром логический элемент И 4 открыт для прохождения импульсоб измеряемой последовательности и, наконец, триггеры 17 селекторов 3 последовательности находятся в нулевом состоянии.

при котором разрешающий потенциал на вторых входах элементов И 16 отсутствует. Цепи установки счетчиков и триггеров в исходное состояние для упрощения на фиг. 1 не показаны.

Сигнал измеряемой частоты F, отсутствует .

Работа цифрового измерителя частоты начинается с поступления на входную шину 6 исследуемого сигнала F (момент ty на фиг. За). Будучи преобразованным в формирователе 5 в последовательность импульсов (на фиг. Зб), он поступает на входы логических элементов И 4, 9 и 11.Поскольку логический элемент И 4 открыт разрешающим напряжением на выходе триггера 8, то первый же импульс последовательности Fj с выхода формирователя 5 поступает на входы селек- торов 3 последовательности, г де проходит на вторые входы логических элементов И 15 и в одном их этих элементов совпадает (фиг. За) по времени

с соответствующей выходной последова-25 тояние триггер 12, в результате че

тельностью формирователя 2. В результате этого совпадения на выходе данного элемента И 15 появляется сигнал который поступает на единичный вход триггера 17 данного селектора, триггер 17 меняет свое состояние, в результате чего на его выходе, соединенном с логическим элементом И 16 появляется разрешающий сигнал и элемент И 16 начинает пропускать импульсы соответствующей последовательности с формирователя 2. С выхода селектора 3 последовательности эти импульсы поступают на вход логического элемента ИЛИ 7, с выхода которого поступают на триггер 8 и логические элементы И 9 и 10.

Первый же из прошедших импульсов последовательности с выхода элемента ИЛИ 7 совпадает с избранной последовательностью формирователя 2 и, следовательно, не совпадает с другими последовательностями, в результате чего триггер 8 переводится в противоположное состояние и снимает со входа элемента И 4 разрешающее напряжение. Это приводит к тому, что в дальнейшем импульсы последовательности F, на входах селекторов 3 последовательностей будут отсутст- вовать и остальные селекторы выдавать сигналы на свои выходы не будут. Поступление выходного сигнала логического элемента ИЛИ 7 на второй

вход логического элемента И 9 одновременно с существованием на его первом входе сигнала измеряемой последовательности Tjj. приводит к появлению на выходе этого элемента И сигнала (фиг.З 3, импульс а), который поступает на счетный вход триггера 12. Триггер 12 меняет свое состояние и на его выходе появляется разрешающее напряжение (фиг. Зк), отпирающее элементы И 10 и 11. Через эти элементы И обе последовательности импульсов поступают на счетные входы счетчиков 13 (фиг. 3м) и 14 (фиг. 3л), причем счетчик 13 считает количество импульсов последовательности Тд, а счетчик 14 - последовательности Т;.

Подсчет продолжается до тех пор, пока не произойдет совпадение во времени импульсов тех же двух последовательностей. При совпадении на выходе элемента И 9 появится сигнал, который вернет в исходное сос0

5

0

го логические элементы И 10 и 11 закроются и поступление импульсов на счетчики 13 и 14 прекратится.

Таким образом, за время нахождения триггера 12 в единичном состоянии на счетчик 13 пройдут N3 импульсов с периодом Tj,a на счетчик 14 пройдут N . импульсов с периодом Ту. Измеряемая частота FX определяется из выражения

„ Ny

X

N -Т,

Таким образом, в цифровом измерителе частоты сокращено время с момента

подачи сигналов измеряемой

частоты Y f до нача-па процесса счета,, т.е. повьш1ено быстродействие.

55

45 Форму л а изобретения

5

1.Цифровой измеритель частоты, содержащий генератор эталонной частоты, последовательно соединенные формирователь импульсов измеряемых последовательностей, вход которого соединен с входной шиной, элемент И и счетчик импульсов, а также последовательно соединенные второй элемент И, счетный триггер, третий элемент И и второй счетчик, причем, первый вход второго элемента И соединен с первым входом первого элемента И, второй вход которого соединен с вы0

ходом счетного триггера, второй вход второг о элемента И соединен с вторым входом третьего элемента И, отлич ающийся тем, что, с целью повышения быстродействия , в него введены N селекторов последовательностей, N-входовой элемент ИЛИ, четвертый элемент И, трип ер и формирователь сдвинутых последовательностей, входом соединенный с выходом генератора эталонного периода, а каждым из N выходов подключенный к первым входам каждого из селекторов последовательности,вторые входы которых через четвертый элемент И и его первый вход подключены к выходу формирователя импульса измеряемой последовательности, а выхоФие,2

ды подключены к N-входовому элементу ИЛИ, выход которого соединен с. входом триггера, выход которого подключен к второму входу четвертого элемента И и с вторыми входами второго и третьего элементов И.

2. Измеритель по п. 1, отличающийся тем, что селектор последовательности содержит триггер и два логических элемента И, первые входы которых соединены и подключены к первому входу селектора, второй вход первого элемента И является вторым входом селектора, а его выход соединен с входом триггера, выход которого подключен к второму входу второго элемента И, выход которого является выходом селектора.

tj игэ

oes fvj csQjj r i: С; S::

Редактор А.Ревин

Составитель Е.Минкин

Техред А.Кравчук Корректор С.Шекмар

Заказ 1627/44 Тираж 731 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

-ю -KJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель отношения частот | 1982 |

|

SU1177762A1 |

| Цифровой частотомер | 1985 |

|

SU1275314A2 |

| Устройство для измерения частоты | 1982 |

|

SU1247773A1 |

| Цифровой измеритель частоты заполнения радиоимпульсов | 1980 |

|

SU938186A1 |

| Цифровой измеритель временных интер-ВАлОВ | 1979 |

|

SU842695A1 |

| АВТОМАТИЧЕСКИЙ СИГНАЛИЗАТОР ДЕФЕКТОВ К УЛЬТРАЗВУКОВОМУ ДЕФЕКТОСКОПУ | 2008 |

|

RU2357242C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Измеритель временных интервалов | 1987 |

|

SU1597859A2 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Устройство для цифрового измерения разности частот электрических колебаний | 1973 |

|

SU495616A1 |

Изобретение относится к технике измерения частот методом дискретного счета. Цель изобретения - повышение быстродействия. Устройство содержит генератор 1 эталонной частоты, формирователь 5 импульсов измеряемой последовательности, элементы И 9, 11, 10, счетный триггер 12,счетчики 13, 14 импульсов. Для достижения поставленной цели в устройство введены N селекторов 3 последовательностей, N-входовый элемент ИЛИ 7, элемент И 4, формирователь 2 сдвинутых последовательностей, триггер 8, образованы новые . Каждый селектор 3 последовательностей состоит из двух элементов И, триггера. В устройстве сокращено время с момента подачи сигналов измеряемой частоты F. до начала процесса счета, т.е. повышено быстродействие. 1 з.п. ф-лы, 3 ил. сл со о со О5 00

| Шляндин В.М | |||

| Цифровые измерительные устройства | |||

| М.: Высшая школа, 1981 | |||

| Цифровой частотомер | 1977 |

|

SU612179A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-04-30—Публикация

1984-12-07—Подача