Изобретение относится к области электросвязи и может быть применено для поиска и оперативной идентификации информации в сетях передачи данных с коммутацией пакетов.

Известны устройства поиска информации - см., например, Авт.Св. СССР № 1621049 "Устройство поиска информации", МПК G06F 15/40, заявленное 09.01.89, Авт.Св. СССР № 1711185 "Устройство поиска информации", МПК G06F 15/40, заявленное 05.04.89.

Известные аналоги содержат регистры границ, суммирующие и вычитающие счетчики, схемы сравнения, блоки памяти, блоки вычисления и ряд других элементов, позволяющих осуществлять поиск информации. В ходе приема цифрового сообщения и поиска в нем определенной цифровой последовательности необходимо определить его параметры и соответствие последовательности передачи правилам обмена данными, установленным для данного протокола. Известные аналоги не в полном объеме выполняют эти требования.

В первом аналоге определение сетевых пакетов реализовано с вероятностью правильного распознавания менее 0.1, поскольку распознавание производится статистическим способом и не учитывает признаков последовательной передачи информации.

Во втором аналоге недостатком является невозможность получения однозначного решения в связи с низким уровнем достоверности и вероятности идентификации коммуникационного протокола (менее 0.3), так как поиск информационных блоков реализован дихотомическим методом без учета наличия допустимой последовательности пакетов.

Из известных наиболее близким аналогом (прототипом) по своей технической сущности заявленному устройству является устройство по Патенту РФ № 2115952 "Устройство поиска информации", МПК G06F 17/40 опубликованное 20.07.98.

Устройство-прототип включает блок памяти, регистр стратегии поиска и вычитающий счетчик, делитель частоты, коммутатор, первый, второй, третий и четвертый блоки селекции, формирователь временных интервалов и блок индикации.

При этом в устройстве-прототипе выход делителя частоты соединен с первыми входами блока памяти, вычитающего счетчика, первого, второго, третьего и четвертого блоков селекции, регистра стратегии поиска. Выходы блока памяти соединены соответственно с четвертым-одиннадцатым входами коммутатора, а первый выход вычитающего счетчика соединен с десятым входом блока памяти, двенадцатым входом коммутатора, одиннадцатым входом первого блока селекции, десятыми входами второго, третьего и четвертого блоков селекции, третьим входом регистра стратегии поиска и является командным выходом устройства. Второй выход вычитающего счетчика соединен с одиннадцатыми входами второго, третьего и четвертого блоков селекции, а третий выход вычитающего счетчика соединен с двенадцатым входом первого блока селекции. Выходы коммутатора соединены с вторым-девятым входами первого, второго, третьего и четвертого блоков селекции соответственно, а первый и второй выходы первого блока селекции соединены соответственно с первым и вторым входами коммутатора. При этом третий выход первого блока селекции соединен с четвертым входом регистра стратегии поиска и четырнадцатым входом вычитающего счетчика, а четвертый выход первого блока селекции соединен с пятым входом регистра стратегии поиска, четырнадцатым входом вычитающего счетчика и входом формирователя временных интервалов. Пятый выход первого блока селекции соединен с третьим входом коммутатора. Шестой выход первого блока селекции и первые выходы второго, третьего и четвертого блоков селекции, выход регистра стратегии поиска соединены с первым входом блока индикации, десятым входом первого блока селекции и четырнадцатым входом вычитающего счетчика. Второй выход второго блока селекции соединен с вторым входом регистра стратегии поиска, а второй выход третьего блока селекции соединен с третьим входом регистра стратегии поиска. При этом второй выход четвертого блока селекции и выход формирователя временных интервалов соединены с вторым входом блока индикации и четырнадцатым входом вычитающего счетчика. Вход делителя частоты, второй-девятый входы блока памяти и второй-тринадцатый входы вычитающего счетчика являются соответственно входом тактовой частоты, сигнальными и информационными входами устройства.

Такая схема, по сравнению с устройствами-аналогами, позволяет принимать однозначное решение о наличии в потоке данных элементов протокола прикладного уровня TFTP (Trivial File Transfer Protocol) за счет синтаксического распознавания данного протокола, основанного на операции идентификации передаваемых по каналу пакетов и правил обмена ими в ходе сеанса связи.

Однако данное устройство имеет ряд существенных недостатков:

1. Относительно большое время, необходимое для идентификации пакетов, так как идентификация осуществляется путем последовательного анализа значений признаков. Это ограничивает применение устройства-прототипа для анализа протоколов в современных высокоскоростных вычислительных сетях.

2. Узкая область применения, а именно только для анализа протокола TFTP на предмет соответствия наблюдаемой последовательности пакетов правилам, установленным для данного протокола.

Целью заявленного технического решения является разработка устройства поиска информации, обеспечивающего расширение области его применения и повышение быстродействия за счет идентификации пакетов, путем параллельного анализа значений признаков идентификации и контроля последовательности обмена ими на предмет соответствия любым, априорно заданным правилам.

Поставленная цель в заявленном устройстве поиска информации достигается тем, что в известном устройстве поиска информации, содержащем N≥2 блоков селекции, регистр стратегии поиска, формирователь временных интервалов, блок индикации, делитель частоты, тактовый вход которого является первым тактовым входом устройства, выходы "Результат сравнения" блоков селекции соединены с соответствующими входами "Результат сравнения" регистра стратегии поиска, дополнительно введены N блоков хранения маски и блок формирования адреса маски переходов.

При этом в заявленном устройстве К-разрядный, где К=(log2N)+1, выход "Код события" блока формирования адреса маски переходов подключен к K-разрядным входам "Код события" регистра стратегии поиска и блока индикации. Входы разрешения записи всех блоков хранения маски соединены между собой и являются входом разрешения записи устройства. Соответствующие разряды L-разрядных информационных входов, где L≥2, блоков селекции объединены и являются соответствующими разрядами L-разрядного информационного входа устройства. Первые L-разрядные входы "Маска 1" и "Маска 2" j-го блока хранения маски, где j=1, 2, ..., N, являются j-ми первыми L-разрядными входами соответственно "Маска 1" и "Маска 2" устройства. Вторые L-разрядные выходы "Маска 1" и "Маска 2" j-го блока хранения маски подключены к соответствующим вторым L-разрядным входам "Маска 1" и "Маска 2" j-го блока селекции. Выходы "Результат сравнения" блоков селекции соединены с соответствующими входами "Результат сравнения" блока формирования адреса маски переходов. Выход делителя частоты соединен с тактовым входом формирователя временных интервалов. Вход "Начальный сброс" формирователя временных интервалов соединен с входом "Начальный сброс" блока формирования адреса маски переходов и является входом "Начальный сброс" устройства. При этом М-разрядный вход "Код времени ожидания" формирователя временных интервалов, где М≥2 - разрядность кода времени ожидания, является M-разрядным входом "Код времени ожидания" устройства, а выход формирователя временных интервалов соединен с входом "Сброс" блока формирования адреса маски переходов. Сигнальный выход регистра стратегии поиска соединен с сигнальными входами формирователя временных интервалов и блока формирования адреса маски переходов. K-разрядный адресный вход, управляющий вход, N-разрядный информационный вход и разрешающий вход регистра стратегии поиска являются соответственно K-разрядным адресным входом, управляющим входом, N-разрядным информационным входом и разрешающим входом устройства. Входы "Выбор кристалла" и "Чтение/запись" регистра стратегии поиска являются соответственно входами "Выбор кристалла" и "Чтение/запись" устройства. N-разрядный вход "Правило завершения поиска" и выход "Результат поиска" блока индикации являются соответственно N-разрядным входом "Правило завершения поиска" и выходом "Результат поиска" устройства.

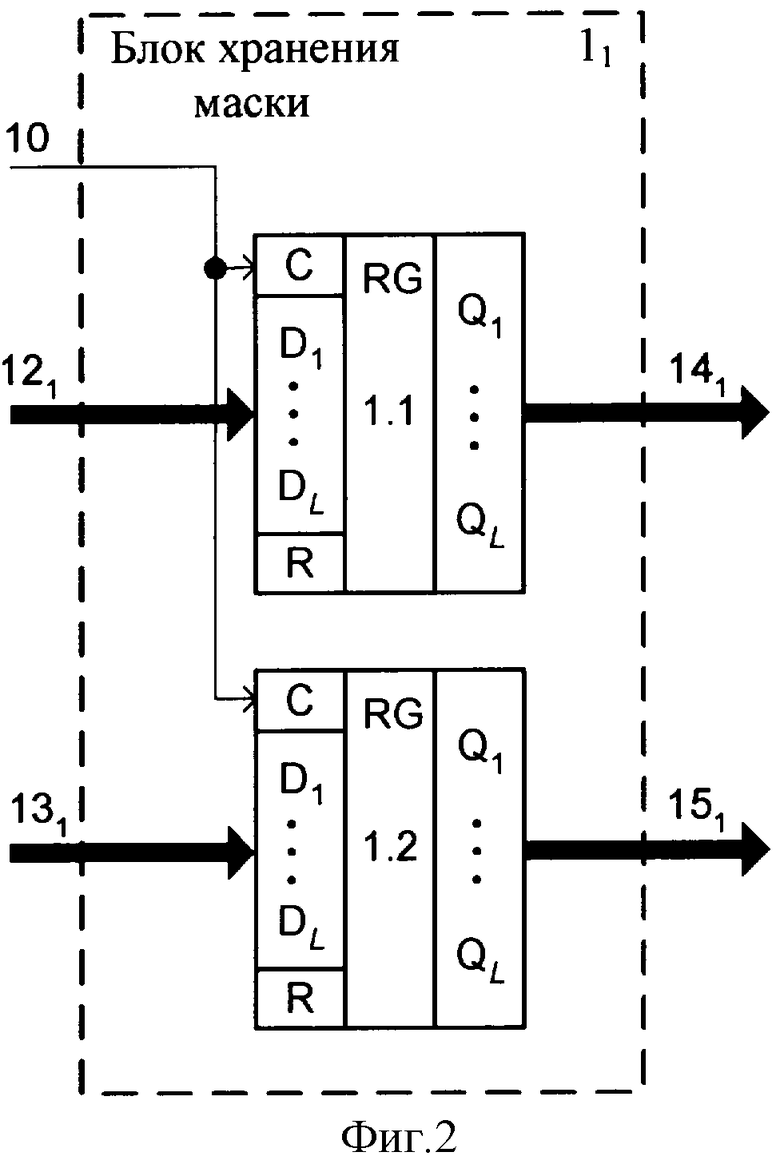

Блок хранения маски состоит из первого и второго регистров. Информационные выходы первого регистра являются соответствующими разрядами второго L-разрядного выхода "Маска 1" блока хранения маски, а информационные выходы второго регистра являются соответствующими разрядами второго L-разрядного выхода "Маска 2" блока хранения маски. Входы разрешения записи первого и второго регистров соединены между собой и являются входом разрешения записи блока хранения маски. Информационные входы первого регистра являются соответствующими разрядами первого L-разрядного входа "Маска 1" блока хранения маски, а информационные входы второго регистра являются соответствующими разрядами первого L-разрядного входа "Маска 2" блока хранения маски.

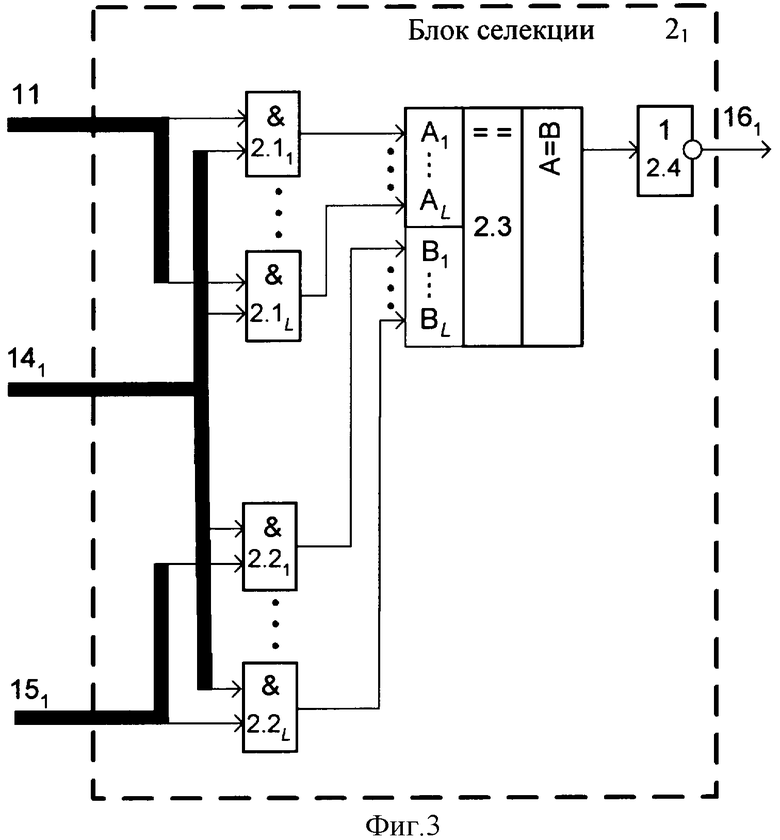

Блок селекции состоит из первой и второй групп двухвходовых элементов И по L элементов в каждой группе, компаратора, инвертора, инверсный выход которого является выходом "Результат сравнения" блока селекции. Вход инвертора подключен к выходу равенства компаратора. При этом i-ый, где i=1, 2, ..., L, вход первой группы информационных входов компаратора соединен с выходом i-го двухвходового элемента И первой группы двухвходовых элементов И, а i-ый вход второй группы информационных входов компаратора соединен с выходом i-го двухвходового элемента И второй группы двухвходовых элементов И. Первый вход i-го двухвходового элемента И первой группы двухвходовых элементов И является i-ым разрядом L-разрядного информационного входа блока селекции. Второй вход i-го двухвходового элемента И первой группы двухвходовых элементов И соединен с первым входом i-го двухвходового элемента И второй группы двухвходовых элементов И и является i-ым разрядом второго L-разрядного входа "Маска 1" блока селекции. Второй вход i-го двухвходового элемента И второй группы двухвходовых элементов И является i-ым разрядом второго L-разрядного входа "Маска 2" блока селекции.

Формирователь временных интервалов состоит из первого двухвходового элемента ИЛИ, JK-триггера, первого двухвходового элемента И, инвертора, второго двухвходового элемента И, второго двухвходового элемента ИЛИ, счетчика. Выход переполнения счетчика соединен со вторыми входами второго двухвходового элемента И и первого двухвходового элемента ИЛИ. Первый вход первого двухвходового элемента ИЛИ соединен с первым входом второго двухвходового элемента ИЛИ и является входом "Начальный сброс" формирователя временных интервалов. Выход первого двухвходового элемента ИЛИ соединен со вторым информационным входом JK-триггера, первый информационный вход которого соединен с входом разрешения записи счетчика и является сигнальным входом формирователя временных интервалов. При этом e-ый, где e=1, 2, ..., М, информационный вход счетчика является e-ым разрядом M-разрядного входа "Код времени ожидания" формирователя временных интервалов. Вход сброса счетчика соединен с выходом второго двухвходового элемента ИЛИ. Счетный вход счетчика соединен с выходом первого двухвходового элемента И, первый вход которого является вторым тактовым входом формирователя временных интервалов. Выход JK-триггера соединен с вторым входом первого двухвходового элемента И и входом инвертора, выход которого соединен с первым входом второго двухвходового элемента И. Выход второго двухвходового элемента И соединен с вторым входом второго двухвходового элемента ИЛИ и является выходом "Сброс" формирователя временных интервалов.

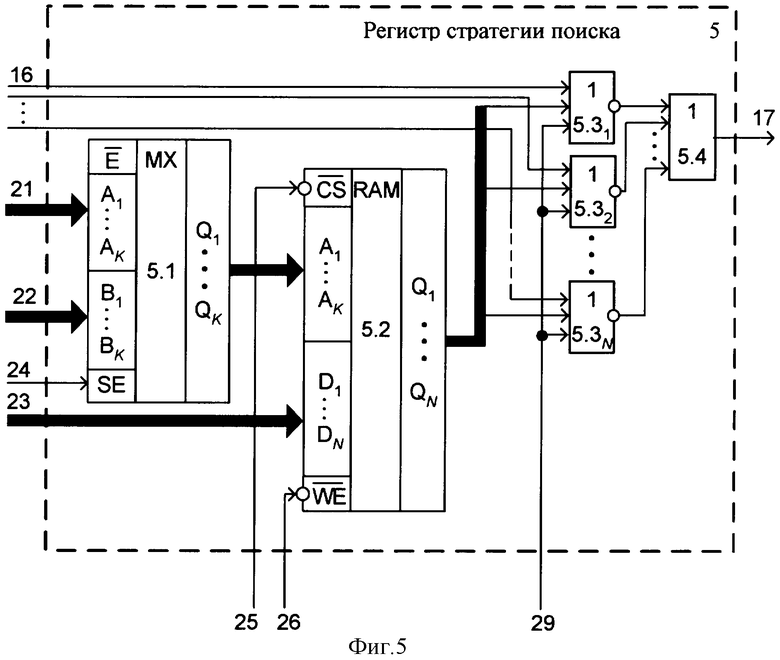

Регистр стратегии поиска состоит из селектора мультиплексора, оперативного запоминающего устройства, N трехвходовых элементов ИЛИ-НЕ, N-входового элемента ИЛИ. Выход N-входового элемента ИЛИ является сигнальным выходом регистра стратегии поиска. При этом j-ый вход N-входового элемента ИЛИ соединен с инверсным выходом j-го трехвходового элемента ИЛИ-НЕ. Первый вход j-го трехвходового элемента ИЛИ-НЕ является j-ым входом "Результат сравнения" регистра стратегии поиска. Второй вход j-го трехвходового элемента ИЛИ-НЕ соединен с j-ым информационным выходом оперативного запоминающего устройства, а третьи входы всех трехвходовых элементов ИЛИ-НЕ соединены между собой и являются разрешающим входом регистра стратегии поиска. При этом, r-ый, где r=1, 2, ..., К, адресный вход оперативного запоминающего устройства соединен с r-ым выходом селектора мультиплексора, а j-ый информационный вход оперативного запоминающего устройства является j-ым разрядом N-разрядного информационного входа регистра стратегии поиска. Инверсные входы "Выбор кристалла" и "Чтение/запись" оперативного запоминающего устройства являются соответственно входами "Выбор кристалла" и "Чтение/запись" регистра стратегии поиска. При этом r-ый вход первой группы информационных входов селектора мультиплексора является r-ым разрядом К-разрядного входа "Код события" регистра стратегии поиска, а r-ый вход второй группы информационных входов селектора мультиплексора является r-ым разрядом K-разрядного адресного входа регистра стратегии поиска. Управляющий вход селектора мультиплексора является управляющим входом регистра стратегии поиска.

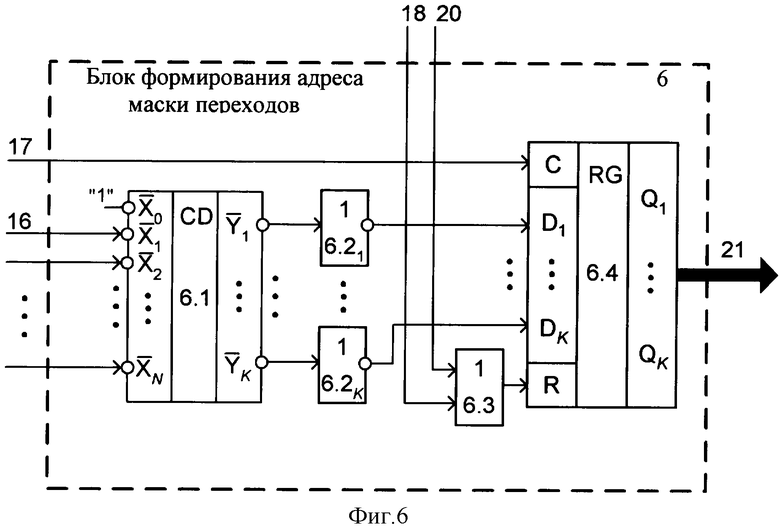

Блок формирования адреса маски переходов состоит из шифратора, К инверторов, двухвходового элемента ИЛИ, регистра, r-ый информационный выход которого является r-ым разрядом K-разрядного выхода "Код события" блока формирования адреса маски переходов. При этом r-ый информационный вход регистра соединен с инверсным выходом r-го инвертора. Вход разрешения записи регистра является сигнальным входом блока формирования адреса маски переходов. Вход сброса регистра соединен с выходом двухвходового элемента ИЛИ. Первый и второй вход двухвходового элемента ИЛИ являются соответственно входом "Сброс" и входом "Начальный сброс" блока формирования адреса маски переходов. Вход r-го инвертора подключен к r-му инверсному выходу шифратора, j-ый инверсный вход которого является j-ым входом "Результат сравнения" блока формирования адреса вектора переходов.

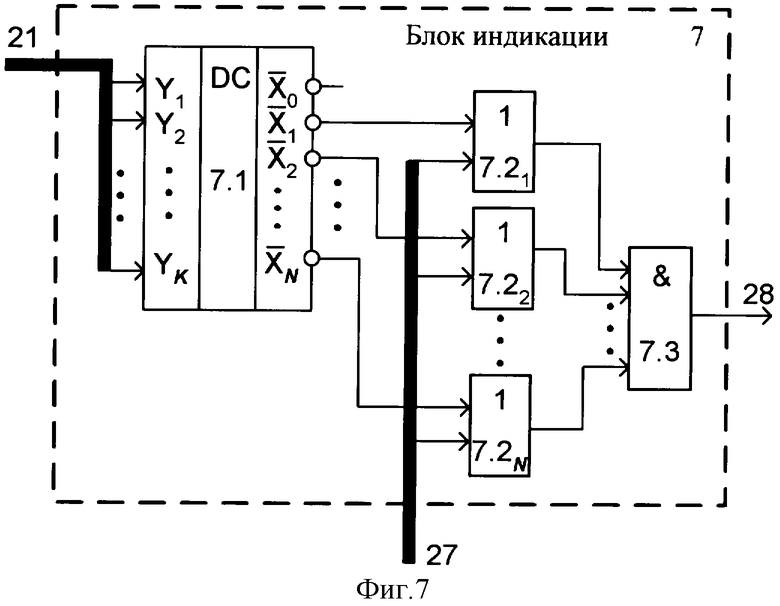

Блок индикации состоит из дешифратора, N двухвходовых элементов ИЛИ, N-входового элемента И, выход которого является выходом "Результат поиска" блока индикации. При этом j-ый вход N-входового элемента И соединен с выходом j-го двухвходового элемента ИЛИ. Первый вход j-го двухвходового элемента ИЛИ соединен с j-ым инверсным выходом дешифратора, а второй вход j-го двухвходового элемента ИЛИ является j-ым разрядом N-разрядного входа "Правило завершения поиска" блока индикации. r-ый вход дешифратора является r-ым разрядом K-разрядного адресного входа "Код события" блока индикации.

Благодаря новой совокупности существенных признаков и введению N блоков хранения маски и блока формирования адреса маски переходов, в устройстве обеспечивается возможность идентификации пакетов путем параллельного анализа признаков идентификации и независимость процесса функционирования устройства от эталонных значений признаков идентификации и содержания правил, определяющих порядок обмена пакетами, что при более высокой скорости анализа, обеспечивает расширение области применения устройства.

Проведенный заявителем анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественных всем признакам заявленного устройства поиска информации, отсутствуют. Следовательно, заявленное изобретение соответствует условию патентоспособности "Новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного изобретения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует по условию патентоспособности "Изобретательский уровень".

Заявленные объекты изобретения поясняются чертежами, на которых

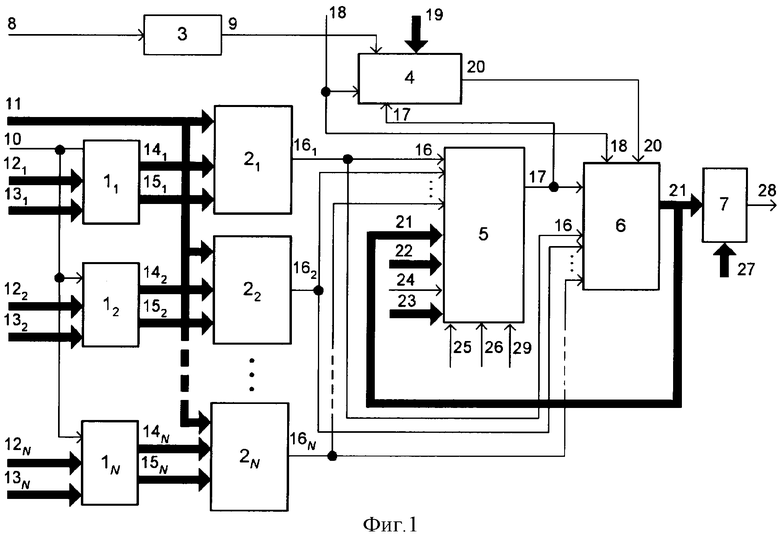

на фиг.1 - устройство поиска информации;

на фиг.2 - регистр хранения маски;

на фиг.3 - блок селекции;

на фиг.4 - формирователь временных интервалов;

на фиг.5 - регистр стратегии поиска;

на фиг.6 - блок формирования адреса вектора переходов;

на фиг.7 - блок индикации;

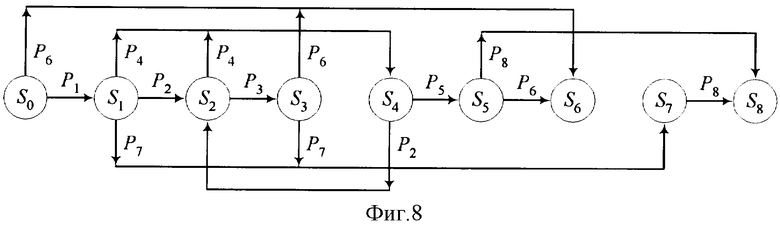

на фиг.8 - пример сценария поиска;

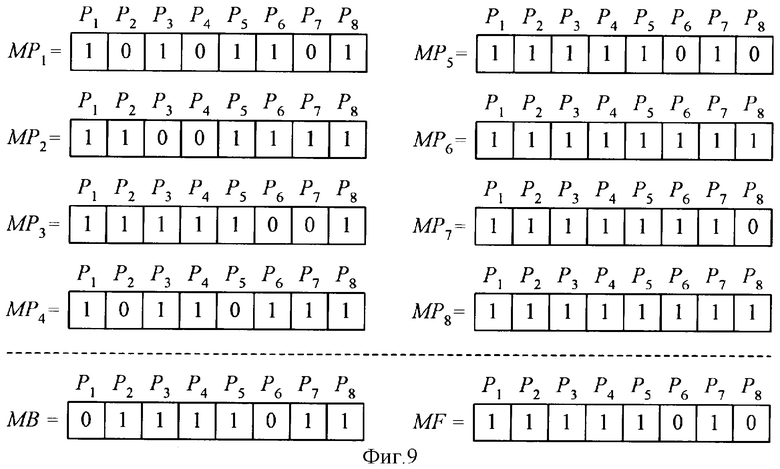

на фиг.9 - пример заполнения масок переходов, маски начала сценария и маски окончания сценария.

Устройство (см. фиг.1) состоит из N, где N≥2,блоков селекции 21-2N, регистра стратегии поиска 5, формирователя временных интервалов 4, блока индикации 7, делителя частоты 3, N блоков хранения маски 11-1N, блока формирования адреса маски переходов 6.

Элементы соединены между собой следующим образом (см. фиг.1). K-разрядный, где К=(log2N)+1, выход "Код события" 21 которого подключен к K-разрядным входам "Код события" 21 регистра стратегии поиска 5 и блока индикации 7. Входы разрешения записи 10 всех блоков хранения маски соединены между собой и являются входом разрешения записи 10 устройства. Соответствующие разряды L-разрядных информационных входов 11, где L≥2, блоков селекции 21-2N объединены и являются соответствующими разрядами L-разрядного информационного входа устройства. Первые L-разрядные входы "Маска 1" 121-12N и "Маска 2" 131-13N j-го блока хранения маски 11-1N, где j=1, 2, ..., N являются j-ми первыми L-разрядными входами соответственно "Маска 1" и "Маска 2" устройства. Вторые L-разрядные выходы "Маска 1" 141-14N и "Маска 2" 151-15N j-го блока хранения маски 11-1N подключены к соответствующим вторым L-разрядным входам "Маска 1" и "Маска 2" j-го блока селекции 21-2N. Выходы "Результат сравнения" 161-16N блоков селекции 21-2N соединены с соответствующими входами "Результат сравнения" регистра стратегии поиска 5 и блока формирования адреса маски переходов 6. Тактовый вход делителя частоты 3 является первым тактовым входом 8 устройства, а его выход соединен с тактовым входом 9 формирователя временных интервалов 4. Вход "Начальный сброс" 18 формирователя временных интервалов соединен с входом "Начальный сброс" 18 блока формирования адреса маски переходов 6 и является входом "Начальный сброс" устройства. При этом M-разрядный вход "Код времени ожидания" 19 формирователя временных интервалов 4, где М≥2 - разрядность кода времени ожидания является M-разрядным входом "Код времени ожидания" 19 устройства, а выход формирователя временных интервалов 4 соединен с входом "Сброс" 20 блока формирования адреса маски переходов 6. Сигнальный выход 17 регистра стратегии поиска 5 соединен с сигнальными входами 17 формирователя временных интервалов 4 и блока формирования адреса маски переходов 6. K-разрядный адресный вход 22, управляющий вход 24, N-разрядный информационный вход 23 и разрешающий вход 29 регистра стратегии поиска 5 являются соответственно K-разрядным адресным входом 22, управляющим входом 24, N-разрядным информационным входом 23 и разрешающим входом 29 устройства. Входы "Выбор кристалла" 25 и "Чтение/запись" 26 регистра стратегии поиска 5 являются соответственно входами "Выбор кристалла" 25 и "Чтение/запись" 26 устройства. N-разрядный вход "Правило завершения поиска" 27 и выход "Результат поиска" 28 блока индикации 7 являются соответственно N-разрядным входом "Правило завершения поиска" 27 и выходом "Результат поиска" 28 устройства.

Делитель частоты 8 предназначен для увеличения периода следования поступающей на его вход последовательности импульсов. Схемы реализации такого делителя частоты известны. В частности, делитель частоты может быть построен на счетчике. См., например, П.П.Мальцев, Н.С.Долидзе и др., справочник "Цифровые интегральные микросхемы". - М.: "Радио и связь", 1994, с.62-74. При этом входом делителя будет счетный вход счетчика, а выходом делителя - один из выходов счетчика.

Блоки хранения маски 11-1N предназначены для хранения битовых масок, используемых для идентификации элементов входящего потока данных. Блок хранения маски может быть реализован по любой известной схеме с учетом описанных функций. В частности, его схема, показанная на фиг.2, состоит из первого 1.1 и второго 1.2 регистров. Информационные выходы первого регистра 1.1 являются соответствующими разрядами второго L-разрядного выхода "Маска 1" блока хранения маски, а информационные выходы второго регистра 1.2 являются соответствующими разрядами второго L-разрядного выхода "Маска 2" блока хранения маски. Входы разрешения записи первого 1.1 и второго 1.2 регистров соединены между собой и являются входом разрешения записи 10 блока хранения маски. Информационные входы первого регистра 1.1 являются соответствующими разрядами первого L-разрядного входа "Маска 1" блока хранения маски, а информационные входы второго регистра 1.2 являются соответствующими разрядами первого L-разрядного входа "Маска 2" блока хранения маски.

Первый 1.1 и второй 1.2 регистры предназначены для хранения соответственно первой и второй битовой маски. Описание работы и схема таких регистров известны и приведены, например, в книге: П.П.Мальцев, Н.С.Долидзе и др., "Цифровые интегральные микросхемы: справочник". - М.: "Радио и связь", 1994, с.57-62.

Блоки селекции 21-2N предназначены для идентификации соответствующих элементов входящего потока данных и формирования результата идентификации. Блок селекции может быть реализован по любой известной схеме с учетом описанных функций. В частности, его схема, показанная на фиг.3, состоит из первой и второй групп двухвходовых элементов И 2.11-2.1L, 2.21-2.2L по L элементов в каждой группе, компаратора 2.3, инвертора 2.4, инверсный выход которого является выходом "Результат сравнения" 161 блока селекции. Вход инвертора подключен к выходу равенства компаратора. При этом i-ый, где i=1, 2, ..., L, вход первой группы информационных входов компаратора соединен с выходом i-го двухвходового элемента И первой группы двухвходовых элементов И 2.11- 2.1L, а i-ый вход второй группы информационных входов компаратора соединен с выходом i-го двухвходового элемента И второй группы двухвходовых элементов И 2.21-2.2L. Первый вход i-го двухвходового элемента И первой группы двухвходовых элементов И 2.11-2.1L является i-ым разрядом L-разрядного информационного входа 11 блока селекции. Второй вход i-го двухвходового элемента И первой группы двухвходовых элементов И 2.11-2.1L соединен с первым входом i-го двухвходового элемента И второй группы двухвходовых элементов И 2.21-2.2L и является i-ым разрядом второго L-разрядного входа "Маска 1" 141 блока селекции, а второй вход i-го двухвходового элемента И второй группы двухвходовых элементов И 2.21-2.2L является i-ым разрядом второго L-разрядного входа "Маска 2" 151 блока селекции.

Компаратор 2.3 предназначен для сравнения двоичных кодов, установленных на его входах, и формирования результата сравнения. Описание работы и схема компаратора приведены, например, в книге: В.Л.Шило "Популярные микросхемы ТТЛ". М.: "АРГУС", 1993, с.183-184.

Формирователь временных интервалов 4 предназначен для контроля интервала времени между элементами входящего потока данных и формирования сигнала по его истечении. Формирователь временных интервалов может быть реализован по любой известной схеме с учетом описанных функций. В частности, его схема, показанная на фиг.4, состоит из первого двухвходового элемента ИЛИ 4.1, JK-триггера 4.2, первого двухвходового элемента И 4.3, инвертора 4.4, второго двухвходового элемента И 4.5, второго двухвходового элемента ИЛИ 4.6, счетчика 4.7. Выход переполнения счетчика 4.7 соединен со вторыми входами второго двухвходового элемента И 4.5 и первого двухвходового элемента ИЛИ 4.1. Первый вход первого двухвходового элемента ИЛИ 4.1 соединен с первым входом второго двухвходового элемента ИЛИ 4.6 и является входом "Начальный сброс" 18 формирователя временных интервалов. Выход первого двухвходового элемента ИЛИ 4.1 соединен со вторым информационным входом JK-триггера 4.2. Первый информационный вход JK-триггера 4.2 соединен с входом разрешения записи счетчика и является сигнальным входом 17 формирователя временных интервалов. При этом e-ый, где e=1, 2, ..., М, информационный вход счетчика является e-ым разрядом M-разрядного входа "Код времени ожидания" 19 формирователя временных интервалов. Вход сброса счетчика соединен с выходом второго двухвходового элемента ИЛИ 4.6, а счетный вход счетчика соединен с выходом первого двухвходового элемента И 4.3. Первый вход первого двухвходового элемента И 4.3 является вторым тактовым входом 9 формирователя временных интервалов. Выход JK-триггера соединен с вторым входом первого двухвходового элемента И 4.3 и входом инвертора 4.4, выход которого соединен с первым входом второго двухвходового элемента И 4.5. Выход второго двухвходового элемента И 4.5 соединен с вторым входом второго двухвходового элемента ИЛИ 4.6 и является выходом "Сброс" 20 формирователя временных интервалов.

JK-триггер 4.2 предназначен для хранения логического значения, определяющего режим функционирования формирователя временных интервалов, и может быть построен по любой известной схеме. См., например, в книге: Б.В.Тарабрин, Л.Ф.Лунин, Ю.Н.Смирнов и др. "Интегральные микросхемы: справочник". - М.: "Энергоатомиздат", 1985, с.67.

Счетчик 4.7 предназначен для счета поступающих на его вход импульсов и выработки управляющего сигнала по истечении интервала времени, определяемого значением кода начального заполнения счетчика и периодом следования тактовых импульсов, то есть выполняет функцию настраиваемого таймера. Описание работы и схема такого счетчика известны и приведены, например, в книге: П.П.Мальцев, Н.С.Долидзе и др., "Цифровые интегральные микросхемы: справочник". - М.: "Радио и связь", 1994, с.71.

Регистр стратегии поиска 5 предназначен для проверки соответствия порядка следования идентифицированных элементов входящего потока данных заданным правилам и формирования сигнала при поступлении элемента, ожидаемого в соответствии с правилами. Регистр стратегии поиска может быть реализован по любой известной схеме с учетом описанных функций. В частности, его схема, показанная на фиг.5, состоит из селектора мультиплексора 5.1, оперативного запоминающего устройства 5.2, N трехвходовых элементов ИЛИ-НЕ 5.31-5.3N, N-входового элемента ИЛИ 5.4, выход которого является сигнальным выходом 17 регистра стратегии поиска. При этом j-ый вход N-входового элемента ИЛИ 5.4 соединен с инверсным выходом j-го трехвходового элемента ИЛИ-НЕ. Первый вход j-го трехвходового элемента ИЛИ-НЕ является j-ым входом "Результат сравнения" 16 регистра стратегии поиска. Второй вход j-го трехвходового элемента ИЛИ-НЕ соединен с j-ым информационным выходом оперативного запоминающего устройства 5.2, а третьи входы всех трехвходовых элементов ИЛИ-НЕ соединены между собой и являются разрешающим входом 29 регистра стратегии поиска. При этом r-ый, где r=1, 2, ..., К, адресный вход оперативного запоминающего устройства 5.2 соединен с r-ым выходом селектора мультиплексора 5.1, а j-ый информационный вход оперативного запоминающего устройства является j-ым разрядом N-разрядного информационного входа 23 регистра стратегии поиска. Инверсные входы "Выбор кристалла" и "Чтение/запись" оперативного запоминающего устройства являются соответственно входами "Выбор кристалла" 25 и "Чтение/запись" 26 регистра стратегии поиска. При этом r-ый вход первой группы информационных входов селектора мультиплексора является r-ым разрядом K-разрядного входа "Код события" 21 регистра стратегии поиска, а r-ый вход второй группы информационных входов селектора мультиплексора является r-ым разрядом K-разрядного адресного входа 22 регистра стратегии поиска. Управляющий вход селектора мультиплексора является управляющим входом 24 регистра стратегии поиска.

Селектор мультиплексора 5.1 предназначен для коммутации одной из двух групп информационных входов на его выходы. Схемы реализации такого селектора-мультиплексора известны. См., например, в книге: П.П.Мальцев, Н.С.Долидзе и др., "Цифровые интегральные микросхемы: справочник". - М.: "Радио и связь", 1994, с.33-40.

Оперативное запоминающее устройство 5.2 предназначено для хранения масок, содержащих правила, определяющие требуемый порядок следования идентифицированных элементов входящего потока данных. Схема реализации оперативного запоминающего устройства известна. См., например, в книге: В.Л.Шило "Популярные цифровые микросхемы". - М.: "Радио и связь", 1987, с.164-166.

Блок формирования адреса маски переходов предназначен для формирования и хранения кода, соответствующего маске, определяющей следующий элемент, который должен быть идентифицирован во входящем потоке данных. Блок формирования адреса вектора переходов может быть реализован по любой известной схеме с учетом описанных функций. В частности, его схема, показанная на фиг.6, состоит из шифратора 6.1, К инверторов 6.21-6.2K, двухвходового элемента ИЛИ 6.3, регистра 6.4, r-ый информационный выход которого является r-ым разрядом К-разрядного выхода "Код события" 21 блока формирования адреса маски переходов. При этом r-ый информационный вход регистра 6.4 соединен с инверсным выходом r-го инвертора. Вход разрешения записи регистра является сигнальным входом 17 блока формирования адреса маски переходов. Вход сброса регистра соединен с выходом двухвходового элемента ИЛИ 6.3, первый и второй вход которого являются соответственно входом "Сброс" 20 и входом "Начальный сброс" 18 блока формирования адреса маски переходов. Вход r-го инвертора подключен к r-му инверсному выходу шифратора, j-ый инверсный вход которого является j-ым входом "Результат сравнения" 16 блока формирования адреса вектора переходов.

Шифратор 6.1 предназначен для формирования кода, соответствующего маске, определяющей следующий элемент, который должен быть идентифицирован во входящем потоке данных, путем преобразования сигнала низкого уровня на одном из его входов в соответствующий двоичный код на его выходах. Схема реализации шифраторов приоритетов известна. См., например, в книге: П.П.Мальцев, Н.С.Долидзе и др., "Цифровые интегральные микросхемы: справочник". - М.: "Радио и связь", 1994, с.40-41.

Регистр 6.4 предназначен для хранения кода, соответствующего маске, определяющей следующий элемент, который должен быть идентифицирован во входящем потоке данных. Описание работы и схема таких регистров известны и приведены, например, в книге: П.П.Мальцев, Н.С.Долидзе и др., "Цифровые интегральные микросхемы: справочник". - М.: "Радио и связь", 1994, с.57-62.

Блок индикации предназначен для обнаружения признаков, свидетельствующих о завершении заданной правилами последовательности элементов входящего потока данных и формирования соответствующего сигнала. Блок индикации может быть реализован по любой известной схеме с учетом описанных функций. В частности, его схема, показанная на фиг.7, состоит из дешифратора 7.1, N двухвходовых элементов ИЛИ 7.21-7.2N, N-входового элемента И 7.3, выход которого является выходом "Результат поиска" 28 блока индикации. При этом j-ый вход N-входового элемента И соединен с выходом j-го двухвходового элемента ИЛИ 7.21-7.2N. Первый вход j-го двухвходового элемента ИЛИ соединен с j-ым инверсным выходом дешифратора, а второй вход j-го двухвходового элемента ИЛИ является j-ым разрядом N-разрядного входа "Правило завершения поиска" 27 блока индикации. r-ый вход дешифратора является r-ым разрядом K-разрядного адресного входа "Код события" 21 блока индикации.

Дешифратор 7.1 предназначен для преобразования поступающего на его вход двоичного кода в сигнал низкого уровня на соответствующем выходе. Схемы реализации дешифратора низкого уровня известны. См., например, в книге: П.П.Мальцев, Н.С.Долидзе и др., "Цифровые интегральные микросхемы: справочник". - М.: "Радио и связь", 1994, с.41-47.

В заявленном устройстве реализован синтаксический подход к распознаванию образов (Гонсалес Р., Ту Дж. Принципы распознавания образов. - М.: Мир, 1978. - 411 с.), основанный на идентификации отдельных элементов входящего потока данных - блоков двоичной информации (БДИ), путем параллельного анализа значений признаков идентификации и контроля порядка их следования на предмет соответствия заданным правилам. В качестве признаков идентификации, используются значения битов в соответствующих позициях БДИ. Правила следования БДИ задаются формальной грамматикой - сценарием поиска.

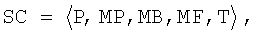

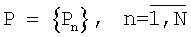

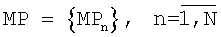

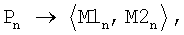

Для пояснения работы устройства необходимо рассмотреть правила задания сценария поиска. Сценарий поиска SC может быть представлен следующей схемой:

где  - множество типов БДИ, входящих в состав сценария;

- множество типов БДИ, входящих в состав сценария;

- множество масок переходов;

- множество масок переходов;

MB - маска начала сценария поиска;

MF - маска окончания сценария поиска;

Т - время ожидания очередного БДИ.

Идентификация типа БДИ в устройстве осуществляется путем сравнения значений идентификационных битов БДИ с их эталонными значениями. Под идентификационными битами понимаются биты БДИ, значения которых позволяют однозначно идентифицировать тип БДИ. Для каждого типа БДИ множество идентификационных битов может быть индивидуальным. В связи с этим каждому типу БДИ ставится в соответствие две битовые маски:

где М1n - первая битовая маска БДИ n-го типа;

М2n - вторая битовая маска БДИ n-го типа.

Битовые маски содержат L разрядов, где L - максимально возможное количество разрядов в БДИ, используемых в сценарии поиска. Первая битовая маска предназначена для указания позиций идентификационных битов БДИ. Значения логической единицы в разрядах первой битовой маски соответствуют позициям идентификационных битов. Во всех остальных разрядах битовой маски устанавливаются значения логического нуля. Вторая битовая маска предназначена для задания эталонных значений, которым должны соответствовать значения идентификационных битов. При этом разряды второй битовой маски, не являющиеся идентификационными, могут иметь произвольные значения, так как не влияют на процесс идентификации БДИ.

Множество масок переходов используется для задания порядка следования БДИ в рамках сценария. Множество содержит N масок переходов, каждая из которых содержит N двоичных разрядов. Таким образом каждому типу БДИ соответствует своя маска переходов. При этом n-ая маска переходов МРn содержит информацию о типах БДИ, которые согласно сценария поиска ожидаются после наблюдения БДИ n-го типа. Указанная информация задается путем установки значения логического нуля в разрядах маски переходов, порядковые номера которых соответствуют типам ожидаемых БДИ. Во всех остальных разрядах маски переходов устанавливаются значения логической единицы.

Маска начала сценария поиска предназначена для указания типов БДИ, которые ожидаются первыми в сценарии поиска - начальных БДИ. Маска MB содержит N двоичных разрядов. В разрядах маски начала сценария поиска, номера которых соответствуют начальным типам БДИ, устанавливаются значения логического нуля. Во всех остальных разрядах маски начала сценария поиска устанавливаются значения логической единицы.

Маска окончания сценария поиска предназначена для указания типов БДИ, наблюдение которых свидетельствует о завершении сценария поиска - конечных БДИ. Маска MF содержит N двоичных разрядов. В разрядах маски окончания сценария поиска, номера которых соответствуют конечным типам БДИ, устанавливаются значения логического нуля. Во всех остальных разрядах маски окончания сценария поиска устанавливаются значения логической единицы.

Время ожидания очередного БДИ Т задает максимально допустимый интервал времени, в течение которого ожидается очередной БДИ, заданного сценарием поиска типа. В том случае, если в течение заданного интервала времени ожидаемый тип БДИ не будет обнаружен, сценарий поиска прерывается, и осуществляется переход к ожиданию начальных БДИ. Время ожидания очередного БДИ задается в виде M-разрядного кода. При этом наименьшему времени ожидания соответствует наибольший код, являющийся дополнением до максимального числа, представленного в M-разрядном коде.

Ниже работа устройства рассмотрена как процесс перехода устройства из состояния в состояние. Множество состояний  , устройства соответствует множеству типов БДИ, входящих в состав сценария. При обнаружении очередного заданного сценарием типа БДИ устройство переходит в состояние, номер которого соответствует типу обнаруженного БДИ. Находясь в одном из состояний устройство ожидает появления БДИ, типы которых определяются маской переходов, номер которой соответствует номеру текущего состояния устройства.

, устройства соответствует множеству типов БДИ, входящих в состав сценария. При обнаружении очередного заданного сценарием типа БДИ устройство переходит в состояние, номер которого соответствует типу обнаруженного БДИ. Находясь в одном из состояний устройство ожидает появления БДИ, типы которых определяются маской переходов, номер которой соответствует номеру текущего состояния устройства.

На фиг.8 приведен пример сценария поиска, включающий N=8 типов БДИ. Соответствующее приведенному сценарию поиска заполнение масок переходов, маски начала сценария и маски окончания сценария приведено на фиг.9.

Инициализация устройства включает в себя проведение следующих операций:

начальный сброс устройства;

установка первой и второй битовых масок;

установка маски начала сценария и масок переходов;

установка маски окончания сценария поиска;

установка времени ожидания очередного БДИ.

Начальный сброс устройства осуществляется следующим образом. На разрешающем входе 29 устройства устанавливают значение логической единицы, которая поступает на соответствующий вход регистра стратегии поиска 5. Логическая единица на разрешающем входе 29 регистра стратегии поиска 5, поступая на третьи входы всех трехвходовых элементов ИЛИ-НЕ 5.31-5.3N, обеспечивает наличие логического нуля на их выходах вне зависимости от логических значений, установленных на первых и вторых входах. В связи с этим на сигнальном выходе 17 регистра стратегии поиска 5 будет установлено значение логического нуля. Логический ноль с сигнального выхода 17 регистра стратегии поиска 5 поступает на соответствующий вход формирователя временных интервалов 4 и далее - на первый информационный вход J JK-триггера 4.2. На входе "Начальный сброс" 18 устройства устанавливают значение логической единицы, которая поступает на соответствующие входы формирователя временных интервалов 4 и блока формирования адреса вектора переходов 6. Значение логической единицы с входа "Начальный сброс" 18 формирователя временных интервалов 4 через первый двухвходовый элемент ИЛИ 4.1 поступает на второй информационный вход К JK-триггера 4.2, а через второй двухвходовый элемент ИЛИ 4.6 - на вход сброса R счетчика 4.7. Логическая единица на входе К JK-триггера при наличии логического нуля на его входе J приводит к установке логического нуля на выходе JK-триггера, который поступая на второй вход двухвходового элемента И 4.3 приводит к установке значения логического нуля на его выходе вне зависимости от логических значений на его первом входе. Логическая единица на входе сброса R счетчика 4.7 обеспечивает установку логического нуля на его выходе переполнения Р. Значение логического нуля с выхода переполнения Р счетчика 4.7 поступает на второй вход второго двухвходового элемента И 4.5, что приводит к безусловной установке на его выходе, а соответственно и на выходе "Сброс" 20 формирователя временных интервалов 4 значения логического нуля. Логическая единица с входа "Начальный сброс" блока формирования адреса маски переходов 6 через двухвходовый элемент ИЛИ 6.3 поступает на вход сброса R регистра 6.4, что приводит к установке логического нуля на его выходах Q1-QK, а соответственно и на всех разрядах К-разрядного выхода "Код события" 21. По завершении операции начального сброса на входе "Начальный сброс" 18 устройства устанавливают значение логического нуля, что приводит к установке значения логического нуля на втором информационном входе К JK-триггера 4.2 и на входе сброса R счетчика 4.7.

Установка первой и второй битовых масок, обеспечивающих идентификацию каждого из N типов БДИ, осуществляется в соответствующие блоки хранения маски 11-1N. Для этого на первых L-разрядных входах "Маска 1" 121-12N каждого из N блоков хранения маски 11-1N устанавливают соответствующие первые битовые маски, а на первых L-разрядных входах "Маска 2" 131-13N каждого из N блоков хранения маски 11-1N устанавливают соответствующие вторые битовые маски. На входе разрешения записи 10 устройства устанавливают значение логической единицы, которая поступает на входы инициализации первых и вторых регистров 1.1 и 1.2 каждого из N блоков хранения маски и обеспечивает запись первых и вторых битовых масок в соответствующие регистры. По окончании операции записи на входе разрешения записи 10 устройства устанавливают значение логического нуля.

Установка маски начала сценария поиска и масок переходов осуществляется в оперативное запоминающее устройство 5.2 регистра стратегии поиска 5. При этом маска начала сценария поиска MB должна быть записана в оперативное запоминающее устройство по нулевому адресу, а n-ая маска перехода  , должна быть записана по адресу, соответствующему ее порядковому номеру, то есть адресу, значение которого равно n. Для этого на управляющем входе 24 устройства устанавливают значение логической единицы, которая, поступая на управляющий вход SE селектора-мультиплексора 5.1, обеспечивает коммутацию второй группы информационных входов B1-ВK селектора-мультиплексора 5.1 на его выходы Q1-qK, где К=(log2N)+1 - количество двоичных разрядов, достаточное для адресации N масок переходов и маски начала сценария поиска. На K-разрядном адресном входе 22 устройства устанавливают K-разрядный адрес, по которому в оперативное запоминающее устройство 5.2 должна быть записана маска начала сценария поиска. С выходов Q1-QK селектора-мультиплексора 5.1 K-разрядный адрес поступает на адресные входы A1-Ак оперативного запоминающего устройства 5.2. На N-разрядном информационном входе 23 устройства устанавливают маску начала сценария поиска, которая поступает на информационные входы D1-DN оперативного запоминающего устройства 5.2. Запись осуществляется путем установки логического нуля на входах "Выбор кристалла" 25 и "Чтение/запись" 26 устройства, с которых логический ноль поступает на соответствующие входы

, должна быть записана по адресу, соответствующему ее порядковому номеру, то есть адресу, значение которого равно n. Для этого на управляющем входе 24 устройства устанавливают значение логической единицы, которая, поступая на управляющий вход SE селектора-мультиплексора 5.1, обеспечивает коммутацию второй группы информационных входов B1-ВK селектора-мультиплексора 5.1 на его выходы Q1-qK, где К=(log2N)+1 - количество двоичных разрядов, достаточное для адресации N масок переходов и маски начала сценария поиска. На K-разрядном адресном входе 22 устройства устанавливают K-разрядный адрес, по которому в оперативное запоминающее устройство 5.2 должна быть записана маска начала сценария поиска. С выходов Q1-QK селектора-мультиплексора 5.1 K-разрядный адрес поступает на адресные входы A1-Ак оперативного запоминающего устройства 5.2. На N-разрядном информационном входе 23 устройства устанавливают маску начала сценария поиска, которая поступает на информационные входы D1-DN оперативного запоминающего устройства 5.2. Запись осуществляется путем установки логического нуля на входах "Выбор кристалла" 25 и "Чтение/запись" 26 устройства, с которых логический ноль поступает на соответствующие входы  и

и  оперативного запоминающего устройства 5.2. По окончании записи маски на входе "Выбор кристалла" 25 устанавливают значение логической единицы. Затем на K-разрядном адресном входе 22 устройства устанавливают K-разрядный адрес, по которому в оперативное запоминающее устройство должна быть записана первая маска переходов МР1 (значение адреса равно 1), а на N-разрядном информационном входе 23 устройства устанавливают маску переходов МР1, после чего путем установки значения логического нуля на входе "Выбор кристалла" 25 инициируют операцию записи в оперативное запоминающее устройство 5.2. Аналогичным образом в оперативное запоминающее устройство записывают все N масок переходов. По окончании записи масок переходов в оперативное запоминающее устройство на входе "Чтение/запись" 26 устанавливают значение логической единицы, а на управляющем входе 24 устройства устанавливают значение логического нуля, что обеспечивает коммутацию первой группы информационных входов A1-АK селектора-мультиплексора 5.1 на его выходы Q1-QK.

оперативного запоминающего устройства 5.2. По окончании записи маски на входе "Выбор кристалла" 25 устанавливают значение логической единицы. Затем на K-разрядном адресном входе 22 устройства устанавливают K-разрядный адрес, по которому в оперативное запоминающее устройство должна быть записана первая маска переходов МР1 (значение адреса равно 1), а на N-разрядном информационном входе 23 устройства устанавливают маску переходов МР1, после чего путем установки значения логического нуля на входе "Выбор кристалла" 25 инициируют операцию записи в оперативное запоминающее устройство 5.2. Аналогичным образом в оперативное запоминающее устройство записывают все N масок переходов. По окончании записи масок переходов в оперативное запоминающее устройство на входе "Чтение/запись" 26 устанавливают значение логической единицы, а на управляющем входе 24 устройства устанавливают значение логического нуля, что обеспечивает коммутацию первой группы информационных входов A1-АK селектора-мультиплексора 5.1 на его выходы Q1-QK.

Установка маски окончания сценария поиска MF заключается в установке на разрядах К-разрядного входа "Правило завершения поиска" 27 устройства логических значений, соответствующих значениям битов маски окончания сценария поиска.

Установка времени ожидания очередного БДИ заключается в установке на разрядах на M-разрядного входа "Код времени ожидания" 19 устройства логических значений, соответствующих значениям разрядов кода времени ожидания.

После выполнения указанных операций устройство готово к работе.

В начальный период, когда подлежащие анализу БДИ не поступают на вход устройства, на вход делителя частоты 3 через первый тактовый вход 8 устройства от внешнего генератора поступают тактовые импульсы. С выхода делителя частоты 3 тактовые импульсы поступают на второй тактовый вход 9 формирователя временных интервалов 4. В результате проведенной операции начального сброса устройства на всех информационных выходах Q1-QK регистра 6.4, а соответственно и на всех разрядах K-разрядного выхода "Код события" 21 блока формирования маски переходов 6 установлено значение логического нуля. На управляющем входе 24 регистра стратегии поиска 5 установлено значение логического нуля, что обеспечивает коммутацию значений логического нуля с разрядов K-разрядного входа "Код события" 21 регистра стратегии поиска 5 на соответствующие адресные входы А1-АK оперативного запоминающего устройства 5.2. Таким образом, на адресном входе оперативного запоминающего устройства установлен нулевой адрес, указывающий на маску начала сценария поиска. Значения логического нуля с разрядов К-разрядного выхода "Код события" 21 блока формирования адреса маски переходов 6 поступают на соответствующие разряды входа "Код события" 21 блока индикации 7 и далее - на входы Y1-YK дешифратора 7.1. При наличии значения логического нуля на всех входах Y1-YK дешифратора 7.1, на всех его инверсных выходах  будет установлено значение логической единицы. Значения логической единицы с инверсных выходов

будет установлено значение логической единицы. Значения логической единицы с инверсных выходов  дешифратора 7.1 поступает на первые входы соответствующих двухвходовых элементов ИЛИ 7.21-7.2N. В результате на выходах всех двухвходовых элементов ИЛИ 7.21-7.2N устанавливается значение логической единицы вне зависимости от логических значений на их вторых входах. Это приводит к установке значения логической единицы на выходе N-входового элемента И 7.3, а соответственно и на выходе "Результат поиска" 28 устройства. Логические значения на выходе "Результат поиска" 28 устройства имеют следующее значение: логический ноль на указанном выходе означает, что во входящем потоке БДИ обнаружен заданный сценарий поиска, а логическая единица - отсутствие заданного сценария поиска. На входе "Чтение/запись" 26 регистра стратегии поиска 5 установлено значение логической единицы, что обеспечивает перевод оперативного запоминающего устройства 5.2 в режим чтения информации. При этом на входе "Выбор кристалла" 25 регистра стратегии поиска 5 также установлено значение логической единицы. На разрешающем входе 29 устройства установлено значение логической единицы, что обеспечивает установку на сигнальном выходе 17 регистра стратегии поиска 5 значения логического нуля. При этом на выходе JK-триггера 4.2, на его первом и втором информационных входах установлено значение логического нуля.

дешифратора 7.1 поступает на первые входы соответствующих двухвходовых элементов ИЛИ 7.21-7.2N. В результате на выходах всех двухвходовых элементов ИЛИ 7.21-7.2N устанавливается значение логической единицы вне зависимости от логических значений на их вторых входах. Это приводит к установке значения логической единицы на выходе N-входового элемента И 7.3, а соответственно и на выходе "Результат поиска" 28 устройства. Логические значения на выходе "Результат поиска" 28 устройства имеют следующее значение: логический ноль на указанном выходе означает, что во входящем потоке БДИ обнаружен заданный сценарий поиска, а логическая единица - отсутствие заданного сценария поиска. На входе "Чтение/запись" 26 регистра стратегии поиска 5 установлено значение логической единицы, что обеспечивает перевод оперативного запоминающего устройства 5.2 в режим чтения информации. При этом на входе "Выбор кристалла" 25 регистра стратегии поиска 5 также установлено значение логической единицы. На разрешающем входе 29 устройства установлено значение логической единицы, что обеспечивает установку на сигнальном выходе 17 регистра стратегии поиска 5 значения логического нуля. При этом на выходе JK-триггера 4.2, на его первом и втором информационных входах установлено значение логического нуля.

При поступлении БДИ, подлежащего анализу, на L-разрядном информационном входе 11 устройства устанавливают логические значения, соответствующие значениям двоичных разрядов БДИ. Момент времени, соответствующий установке БДИ на L-разрядном информационном входе 11 устройства, обозначим как Т1. С L-разрядного информационного входа 11 устройства БДИ поступает на L-разрядные информационные входы блоков селекции 21-2N. Каждый блок селекции осуществляет идентификацию БДИ соответствующего типа. Тип БДИ определяется первой и второй битовыми масками, поступающими соответственно на второй L-разрядный вход "Маска 1" и второй L-разрядный вход "Маска 2" блока селекции. В компараторах 2.3 каждого блока селекции 21-2N происходит сравнение значений идентификационных битов поступившего БДИ с значениями соответствующих битов второй битовой маски. Выделение идентификационных битов осуществляется в первой и второй группах двухвходовых элементов И 2.11-2.1L, 2.21-2.2L каждого блока селекции на основании соответствующей первой битовой маски. В случае равенства сравниваемых значений на выходе равенства "А=В" компаратора 2.3 установится значение логической единицы, в противном случае - значение логического нуля. Логическое значение, соответствующее результату сравнения, с выхода "А=В" компаратора инвертируется инвертором 2.4 и поступает на выход "Результат сравнения" блока селекции. Таким образом, при поступлении БДИ, тип которого соответствует одному из типов БДИ, предусмотренных в сценарии поиска, на выходе "Результат сравнения" блока селекции, в котором обнаружено совпадение значений идентификационных битов поступившего БДИ с соответствующими значениями второй битовой маски, будет установлено значение логического нуля, а на выходах всех остальных блоков селекции - значение логической единицы. При поступлении БДИ, не предусмотренного сценарием поиска, на выходах "Результат сравнения" всех блоков селекции будет установлено значение логической единицы. Логические значения, соответствующие результатам сравнения, с выходов блоков селекции поступают на соответствующие входы "Результат сравнения" (161-16N) регистра стратегии поиска 5 и блока формирования адреса маски переходов 6.

В регистре стратегии поиска 5 осуществляется проверка соответствия идентифицированного блоками селекции типа БДИ типу, ожидаемому согласно сценария поиска. Проверка осуществляется вне зависимости от результатов идентификации БДИ в блоках селекции. Тип (типы) ожидаемого БДИ определяются маской начала сценария поиска или масками переходов, хранящимися в оперативном запоминающем устройстве 5.2. Маска, на соответствие которой осуществляется проверка, определяется К-разрядным адресом, установленным на адресных входах А1-AK оперативного запоминающего устройства 5.2. В качестве адреса используется код, установленный на K-разрядном входе "Код события" 21 регистра стратегии поиска 5. С K-разрядного входа "Код события" 21 указанный код поступает на первую группу информационных входов А1-АK селектора-мультиплексора 5.1, где при наличии на управляющем входе SE селектора-мультиплексора 5.1 значения логического нуля, коммутируется на адресные входы оперативного запоминающего устройства 5.2. Считывание соответствующей маски осуществляется путем установки значения логического нуля на входе "Выбор кристалла" 25 регистра стратегии поиска 5. Установка значения логического нуля на входе "Выбор кристалла" 25 регистра стратегии поиска должна осуществляться с временной задержкой относительно момента времени Т1, определяемой временем задержки сигнала в блоке селекции. Обозначим момент времени установки логического нуля на входе "Выбор кристалла" 25 регистра стратегии поиска 5 как Т2. Проверка соответствия идентифицированного типа БДИ типу, ожидаемому согласно сценария поиска, осуществляется трехвходовыми элементами ИЛИ-НЕ 5.31-5.3N. При этом на первые входы трехвходовых элементов ИЛИ-НЕ 5.31-5.3N поступают логические значения с выходов соответствующих блоков селекции 21-2N, а на вторые входы - логические значения, соответствующие считанной из оперативного запоминающего устройства 5.2 маски. Результаты проверки поступают с выходов трехвходовых элементов ИЛИ-НЕ 5.31-5.3N на соответствующие входы N-входового элемента ИЛИ 5.4 после установки значения логического нуля на разрешающем входе 29 устройства. Установка значения логического нуля на разрешающем входе 29 устройства должна осуществляться с временной задержкой относительно момента времени Т2, определяемой временем считывания информации из оперативного запоминающего устройства 5.2. Обозначим момент времени установки логического нуля на разрешающем входе 29 устройства как T3. В случае совпадения идентифицированного типа БДИ с одним из типов, ожидаемых согласно сценария поиска, на выходе соответствующего трехвходового элемента ИЛИ-НЕ, а следовательно, и на сигнальном выходе 17 регистра стратегии поиска 5 установится значение логической единицы, которое поступает на сигнальный вход 17 блока формирования адреса маски переходов 6 и формирователя временных интервалов 4.

В случае соответствия типа поступившего БДИ типу, ожидаемому согласно сценария поиска, в блоке формирования адреса маски переходов 6 на основании результатов идентификации поступившего БДИ осуществляется формирование адреса, по которому в оперативном запоминающем устройстве 5.2 хранится маска переходов, определяющая следующий за ним тип (типы) БДИ. Логические значения, соответствующие результатам идентификации БДИ с выходов блоков селекции 21-2N, поступают на соответствующие входы "Результат сравнения" 161-16N блока формирования адреса маски переходов 6 и далее - на соответствующие инверсные входы  шифратора 6.1 (нулевой вход шифратора 6.1 не используется, при этом на нем всегда должно быть установлено значение логической единицы). Если поступивший БДИ идентифицирован одним из блоков селекции 21-2N, на инверсном входе шифратора 6.1, номер которого соответствует номеру блока селекции, идентифицировавшего БДИ, будет установлено значение логического нуля, а на всех остальных инверсных входах - значение логической единицы. При этом на инверсных выходах

шифратора 6.1 (нулевой вход шифратора 6.1 не используется, при этом на нем всегда должно быть установлено значение логической единицы). Если поступивший БДИ идентифицирован одним из блоков селекции 21-2N, на инверсном входе шифратора 6.1, номер которого соответствует номеру блока селекции, идентифицировавшего БДИ, будет установлено значение логического нуля, а на всех остальных инверсных входах - значение логической единицы. При этом на инверсных выходах  дешифратора 6.1 установится код, соответствующий инверсному представлению номера входа дешифратора, на котором установлено значение логического нуля. Инверторами 6.21-6.2K данный код преобразуется в код типа БДИ, то есть код, соответствующий номеру блока селекции, идентифицировавшего поступивший БДИ. Данный код используется в качестве адреса, по которому в оперативном запоминающем устройстве 5.2 хранится соответствующая маска переходов. С выходов инверторов 6.21-6.2K K-разрядный код типа БДИ поступает на соответствующие информационные входы D1-DK регистра 6.4. Запись кода типа БДИ в регистр 6.4 осуществляется только при поступлении на сигнальный вход 17 блока формирования адреса маски переходов 6 значения логической единицы, то есть только в том случае, когда в блоке стратегии поиска 5 будет обнаружено соответствие типа поступившего БДИ типу, ожидаемому согласно сценария поиска. В противном случае в регистре 6.4 сохраняется предыдущее значение кода типа БДИ. Таким образом, на K-разрядном выходе "Код события" 21 блока формирования адреса маски переходов 6 всегда установлен код, соответствующий адресу, по которому в оперативном запоминающем устройстве 5.2 хранится маска переходов, определяющая тип (типы) ожидаемых согласно сценария поиска БДИ. С K-разрядного выхода "Код события" 21 блока формирования адреса маски переходов 6 код типа БДИ поступает на соответствующие входы регистра стратегии поиска 5 и блока индикации 7.

дешифратора 6.1 установится код, соответствующий инверсному представлению номера входа дешифратора, на котором установлено значение логического нуля. Инверторами 6.21-6.2K данный код преобразуется в код типа БДИ, то есть код, соответствующий номеру блока селекции, идентифицировавшего поступивший БДИ. Данный код используется в качестве адреса, по которому в оперативном запоминающем устройстве 5.2 хранится соответствующая маска переходов. С выходов инверторов 6.21-6.2K K-разрядный код типа БДИ поступает на соответствующие информационные входы D1-DK регистра 6.4. Запись кода типа БДИ в регистр 6.4 осуществляется только при поступлении на сигнальный вход 17 блока формирования адреса маски переходов 6 значения логической единицы, то есть только в том случае, когда в блоке стратегии поиска 5 будет обнаружено соответствие типа поступившего БДИ типу, ожидаемому согласно сценария поиска. В противном случае в регистре 6.4 сохраняется предыдущее значение кода типа БДИ. Таким образом, на K-разрядном выходе "Код события" 21 блока формирования адреса маски переходов 6 всегда установлен код, соответствующий адресу, по которому в оперативном запоминающем устройстве 5.2 хранится маска переходов, определяющая тип (типы) ожидаемых согласно сценария поиска БДИ. С K-разрядного выхода "Код события" 21 блока формирования адреса маски переходов 6 код типа БДИ поступает на соответствующие входы регистра стратегии поиска 5 и блока индикации 7.

В случае соответствия типа поступившего БДИ ожидаемому типу значение логической единицы с сигнального выхода 17 регистра стратегии поиска 5 поступает на соответствующий вход формирователя временных интервалов 4. С сигнального выхода 17 формирователя временных интервалов 4 значение логической единицы поступает на вход разрешения записи V счетчика 4.7 и первый информационный вход J JK-триггера 4.2. При этом осуществляется запись кода времени ожидания очередного БДИ, установленного на M-разрядном входе "Код времени ожидания" 19 устройства, в счетчик 4.7 и формирование на выходе JK-триггера 4.2 значения логической единицы (так как на его втором информационном входе К установлено значение логического нуля). Значение логической единицы с выхода JK-триггера 4.2, поступая на второй вход первого двухвходового элемента И 4.3, разрешает поступление тактовых импульсов с второго тактового входа 9 формирователя временных интервалов на счетный вход С счетчика 4.7. Таким образом, в формирователе временных интервалов инициируется отсчет времени ожидания очередного БДИ.

Окончание анализа поступившего БДИ и переход к ожиданию очередного БДИ осуществляется путем установки значения логической единицы на разрешающем входе 29 устройства, что приводит к безусловной установке значения логического нуля на сигнальном выходе 17 регистра стратегии поиска 5. Для корректной работы устройства установка значения логической единицы на разрешающем входе 29 должна осуществляться с временной задержкой ΔT относительно момента времени T3, определяемой временем задержки параллельного срабатывания трехвходовых элементов ИЛИ-НЕ 5.31-5.3N, N-входового элемента ИЛИ 5.4 и максимального из времени задержки записи в регистр 6.4, времени задержки срабатывания JK-триггера 4.2 и времени задержки записи в счетчик 4.7:

где ΔТ5.3 - время задержки параллельного срабатывания трехвходовых элементов ИЛИ-НЕ 5.31-5.3N;

ΔT5.4 - время задержки срабатывания N-входового элемента ИЛИ 5.4;

ΔT6.4 - время задержки записи в регистр 6.4;

ΔT4.2 - время задержки срабатывания JK-триггера 4.2;

ΔT4.7 - время задержки записи в счетчик 4.7.

Одновременно с установкой значения логической единицы на разрешающем входе 29 устройства осуществляется установка значения логической единицы на входе "Выбор кристалла" 25.

Если до истечения времени ожидания поступит очередной БДИ, тип которого соответствует типу, ожидаемому согласно сценария поиска, то значение логической единицы на сигнальном выходе 17 регистра стратегии поиска приведет к повторной инициализации счетчика 4.7 формирователя временных интервалов 4 (повторной записи в счетчик кода времени ожидания очередного БДИ). При этом логическое значение на выходе JK-триггера 4.2 не изменится (так как на его втором информационном входе К установлено значение логического нуля), и тактовые импульсы будут продолжать поступать на счетный вход С счетчика 4.7. Таким образом отсчет времени ожидания очередного БДИ начнется с начала.

Если очередной БДИ, соответствующий сценарию поиска, не поступит до истечения времени ожидания, то произойдет переполнение счетчика 4.7. При этом на выходе Р переполнения счетчика 4.7 установится значение логической единицы, которое поступит на второй вход второго двухвходового элемента И 4.5 и через первый двухвходовый элемент ИЛИ 4.1 - на второй информационный вход К JK-триггера 4.2. Значения логической единицы на выходе переполнения Р счетчика 4.7 и на сигнальном входе 17 формирователя временных интервалов могут устанавливаться в произвольные моменты времени. В связи с этим на информационных входах JK-триггера 4.2 возможно появление следующих комбинаций логических значений:

на первом информационном входе J JK-триггера 4.2 установлено значение логического нуля, а на его втором информационном входе К установлено значение логической единицы;

на первом и втором информационных входах JK-триггера 4.2 установлены значения логической единицы.

В первом случае на выходе JK-триггера 4.2 установится значение логического нуля, которое поступит на второй вход первого двухвходового элемента И 4.3 и на вход инвертора 4.4. Значение логического нуля на втором входе первого двухвходового элемента И 4.3 приведет к прекращению поступления тактовых импульсов с второго тактового входа 9 формирователя временных интервалов 4 на счетный вход С счетчика 4.7. Значение логического нуля на входе инвертора 4.4 приведет к установке значения логической единицы на первом входе второго двухвходового элемента И 4.5, что при наличии значения логической единицы на его втором входе приведет к установке значения логической единицы на втором входе второго двухвходового элемента ИЛИ 4.6 и на выходе "Сброс" 20 формирователя временных интервалов 4. Значение логической единицы на втором входе второго двухвходового элемента ИЛИ 4.6 приведет к сбросу счетчика 4.7, а значение логической единицы на выходе "Сброс" 20 приведет к сбросу регистра 6.4 блока формирования адреса маски переходов 6. Сброс счетчика приведет к установке на его выходе переполнения Р значения логического нуля, который поступит на второй информационный вход К JK-триггера 4.2 и на второй вход второго двухвходового элемента И 4.5. При этом на выходе "Сброс" 20 формирователя временных интервалов 4 установится значение логического нуля. Сброс регистра 6.4 блока формирования адреса маски переходов 6 приведет к установке на адресных входах A1-AK оперативного запоминающего устройства 5.2 регистра стратегии поиска 5 нулевого адреса. Таким образом, поиск очередных БДИ, определяемых текущей маской переходов, прерывается и устройство переходит к ожиданию БДИ, типы которых определены маской начала сценария поиска (начальных БДИ).

Во втором случае логическое значение на выходе JK-триггера 4.2 не изменится. При этом тактовые импульсы будут продолжать поступать на счетный вход С счетчика 4.7, а на выходе второго двухвходового элемента И 4.5 останется значение логического нуля (не смотря на значение логической единицы на его втором входе). Значение логической единицы на сигнальном входе 17 формирователя временных интервалов 4 приведет к записи кода ожидания очередного БДИ, установленного на M-разрядном входе "Код времени ожидания" 19 в счетчик 4.7. При этом на выходе переполнения Р счетчика 4.7 установится значение логического нуля, который поступит на второй информационный вход К JK-триггера 4.2 и на второй вход второго двухвходового элемента И 4.5. Таким образом, сброс регистра 6.4 блока формирования адреса маски переходов 6 не произойдет и на адресных входах A1-AK оперативного запоминающего устройства 5.2 регистра стратегии поиска 5 будет установлен адрес, соответствующий адресу очередной маски переходов. В связи с этим работа устройства по поиску очередных (согласно сценария поиска) БДИ продолжится.

При поступлении БДИ, тип которого соответствует одному из типов БДИ, указанных в маски окончания сценария поиска (конечных БДИ), на выходе "Результат поиска" 28 устройства формируется значение логического нуля. Формирование значения логического нуля на выходе "Результат поиска" 28 устройства осуществляется следующим образом. С разрядов K-разрядного входа "Код события" 21 блока индикации 7 код типа БДИ поступает на соответствующие входы Y1-YK дешифратора 7.1. При этом на инверсном выходе дешифратора 7.1, номер которого соответствует коду типа БДИ, установится значение логического нуля, а на всех остальных выходах дешифратора - значение логической единицы. Логические значения с выходов  дешифратора 7.1 поступают на первые входы соответствующих двухвходовых элементов ИЛИ 7.21-7.2N, где происходит их сравнение с значениями маски окончания сценария поиска, установленными на N-разрядном входе "Правило завершения поиска" 27. При совпадении логических значений на входах двухвходового элемента ИЛИ, номер которого соответствует коду типа БДИ, на его выходе установится значение логического нуля, которое через N-входовый элемент И 7.3 поступит на выход "Результат поиска" 28 устройства, что соответствует обнаружению в входящем потоке БДИ последовательности БДИ, соответствующей сценарию поиска.

дешифратора 7.1 поступают на первые входы соответствующих двухвходовых элементов ИЛИ 7.21-7.2N, где происходит их сравнение с значениями маски окончания сценария поиска, установленными на N-разрядном входе "Правило завершения поиска" 27. При совпадении логических значений на входах двухвходового элемента ИЛИ, номер которого соответствует коду типа БДИ, на его выходе установится значение логического нуля, которое через N-входовый элемент И 7.3 поступит на выход "Результат поиска" 28 устройства, что соответствует обнаружению в входящем потоке БДИ последовательности БДИ, соответствующей сценарию поиска.

Таким образом, предлагаемое устройство поиска информации обеспечивает выполнение следующих функций:

параллельную идентификацию поступающих БДИ;

контроль порядка следования БДИ;

контроль интервалов следования БДИ;

сигнализацию об обнаружении заданной сценарием поиска последовательности БДИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

| Устройство поиска информации | 2017 |

|

RU2656736C1 |

| Устройство поиска информации | 2019 |

|

RU2724788C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2022 |

|

RU2792840C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2012 |

|

RU2480823C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство управления организацией доступа к внешней памяти | 1986 |

|

SU1357965A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2133500C1 |

Изобретение относится к области электросвязи и может быть применено для поиска и оперативной идентификации информации в сетях передачи данных с коммутацией пакетов. Целью изобретения является разработка устройства поиска информации, обеспечивающего расширение области его применения и повышение быстродействия за счет идентификации пакетов путем параллельного анализа значений признаков идентификации и контроля последовательности обмена ими на предмет соответствия любым, априорно заданным правилам. Устройство состоит из N, где N≥2, блоков селекции, регистра стратегии поиска, формирователя временных интервалов, блока индикации, делителя частоты, N блоков хранения маски, блока формирования адреса маски переходов. Устройство обеспечивает возможность идентификации пакетов путем параллельного анализа признаков идентификации. Независимость процесса функционирования устройства от эталонных значений признаков идентификации и содержания правил, определяющих порядок обмена пакетами, обеспечивает более высокую скорость анализа и позволяет расширить область применения устройства. 5 з.п. ф-лы, 9 ил.

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1996 |

|

RU2115952C1 |

| Устройство для поиска информации | 1989 |

|

SU1711185A1 |

| Устройство для поиска информации | 1989 |

|

SU1621049A1 |

| JP 2002325091, 08.11.2002 | |||

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

Авторы

Даты

2007-12-20—Публикация

2006-06-05—Подача