1

Изобретение относится к электроизмерительной технике и может быть использовано в измерителях разности частот.

Известно устройство для цифрового измерения разности частот электрических колеба«ий, содержащее реверсивный счетчик, входы которого связаны с входными клеммами через логические схемы «ИЛИ, временные селекторы, формирователи импульсов и триггеры, а выход - с цифровым индикатором, источник импульсов эталонной частоты, формирователь временного измерительного интервала, триггеры, элементы задержки.

Предложенное устройство отличается от известного тем, что снабжено компаратором длительности иачки, образованным счетчиком импульсов, тремя дешифраторами состояния счетчика, элементом задержки и схемой «ИЕ. Первый вход схемы «НЕ соединен через элемент задержки с выходом второго дешифратора, второй вход - с выходом третьего дешифратора, входом соединенного с входами первого и второго дешифраторов и выходом счетчика, счетный вход которого связан с выходом третьего селектора, вход сброса, через первый элемент задержки - с выходом первой схемы «ИЛИ, входы которой через первый и второй селекторы и второй и третий формирователи импульсов связаны с первым и вторым выходами второго

входного триггера, выход-с вторым входом управляющего триггера. Первый вход управляюпдего триггера через первый формирователь подключен к выходу первого входного триггера, выход-к входу третьего селектора, вторым входом соединенного с источником эталонной частоты и через четвертый селектор - с первым выходом второго входного триггера, а выходом - с первыми входами пятого и шестого селекторов, вторые входы которых подключены к выходам формирователя временного ит1тервала, выходы - к первым входам второй и третьей схем «ИЛИ, выходы которых соединены с входами реверcnriiioro счетчика, а вторые входы раздель iO - с входами пятой схемы «ИЛИ и выхо;ui:4i седьмого и восьмого селекторов, импульсными входами связанных с выходо:. четвертого селектора, потенциальными - с вь:хода.п1 первого п второго триггеров ввода поправки, нулевые входы которых соединены через второй элемент задержки с выходом иягой схемы «ИЛИ. Единичный вход второго триггера ввода поправки подключен ко второму входу четвертой схел.ы «ИЛИ и первого ;;ешифрато11а, единичный вход первого триггера ввода поправки - к первому входу четвертой схемы «Г1Л1--1 и через третий элемент задержки,- к выходу схемы «ИЕ, причем выход четвертой схемы

«ИЛИ связан со счетным входом трлпт.ра, выходы которого соедписиы с лотеншкьльньь ми входами первого и второго селекто юн. Такое вынолненне устройства позволяет повыснть его быстродействне.

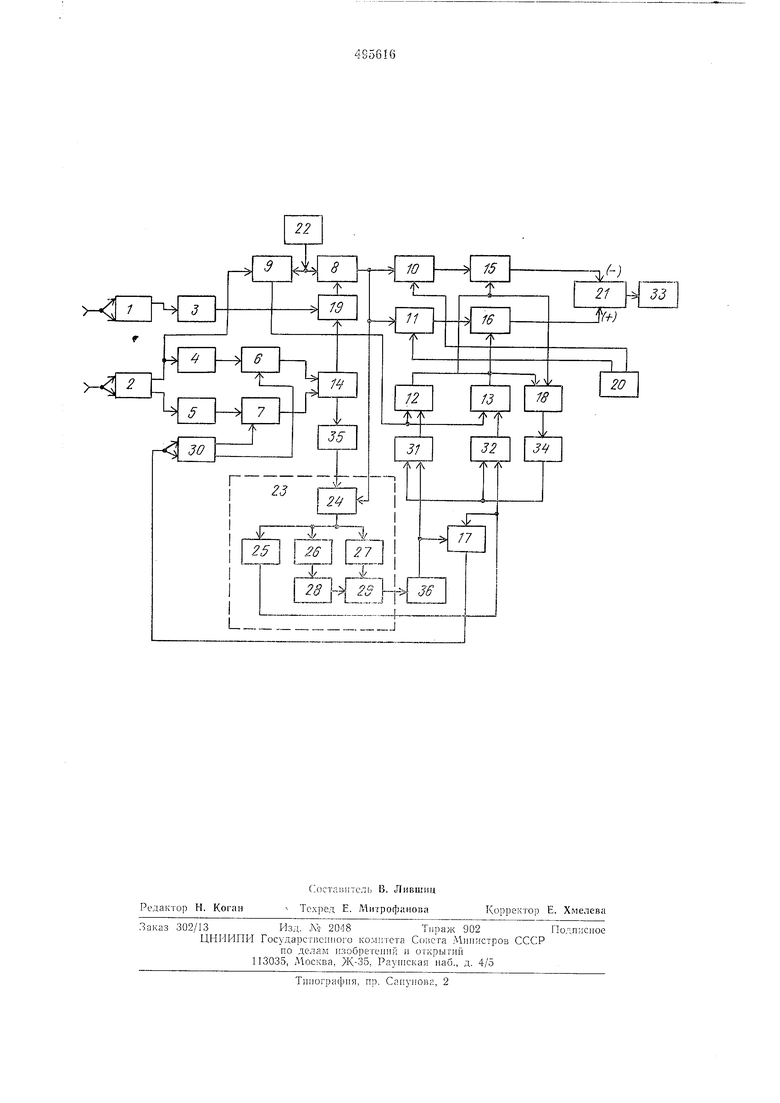

Блок-схема устройства приведена ;i;i ч-ертеже.

Устройство состоит нз входных трнгге;)ог) н 2; формирователей 3--5 копотких импульсов; временных селекто 1ов б--13; схе «ИЛ1-Ь 14-18; управляющего трште;); формирователя 20 временного измерите; го интервала; ревереи13 ;ого ечетчика 21 точника 22 импульеов эталонной частоты; комнаратора 23 длительности нгипчи; ;;б;1азованного счетчиком имиульсов 24, дешифраторами 25, 26, 27 состояния счетчика, элементом задержки 28 и схемой «НЕ 29; триггера 30; триггеров 31. 32 ввода понравки и цифрового индикатора 33, элемситов задержки 34, 35, 36.

Устройство работает следующим образом.

Если за временной нзмерительнв1Й интервал Ги фазовый сдвиг между носледовательиостями иа ввьходах триггеров 1, 2 изменяется монотонно и в )1ределах от О до 360°, то реализуется нервый вариант заботы.

На счстные входы триггеров 1, 2 поступают последовательности имнульеов сравн);ваемых частот. Частота повторения выход.пых импульсов триггеров 1 н 2 в два раза ниже частоты входных имиульсов. Импульсы на выходах формирователей 4. 5 едвннуты д.рут отноентельно друга на иолов1П у нер);ода их частоты следования. Триггер 30 находится в состоянии, при котором селектор 6 и закрыт еелектор 7. На раздельные входы триггера 19 иоетупают двС последовательности и лнульсов, близкие но частоте с временным сдвигом т между ними. Р1мпульсы с выхода формирователя 3 переводят триггер 19 в состояние, нрн котором селектор 8 открыт, а импульсы с выхода схемы «ИЛИ 14 переводят триггер 19 в состояни1 при котором селектор 8 закрыт. Начки импульсов эталонной частоты, еледуюгцие с периодом TI с выхода селектора 8, поступают «а входы селекторов 10, II, которые управляются формирователем 20 времеипого и измерительного интервала. Формирователь 20 вырабатывает сигналы начала и коииа измерения, интервал между которымн равен Т,,.

Под действием первого еигиала открываетея селектор 10 и одна начка имнульеов с выхода селектора 8 через еелектор 10 н схему «ИЛИ 15 поступает па вычитающий вход реверсивного счетчика 21. Ио истечении иитервала Г,, формирователь 20 вырабатывгет второй сигнал, под действием которого иа длительность одной иачки открывается сеЛбктор 11 и вторая иачка имнульеов ге)ез него и схему 16 постунает на суммнрукпц1и1 вход счетчика 21. Оставшийся в счетчике 21 код проиорпионален изменению сдвига фаз между напряжениями на входах трнггеров

4

выполияетея равен/„fsT- i- lO,

где п - целое положительное число, то число импульсов, записанных на счетчике в конце нзмеритеомьного интервала, определяется выражением

-A/.10S

где А/.х-- измеряемая разноеть частот.

Если за временной измерительный ннтервал 7„ фазовый сдвиг между последовательностями импульсов на выходах трнггеров из.меняется более, чем на 360°, то реализуетея

второй вариант работы.

Иачка эталонных импульсов с выхода селектора 8 поступает на счетный вход счетчика 24. Ири достижении количеством импульсов в пачке числа, соответствующего длительности, меньшей j(,T, срабатывает дешнфратор 26. Выходной имнульс дещифратора 2G задерживается элемеитом 28 и проходит через открытую схему «НЕ 29 и элемент задержки 36 на вход схемы «ИЛИ 17 и едиличный вход триггера 31. Задержка элемента 36 превышает время Vz Тгм (где 72.м - лакс :мальная длительность Т, а /вТ}-,Т.2 /6J i). С выхода схемы «ИЛИ 17 сигнал ноступает на триггер 30 и переводит его во

второе устойчивое состояние, нри котором селекторы 6, 7 изменяют свое состояние. Г1ри этом на выход схемы «ИЛИ 14 проходит последоватедьность импульсов, едвинутая на /2 , в результате чего длительность пачки

превышает /zTi. Иекусствснное увеличение длительноетн пачки требует введения понравки в счетчик 21, для чего сигнал, поступивший иа единичный вход триггера 31, иереводит его в единичное состояние, при котором открывается селектор 12 и через него на схему «ИЛИ 15 поетунают имнульсы с выхода селектора 9. Селектор 9 управляется с выхода триггера 2 и остается поэтому открытым в течеиие половины периода TZ. За

это время через него проходят импульеы эталонной чаетоты в количестве, соответствующем коду фазового сдвнга на 180°. Эти имнульсы с выхода схемы «ИЛИ 15 поступают на вычитаюн,ий вход ревереивного ечетчика

2.

Ири доетижеиии длительиостью пачки величины, меньшей leTi, но большей Ve Tl, сразу же носле срабатывания дещнфратора 26 ерабатывает дешифратор 27, который вырабатывает импульс, занирающий схему «ИЕ 29, вследствие чего сигнал на его выходе отсутствует.

При достнжении длите,ты1оетью пачки величины срабатывает дешифратор 25,

сигнал с выхода которого ностунает на вто))ой Вход схемы «ИЛИ 17 и вызывает смеи еиие иа 180° запирающей селектор 8 иоеледовательностн. В резл льтате этого длительность иачки сокращается до величины РТ,

а на суммируюнднй вход счетчнка 21 поступает корректирующая пачка импульсов длительностью 0,5 Тг от источника эталонной частоты 22 через элемеиты 9, 13, 16.

Первый импульс пачки, пройдя схему «ИЛИ 18, задерживается элементом ,34 на длительность, превышающую длительность корректирующей пачки, и, поступая на нулевые входы триггеров 31, 32, фиксирует их нулевое состояние, при котором селекторы 12, 13 закрыты.

В течение всего интервала Гц фазовый сдвиг между лоследовательностями на управляющем триггере 19 поддерживается в интервале между /eTi и Ve i- Величина разностной частоты индицируется цифровым индикатором 33.

Формула изобретения

Устройство для цифрового измерения разности частот электрических колебаний, содержащее реверсивный счетчик, входы которого связаны с входными клеммами через логические схемы «ИЛИ, временные селекторы, формирователи импульсов и триггеры, а выход-с цифровым индикатором, источник импульсов эталонной частоты, формирователь временного измерительного интервала, триггеры, элементы задержки, отличающееся тем, что, с целью повышения быстродействия, оно снабжено компаратором длительности пачки, образованным счетчиком импульсов, тремя дешифраторами состояния счетчика, элементом задержки и схемой «НЕ, первый вход которой соединен через элемент задержки с выходом второго дешифратора, второй вход-с выходом третьего дешифратора, входом соединенного с входами первого и второго дешифраторов и выходом счетчика, счетный вход которого

связан с выходом третьего селектора, вход сброса через первый элемент задержки - с выходом первой схемы «ИЛИ, -входы которой через первый и второй селекторы и второй и третий формирователи импульсов связаны с первым и вторым выходами второго входного триггера, выход-с вторым входом управляющего триггера, первый вход которого через первый формирователь подключей к выходу первого входного триггера, выход-ко входу третьего селектора, вторым входом соединенного с источником эталонной частоты, и через четвертый селектор - .с первым выходом второго входного триггера, а выходом - с первым входами пятого и шестого селекторов, вторые входы которых подключены к выходам формирователя временного интервала, выходы - к первым входам второй и третьей схем «ИЛИ, выходы

которых соединены с входами реверсивного счетчика, а вторые входы раздельно - е входами пятой схемы «ИЛР1 и выходами седьмого и восьмого селекторов, импульсными входами связанных с выходом четвертого селектора, потенциальными - с выходами первого и второго триггеров ввода поправки, нулевые входы которых Соединены через второй элемент задержки с выходами пятой схемы «ИЛИ, единичный вход второго триггера ввода поправки подключен ко второму входу четвертой схемы «ИЛИ и выходу первого дешифратора, единичный вход первого триггера ввода поправки - к первому входу четвертой схемы «ИЛИ и через третий элемент задержки - к выходу схемы «НЕ, причем выход четвертой схемы «ИЛИ связаи со счетным входом триггера, выходы которого соединены с потеициальными входами первого и второго селекторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового измерения разности частот электрических колебаний | 1977 |

|

SU739430A1 |

| Селектор импульсной последовательности заданной длительности, содержащей импульсы заданной длительности | 1989 |

|

SU1670782A1 |

| Устройство для контроля фазовых искажений сигнала воспроизведения | 1987 |

|

SU1413673A1 |

| Селектор серий импульсов по дли-ТЕльНОСТи | 1979 |

|

SU813768A1 |

| Селектор последовательности заданной длительности, содержащей импульсы заданной длительности | 1988 |

|

SU1555842A1 |

| Селектор импульсов по длительности | 1989 |

|

SU1690185A1 |

| Селектор импульсов | 1979 |

|

SU815890A1 |

| Селектор импульсов по длительности | 1988 |

|

SU1499466A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

Авторы

Даты

1975-12-15—Публикация

1973-08-06—Подача