Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных ЭВМ для приоритетного обслуживания запросов на разделяемые ресурсы: магистраль обмена данными, общие .модули памяти процессоры.

Цель изобретения - повышение быстродействия устройства дпя, выбора запросов по приоритетам.

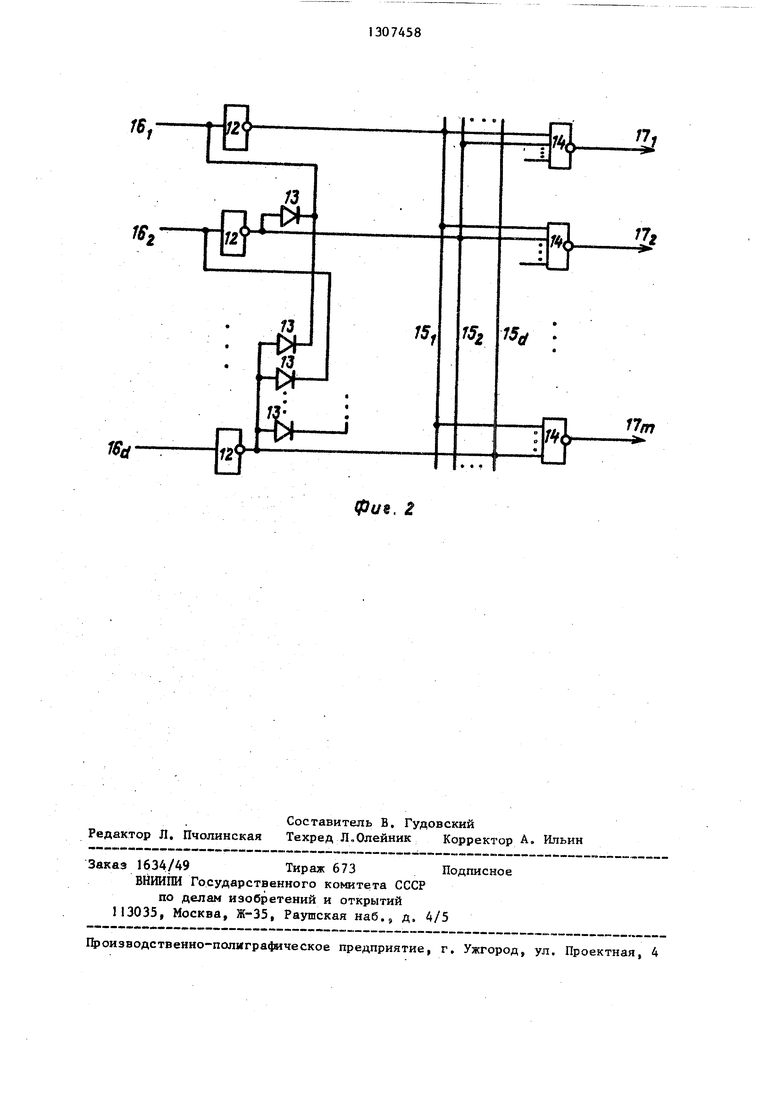

На фиг, 1 изображена функциональная схема устройства; на фиг. 2 - схема шифратора.

Устройство содержит регистры 1 приоритетов, каналы 2, узел 3 селекции каналов, шифратор 4, запросные входы 5 и запросные выходы 6 устройства. Канал 2 содержит дешифратор 7 группу из m элементов ИСКЛОЧАЩЕЕ ИЛИ 8 и пороговый элемент, выполненный в виде диода 9,

Узел селекции каналов содержит группу из (п-1) элементов НЕ 10 и (п-1) групп по (J-1) пороговый элемент, выполненных в виде диодов 11,

Шифратор 4 содержит группу из () элементов НЕ 12, () групп пороговых элементов, выполненных в виде диодов 13 по (К-1) диодов в К-й группе, группу из m элементов ИЛИ-НЕ 14 и шины 15,,.,. ,15ju.

На .фиг, 1 обозначены логические шины 16-. ,, 16(i (.) , разрядные шины 17 ,,,. 1 7fnf выходные шины 18.,

, п

Устройство работает следующим образом,

В регистрах 1 находятся коды N ; приоритетов каналов, максимальному коду соответствует высший приоритет. Допускаются совпадающие коды. Каналы, выставившие запросы на обслуживание, устанавливают на соответствующих входах 5 устройства 1, Двоичные разряды кода N поступа ют из регистра 1 на входы дешифратора 7 и на первые входы элементов ИСКЛЮЧАЩЕЕ ИЛИ 8 группы,

На вторые входы этих элементов поступает код с разрядных шин 17. , ,,,,17, Единичный сигнал с входа 5 разрешает дешифрацию кода N дешифратором 7, На к-м выходе дешифратора 7, соответствующем входному коду N (), при этом имеется О, а на остальных выходах - 1, При нулевом сигнале на входе 5 (отсутствие

074582

запроса) на всех выходах дешифратора 7 имеют,ся I,

На шине 16, к которой подключены к-е выходы всех дешифраторов 7,

5 реализуется операция И по принципу монтажной логики. На шине 16 1 присутствует только в том случае, когда на к-х выходах всех дешифраторов 7 присутствуют 1, Если в ка налах устройства, выставивших запросы, коды NI приоритетов отличаются, то О появляются на нескольких шинах 16,

Шифратор 4 выделяет из всех ло гических шин только ту шину 16, позиционный номер которой К,-„ 2 - мокс минимальной среди номеров шин, имеющих О, В шифраторе 4 из позиционного номера Кд,,.„ получает ся т-разрядный инверсный двоичный код который выставляется на разрядные шины 17,..,,17,

Входы шифратора 4 подключены к

, логическим шинам 16/) ,,, ,, , где . В общем случае на этих шинах находится комбинация нулевых и единичных сигналов, Нулевой сигнал с шин 16 после инвертирования элементами НЕ 12 в виде 1 стремит ся выработаться на пшнах 15,. Но единичный сигнал выработается только на одной шине 15, номер которой wwH наименьший, так как нулевой сигнал шины 16 с номером К д,щ, от35 крывает диода 13 с номерами Кцдщ, тех диодных групп, номера которых больше Кщ,, исключая возможность выработки логических единиц на этих шинах 15,

С помощью группы элементов ИЛИ- НЕ 14 происходит преобразование позиционного номера К,ии шины 15 в двоичный т-разрядный инверсный код N.

45

WflKC

В группах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8 всех логических узлов 2 происходит сравнение кодов приоритетов N-, поступающих с регистров 1 соот50 ветствующих каналов, с кодом , поступающим с разрядных шин 17,.., ,,,, 7п,. В каналах, выставивших запросы и имеюдах в регистрах 1 максимальный код N., на выходах

.j группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8 согласно принципу монтажной логики И образуется единичный сигнал, поступающий на выходные шины 18 этих каналов, В каналах, не выставивших

запросы, на выходной шине 18 постоянно присутствует О, 1 на шине 18 не может установиться, так как этому препятствует открытый диод 9, катод которого связан с нулевым запросным входом 5.

Если среди каналов, выставивших запросы, будет несколько каналов с кодом через узел 3 селекции каналов на выход 6 устройства проходит единичный сигнал выходной шины 18 только с наименьшим номером J. Это осуществляется благодаря тому, что единичный сигнал с шины V, с наименьшим номером j после инвертирования элементом НЕ 10 открывает диоды 11 всех диодных групп, номера которых больше j, запрещая образование 1 на всех остальных выходах 6 устройства.

Формула изобретения

Устройство для выбора запросов по приоритетам, содержащее п (п - число запросов) каналов, каждый из которых содержит дешифратор, причем i-й (,...,т, где ш - разрядность кода приоритета) вход кода приоритета j-ой группы устройства соединен с i-M входом j-ro дешифратора, отличающееся тем, что, с целью повышения быстродействия, в него

fO

15

20

25

30

ментов (,,,,,п-1), шифратор, содержащий группу из () элементов НЕ, () групп из (К-1) пороговых элементов ( ,.,. , ) и группу из m элементов ИЛИ-НЕ, а в каждый канал введен пороговый элемент и группа из m элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем i-й вход кода приоритета j-й группы устройства соединен с первым входом i-ro элемента ИСКЛЮЧАКЬ ЩЕЕ ИЛИ группы j-ro канала, j-й запросный вход устройства соединен с управляющим входом дешифратора и входом порогового элемента j-ro канала, j-й запросный выход устройства соединен с выходом порогового элемента j-ro канала, выходами m элементов ИСКЛЮЧАЮЩЕЕ ИЛИ j-ro канапа и выходами пороговых элементов (j-1) группы узлы селекции каналов, g-и , запросный выход устройства соединен с входом g-ro элемента НЕ группы узла селекции каналов, выход g-ro элемента НЕ группы узла селекции каналов соединен с входами пороговых элементов R-x (g,..,n-1) групп узла селекции каналов, К-й выход деши4ч атора j-ro канала соединен с входом К-го элемента НЕ группы и входами К-х пороговых элементов S-X (S7 к) групп шифратора, выход К-го элемента НЕ группы шифратора соединен с К-ми входами i-x элементов ИЛИ-НЕ группы шифратора, для

введены узел селекции каналов, содер-35 которых при представлении числа жащий группу из (п-1) элементов НЕ и в двоичном коде L-Й разряд кода (п-1) групп по (g-1) пороговых эле- содержит единицу.

5

0

5

0

ментов (,,,,,п-1), шифратор, содержащий группу из () элементов НЕ, () групп из (К-1) пороговых элементов ( ,.,. , ) и группу из m элементов ИЛИ-НЕ, а в каждый канал введен пороговый элемент и группа из m элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем i-й вход кода приоритета j-й группы устройства соединен с первым входом i-ro элемента ИСКЛЮЧАКЬ ЩЕЕ ИЛИ группы j-ro канала, j-й запросный вход устройства соединен с управляющим входом дешифратора и входом порогового элемента j-ro канала, j-й запросный выход устройства соединен с выходом порогового элемента j-ro канала, выходами m элементов ИСКЛЮЧАЮЩЕЕ ИЛИ j-ro канапа и выходами пороговых элементов (j-1) группы узлы селекции каналов, g-и , запросный выход устройства соединен с входом g-ro элемента НЕ группы узла селекции каналов, выход g-ro элемента НЕ группы узла селекции каналов соединен с входами пороговых элементов R-x (g,..,n-1) групп узла селекции каналов, К-й выход деши4ч атора j-ro канала соединен с входом К-го элемента НЕ группы и входами К-х пороговых элементов S-X (S7 к) групп шифратора, выход К-го элемента НЕ группы шифратора соединен с К-ми входами i-x элементов ИЛИ-НЕ группы шифратора, для

IS,

Составитель В. Гудовский Редактор Л. Пчолинская Техред Л Олейник Корректор А. Ильин

Заказ 1634/49Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий Н3035, Москва, Ж-35, Раушская наб., д. 4/5

Дроизводственно-полмграфическое предприятие, г, Ужгород, ул. Проектная, 4

4&

Фи9. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритета | 1988 |

|

SU1536382A1 |

| Устройство приоритета | 1988 |

|

SU1619267A1 |

| Устройство для приоритетного обслуживания | 1984 |

|

SU1226458A1 |

| Многоканальное устройство приоритета | 1989 |

|

SU1642468A1 |

| Устройство для выбора запросов по приоритетам | 1985 |

|

SU1295394A1 |

| Многоканальное устройство приоритета | 1985 |

|

SU1283765A1 |

| Устройство для обслуживания группы запросов | 1988 |

|

SU1562913A1 |

| Многоканальное устройство приоритетного обслуживания | 1984 |

|

SU1190382A1 |

| Устройство для приоритетного обслуживания запросов | 1987 |

|

SU1462310A1 |

| Устройство приоритета с шифрацией номера канала и абонента | 1984 |

|

SU1247872A1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных ЭВМ для приоритетного обслуживания запросов на разделяемые ресурсы: на- гистраль обмена данными, общие модули памяти, процессоры. Цель изобретения - повышение быстродействия. Устройство содержит регистры приоритета 1f каналы 2, узел 3 селекции каналов, шифратор 4. Каждый канал 2 содержит дешифратор 7, группу элементов Исключающее ИЛИ 8 и диод 9. В устройстве происходит одновременное сравнение всех разрядов кодов приоритетов во всех, каналах. 2 ил.

| Многоканальное устройство приоритета | 1981 |

|

SU1005055A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство переменного приоритета | 1983 |

|

SU1120332A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-30—Публикация

1985-03-06—Подача