Изобретение относится к вычислительной технике и может быть использовано в системах параллельной обработки информации для организации бесконфликтного приоритетного доступа абонентов к общим разделяемым ресурсам,,

Цель изобретения - сокращение объема оборудования.

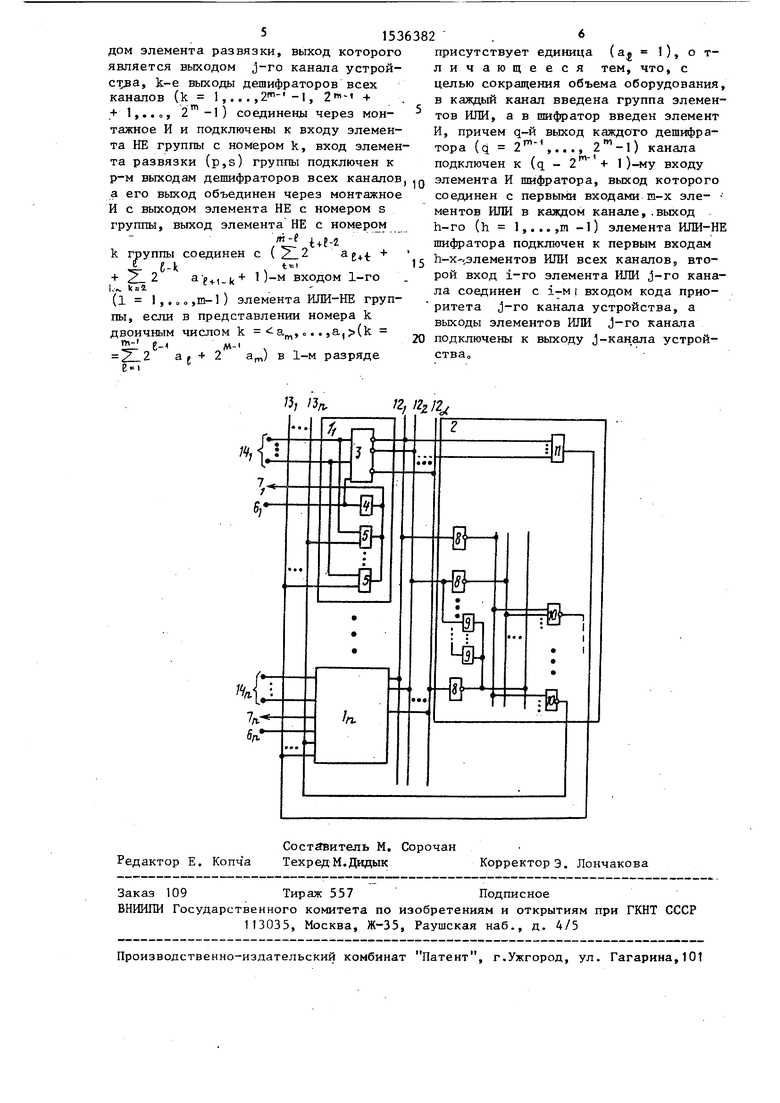

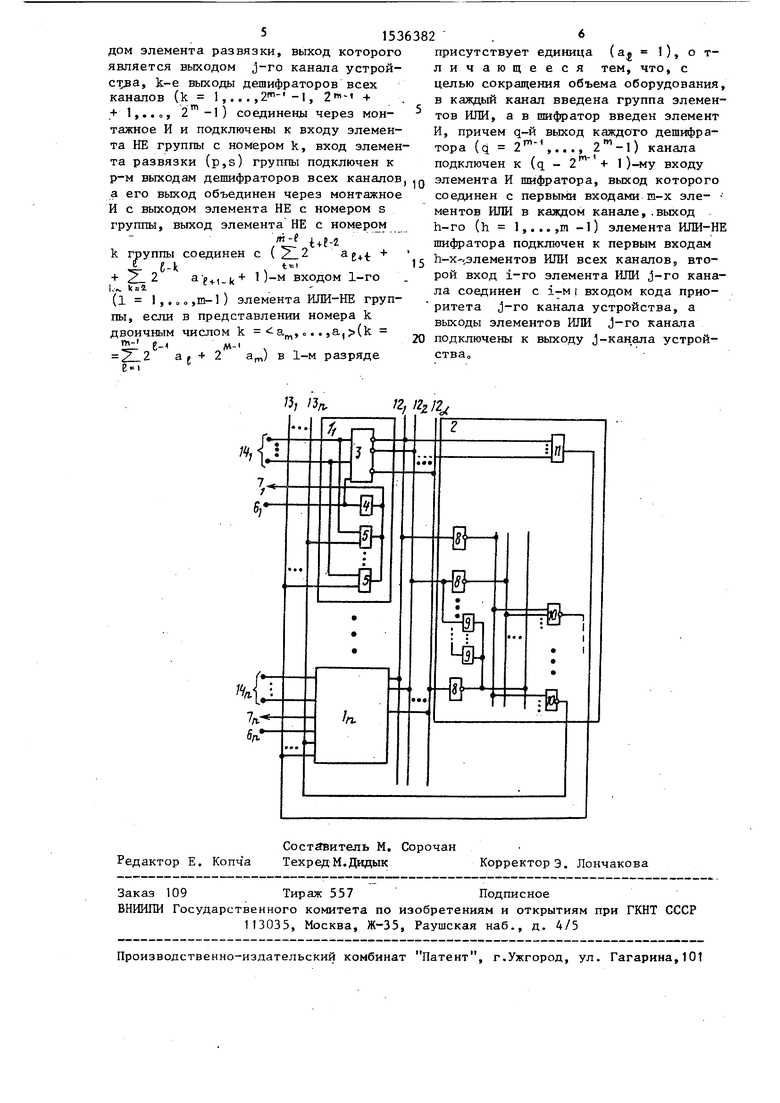

На чертеже представлена функциональная схема устройства.

Устройство содержит каналы 1 и шифратор 2. В каждом канале содержатся дешифратор 3, элемент 4 развязки, группа элементов ИЛИ 5„ Устройство содержит запросные входы 6 и выходы 7. В составе шифратора 2 содержатся элементы НЕ 8, элементы 9 развязки, элементы ИЛИ-НЕ 10 и И 11. На схеме обозначены логические шины 1-2 4, о о,

12(0/. 2™ - 1), разрядные шины 13,..„,13П и входы 14 кода приоритета

Устройство работает следующим образом

Устройство предназначено для выдачи разрешения каналу, имеющему максимальный приоритет среди приори- тетов тех каналов, которые выставили запросы.

Исходное состояние устройства характеризуется наличием на входах 14 кодов приоритетов каналов 1. Максимальному коду соответствует высший приоритете

Работа устройства начинается с появления сигналов на запросных входах 6 устройства Каналы, выставившие запросы на обслуживание, устанавливают на соответствующих входах 6 сигнаСП

00 О)

со

00

ьэ

лы логических единиц Эти сигналы разрешают дешифрацию кодов приоритета дешифраторами 3. На единственном k-м выходе дешифратора 3-, соответствующем входному коду приоритета, образуется соответственно сигнал О а на остальных - 1

Ори наличии

на входах дешифратора кода N: 10...0 лишь на выхс шифратора 3 ; будет сигнал О нулевом сигнале на запросном входе 6 канала 1 на все выходы его дешифра- 3 поступают сигнапы

выходе де- л При

и 3. Однако нет необходимости устанавливать аналогичную связь с выходом элемента НЕ 8 с номером один, так как он не влияет на установление указанного единичного сигнала на выходе второго элемента ИЛИ-НЕ 10.

В результате после шифрования на первые входы элементов ИЛИ 5 во .,Q все каналы по шинам 13,1,...,13П поступит код, инверсный максимальному коду приоритета. На вторые входы поступят коды приоритетов соответствующих каналов После срабатывания

тора j поступают сигнапы

На каждой из шин 12, к которой под-|5 элементов ИЛИ 5, если в канале присут- ключены соответствующие ее номеру выходы всех дешифраторов 3, реализуется операция И по принципу монтажной логиствовал код N: i N

макс то на выходе

элементов ИЛИ 5 канала, связанных по принципу монтажной логики И, будет присутствовать сигнал логического О11. С другой стороны на выходах группы элементов ИЛИ будут-логические 1, если выполнено неравенство Nj NMaKCH все единичные разряды кода NMaксповторены в кодах Nj. Например, NMOKC 101, а N: 111. Однако наличие нулевых сигналов на запросных входах 6 устройства во всех каналах где Nj NMaKC, обеспечит единичные сигналы на выходах 7 только в тех каналах, на входах 6 которых присутствовал сигнал 1 запроса и код Nj N,

ки.

Если хотя бы на одном из выходов дешифратора хотя бы в одном из каналов присутствует сигнал О, то это свидетельствует о равенстве старшего разряда кода приоритета единице На выходе элемента И 11 вследствие его связей со всеми старшими выходами дешифраторов 3 образуется инверсное значение сигнала по отношению к значению старшего разряда кода приоритета.

Пулевые сигналы с выходов дешифраторов 3, проходя через элементы НЕ 8, пытаются образовать на выходах элементов ИЛИ-НЕ 10 остальные инверсные разряды кодов N:, т.е. кодов, которые инициировали нулевые сигналы на выходах соответствующих дешифраторов 30 При наличии нескольких нулевых сигналов на различных выходах дешифратора 3 сигнал со старшим номером устранит (проходя через повторители) только те единичные сигналы на выходах элементов НЕ 8, которые пытаются установить на выходах элементов ИЛИ-НЕ 10 значения нулевых сигналов, не совпадающих по позициям с расположением единичных сигналов в коде N /«акс

Например, для кода Nwalcc 101 сигнал логической 1 вырабатывается на выходе элемента НЕ 8 с номером 5, который, в свою очередь, пытается образовать на выходах элементов ИЛИ- НЕ 10 сигналы 1 и О (инверсные максимальным). Необходимо исключить возможность исчезновения сигнала логической 1. Это будет достигнуто, если соединить через элементы 9 вход элемента НЕ 8 с номером 5 с выходами элементов НЕ 8 с номерами 2

63824

и 3. Однако нет необходимости устанавливать аналогичную связь с выходом элемента НЕ 8 с номером один, так как он не влияет на установление указанного единичного сигнала на выходе второго элемента ИЛИ-НЕ 10.

В результате после шифрования на первые входы элементов ИЛИ 5 во .,Q все каналы по шинам 13,1,...,13П поступит код, инверсный максимальному коду приоритета. На вторые входы поступят коды приоритетов соответствующих каналов После срабатывания

элементов ИЛИ 5, если в канале присут-

ствовал код N: i N

0

макс то на выходе

элементов ИЛИ 5 канала, связанных по принципу монтажной логики И, будет присутствовать сигнал логического О11. С другой стороны на выходах группы элементов ИЛИ будут-логические 1, если выполнено неравенство Nj NMaKCH все единичные разряды кода NMaксповторены в кодах Nj. Например, NMOKC 101, а N: 111. Однако наличие нулевых сигналов на запросных входах 6 устройства во всех каналах где Nj NMaKC, обеспечит единичные сигналы на выходах 7 только в тех каналах, на входах 6 которых присутствовал сигнал 1 запроса и код Nj N,

макс

5

0

5

0

Формула изобретения

Устройство приоритета, содержащее п каналов (п - число запросов) и шифратор, причем каждый из каналов содержит дешифратор и элемент развязки, а шифратор - группу из 2т - -2(щ- разрядность кода приоритета) элементов НЕ, группу из т-1 2т -вхо- довых элементов ИЛИ-НЕ и 2 -т-1 групп элементов развязки, каждый элемент развязки группы имеет номер (p,s), где U р 2т-1 и р Ј ( 2г - 1 ; 2 3 - J ,

г

i m-

2 п ,т-г.

-, а 1 6 s р

0J 1И-Ч

И sЈ{2- ,( ,

2,.;., ... + 2 }, причем элемент развязки (p,s) группы существует, если в представлении числа р в двоичном коде его i-й разряд (i 1,...,m) содержит нуль, а 1-й разряд двоичного представления s равен единице, причем i-й вход кода приоритета j-ro канача (,0.,,n) 5 устройства соединен с i-м входом дешифратора j-ro канала, запросный вход j-ro канала устройства соединен со стробирующим входом дешифратора и входом элемента развязки, выход которого является выходом j-ro канала устрой- , k-e выходы дешифраторов всех каналов (k 1,... ,2m- -1, 2м- + + I,.., 2m-l) соединены через мои-

целью сокращения объема оборудования, в каждый канал введена группа элементов ИЛИ, а в шифратор введен элемент И, причем q-й выход каждого дешифратора (q ,..., 2 -1) канала подключен к (q - 2m + 1)-му входу

И с выходом элемента НЕ с номером s группы, выход элемента НЕ с номером

тажное И и подключены к входу элемента НЕ группы с номером k, вход элемента развязки (p,s) группы подключен к р-м выходам дешифраторов всех каналов, д элемента И шифратора, выход которого а его выход объединен через монтажное соединен с первыми входами т-х эле-

ментов ИЛИ в каждом канале,.выход h-ro (h 1,...,m -1) элемента ИЛИ-НЕ шифратора подключен к первым входам J5 Ь-х,,элементов ИЛИ всех каналов, второй вход 1-го элемента ИЛИ j-ro канала соединен с i-м i входом кода приоритета j-го канала устройства, а выходы элементов ИЛИ j-го канала 20 подключены к выходу j-канала устройства

Д:. Ы-а k группы соединен с ( / 2 aЈ+t +

е C-kt i

+ 21 2 0-м входом 1-го ..

(1 1,.„о,т-1) элемента ИЛИ-НЕ группы, если в представлении номера k двоичным числом k am, о.. ,a,(k

- е- .м-1

t

+ 2 am) в 1-м разряде

го й- - 5

1536382.6

присутствует единица личающееся

целью сокращения объема оборудования, в каждый канал введена группа элементов ИЛИ, а в шифратор введен элемент И, причем q-й выход каждого дешифратора (q ,..., 2 -1) канала подключен к (q - 2m + 1)-му входу

элемента И шифратора, выход которого соединен с первыми входами т-х эле-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритета | 1988 |

|

SU1619267A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1532930A1 |

| Устройство для выбора запросов по приоритетам | 1985 |

|

SU1307458A1 |

| Устройство приоритета с шифрацией номера канала и абонента | 1984 |

|

SU1247872A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| Устройство переменного приоритета | 1986 |

|

SU1383353A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство приоритета | 1988 |

|

SU1619324A1 |

| Устройство для обслуживания групповых приоритетных запросов | 1990 |

|

SU1753473A1 |

| Многоканальное устройство приоритета | 1977 |

|

SU679982A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах параллельной обработки информации для организации бесконфликтного приоритетного доступа абонентов к общим разделяемым ресурсам. Цель изобретения - сокращение объема оборудования. Устройство приоритета содержит каналы по числу запросных входов устройства и шифратор, содержащий группу элементов НЕ, группу элементов ИЛИ-НЕ, элемент И, группу элементов развязки, а каждый канал содержит дешифратор, элемент развязки и группу элементов ИЛИ. Новый алгоритм работы устройства позволил существенно уменьшить число элементов развязки группы, входящих в шифратор. 1 ил.

| Устройство для приоритетного обслуживания | 1984 |

|

SU1226458A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сложения 2 @ чисел | 1985 |

|

SU1307456A1 |

Авторы

Даты

1990-01-15—Публикация

1988-04-04—Подача