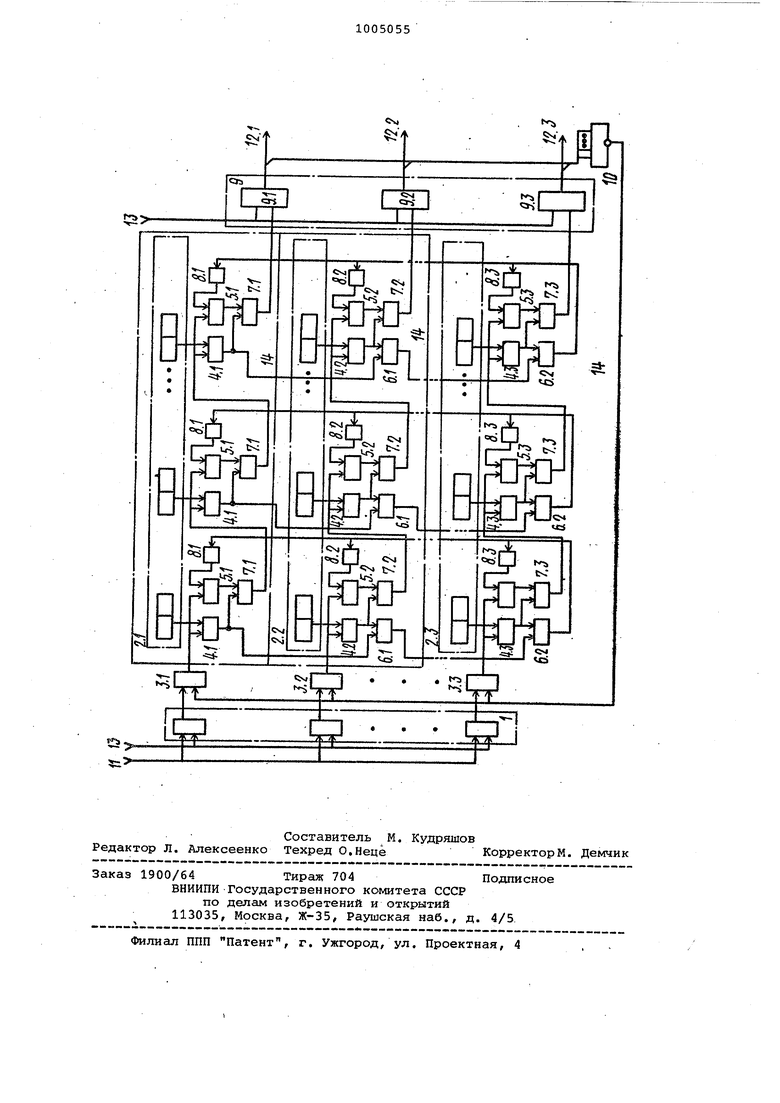

.Изобретение относится к вычислительной технике, в чacтJHOcти к устройствам переменного приоритета, и может быть использовано при .построе нии вычислительных систем и систем обмена информацией. Известно приоритетное устройство содержащее.логические схемы, регист прерывания, регистры приоритетов, регистры защиты, схемы поразрядного сравнения и поиска крайней единицы 11. Недостатком устройства является отсутствие возможности простой перен стройки при работе в составе многопроцессорных систем, в которых приоритеты блоков могут быть изменены в процессе функционирования. Это сн жает эффективность работы приоритет ных устройств и система в целом. Известно приоритетное устройство содержащее регистры, группы элементов И, счетчики, генератор импульсо триггеры, элементы ИЛИ 23. Недостатком устройства является значительный объем оборудования. Цель изобретения - сокращение объема оборудования. Поставленная цель достигается те что в многоканальное устройство при оритета, содержащее входной и выходной регистры, группу из п элементо в И (где п - число источников заявок, каналы, а в каждом канале, кроме первого, регистр приоритета, 2п элементов И и 2п элементов ИЛИ, в первом канале 2п элементов И, регистр приоритета и п элементов ИЛИ, причем запросный вход устройства соединен с информационными входами входного регистра, вход сброса устройства соединен с входами сброса входного и выходного регистров, информационные выходы выходного регистра являются информационными выходами устройства, каждый 1-й(1 1,...,п) выход входного регистра соединен с первым входом i-ro элемента И гРУппы, каждый выход регистра приоритета канала соединен с первым входом нечетного.элемента И своего канала, введены элемент ИЛИ-НЕ, а в каждом канале п э.пементов НЕ, причем выходы нечетных элементов И первого канала со- единены с .первыми входами одноименных элементов ИЛИ второго канала и с первыми входами соответствующих злементов И своего канала, выходы нечетных элементов ИЛИ каждого 1-го канала, начиная с второго до (п-1)-гр соединены с первыми входами, одноименных элементов ИЛИ (i-l)-ro кана ла , выходы нечетных элементов ИЛИ п-го канала соединены через элементы НЕ каналов с первыми входами чет ных элементов И своего и предыдущих каналов, выход каждого i-ro элемент И группы, начиная с второго, соединен с первым входом первого и вторым входом второго, элементов И tx-ro канала, выход первого элемента И группы соединен с вторыми входами первого и второго элементов И первого канала, вторые входы каждых двух соседних элементов И первого канала, начйная с третьего элемента И,соедине .с выходом предыдущего элемента ИЛИ своего канала, вторые входы элементов ИЛИ первого канала соединены с выходами соответствующих четных элементов И своего канала, второй вход первого и первые входы поспедутощих нечетных элементов И всех каналов, начиная с второго, соединены с выходами регистра приоритета своего канала, вторые входы каждых двух соседних элементов И каждого канала кроме первого, соединены с выходами предыдущих четных элементов ИЛИ своих каналов, первый вход каждого четного элемента ИЛИ каналов, начиная с второго, соединен с выходом соответствующего четного элемента И своего канала, вторые входы каждых двух соседних элементов ИЛИ каналов, начиная с второго, соединены между собой и с входом предыдущего нечетного Элемента И своего канала, выход п-го элемента ИЛИ первого канала и 2п -го элемента ИЛИ всех остгшьных каналов соединены с соответс.твугадими информационными входами выходного регистра. Структурная схема предлагаемого устройства приведена на чертеже. Устройство содержит входной -регистр 1, регистры приоритета каналов 2.1 - 2.3, элементы И группы 3.1-3.3 элементы И каналов 4.1 -4.3, 5.15.3, элементы ИЛИ каналов 6.1 - 6.2, 7.1-7.3, элементы НЕ каналов 8.1-8.3 выходной регистр 9, триггеры выходного регистра 9.1 - 8.3, элемент ИЛИ-НЁ 10, запросный вход 11 устройства, информационные выходы 12.112.3 устройства, вход сброса 13 устройства, каналы 14. При необходимости обращения к устройствупроцессоры направляют запросы, поступающие с входов 11 в соответствующий разряд регистра 1 заявок. Количество разрядов регистра 1 заявок равно числу процессоров. Сигналы .заявок подаются в случайные моменты времени. Приоритеты процессоров определяются приоритетными номерами, коды которых заносятся в регистры 2.1,2.2 и 2.3 приоритета. Самому приоритетному процессору соответствует наибольший приоритетный ( двоичный ) код. При работе системы эти коды могут изменяться при каждом цикле назначения приоритетов в системе. Группы элементов И 4.1, 4.2 и 4.3, 5.1, 5.2 и 5.3, ИЛИ .6.1 и6.2, 7.1, 7.2 и 7.3, НЕ 8.1, 8.2 и 8.3 обеспечивают выбор приоритетного кода из приславших сигналы абонентов в регистр 1 заявок. Триггеры выходного регистра 9.1, 9.2 и 9.3 фиксируют приоритетный запрос, а элемент ИЛИ-НЕ 10 осуществляет блокировку запросов. Устройство работает следующим образом. Рассмотрим работу устройства для трех абонентов. Сигналы заявок от абонентов, приоритеты которых различны и определяются приоритетными кодами, занесенными в регистры 2.1, 2.2 и 2.3 приоритеттов (пусть в регистрах приоритетов записаны следующие коды per. 2.1-100, per. 2.2 111, per. 2.3-101), подаются в регистр 1 заявок. Предположим,что запросы пришли от 1 и 3 абонентов. В результате на шинах 14.1 и 14.3 возникает единичный потенциал, а на шине 14.2 - нулевой. Далее элементами И 4.1, 4.2 и 4.3, 5.1, 5.2 и 5.3, ИЛИ 6.1 и 6.2, 7.1, 7.2 и 7.3,НЕ8.1,8.2и8.3 производится выборка приоритетного кода, причем сравниваются коды приоритетов только тех регистров приоритетов, которые соответствуют абонентам, приславшим сигналы в регистр 1 заявок, т.е. коды приоритетов 1 и 3 абонентов. Единичный сигнал с соответствующего элемента ИЛИ 7.3 устанавливает соответствующий триггер (9.3) выходного регистра 9, который, в свою очередь, является сигналом оповещения абонента (третьего), а элемент ИЛИ-НЕ 10 осуществляет блокировку запросов. При поступлении на входы 13 устройства сигнала ответа от абонента третьего) производится сброс соответствующих триггеров входного 1 и выходного 9 регистров. Применение изобретения позволяет сохранить объем оборудования. Формула изобретения Многоканальное устройство приоритета, содержащее входной и выходной регистры, группу из п элементов И (где п - число источников заявок), каналы, а в каждом канале, кроме первого, регистр приоритета, 2п элементов И и 2п элементов ИЛИ, а в первом канёше 2п элементов И, регистр приоритета и п элементов ИЛИ, причем запросный вход устройства соединен с информационными входами входного

регистра, вход сброса устройства соединен с входами сброса входного и выходного регистров, информационные выходы выходного регистра являются информационными выходами устройства, каждый (i - 1 ,. . , ,п) выход входкого регистра соединен с первым входом 1-го элемента И группы, каждый выход регистра прио1)итета канала соединен с первым входом нечетного элемента И своего канала, отличаю щ е е с я тем, что, с целью сокрашения объема оборудования, устройство содержит элемент ИЛИ-НЕ, а в каждом канёше п элементов НЕ, причем выходы нечетных элементов И первого канала соединены с первыми входами . одноименных элементов ИЛИ второго канала и с первыми входами соответствующих элементов И своего канала, выходы нечетных элементов ИЛИ каждого .1-го канала, начиная с второго до (n-l)-ro, соединены с первыми входами одноименных элементов ИЛИ (l-l)-ro канала, выходы нечетных элементов ИЛИ п-го канала -соединены череэ элементы НЕ каналов с первыми входами четных элементов И своего и предыиу1дих каналов, выход каждого 1-го элемента И группы, начиная с второго соединен с первым входом перового и вторым входом Sfopq o элементов И t-ro канала, выход первого элемен.та И группы соединен с вторыми входами первого и второго элементов И первого канала, вторые входы каждых двух сос-эдних элементов И первого канала, начиная с третьего элемента И, соединены с выходом ns}eдыдущего элемента ИЛИ своего канала, вторые входы элементов ИЛИ первого канала соединены с выходами соответствукадих четных элементов И своего канала, второй вход первого и первые входы последующих нечетных элементов И всех каналов, начиная с второго, соединены с выходами регистра приоритета своего канала, вторые входы каждых двух соседних элементов И каждого канала, кроме первого, соединены с выходами предыдущих четных элементов ИЛИ своих каналов , первый вход каждого четного . элемента ИЛИ каналов, начиная с вто,рого, соединен с выходом соответствующего четного элемента И своего канала, вторые входа каждых двух соседних элементов ИЛИ каналов, начиная с второго, соединены между собой и с выходом предыдущего нечетного элемента И. своего канала, выход п-го элемента ИЛИ первого канала и 2п-го элемента ИЛИ всех остальных каналов соединены с соответствуиицими информационными входами выходногррегистра.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 293242, кл. G Об F 9/46, 1971.

2.Авторское свидетельство СССР. 475622, кл. G 06 F 9/46, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для обслуживания запросов | 1983 |

|

SU1149258A1 |

| Устройство для приоритетного управления | 1982 |

|

SU1070552A1 |

| Устройство для обслуживания групповых приоритетных запросов | 1990 |

|

SU1753473A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство динамического приоритета | 1980 |

|

SU926659A1 |

| Устройство приоритета | 1981 |

|

SU976446A1 |

| Устройство динамического приоритета | 1980 |

|

SU868760A1 |

| Устройство приоритета | 1990 |

|

SU1746382A2 |

| Устройство приоритетного обслуживания каналов | 1989 |

|

SU1702369A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

Авторы

Даты

1983-03-15—Публикация

1981-08-10—Подача