113

Изобретение относится к вычислительной технике и может быть использовано при построении контрольной аппаратуры для проверки прохождения информации в дискретных устройствах различного типа и для проверки работоспособности ЗУ, сумматоров, счетчиков, регистров и других более сложных дискретных устройств.

Цель изобретения - повьгаение быстродействия.

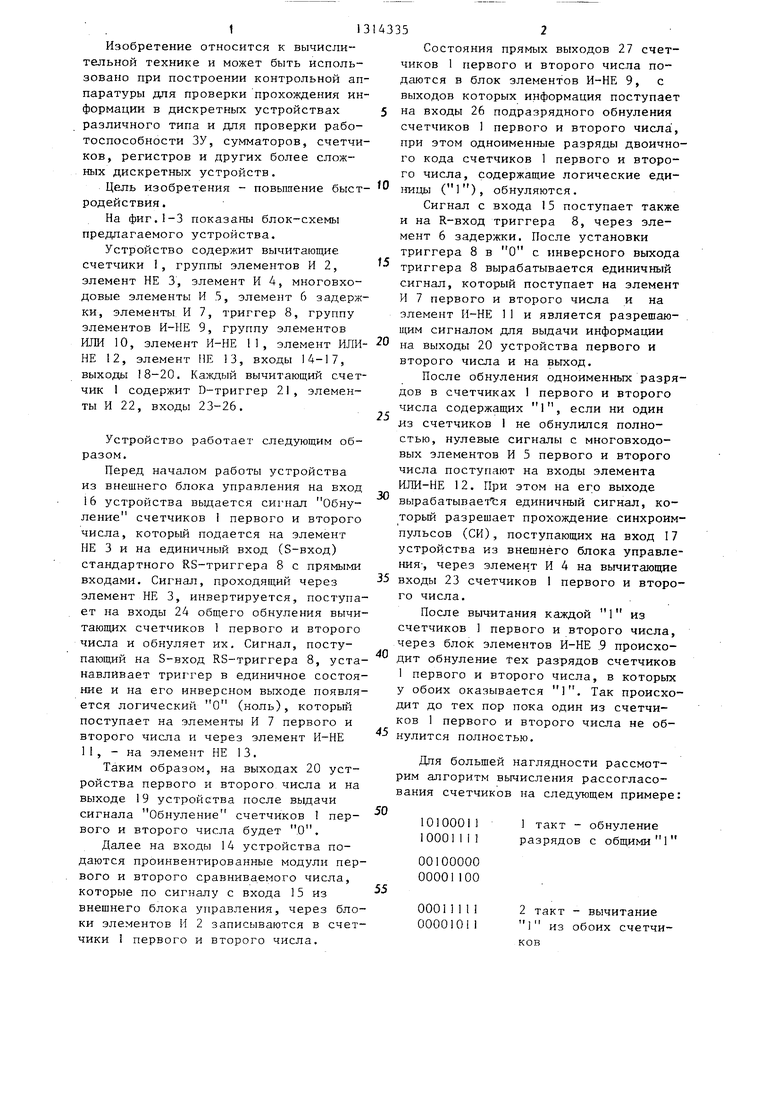

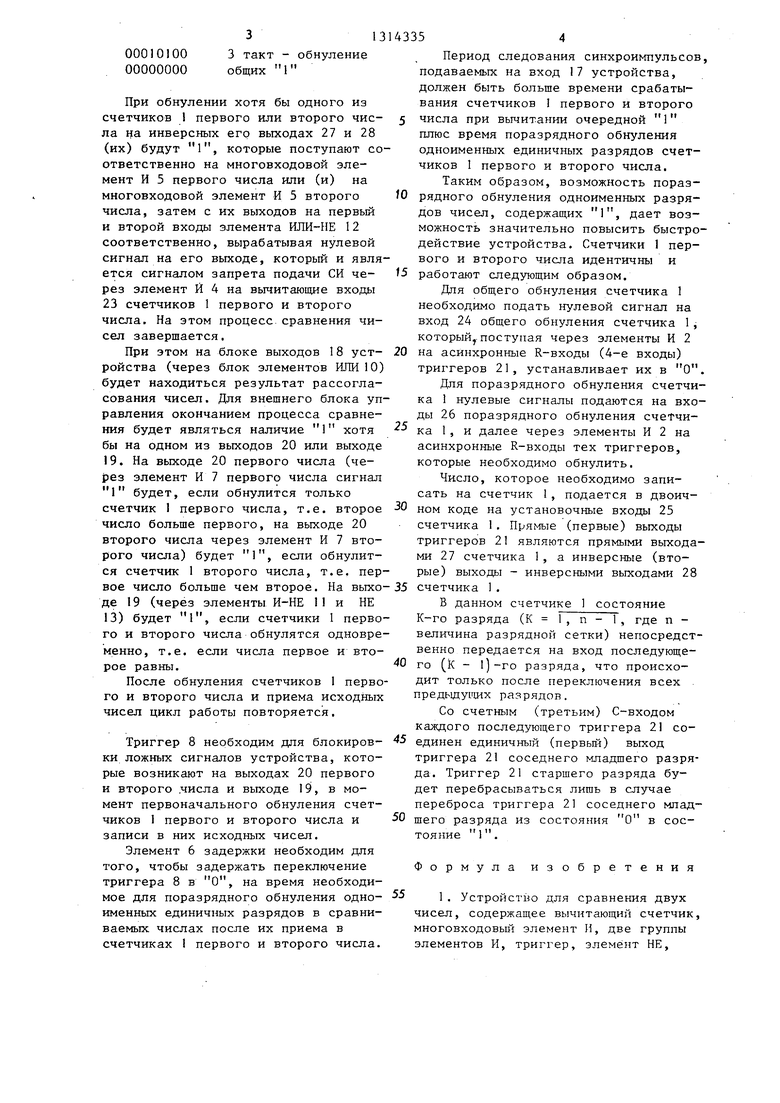

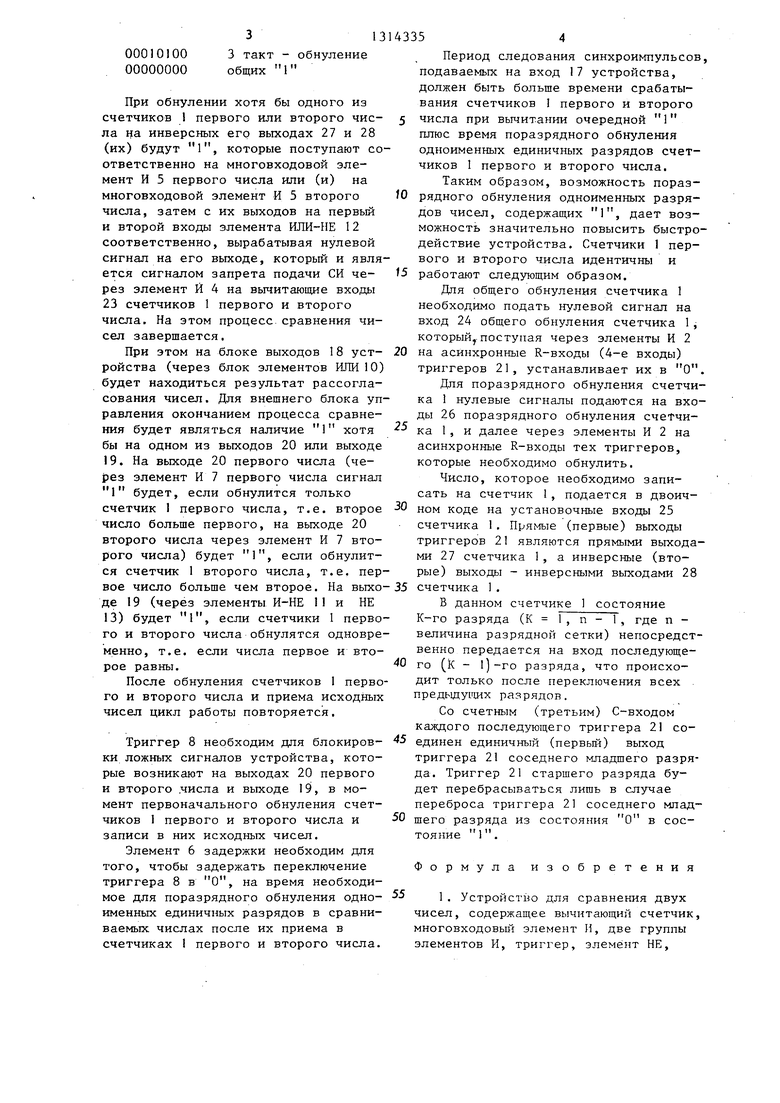

На фиг.1-3 показаны блок-схемы предлагаемого устройства.

Устройство содержит вычитающие счетчики 1, группы элементов И 2, элемент НЕ 3, элемент И 4, многовхо- довые элементы И 5, элемент 6 задержки, элементы И 7, триггер 8, группу элементов И-НЕ 9, группу элементов ИЛИ 10, элемент И-НЕ 11, элемент ИЛИ- НЕ 12, элемент НЕ 13, входы 14-17, выходы 18-20. Каждый вычитающий счетчик 1 содержит D-триггер 21, элементы И 22, входы 23-26.

Устройство работает следующим образом.

Перед началом работы устройства из внешнего блока управления на вход 16 устройства выдается сигнал Обнуление счетчиков I первого и второго числа, который подается на элемент НЕ 3 и на единичный вход (S-вход) стандартного RS-триггера 8 с прямыми входами. Сигнал, проходящий через элемент НЕ 3, инвертируется, поступает на входы 24 общего обнуления вычитающих счетчиков 1 первого и второго числа и обнуляет их. Сигнал, поступающий на S-вход RS-триггера В, устанавливает триггер в единичное состояние и на его инверсном выходе появляется логический О (ноль), который поступает на элементы И 7 первого и второго числа и через элемент И-НЕ 11, - на элемент НЕ 13.

Таким образом, на выходах 20 устройства первого и второго числа и на выходе 19 устройства после выдачи сигнала Обнуление счетчиков 1 первого и второго числа будет ,0.

Далее на входы 14 устройства подаются проинвентированные модули первого и второго сравниваемого числа, которые по сигналу с входа 15 из внешнего блока управления, через блоки элементов И 2 записываются в счетчики 1 первого и второго числа.

52

Состояния прямых выходов 27 счетчиков 1 первого и второго числа по- Дсшзтся в блок элементов И-НЕ 9, с выходов которых информация поступает на входы 26 подразрядного обнуления счетчиков 1 первого и второго числа, при этом одноименные разряды двоичного кода счетчиков 1 первого и второго числа, содержащие логические еди- ницы (1), обнуляются.

Сигнал с входа 15 поступает также и на R-вход триггера 8, через элемент 6 задержки. После установки триггера 8 в О с инверсного выхода триггера 8 вырабатывается единичный сигнал, который поступает на элемент И 7 первого и второго числа и на элемент И-НЕ 11 и является разрешающим сигналом для выдачи информации на выходы 20 устройства первого и второго числа и на выход.

После обнуления одноименных разрядов в счетчиках 1 первого и второго числа содержащих 1, если ни один из счетчиков 1 не обнулился полностью, нулевые сигналы с многовходо- вых элементов И 5 первого и второго числа поступают на входы элемента ИЖ-НЕ 12. При этом на его выходе вырабатываетТзя единичный сигнал, который разрешает прохождение синхроимпульсов (СИ), поступающих на вход 17 устройства из внешнего блока управления-, через элемент И 4 на вычитающие входы 23 счетчиков 1 первого и второго числа.

После вычитания каждой 1 из счетчиков 1 первого и второго числа, через блок элементов И-НЕ ,9 происходит обнуление тех разрядов счетчиков 1 первого и второго числа, в которых у обоих оказывается 1. Так происходит до тех пор пока один из счетчиков 1 первого и второго числа не об-

нулится полностью.

Для большей наглядности рассмотрим алгоритм вычисления рассогласования счетчиков на следующем примере:

10100011 1 такт - обнуление I 0001111 разрядов с общими

00100000 00001100

2 такт - вычитание 1 из обоих счетчиков

3131

00010100 3 такт - обнуление 00000000 общих 1

При обнулении хотя бы одного из счетчиков 1 первого или второго числа на инверсных его выходах 27 и 28 (их) будут 1, которые поступают соответственно на многовходовой элемент И 5 первого числа или (и) на многовходовой элемент И 5 второго числа, затем с их выходов на первый и второй входы элемента ИЛИ-НЕ 12 соответственно, вырабатывая нулевой сигнал на его выходе, который и является сигналом запрета подачи СИ через элемент И 4 на вычитающие входы 23 счетчиков 1 первого и второго числа. На этом процесс сравнения чисел завершается.

При этом на блоке выходов 18 устройства (через блок элементов ИЛИ 10) будет находиться результат рассогласования чисел. Для внешнего блока управления окончанием процесса сравнения будет являться наличие хотя бы на одном из выходов 20 или выходе 19. На выходе 20 первого числа (через элемент И 7 первого числа сигнал 1 будет, если обнулится только счетчик 1 первого числа, т.е. второе число больше первого, на выходе 20 второго числа через элемент И 7 второго числа) будет 1, если обнулится счетчик 1 второго числа, т.е. первое число больше чем второе. На выходе 19 (через элементы И-НЕ Пи НЕ 13) будет 1, если счетчики 1 первого и второго числа обнулятся одновременно, т.е. если числа первое и второе равны.

После обнуления счетчиков I первого и второго числа и приема исходных чисел цикл работы повторяется.

Триггер 8 необходим для блокировки ложных сигналов устройства, которые возникают на выходах 20 первого и второго .числа и выходе 19, в момент первоначального обнуления счетчиков I первого и второго числа и записи в них исходных чисел.

Элемент 6 задержки необходим для того, чтобы задержать переключение триггера 8 в О, на время необходимое для поразрядного обнуления одноименных единичных разрядов в сравниваемых числах после их приема в счетчиках I первого и второго числа.

54

Период следования синхроимпульсов, подаваемых на вход 17 устройства, должен быть больше времени срабатывания счетчиков I первого и второго

числа при вычитании очередной 1 плюс время поразрядного обнуления одноименных единичных разрядов счетчиков 1 первого и второго числа.

Таким образом, возможность поразрядного обнуления одноименных разрядов чисел, содержащих 1, дает возможность значительно повысить быстродействие устройства. Счетчики 1 первого и второго числа идентичны и

работают следующим образом.

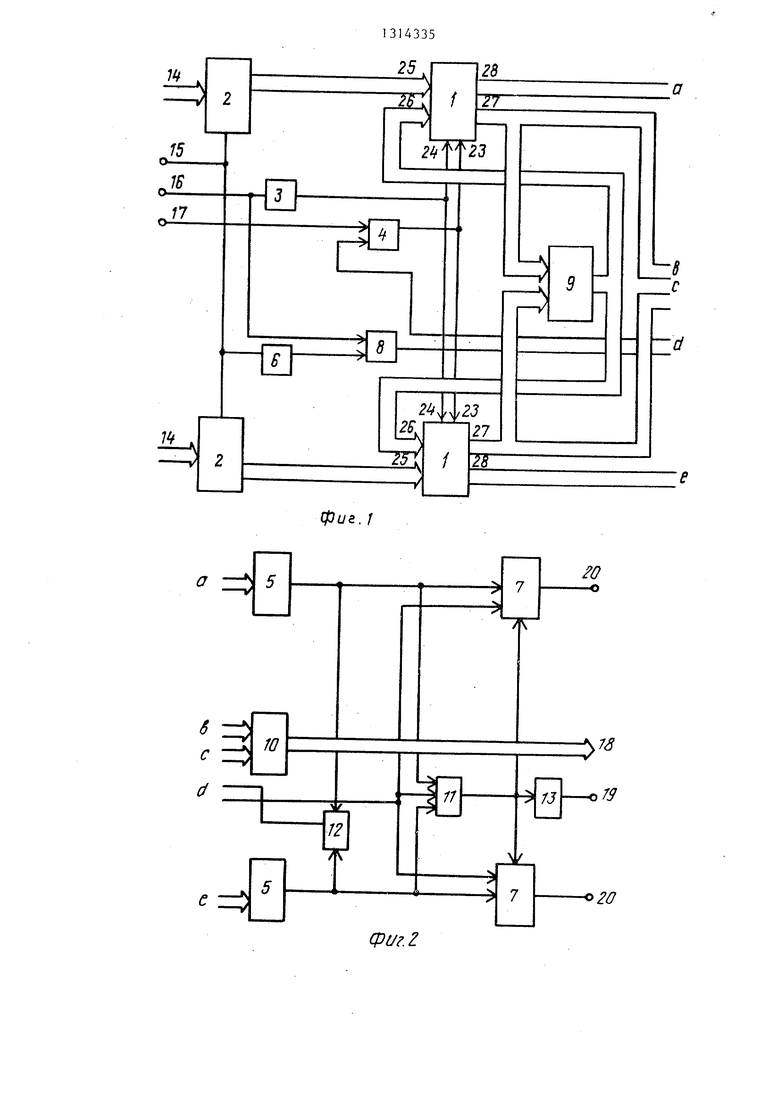

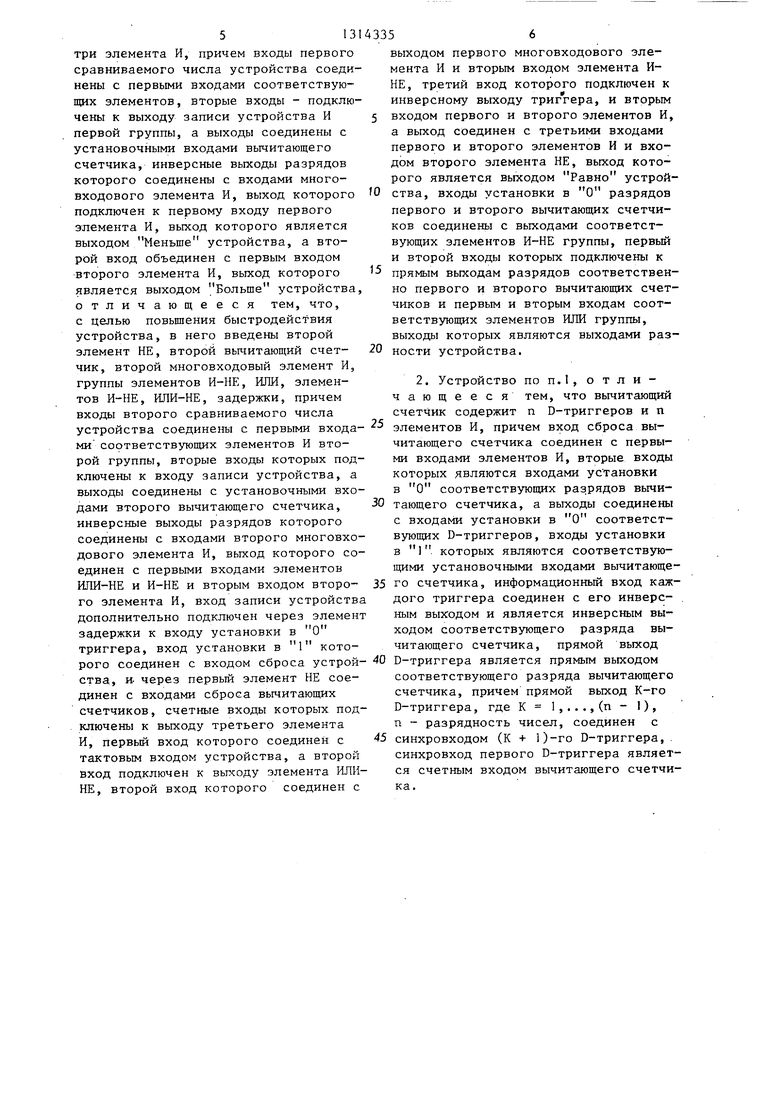

Для общего обнуления счетчика 1 необходимо подать нулевой сигнал на вход 24 общего обнуления счетчика 1, который,-поступая через элементы И 2

на асинхронные R-входы (4-е входы) триггеров 21, устанавливает их в О. Для поразрядного обнуления счетчика 1 нулевые сигналы подаются на входы 26 поразрядного обнуления счетчика 1 , и далее через элементы И 2 на асинхронные R-входы тех триггеров, которые необходимо обнулить.

Число, которое необходимо записать на счетчик 1, подается в двоичном коде на установочные входы 25 счетчика 1. Прямые (первые) выходы триггеров 21 являются прямыми выходами 27 счетчика 1, а инверсные (вторые) выходы - инверсными выходами 28

счетчика 1.

В данном счетчике 1 состояние К-го разряда (К 1, п - 1, где п - величина разрядной сетки) непосредственно передается на вход последующего (к - разряда, что происходит только после переключения всех редыдущих разрядов.

Со счетным (третьим) С-входом каждого последующего триггера 21 соединен единичный (первый) выход

триггера 21 соседнего младшего разряда. Триггер 21 старшего разряда будет перебрасываться лишь в случае переброса триггера 21 соседнего младшего разряда из состояния О в состояние 1.

Формула изобретения

1 . Устройство для сравнения двух чисел, содержащее вычитающий счетчик, многовходовый элемент И, две группы элементов И, триггер, элемент НЕ,

513

три элемента И, причем входы первого сравниваемого числа устройства соединены с первыми входами соответствующих элементов, вторые входы - подключены к выходу записи устройства И первой группы, а выходы соединены с установочными входами вычитающего счетчика, инверсные выходы разрядов которого соединены с входами много- входового элемента И, выход которого подключен к первому входу первого элемента И, выход которого является выходом Меньше устройства, а второй вход объединен с первым входом второго элемента И, выход которого является выходом Больше устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй элемент НЕ, второй вычитающий счетчик, второй многовходовый элемент И, группы элементов И-НЕ, ИЛИ, элементов И-НЕ, ИЛИ-НЕ, задержки, причем входы второго сравниваемого числа устройства соединены с первыми входами соответствующих элементов И второй группы, вторые входы которых подключены к входу записи устройства, а выходы соединень с установочными входами второго вычитающего счетчика, инверсные выходы разрядов которого соединены с входами второго многовхо- дового элемента И, выход которого соединен с первыми входами элементов ИЛИ-НЕ и И-НЕ и вторым входом второго элемента И, вход записи устройства дополнительно подключен через элемент задержки к входу установки в О триггера, вход установки в 1 которого соединен с входом сброса устройства, и- через первый элемент НЕ соединен с входами сброса вычитающих счетчиков, счетные входы которых подключены к выходу третьего элемента И, первый вход которого соединен с тактовым входом устройства, а второй вход подключен к выходу элемента ИЛН- НЕ, второй вход которого соединен с

6

выходом первого многовходового элемента И и вторым входом элемента И- НЕ, третий вход которого подключен к инверсному выходу триг гера, и вторым

входом первого и второго элементов И, а выход соединен с третьими входами первого и второго элементов И и входом второго элемента НЕ, выход которого является выходом Равно устройства, входы установки в О разрядов первого и второго вычитающих счетчиков соединены с выходами соответствующих элементов И-НЕ группы, первый и второй входы которых подключены к

прямым выходам разрядов соответственно первого и второго вычитающих счетчиков и первым и вторым входам соответствующих элементов ИЛИ группы, выходы которых являются выходами разности устройства.

2. Устройство по п.1, о т л и - чающееся тем, что вычитающий счетчик содержит п D-триггеров и п элементов И, причем вход сброса вычитающего счетчика соединен с первыми входами элементов И, вторые входы которых являются входами установки в О соответствующих разрядов вычитающего счетчика, а выходы соединены

с входами установки в О соответствующих D-триггеров, входы установки в 1 которых являются соответствующими установочными входами вычитающе35 го счетчика, информационный вход каждого триггера соединен с его инверсным выходом и является инверсным выходом соответствующего разряда вычитающего счетчика, прямой выход

40 D-триггера является прямым выходом соответствующего разряда вычитающего счетчика, причем прямой выход К-го D-триггера, где К 1,...,(п - 1), п - разрядность чисел, соединен с

45 синхровходом (К + 1)-го D-триггера, . синхровход первого D-триггера является счетным входом вычитающего счетчика.

11

фиа. f

s

с

ю

7

/ -о

фиг. г

8 27

23 25 26

28 27

28 27

25 26 24

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения максимального числа | 1986 |

|

SU1381483A1 |

| Устройство для сравнения чисел | 1980 |

|

SU903862A1 |

| Устройство для выделения максимального числа | 1988 |

|

SU1515159A1 |

| Устройство для исследования путей в графе | 1982 |

|

SU1076909A1 |

| Устройство для выделения максимального числа | 1987 |

|

SU1495781A1 |

| Устройство для сортировки чисел | 1989 |

|

SU1793438A1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Устройство для сравнения чисел | 1986 |

|

SU1361541A1 |

| Устройство для группового сравнения двоичных чисел | 1975 |

|

SU650071A1 |

| Многовходовой сумматор | 1989 |

|

SU1679483A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении контрольной аппаратуры для проверки прохождения информации в дискретных устройствах различного типа и для проверки работоспособности запоминающих устройств, счетчиков, регистров и других более сложных дискретных устройств. Цель Изобретения - повышение быстродействия устройства для сравнения чисел. Устройство содержит вычитающие счетчики , группы элементов И, многовхо- довые элементы И, группы элементов И-НЕ, ИЛИ, элементы ИЛИ-НЕ, НЕ, И. Совокупность введенных элементов и связей позволила после-каждого такта вычитания единиц из счетчиков производить обнуление тех разрядов чисел, в которых у обоих чисел появились единицы, что исключило необходимость подачи вычитающих импульсов в количестве, равном одному из чисел, и, как следствие, привело к увеличению , быстродействия. 1 з.п. ф-лы, 3 ил. to (Л :лэ 00 W) ел

Редактор Ю.Середа

Составитель Е.Иванова Техред М.Ходанич

Заказ 2214/49

Тираж 673Подписное

БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-355 Раушская наб., д. 4/5

Производственно-полиг рафическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор И.Шулла

| Устройство для определения разности двух чисел | 1976 |

|

SU599264A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сравнения чисел | 1981 |

|

SU1012238A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-30—Публикация

1986-03-04—Подача