Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых системах контроля и управления.

Цель изобретения - расширение области применения за счет режекции анализируемых чисел в заданном интервале.

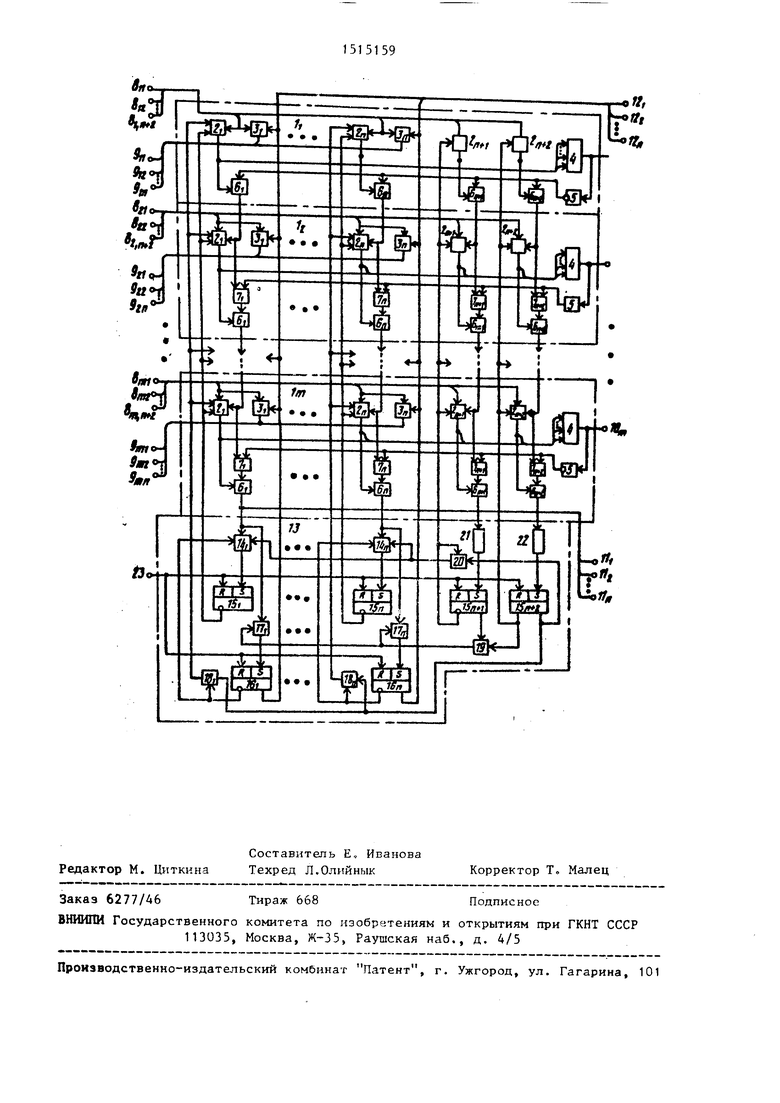

Структурная электрическая схема устройства показана на чертеже.

Устройство содержит узлы 1 анализа, включающие каждый элементы И 2 и 3, многовходовой элемент ИЛИ 4, элемент НЕ 5 и элементы ИЛИ 6, а узлы анализа, кроме первого, дополнительно содержат элементы И 7, входы 8,

выходы 9 режектируемых чисел, выходы 10 максимального числа, выходы 11 адреса максимального числа, выходы

12адреса режектируомого числа, блок

13управления, который содержит элементы И 14, RS-триггеры 15 и 16, элементы И 17, элементы ИЛИ 18, элемент И 19, элемент ИЛИ 20, элементы задержки 21 и 22, вход Сброс 23.

Устройство работает следующим образом.

Рассмотрим сначала работу узлов анализа 11, i 1,m. На информацион- ные входы 8ij (i 1,m, j 1,п+Z) подаются коды i-x разрядов j-x двоичных чисел, из которых первые п чиселУ1 У1 СД

:о

315

образуют входной массив данных, а (п+1)-е и ()-е числа определяют задаваемую верхнюю (В) и нижнюю (А) границы интервала режекции чисел входного массива.

В исходньй момент времени триггеры 15 и 16 должны находиться в нулевом состоянии. Установка триггеров в нулевое состояние производится подачей импульса на шину Сброс 23. При этом на BTOpi e и третьи входы элементов И 2J всех узлов анализа с инверсных выходов триггеров 15 и 16 поступают единичные уровни напряжения, разреша-ющие работу указанных элементов И.

Блоки анализа осуществляют поиск максимального числа среди множества (п+2) заведенных на их входы чисел путем последовательного поразрядного сравнения кодов входных чисел, начиная со старшего (в нашем случае - первого i 1)) разряда. При этом в случае равенства значений одноименных высших разрядов чисел устройство автоматически переходит к сравнению следующих низших разрядов и при несовпадении значений сравниваемых одноименных разрядов исключаются из анализа числа с нулевым значен 1ем иско- мого разряда и поиск максимального числа продолжается среди оставшихся сравниваемых чисел.

Допустим, что на все информацион- ные входы 8,: (j 1,п+2) узла ана- лиза 1 поданы либо коды нулей, либо коды единиц (т.е. старшие разряды всех сравниваемых чисел имеют одинаковые значения). Тогда они пройдут на выход соответствующих элементов И 2.; , откуда поступят на входы многовходо- вого элемента ИЛИ 4 и на первые входы элементов ИЛИ 6j . На выходе элемента ИЛИ 4, связанного с информационным выходЬм 10 устройства появится при этом соответственно код нуля или единицы, а на выходах элементов ИЛИ 6j, связанных вторыми входами с выходом элемента ИЛИ 4 через элемент НЕ 5, будут сформированы коды единиц, разрешающие работу соседнего узла анализа Ij.

Если сигналы на входах 8() не все идентичны (т.е. на некоторых информационных входах (8,к) присутствуют к О ды единиц, а на остальных входах (8,g S k) - коды нулей), то код единицы будет сформирован на информационном выходе 10 данного узла анализа, оп

Q5

0 5 0

с Q

0

594

ределяя значение старшего (первого) разряда максимального числа, и на выходах элементов ИЛИ 6. На выходах остальных элементов l-ITM 63 узла ана- лиза 1 имеют место коды нулей.

Выходные сигналы элементов ИЛИ бу узла анализа 1, поступают в узел анализа , где заводятся на четвертые входы элементов И 2 j и на первые входы элементов И 7. При этом элементы И 2 и 7, на которые поступают упрдв- ляю1цие сигналы единичного уровня, по соответстзуюшим входам разрешены. Все остальные элементы И 7д узла анализа 1, на которые поступают управпяюшуле сигналы нулевого уровня, запрещены, а следовательно, имеют место нулевые управляю1цие сигналы на выходах элементов ИЛИ 6 данного узла анализа.

На первые входы элементов И 2; узла анализа 1 поступают с соответствующих информационных входов 82;значения вторых разрядов сравниваемых чисел. В i-M (i 2,m) узле анализа, как и в первом, выходш ю сигналы элементов И 2 поступают на входы соответствующего многовходового элемента ИЛИ 4 и на первые входы элементов ИЛИ 6:, связанных вторьп-с входами с выходами элементов И 7, на вторые входы которых заводится сигнал с выхода соответствующего элемента НЕ 5.

Если на все разрешенные элементы И 2; узла анализа 1. поступят с соответствующих информационных входов устройства одинаковые (единичные или нулевые) сигналы, то соответственно единичный или нулевой сигнал будет сформирован на выходе элемента ИЛИ 4 данного узла анализа и единичные управляющие сигналы - на выходах элементов ИЖ 6,.

Если же некоторое подмножество разрешенных элементов И 2, поступят с соответствующих информационных входов 8 20 (q 6 k) единичные сигналы, а на осталь 1ых разрешенные элементы И 2у (v 5 q) - нулевые сигналы, то на вьЕходе элемента iUM 4 и выходах элементов ИЛИ , будут иметь место сигналы единичного уровня, а на выходах элементов ИЛИ 6у - сигналы нулевого уровня.

Аналогичным образом работают узлы анализа 1 (), на которые поступают управляющие сигналы с выходов

515

элементов ИЛИ 6j (i-l)-x узлов анализа.

В результате поразрядного сравнения двоичных чисел на информационных выходах 10, i l,lii, устройства формируется код максимального из (n-t-2 сравниваемых чисел, а порядковые номера элементов ИЛИ 6,, т-го узла анализа на выходах которых формируется код единицы, определяют порядковые номера (адреса) найденных максимальных чисел (их может быть несколько). Эти адреса формируются на соответствующих адресных выходах 1lj (j 1,n) уст- ройства,связанных с выходами одноимен- ых элементов ИЛИ 6j m-ro узла анализа.

Рассмотрим теперь процесс замещения найденного максимального числа нулевым. Этот процесс осуществляется с помощью блока управления.

Допустим, что первое найденное максимальное число имеет порядковый номер f. Тогда возникший на выходе элемента ИЛИ бг ш-го узла анализа потенциальный уровень 1 пройдя разрешенный по второму и третьему входам элемент И , опрокинет в единичное состояние по s-входу триггер 15. Возникший при этом нулевой потенциал на инверсном выходе триггера 15, закроет элементы И 2 всех узлов анализа, в результате чего на информаци- онных выходах 10 (i 1,m) и адресном выходе 11, устройства установится код нуля, что указывает на замещение найденного максимального числа на нулевое. Этот процесс замещения является необратимым, т.к. триггер 15 бу- дет сохранять единичное состояние-до очередного сброса его в нуль подачей импульса на шину сброс 19.

После обнуления числа с порядковым номером f автоматически начинается процесс поиска нового максимального числа среди оставшихся входных чисел.

Рассмотрим режим работы устройства в режиме поиска максимального числа среди анализируемых чисел, попадающих в пределы интервала, задаваемого (n+0-M числом (верхняя граница В) и (п+2)-м числом (нижняя граница А).

В результате поочередного обнуления найденных максимальных чисел нас- момент, когда максимальным окажется число В с порядковым номером (п+1). Среди входных чисел может ока51

Q 5

0

25 о „

5

0

5

596

заться еще одно (или несколько) чисел, равных В. Допустим, их порядковый номер f. Тогда на выходе элементов ИЛИ 6 и 6, одновременно возникнут .иничные скачки напряжения, которые, пройдя через элемент И lAf и элемент задержки 21, опрокинут в единичное состояние триггеры 15j и 15,. При этом произойдет обнуление сначала числа с порядковым номером f, а спустя время t задержки элемента задержки 21 будет замещено на нулевое и число В.

Применение элемента задержки 21 исключает неопределенность в обнулении парных чисел. При его отсутствии из-за разброса времен переходных процессов обнуления чисел с различными порядковьпии номерами одно из парных чисел могло бы остаться необнуленным,, После срабатьшания триггера 15 ,., элементы И 14 будут запрещены нулевым потенциалом на выходе элемента ИЛИ 20, а элементы И 17 будут разрешены единичным потенциалом на выходе элемента И 19. После обнуления числа В начнется процесс поиска очередного максимального числа. Пусть его порядковый номер равен t (п+1 ). Тогда единичный скачок напряжения на выходе элемента ИЖ 6 п-го узла анализа, пройдя элемент И 17, опрокинет в единичное состояние триггер При этЬм нулевой потенциал на инверсном выходе триггера 16 запретит по третьему входу элемент И 14, а нулевой потенциал на выходе элемента ИЛИ 18 запретит элементы И 2. во всех узлах анализа, что приведет к обнулению числа с порядковым номером t и поиску с последующим обнулением очередных максимальных чисел, лежащих в пределах заданного интервала с граничными значениями А, В. В результате указанного процесса наступит момент, когда максимальным окажется число А с порядковым номером (п+2) и, возможно, одно (или несколько) ралтгх ему чисел, допустим, с порядковыми номерами f. При этом опрокинется в единичное состояние триггер 16, а спустя время задержки t элемента задержки 22 опрокинется в единичное состояние триггер . Срабатывание указанных триггеров приведет к обнулению чисел с порядковыми номерами f и (п+2).

Время задержки элементов задержки 21 и 22 одинаково и должио удовлетворять условию

.

где - длительность переходного процесса замещения максимального числа на нулевое.

После срабатывания триггера 15. единичный потенциал на его прямом выходе, пройдя элемент ИЛИ 20, разрешит по вторым входам элементы И 14, пройдя через элемент ИЛИ 18, восста- новит разрешающие потенгдллы на третьих входах тех элементов И 2, которые на предьщущих этапах работы устройства оказались по этим входам запрещенными. Среди элементы И 14 по- прежнему останутся запрещенными но третьим входам те из них, которые к моменту срабатьшания триггера 15г,4.г оказались запрещенными на предьщущем этапе работы устройства. Порядковые номера этих элементов И равны порядковым номерам чисел X, удовлетворяющих условию , Таким образом. после срабатывания триггера окажутся восстановленными указан- вые числа X, что приведет к процессу поиска максимального среди них числа Найденное максимальное число (пусть его порядковый номер равен t) не сотрется, поскольку запрещен по третьем входу элемент 14,. и, следовательно, единичный скачок на выходе элемента ИЛИ 6. ш-го каскада не пройдет на 8-вход триггера 15. На этом переходные процессы в устро стве закончатся Код последнего максимального числа вьщелится на информационных выходах I0,j, i 1,П1, его порядковый номер на адресном выходе порядковые номера чисел X, попавших в границы заданного интервала, будут зафиксированы в виде единичных потенциалов на прямых выходах сработавших триггеров 16 и, следовательно, на соответствую 1Щ1Х адресных выходах 12 (j сп) этих чисел.

Для режекции на выходах 9;; (i « 1,m, j 1,n) кодов чисел X в узла анализа используются элементы И 3, k 1,п, связанные первыми входами С первыми вxoдa ш соответствующих элментов И 2, а по вторым входам - управляемые потенциалами на прямьЕХ выходах триггеров 16ц. Поэтому на раз

Q

0 5 О .« .

5

рядных выходах 9;: будут сформированы коды чисел, KOTopbw соответствуют разращенные элементы И 3,, т.е. попавших в границы заданного интервала.

В случае, если среди анализируемых чисел не окажется ни одного числа, попадающего в границы заданного интервала значений, после обнаружения числа А (с порядковым номером п+2) начнется автоматический процесс поиска и последующего обнуления очередных максимальных чисел, который будет продолжаться до тех пор, пока не окажутся замещенными на нуль все (п+2) входных числа. Нулевые потенциалы на всех выходных информационных и адресных выходах устройства будут свидетельствовать об этом факте.

Формула изобретения

Устройство для вьщеления максимального числа, содержащее m узлов анализа (т - число разрядов анализируемых двоичных чисел) и блок управления, каждый узел анализа содержит п- -2 элементов И первой группы (п - число анализируе71ых чисел), пь2 элементов ИЛИ группы, многовходо- вый элемент ИЛИ и элемент НЕ, i-й узел анализа (i 2,...,m) содержит дополнительно п+2 элементов И второй группы, блок управления содержит п эо .-зментов И анализа, п+2 RS-тригге- ров первой группы, элемент И, элемент ИШ и элемент задержки, причем в каждом узле, анализа первый вход k-ro элемента И первой группы (k 1,2, ,..,п) является входом j-ro разряда k-ro анализируемого числа устройства ( 1,2,,..,т), первые входы (п+1)-го и (п+2)-го элементов И первой группы являются входами j х разрядов соответственно верхней и шшней границ устройства, второй вход k-ro элемента И первой группы каждого узла анализа соединен с инверсным выходом k-ro RS-триггер первой группы блока управления, вторые входы (п+1)-х элементов И первых групп всех узлов анализа объединены, и соединены с первым входом элемента ИЛИ блока управления, вторые входы (п+2)-х элементов И первых групп всех узлов анализа подключены к инверсному выходу (п+2)-го RS-триггера первой группы и первому входу элемента И, второй

91

вход которого соединен с прямым вы- ходом (п+1)-го RS-триггера первой группы, в каждом узле анализа выход р-го элемента И первой группы (р 1,2...,п+2) подключен к первому вхо- ду р-го элемента ИЛИ группы и р-му входу многовходового элемента ИЛИ, выход которого является соответству- кяцим максимального числа уст- ройства и подключен к входу элемента НЕ, в первом узле анализа выход элемента НЕ соединен с вторыми входами элементов ИЛИ группы, в i-м узле анализа выход элемента НЕ подключен к первым входам элементов И второй группы,выход р-го элемента И второй группы соединен с вторым входом р-го элемента ИЛИ группы, выход р-го элемента ИЛИ группы (i-l)-ro узла анали- за подключен к третьему входу р-го элемента И первой группы и второму входу р-го элемента И второй группы i-ro узла анализа, выход k-ro элемента ИЛИ группы т-го узла анализа является k-M адресным выходом максимального числа устройства и соединен с первым входом k-ro элемента И анализа, выход которого соединен с входом установки в 1 k-ro триггера первой группы, вход сброса устройства подключен к входам установки в О всех RS-триггеров первой группы, прямой выход (п+2)-го RS-триггера перво группы соединен с вторым входом элемета ИЛИ, выход которого соединен с вторыми входами всех элементов И анализа отличающееся тем, что, с целью расамрения области применения путем режекции анализируемых чисел в заданном интервале, в каждый блок анализа введена дополнительная группа из п элементов И, а в блок управления

3910

введены второй элемент задержки, п дополнительных элементов И, п дополнительных элементов ИЛИ и п RS-триггеров второй группы, причем выход k-ro элемента ИЛИ группы ш-го узла анализа соединен с первым входом k-ro дополнительного элемента И в блоке управления, выход которого соединен с входом установки в 1 k-ro RS-триггера второй группы, инверсный выход которого соединен с третьим входом k-ro элемента И анализа и первым входом k-ro дополнительного элемента ИЛИ, выход которого соединен с третьим входом k-ro элемента И первой группы первого узла анализа и четвертым входом k-ro элемента И первой группы i-ro узла анализа, в каждом узле анализа первый вход k-ro элемента И дополнительной группы является входом j-ro разряда k-го анализируемого числа устройства, а выход - выходом j-ro разряда k-ro режектируемого числа устройства, прямой выход k-ro RS- триггера второй группы соединен с вторыми входами k-x элементов И дополнительных групп всех узлов анализа и является выходом адреса режектируемого числа устройства, инверсный выход (n+l)-го RS-триггера первой группы соединен с вторыми входами (п+1)-х элементов И первых групп всех узлов анализа, выходы (п+1)-го и (п+2)-го элементов ИЛИ группы га-го узла анализа через элементы задержки подключены к входам установки в 1 соответственно (п+1)-го и (п+2)-го RS-триггеров первой группы, прямой выход которого подключен к вторым входам дополнительных элементов ИЛИ, вькод элемента И соединен с вторыми входами дополнительных элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения максимального числа | 1986 |

|

SU1381483A1 |

| Устройство для выделения максимального числа | 1987 |

|

SU1495781A1 |

| Устройство для сортировки информации | 1984 |

|

SU1242932A1 |

| Генератор случайных чисел | 1987 |

|

SU1585794A1 |

| Устройство для сортировки чисел | 1989 |

|

SU1793438A1 |

| Устройство для сравнения чисел | 1980 |

|

SU903862A1 |

| Устройство для выделения экстремального числа | 1985 |

|

SU1553971A1 |

| Устройство для распределения заданий процессорам | 1980 |

|

SU964643A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1783512A1 |

| Устройство для сравнения чисел | 1985 |

|

SU1293726A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых системах контроля и управления. Цель изобретения - расширение области применения путем режекции множества анализируемых чисел, попадающих в заданные границы интервала значений. Устройство содержит M узлов анализа (M-разрядность двоичных чисел) и блок управления. Каждый узел анализа включает элементы И первой группы, элементы ИЛИ группы, многовходовый элемент ИЛИ, элемент НЕ и дополнительную группу элементов И, а узлы анализа, кроме первого, дополнительно содержат элементы И второй группы. Блок управления содержит элементы И, элементы ИЛИ, элемент И, элементы ИЛИ, RS-триггеры первой группы и второй группы, а также элементы задержки. Устройство позволяет, кроме выделения максимального числа, провести режекцию анализируемых чисел, попавших в заданный интервал. 1 ил.

| Устройство для поиска чисел в заданном диапазоне | 1982 |

|

SU1116426A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР по заявке 4333692/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-15—Публикация

1988-01-05—Подача